# FOR REFERENCE

IOT U BE TAKEN FROM THIS ROOM

### TIME-VARIANT LINEAR TRANSISTOR MODEL TO BE USED IN SWITCHING CIRCUITS

by

İrfan Karagöz

B.S. in E.E., Boğaziçi University, 1983

Submitted to the Institute for Graduate Studies in Science and Engineering in partial fulfillement of the requirements for the degree of

Master of Science

in

Electrical Engineering

Boğaziçi University

TIME-VARIANT LINEAR TRANSISTOR MODEL TO BE USED IN SWITCHING CIRCUITS

APPROVED BY

Doç.Dr. Avni Morgül (Thesis Supervisor)

Y.Doç.Dr. Ömer Cerid

Prof.Dr. Sabih Tansal

DATE OF APPROVAL : June.5.1985

**11**

#### ACKNOWLEDGEMENTS

I would like to express my gratitude to my thesis supervisor Doç.Dr.Avni Morgül for his advice and helpful criticisms that have been valuable in all parts of this work.

I would also like to express my thanks to Prof.Dr.Sabih Tansal and Y.Doç.Dr.Ömer Cerid for their kind helps and understanding throughout my graduate study.

### TIME-VARIANT LINEAR TRANSISTOR MODEL TO BE USED IN SWITCHING CIRCUITS

The aim of this thesis is to apply a time-variant linear large signal transistor model (15) to the Bipolar Junction Transistors (BJTs) and Vertical V-groove Metal Oxide Semiconductor Transistors (VVMOSTs), to analyse basic three transistor switching circuits by using this model, and to compare the results of analyses with the experimental results.

The time-variant linear large-signal BJT model includes the time-variant equivalent output resistance and capacitance and the D.C. voltage source which represents the saturation voltage. In this model the equivalent output capacitance is connected in parallel with the equivalent output resistance and the D.C. voltage source which are connected in series with one another. This model which is applied to the bipolar transistor is also used as the output side of the VVMOS transistor model beyond the saturation voltage. The input side of the VVMOS model includes only an input capacitance between the gate and the source. The related model parameters are determined separately for the BJTs and VVMOS transistors.

The equivalent output resistance and capacitance of the new BJT model are changed only in the transient regions as an exponential function. They are taken as a constant value in the other regions.

In the VVMOS transistor model the equivalent output resistance

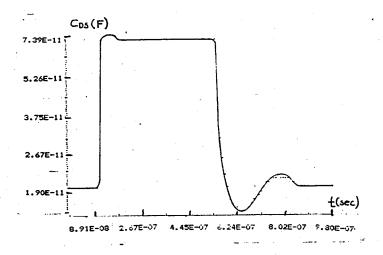

is considered as a function of input voltage in the resistive and pinch-off regions. For the turn-on delay and cut-off regions, the equivalent output resistance is taken as a constant value which is equal to the transistor maximum drain to source resistance. The equivalent output capacitance is considered as a function of the output voltage for all regions.

The model related to the VVMOS transistors can also be used for the Vertical Double-diffused Metal Oxide Semiconductor (VDMOS) transistor.Useful formulas and necessary explanations for this purpose and the related model parameters are also considered as the subject of this thesis.

As an application, the analysis of three basic transistor switching circuits, switching circuits with resistive, resistiveinductive and resistive-inductive-capacitive loads, and the Complementary VDMOS (CVDMOS) inverter are done by using the proposed models. The accuracy of the models is evaluated by a detailed comparison of simulated and measured switching characteristics on the experimental high-speed switching circuits.

This new model which is applied to the transistor switching circuits can be considered as the best one which provides an optimum combinetion of accuracy, ease of parameter acquisition, simplicity, and less computational costs, so far.

V

### ANAHTARLAMA DEVRELERİNDE KULLANILACAK ZAMANLA DEĞİŞEN LİNEER TRANZİSTOR MODELLERİ

Bu tezin gayesi bipolar tranzistorlar için geliştirilmiş modeli VVMOS tranzistorlara uygulamak, bu model yardımı ile tranzistorlu üç temel anahtarlama devresinin analizlerini yapmak ve elde edilen analiz sonuçlarını deneysel sonuçlarla mukayese etmektir.

Bipolar tranzistorun lineer zamanla değişen büyük işaret modeli, zamanla değişen eşdeğer çıkış direnç ve kapasitesi ile doyma gerilimini temsil eden bir doğru gerilim kaynağından oluşur.Bu modelde, eşdeğer çıkış kapasitesi,seri olarak birbirine bağlanmış olan eşdeğer çıkış direnci ve doyma gerilim kaynağı ile paralel bağlı olarak düşünülmüştür.Bipolar tranzistor için geliştirilen bu model kollektör emetör doyma gerilimi dışında VVMOS tranzistor modelinin çıkış kısmı olarak da kullanılmıştır.VVMOS tranzistor modelinin giriş kısmı ise sadece tranzistorun kapı ve kaynak terminalleri arasındaki giriş kapasitesinden oluşmuştur.İlgili model parametreleri herbir tranzistor için ayrı ayrı belirlenmiştir.

Bipolar tranzistorlar için geliştirilen yeni modelin eşdeğer çıkış direnç ve kapasitesi sadece geçiş bölgelerinde üstel fonksiyon şeklinde değiştirilmiş diğer bölgelerde sabit olarak düşünülmüştür.

VVMOS tranzistor modelinde eşdeğer çıkış direnci direnç ve geçiş bölgelerinde giriş geriliminin bir fonksiyonu olarak düşünülmüştür.Kesimde ise eşdeger çıkış direnci maksimum tranzistor savakkaynak direncine eşit olan sabit bir değer olarak alınmıştır.Eşdeğer

vi

Çıkış kapasitesi ise tüm bölgelerde çıkış geriliminin bir fonksiyonu olarak ifade edilmiştir.

VVMOS tranzistorlar için geliştirilen model VDMOS tranzistorların modellenmesinde de kullanılabilir.Bunun için gerekli formül ve açıklamalar ile model parametrelerinin elde edilmesi bu tezin konuları arasındadır.

Uygulama olarak tranzistorlu üç temel anahtarlama devresi olan rezistif,rezistif-indüktif,rezistif-indüktif-kapasitif yüklü anahtarlama devrelerinin ve CVDMOS eviricinin analizleri bu model yardımı ile yapılmıştır.Modelin doğruluğu,yüksek hızlı anahtarlama devreleri üzerinde ölçmeyle ve teorik olarak da bilgisayar çalışması sonucu elde edilen anahtarlama karekteristiklerinin teferruatlı bir mukayesesi ile incelenmiştir.

Tranzistorlu anahtarlama devrelerinin çalışmasını açıklamak ve göstermek için geliştirilen bu model şimdiye kadar yapılan modeller içinde basitlik,doğruluk,parametre verme kolaylığı ve devre analizlerinde daha az bilgisayar zamanı gerektirmesi gibi hususların en iyi birleşimini sağlayan bir model olarak düşünülebilir.

### TABLE OF CONTENTS.

|                                                                                                   | Page        |

|---------------------------------------------------------------------------------------------------|-------------|

| ACKNOWLEDGEMENTS                                                                                  | 1 <b>11</b> |

| ABSTRACT                                                                                          | iv          |

| ÖZET                                                                                              | vi          |

| LIST OF FIGURES                                                                                   | xi          |

| LIST OF TABLES                                                                                    | xiv         |

| LIST OF SYMBOLS                                                                                   | xv          |

| I. INTRODUCTION                                                                                   | l           |

| II. DESCRIPTION OF TIME-VARIANT LINEAR LARGE-SIGNAL<br>TRANSISTOR MODELS AND THEIR PARAMETERS     | . 4         |

| 2.1. General Review to Non-Linear Models for Bipolar<br>Transistors                               | 4           |

| 2.2. A Time-Variant Linear Large-Signal Modeling of<br>Bipolar Transistors                        | 6           |

| 2.3. Description of BJT Model Parameters                                                          | ° . 9       |

| 2.3.1. Theoretical Explanations and Formulas<br>for Switching Times                               | 10          |

| a. Turn-on Time                                                                                   | 10          |

| (1). Delay Time                                                                                   | 10          |

| (2). Rise Time                                                                                    | 12          |

| b. Turn-off Time                                                                                  | 13          |

| (1). Storage Time                                                                                 | 13          |

| (2). Fall Time                                                                                    | 14          |

| 2.3.2. Determination of Saturation Voltage and<br>On and Off Impedances of Bipolar<br>Transistors | 15          |

| 2.4. General Review to VVMOS Transistors                                                          | 19          |

| 2.5. A Time-Variant Linear Modeling Of VVMOS<br>Transistors for Switching Circuits                | 20          |

| 2.6. Description of VVMOST Model Parameters                                                       | 21          |

| 2.6.1. ON-Resistance                                                                              | 21          |

| 2.6.2. OFF-Resistance                                                                             | 22          |

|        |      |         |                                                            | Page       |

|--------|------|---------|------------------------------------------------------------|------------|

|        |      | 2.6.3.  | Pinch-Off Resistance                                       | 22         |

|        |      | 2.6.4.  | Device Capacitances                                        | 23         |

|        |      | 2.6.5.  | Switching Times                                            | 27         |

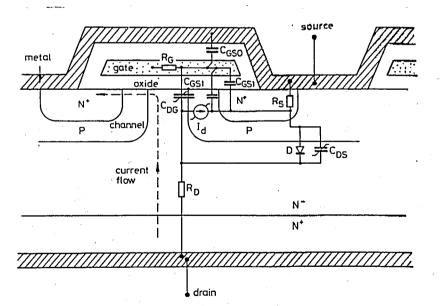

|        | 2.7. | General | Review to VDMOS Transistors                                | 29         |

|        | 2.8. | Descrip | tion of VDMOST Model Parameters                            | 34         |

|        |      | 2.8.1.  | D.C. Characterisation                                      | 34         |

|        |      |         | a. Determination of $V_{\underline{T}}$ and B              | 3 <b>7</b> |

|        |      |         | b. Determination of R <sub>S</sub>                         | 3 <b>7</b> |

|        | •    |         | c. Determination of $R_{D}$                                | 37         |

|        |      | 2.8.2.  | A.C. Characterisation                                      | 38         |

|        |      |         | a. Determination of $C_{DG}$                               | 38         |

|        |      |         | b. Determination of C <sub>DS</sub>                        | 39         |

|        |      |         | c. Determination of C <sub>GS</sub>                        | <b>39</b>  |

|        |      |         | d. Determination of R <sub>G</sub>                         | 40         |

| III.   |      |         | NG CIRCUITS ANALYSES BY USING TIME-<br>R TRANSISTOR MODELS | 42         |

|        | 3.1. | Analysi | s of Switching Circuits with RLC Load                      | 4 <b>7</b> |

|        |      | 3.1.1.  | Case of Ll=0                                               | 51         |

|        |      |         | a. Determination of $I_{L}(t)$                             | 52         |

|        |      |         | b. Determination of $V_0(t)$                               | 53         |

|        |      | 3.1.2.  | Case of $Ll \neq 0$                                        | 54         |

|        |      |         | <b>a.</b> The Case of $\triangle \pm 0$                    | 56         |

|        |      |         | (1). Determination of $I_{L}(t)$                           | 57         |

|        |      |         | (2). Determination of $V_0(t)$                             | 58         |

|        |      |         | b. The Case of $\triangle \langle 0 \rangle$               | 60         |

|        |      |         | (1). Determination of $I_{L}(t)$                           | 60         |

|        |      |         | (2). Determination of $V_0(t)$                             | 63         |

|        |      |         | c. The Case of $\triangle > 0$                             | 67         |

|        |      |         | (1). Determination of $I_{L}(t)$                           | 67         |

| •<br>• |      |         | (2). Determination of $V_0(t)$                             | 69         |

ix

ş

|                          |         |                 |                                                                                                       | Page |

|--------------------------|---------|-----------------|-------------------------------------------------------------------------------------------------------|------|

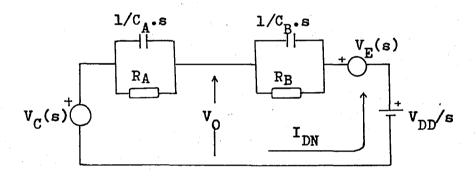

|                          | 3.2.    | Analysi         | s of Comlementary VDMOS Inverter                                                                      | 71   |

|                          |         | 3.2.1.          | Determination of $I_{DN}(t)$                                                                          | 76   |

|                          |         | 3.2.2.          | Determination of $V_0(t)$                                                                             | 77   |

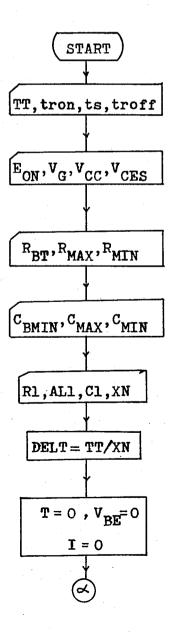

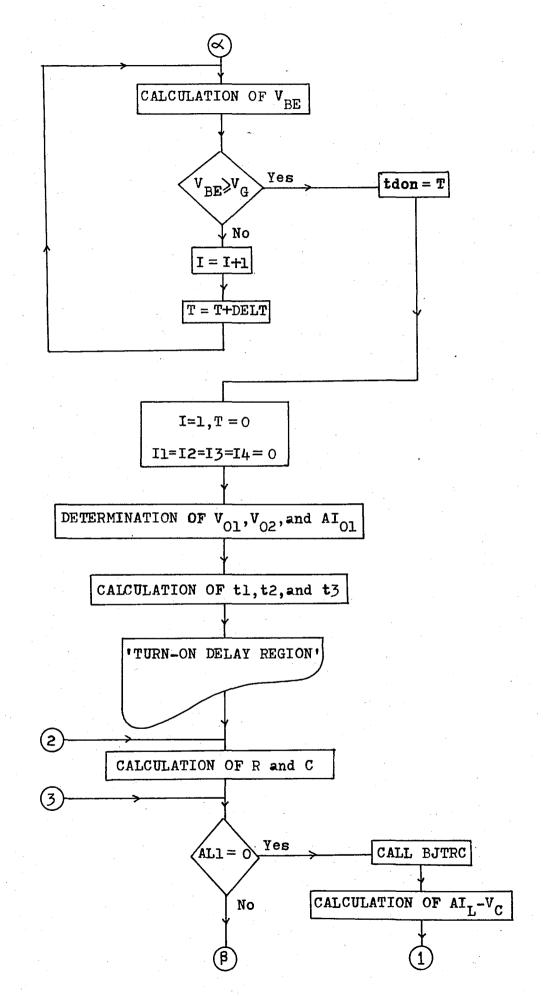

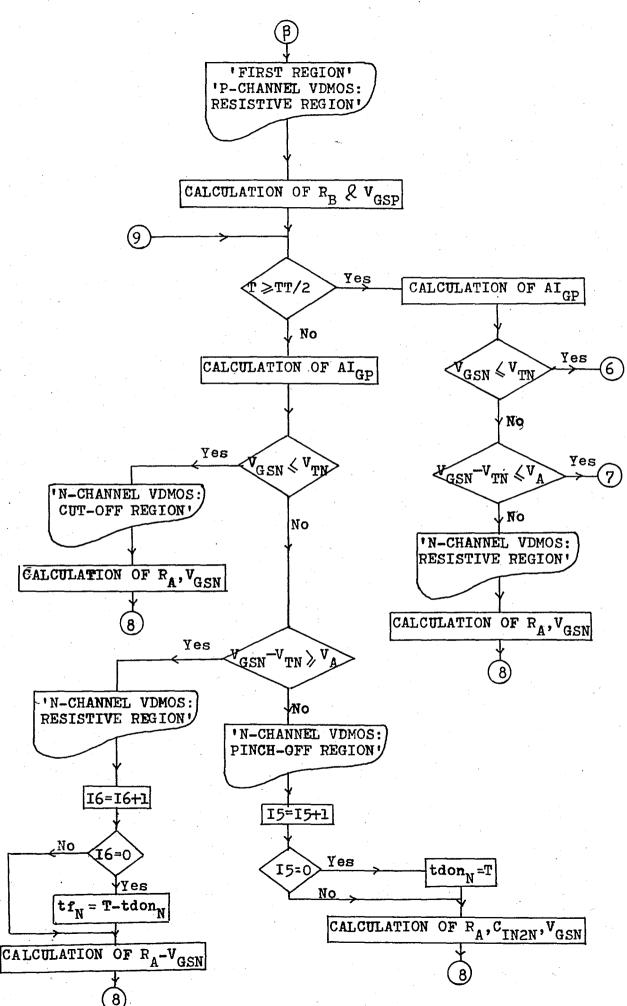

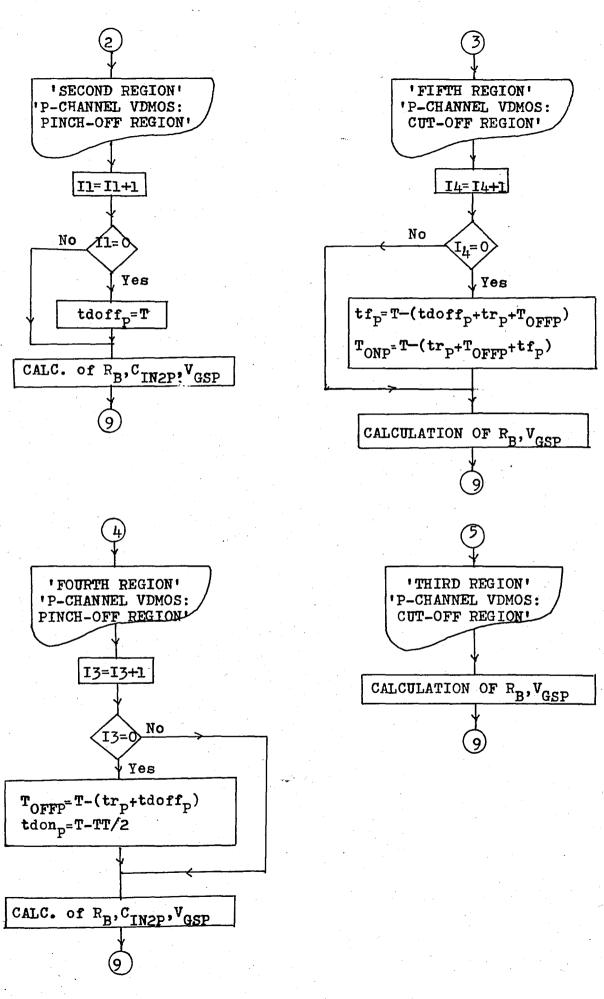

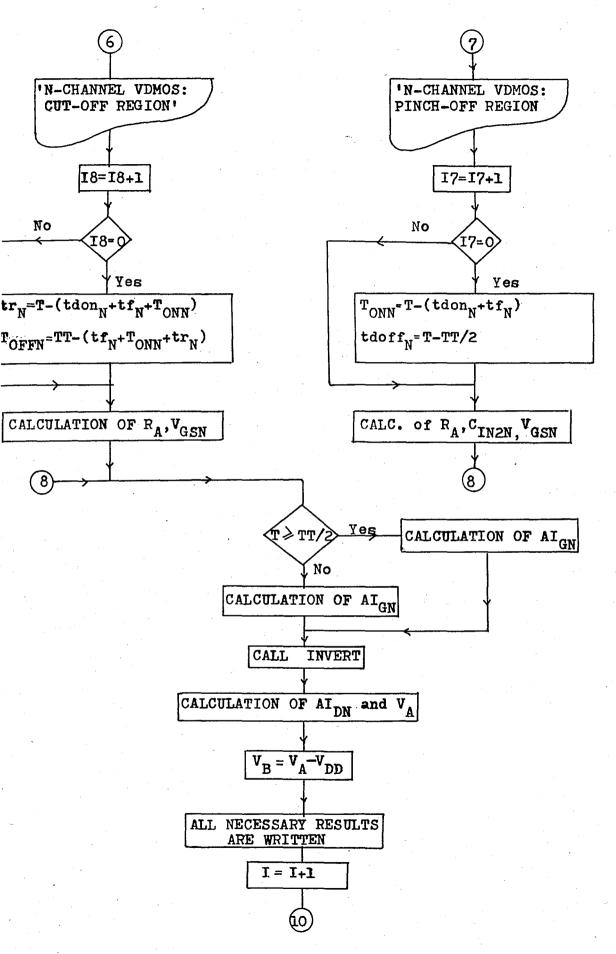

|                          | 3.3.    | Compute         | r Program Description                                                                                 | 79   |

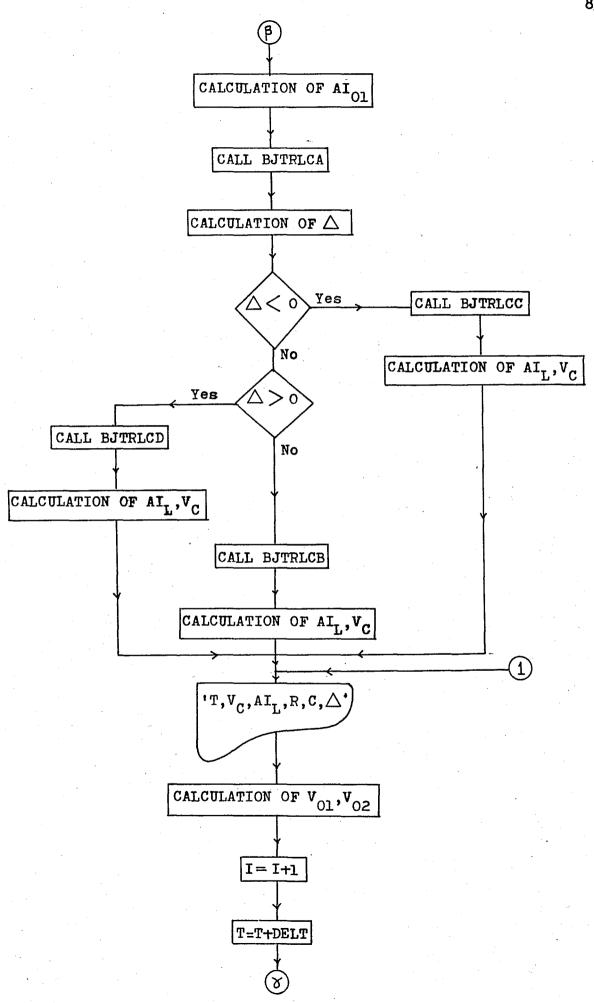

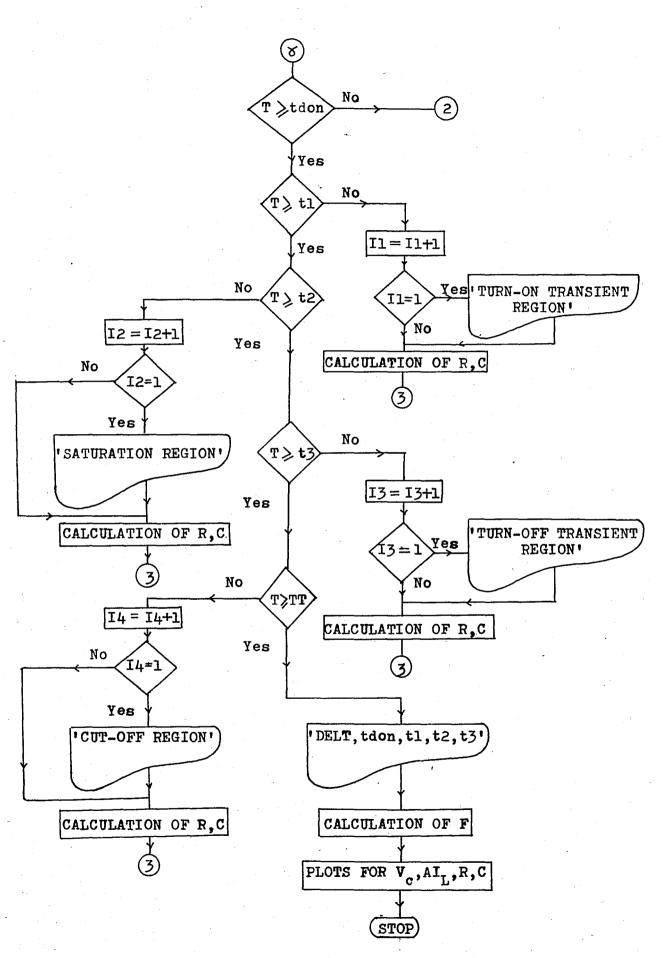

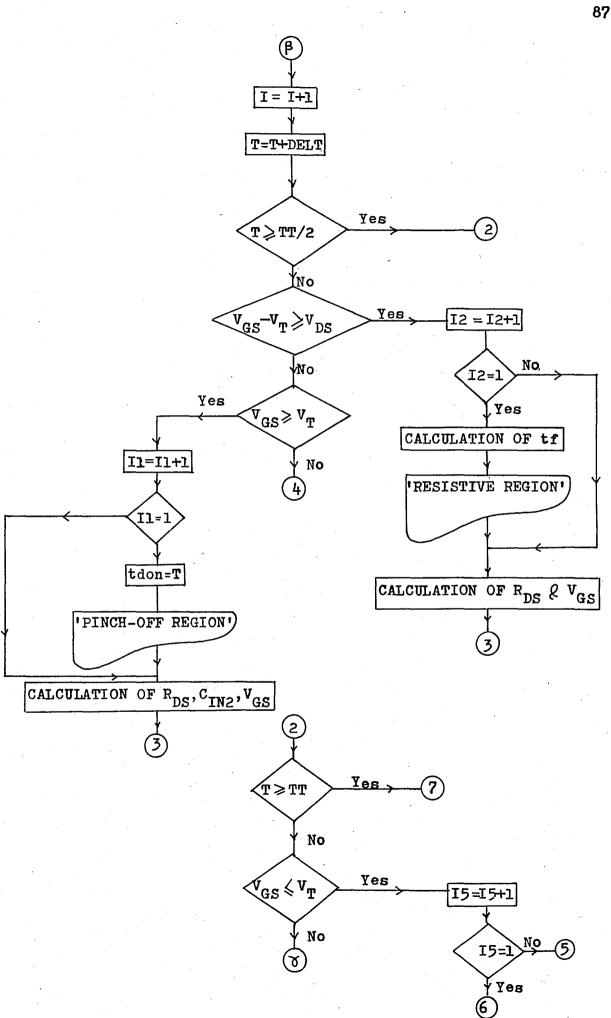

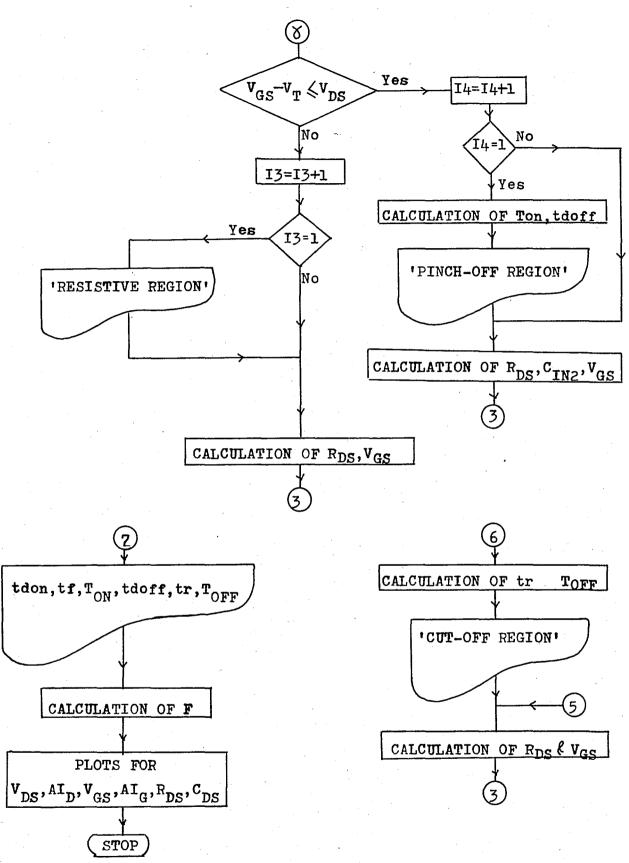

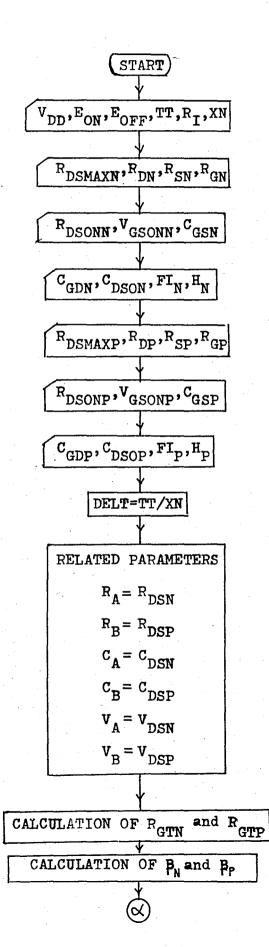

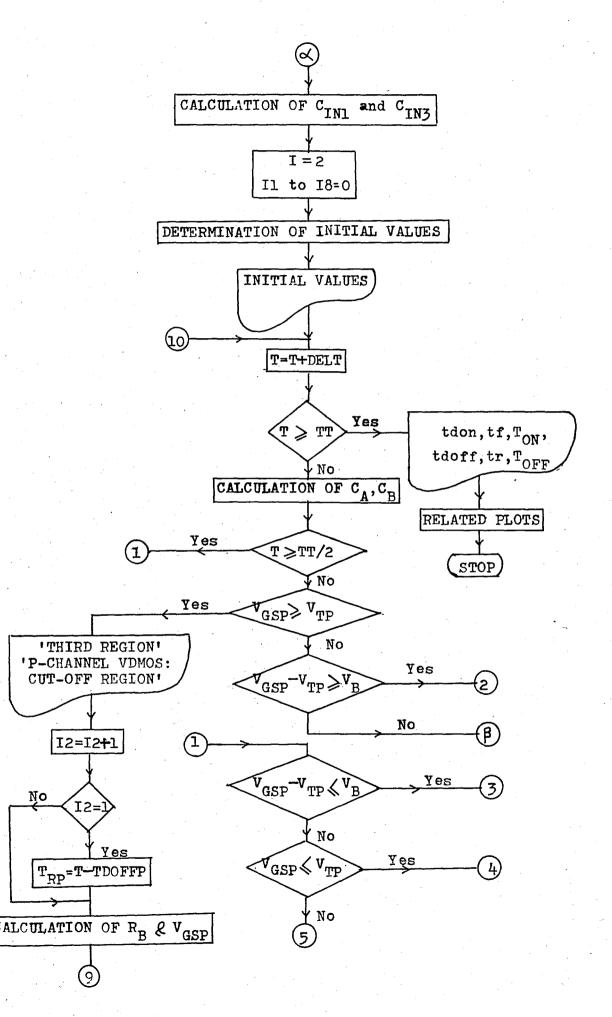

|                          |         | 3.3.1.          | Flowchart Related to the Computer<br>Simulation of BJT Switching Circuit<br>with RLC Load             | 81   |

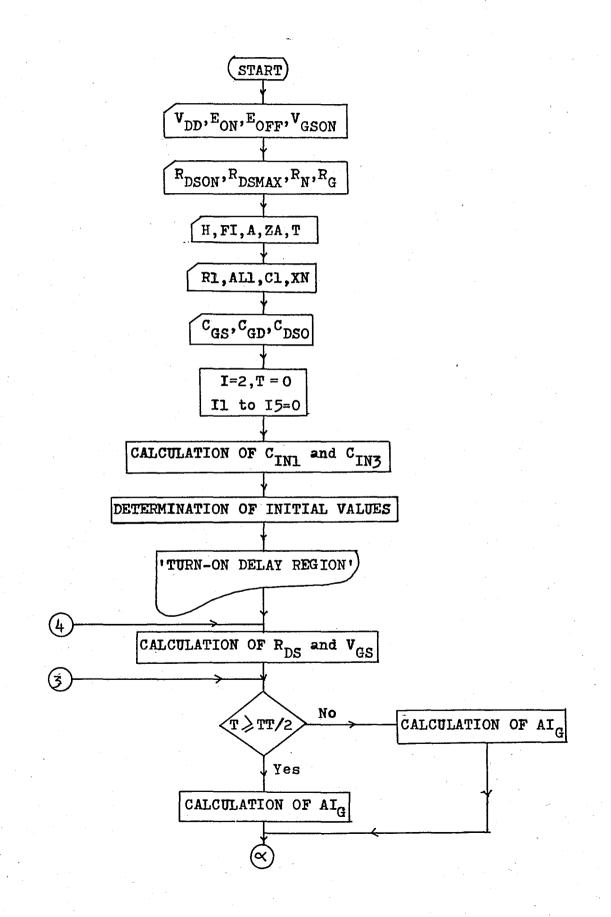

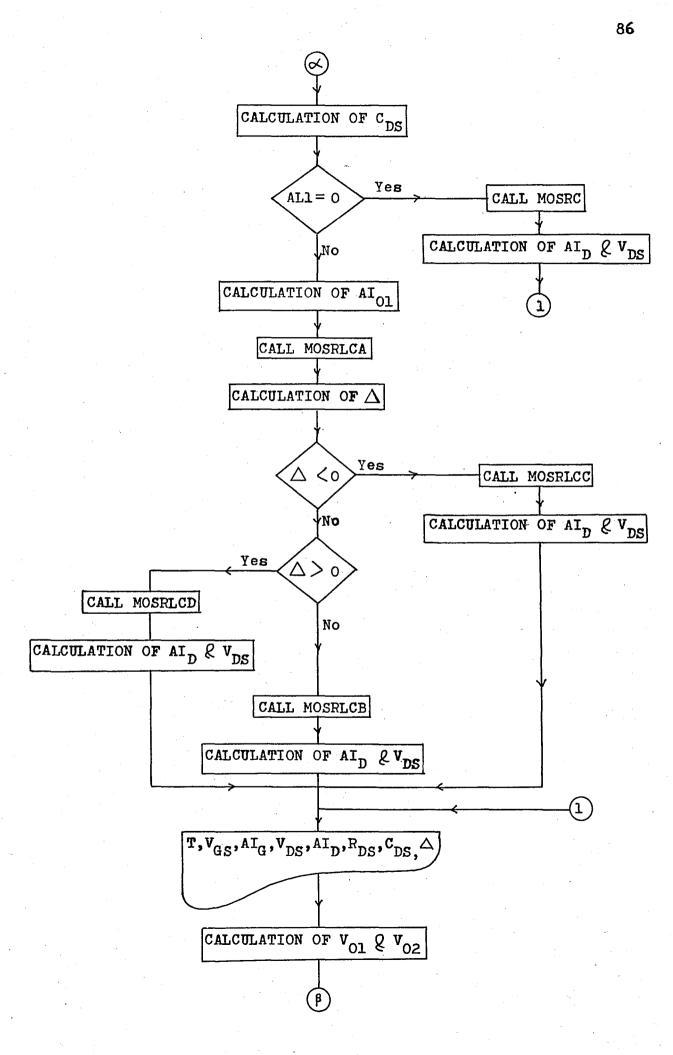

|                          |         | 3.3.2.          | Flowchart Related to the Computer<br>Simulation of VVMOS and VDMOS Switching<br>Circuit with RLC Load | 85   |

|                          |         | 3.3.3.          | Flowchart Related to the Computer<br>Simulation of CVDMOS Inverter                                    | 89   |

| IV.                      | COMPA   | RISON OF        | THEORETICAL AND EXPERIMENTAL RESULTS .                                                                | 94   |

|                          | 4.1.    | Introdu         | ction                                                                                                 | 94   |

|                          | 4.2.    |                 | ation of the Validity of the BJT<br>g Procedure                                                       | 95   |

| 1                        | 4•3•    |                 | ation of the Validity of the VVMOS and<br>odeling Procedure                                           | 101  |

|                          |         | 4.3.1.          | VVMOS Transistors                                                                                     | 101  |

|                          |         | 4•3•2•          | VDMOS Transistors                                                                                     | 107  |

|                          |         | 4.3.3.          | Complementary VDMOS Inverter                                                                          | 111  |

| v.                       | CONCL   | USION .         | •••••••••••••                                                                                         | 115  |

| APPENDIX A               | EBERS   | -MOLL MC        | DEL                                                                                                   | 118  |

| APPENDIX B               | VVMOS   | (VERTIC         | AL V-GROOVE MOS) TRANSISTORS                                                                          | 123  |

|                          |         |                 | RAMS                                                                                                  | 129  |

| BIBLIOGRAPHY             | • • • • | • • • • • • • • | •••••                                                                                                 | 141  |

| REFERENCES NOT CITED 143 |         |                 |                                                                                                       | 143  |

x

### LIST OF FIGURES

| . · · · ·    |                                                                                                                         | Page |

|--------------|-------------------------------------------------------------------------------------------------------------------------|------|

| FIGURE 2.1   | The new time-variant linear large-signal model for BJTs                                                                 | 7    |

| FIGURE 2.2.a | Variation of the BJT output resistance<br>versus time                                                                   | 7    |

| FIGURE 2.2.b | Variation of the BJT output capacitance<br>versus time                                                                  | 7    |

| FIGURE 2.3   | Linear model developed for the input<br>side of BJTs                                                                    | 11   |

| FIGURE 2.4   | Equivalent circuit to be used in the calculation of tdon                                                                | 12   |

| FIGURE 2.5   | Typical I versus $V_{CE}$ characteristics at constant I B                                                               | 16   |

| FIGURE 2.6   | A time-variant linear large-signal model<br>for VVMOSTs                                                                 | 20   |

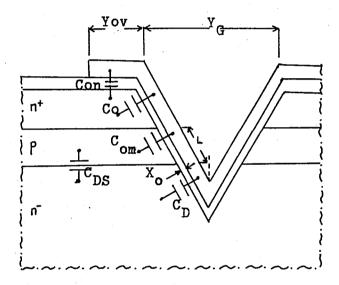

| FIGURE 2.7   | Capacitances associated with the VVMOST structure                                                                       | 24   |

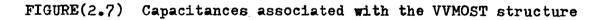

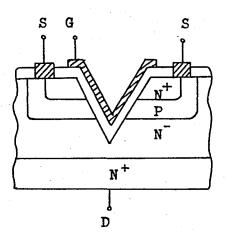

| FIGURE 2.8   | Cross section of the high voltage VDMOS device                                                                          | 31   |

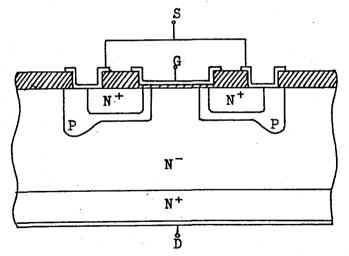

| FIGURE 2.9   | Cross-section of single cell of power<br>VDMOS structure                                                                | 32   |

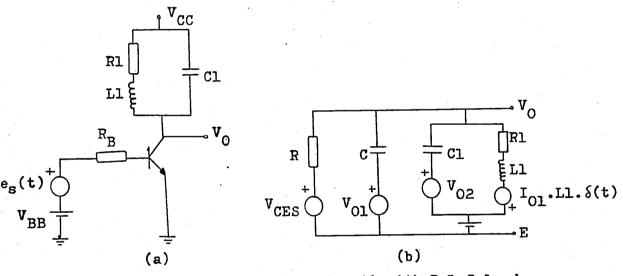

| FIGURE 3.1.a | A BJT switching circuit with RLC load                                                                                   | 47   |

| FIGURE 3.1.b | The related linear equivalent circuit                                                                                   | 47   |

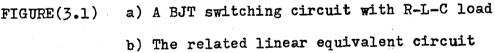

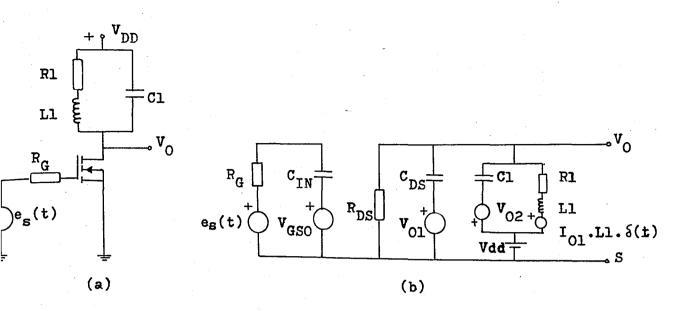

| FIGURE 3.2.a | A VVMOST switching circuit with RLC load                                                                                | 48   |

| FIGURE 3.2.b | The related linear equivalent circuit                                                                                   | 48   |

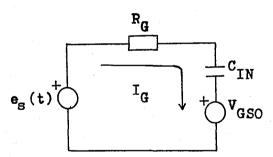

| FIGURE 3.3   | Input side of the equivalent circuit shown in Figure(3.2.b)                                                             | 48   |

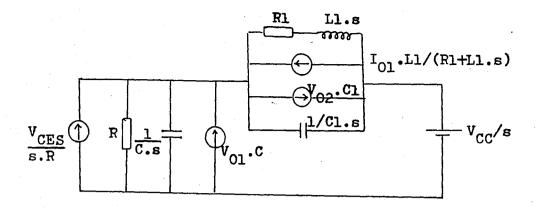

| FIGURE 3.4   | The circuit obtained by using Laplace<br>transform method and network theorems in<br>the circuit shown in Figure(3.1.b) | 49   |

| FIGURE 3.5   | The circuit to be used in the analysis                                                                                  | 49   |

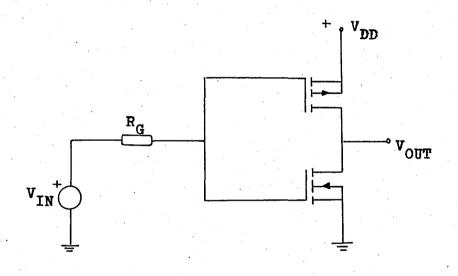

| FIGURE 3.6   | A complementary VDMOS inverter circuit                                                                                  | 71   |

xi

|             |                                                                                                                               | Page       |

|-------------|-------------------------------------------------------------------------------------------------------------------------------|------------|

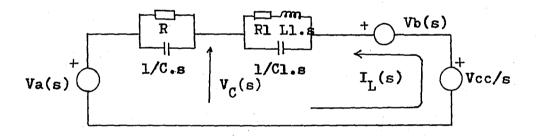

| FIGURE 3.7  | Equivalent linear model of the CVDMOS inverter circuit                                                                        | 71         |

| FIGURE 3.8  | Equivalent circuit which is obtainad by using the Laplace transform method and network                                        |            |

|             | theorems in the circuit showm in Figure(3.7)                                                                                  | 72         |

| FIGURE 3.9  | The circuit to be used in the analysis                                                                                        | 73         |

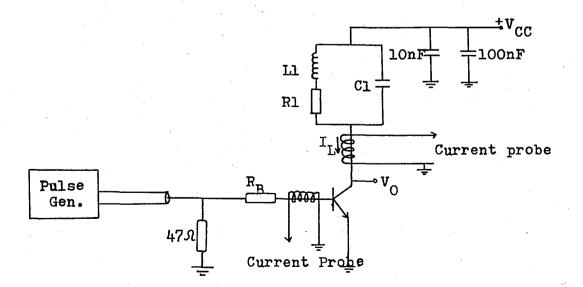

| FIGURE 4.1  | BJT switching circuit and measurement set-up                                                                                  | 96         |

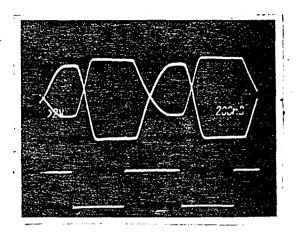

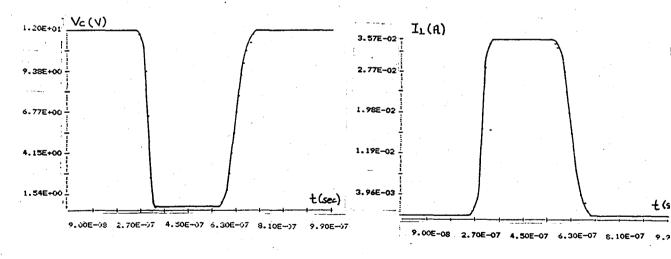

| FIGURE 4.2  | Oscilloscope measurements of the switching<br>waveforms related to the BJT switching<br>circuit with resistive load           | 97         |

| FIGURE 4.3  | Simulated switching waveforms of the BJT<br>switching circuit with resistive load                                             | 97         |

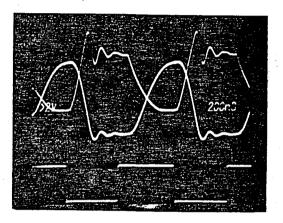

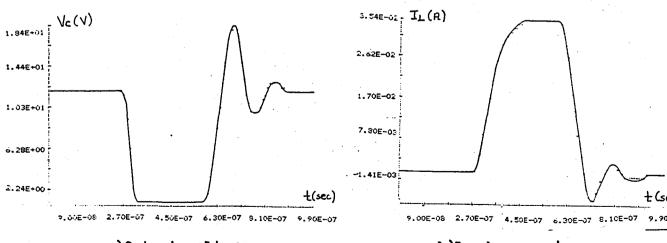

| FIGURE 4.4  | Oscilloscope measurements of the switching<br>waveforms related to the BJT switching<br>circuit with resistive-inductive load | 98         |

| FIGURE 4.5  | Simulated switching waveforms of the BJT switching circuit with RL load                                                       | 98         |

| FIGURE 4.6  | Oscilloscope measurements of the switching<br>waveforms related to the BJT switching<br>circuit with RLC load                 | 99         |

| FIGURE 4.7  | Simulated switching waveforms of the BJT<br>switching circuit with RLC load                                                   | 9 <b>9</b> |

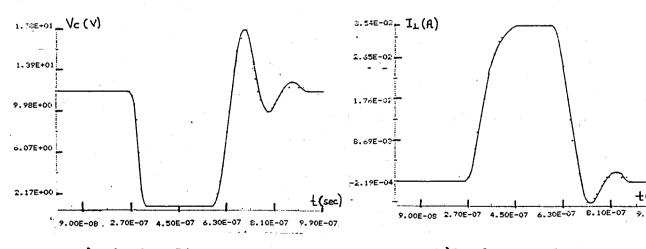

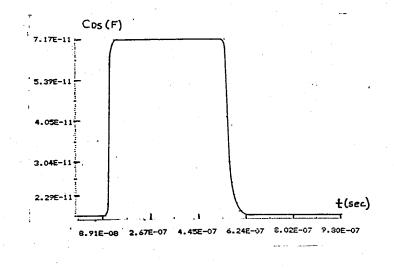

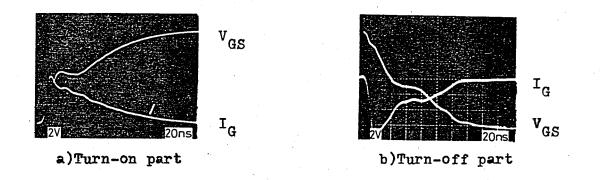

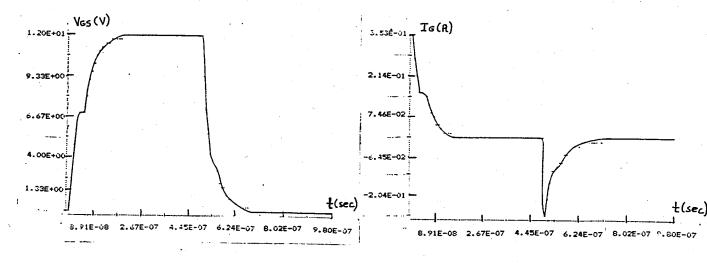

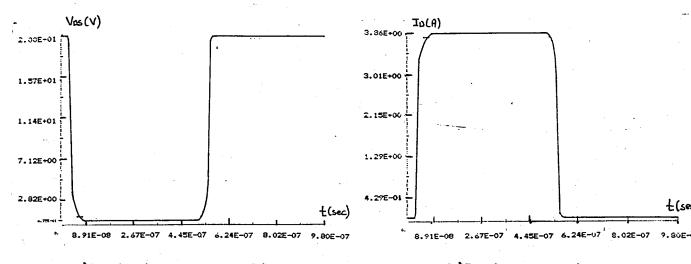

| FIGURE 4.8  | Simulated switching waveforms related to<br>the input side of the VVMOS switching<br>circuit with resistive load              | 102        |

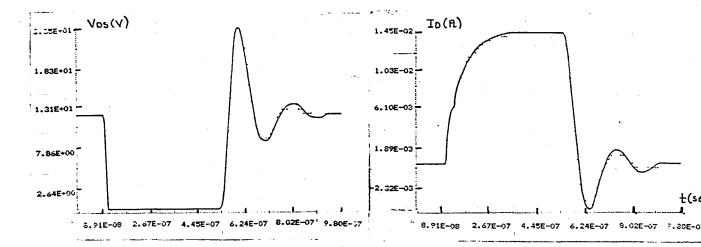

| FIGURE 4.9  | Simulated switching waveforms related to<br>the output side of the VVMOS switching<br>circuit with resistive load             | 103        |

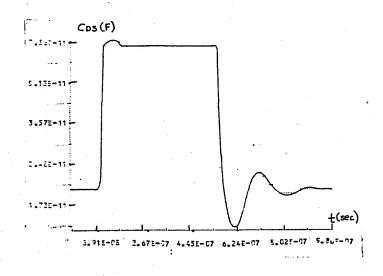

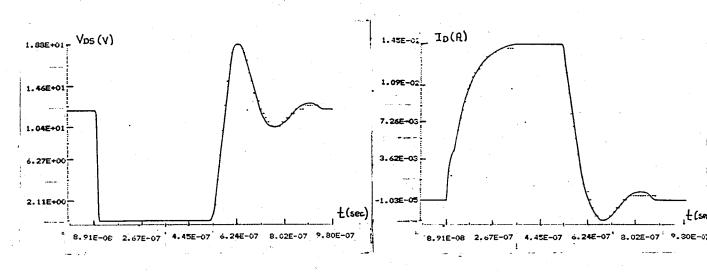

| FIGURE 4.10 | Simulated switching waveforms related to<br>the output side of the VVMOS switching<br>circuit with resistive-inductive load   | 104        |

| FIGURE 4.11 | Simulated switching waveforms related to<br>the output side of the VVMOS switching<br>circuit with RLC load                   | 105        |

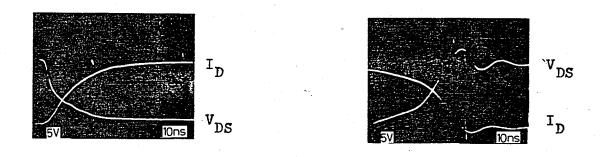

| FIGURE 4.12 | Oscilloscope measurements of V and I waveforms related to the VDMOS switching                                                 |            |

|             | circuit with resistive-load                                                                                                   | 108        |

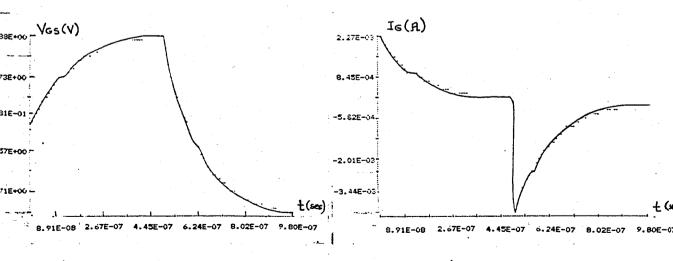

| FIGURE 4.13 | Simulated switching waveforms related to<br>the input side of the VDMOS switching                                             |            |

|             | circuit with resistive load                                                                                                   | 108        |

xii

|        |      |                                                                                                                              | Page |

|--------|------|------------------------------------------------------------------------------------------------------------------------------|------|

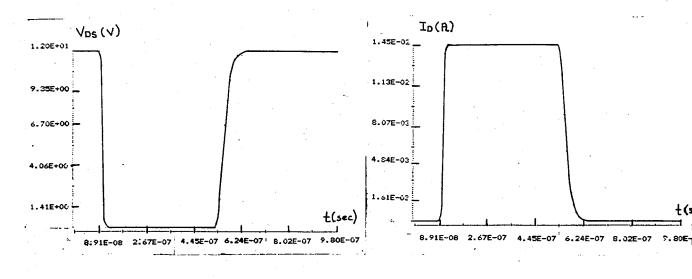

| FIGURE | 4.14 | Oscilloscope measurements of $V_{DS}$ and $I_{D}$<br>waveforms related to the VDMOS switching<br>circuit with resistive load | 109  |

| FIGURE | 4.15 | Simulated switching waveforms related to the<br>output side of the VDMOS switching circuit<br>with resistive load            | 109  |

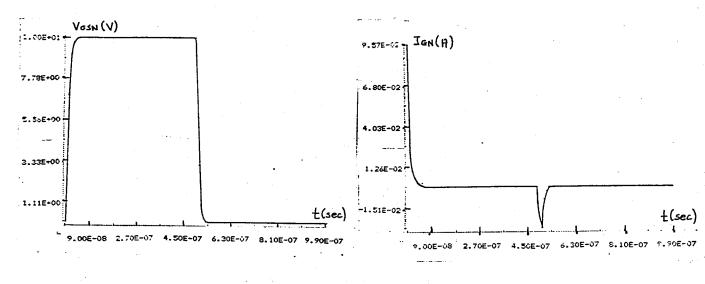

| FIGURE | 4.16 | Simulated switching waveforms related to<br>the n-channel transistor in CVDMOS inverter                                      | 112  |

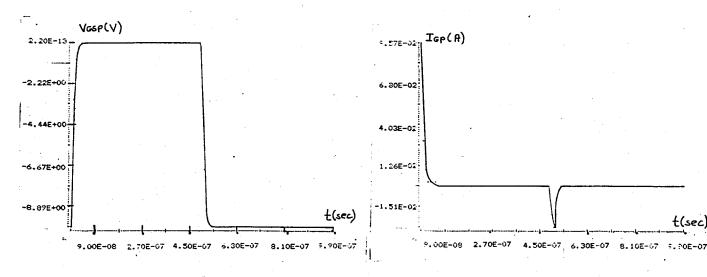

| FIGURE | 4•17 | Simulated switching waveforms related to<br>the p-channel transistor in CVDMOS inverter                                      | 112  |

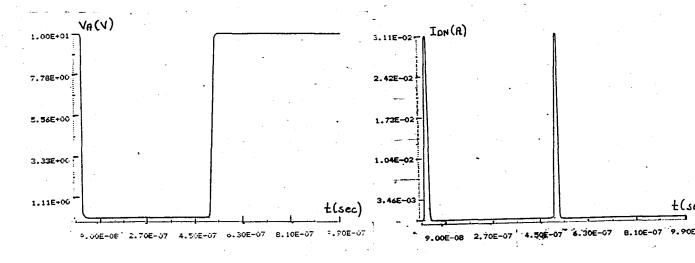

| FIGURE | 4.18 | Simulated switching waveforms related to the CVDMOS inverter                                                                 | 113  |

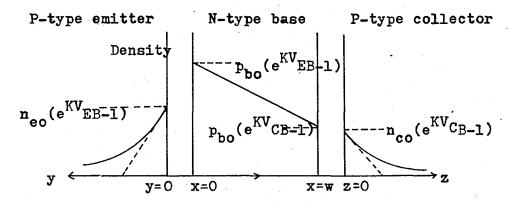

| FIGURE | A.l  | Excess minority-carrier distribution                                                                                         | 118  |

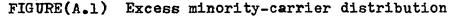

| FIGURE | A.2  | Circuit representing equations                                                                                               | 121  |

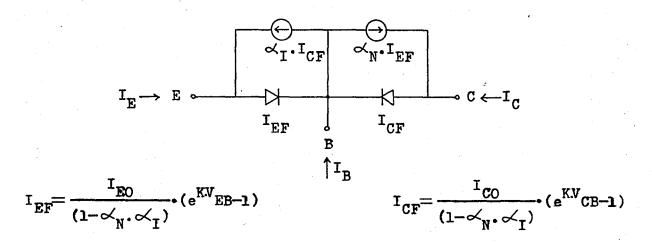

| FIGURE | A.3  | Complete Ebers-Moll model                                                                                                    | 122  |

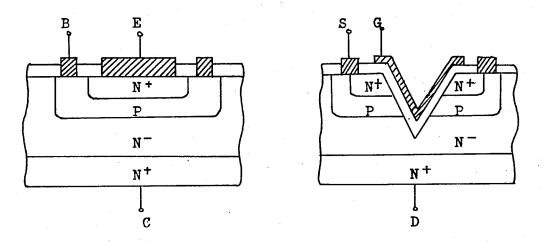

| FIGURE | A.4  | Cross section of a VVMOS channel                                                                                             | 124  |

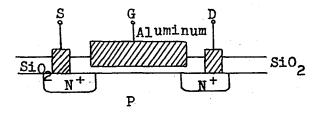

| FIGURE | A.5  | The cross section of a conventional MOSFET                                                                                   | 125  |

| FIGURE | A.6  | A comparison of a four-layer bipolar transistor with VVMOS transistor                                                        | 128  |

xiii

### LIST OF TABLES .

| TABLE 2.1 | Pertinent VVMOST switching relationships                                     | 28  |

|-----------|------------------------------------------------------------------------------|-----|

| TABLE 3.1 | Explanation of CVDMOS inverter equivalent circuit parameters                 | 72  |

| TABLE 4.1 | 2N1711 bipolar transistor parameters                                         | 95  |

| TABLE 4.2 | Comparison of theoretical and measured ringing frequencies and overshoots    | 100 |

| TABLE 4.3 | VVMOS transistor parameters                                                  | 101 |

| TABLE 4.4 | simulated and calculated VVMOS switching characteristics                     | 106 |

| TABLE 4.5 | VDMOS (IRF130) model parameters                                              | 107 |

| TABLE 4.6 | Comparison between measured and simulated<br>VDMOS switching characteristics | 110 |

| TABLE 4.7 | N-channel VDMOS transistor (BST78) parameters                                | 111 |

| TABLE 4.8 | Simulated CVDMOS inverter switching characteristics                          | 114 |

xiv

#### LIST OF SYMBOLS

#### Total area of VVMOST within groove

Bipolar transistor collector to emitter time-variant non-linear capacitance

Load capacitance

Drain to source junction capacitance

Drain to source junction capacitance at  $V_{nc}=0$

Gate to drain capacitance

Gate to source capacitance

MOS transistor input capacitance

Maximum value of collector to emitter time-variant non-linear capacitance

Minimum value of collector to emitter time-variant non-linear capacitance

Stray capacitance for VDMOSTs

Timing interval

Low value of the square wave applied to the input of the switching circuit

High value of the square wave applied to the input of the switching circuit

Ringing frequency

Grading coefficient  $0.3 \leq H \leq 0.5$

Load current for MOS transistors

Gate current

Load current for bipolar transistors Initial condition of load inductance Load inductance

Bipolar transistor collector to emitter time-variant non-linear resistance

Cl

A

C

c<sub>DS</sub> c<sub>DSO</sub>

C<sub>GD</sub>

C<sub>GS</sub>

CIN

C<sub>MAX</sub>

C<sub>MIN</sub>

Cp

DELT

EOFF

<sup>E</sup>on

F

H ID IG IL IOL

Ll R

| RL                 | Load resistance                                                                    |

|--------------------|------------------------------------------------------------------------------------|

| R <sub>B</sub>     | Bipolar transistor base to emitter<br>time-variant non-linear resistance           |

| R <sub>BT</sub>    | Series combination of base spreading<br>resistance and external base<br>resistance |

| R <sub>D</sub>     | Drain resistance                                                                   |

| <sup>R</sup> DS    | Drain to source time-variant non-<br>linear resistance                             |

| R <sub>DSMAX</sub> | Maximum value of the drain to source<br>time-variant non-linear resistance         |

| R <sub>G</sub>     | Gate resistance                                                                    |

| RI                 | Input voltage source impedance in<br>MOS switching circuit                         |

| RMAX               | Maximum value of collector to emitter<br>time-variant non-linear resistance        |

| R <sub>MIN</sub>   | Minimum value of collector to emitter time-variant non-linear resistance           |

| R <sub>N</sub>     | N(-) drift layer resistance in VVMOST                                              |

| <sup>R</sup> s     | Source resistance                                                                  |

| tdoff              | Turn-off delay time                                                                |

| tdon               | Turn-on delay time                                                                 |

| tſ                 | Fall time                                                                          |

| TOFF               | Off time                                                                           |

| TON                | On time                                                                            |

| tr                 | Rise time                                                                          |

| troff              | Turn-off transient time                                                            |

| tron               | Turn-on transient time                                                             |

| T <sub>S</sub>     | Storage time                                                                       |

| TT                 | Operating period                                                                   |

| v <sub>BE</sub>    | Base to emitter output voltage                                                     |

| v <sub>cc</sub>    | Supply voltage for BJT switching circuits                                          |

V<sub>CES</sub> V<sub>DD</sub> V<sub>DS</sub> V<sub>G</sub> V<sub>GS</sub> V<sub>O</sub>

v<sub>02</sub> v<sub>t</sub> xn

Za

β

ø

Collector to emitter saturation voltage

Supply voltage for MOS transistor switching circuits

Drain to source voltage

Cut-in voltage of bipolar transistors

Gate to source voltage

Output voltage

Initial voltage across the collector to emitter or drain to source timevariant non-linear capacitance by depending on the type of the switching circuit to be used

Initial voltage across the load capacitance

Threshold voltage of MOS transistors

Total number of steps

VVMOS area occupied by the grooves at the P-N(-) interface

Constant related to MOS transistor

Transistor junction potential

#### I. INTRODUCTION

Most transistor models are aimed either toward portraying the interaction of the device with an external circuit or toward relating device behavior to device physics, and most models involve some degree of approximation. In the former case, the primary interest is the specification of performance; just as it is sometimes convenient to use only the two-port parameters of an electric network to describe its terminal behavior, so it is sometimes convenient to prescribe a particular set of terminal measurements as parameters which characterize transistor behavior. In the latter case, the primary concern is the analysis of device behavior in terms of physical processes. Either case, when carried to its extreme, is unsatisfactory from a model point of view.On one hand, the terminal properties, while conveniently measured, do not themselves elucidate the reasons for device behavior. On the other hand.consideration of physical processes alone generally leads to cumbersome results which obscure dominant tendencies and inhibit qualitative interpretation of the relationship between processes and terminal behavior.

An ideal model may be regarded as one which

- 1) involves parameters which maintain a one-to-one correspondence with physical processes.

- 2) lends itself well to analysis of circuit problems.

- 3) involves a degree of approximation sufficient to enhance qualitative understanding and interpretation while maintaining reasonable quantitative accuracy.

- 4) cuts computer costs with sufficient accuracy for practical application.

Large-signal models for transistors are necessary tools for the device engineer, who must specify device performance, and the circuit designer, who must be equipped for both the analysis and design of transistor circuits. Over the past few years, a number of models have been proposed. The non-linear models which have received the most attention are the Linvill lumped model(1), the Beaufoy-Sparkes charge-control model(2), and the Ebers-Moll model (3), (4), (5).

2

The classical method of analyzing high-power high-frequency transistor performance is to use the hybrid- $\Pi$  model.To date, this model has been the most popular high-frequency equivalent circuit for a junction transistor.Because this model does not include a collector-base diode, it can accurately represent operation in the ACTIVE region, but not in the ON and OFF regions.

Although each of the hybrid-TT model parameters varies with instantaneous signal level and time, they are normally assumed to have fixed values which are a function of the average level of operation.With a judicious selection of parameter values, this model can be adjusted to predict small and even medium signal performance quite well over wide frequency ranges. It does not predict very well the characteristics of a transistor driven heavily into saturation. That's why a linear model more complete than the hybrid-TT type is necessary to represent and explain the operation of transistor switching circuit.

The purpose of this thesis is to apply a time-variant linear large-signal transistor model (15) to the bipolar transistors and

VVMOS-or VDMOS-transistors, to analyse basic three transistor switching circuits by using the related model, and to compare the results of analysis with the experimentel results.

In the second chapter the new linear large-signal transistor

model is introduced.At the beginning a genaral information is given about the non-linear models.Then the Ebers-Moll model is preferred as a favorite model within non-linear models .But high-computer costs are seen as a disadvantage in the Ebers-Moll model.The new linear model which is more simple than the Ebers-Moll model is developed and it is considered as a linearized version of the Ebers-Moll model.This model is proposed separately for the bipolar and VVMOS-or VDMOS-transistors.After the model is presented,the necessary formulas and explanations for the related model parameters are given separately for each one of the transistors.

In the third chapter basic transistor switching circuits and their characteristics are explained and the analysis of all the switching circuits are made. For each one of the BJTs and VVMOST-or VDMOS-switching circuits only one analysis is made because they have the similar equivalent linear circuits when the proposed model is used instead of the related transistor. Then, as an application of the proposed VVMOST-or VDMOS-model, the analysis of a CVDMOS inverter is made. At the end of the chapter, for all the analyses, the related flowcharts are given. A general idea for the preparation of computer programs is also given.

The last chapter is devoted to the experimental studies. Profitting by the related references and the measurement techniques, the values of the parameters required to characterise the model are conveniently obtained. The application of the proposed time-variant linear large-signal model to the basic transistor switching circuits to compute transient switching characteristics is illustrated and the accuracy of the model is evaluated by a detailed comparison of computer simulations with experimental switching waveforms.

## II. DESCRIPTION OF TIME-VARIANT LINEAR LARGE-SIGNAL TRANSISTOR MODELS AND THEIR PARAMETERS

Transistor models are tools which are used to facilitate the optimization of transistor design and performance. The degree of complexity of a model is always a compromise between accurate device representation and ease of analysis. Relatively simple linear models have traditionally been used to characterize high-frequency transistors with excellent results for low-signal levels. At largesignal levels, however, a transistor exhibits significant effects which can not be analyzed by means of the simpler models. These effects are generally caused by harmonic components of the voltages and currents generated by non-linear mechanisms within the transistor. To date, many large-signal non-linear models have been used to represent these mechanism. A general information is to be given about the non-linear large-signal models at the beginning in this chapter.

Our main interest in this chapter is to represent a new timevariant linear large-signal transistor model which provides an optimum combination of accuracy, ease of parameter acquisition and simplicity, (15). After development of the model which is constructed for the bipolar and VVMOS-or VDMOS-transistors, parameter evaluation for this model is presented.

2.1. General Review to Non-Linear Models for Bipolar Transistors

Of the many large-signal models which have been proposed for the bipolar transistors, three have received the most attention. These are the Linville lumped model(1), the Beaufoy-Sparkes chargecontrol model (2), and the Ebers-Moll model (3), (4), (5). Each represents a different approach to solution of the relations describing the

distributed base region of a diffused transistor.

The Linville lumped model is obtained by solution of the continuity equation for current carriers at finite intervals in the base. The form of the solution leads naturally to a set of lumped elements which can be treated as a network. The accuracy of the representation depends on the number of sections into which the base is divided. Of the three models, this type provides the most accurate physical description of the transistor. The resulting representation, however, is quite cumbersome to analyse, (1).

The charge-control model focuses upon the relationship between the terminal currents and minority-carrier stored charge. The resulting equations can be represented by circuit elements. Although the elements are not the conventional type, they can be used in a circuit analysis. (2).

The Ebers-Moll model is based upon the concept of superimposing normal and inverse transistors in which the collector-base and emitter-base junctions are represented by diodes shunted with capacitors. This model is the easiest of the three types to use because it can be represented by conventional circuit elements. The biggest shortcoming of the model is that it does not accurately include the effect of the carrier storage. However, the errors incurred by this lack depend upon the frequency of operation, (3), (4), (5).

When these three models are to be compared with each other, the Ebers-Moll model is preferred as a favorite model because

- 1) its elements have meaning as a result of familiarity;

- 2) there is some easy way of getting data for the elements;

- 3) temperature changes and aging can be easily accounted in the model;

- 4) from past experience the model has given satisfied results;

5) the model provides insight to what is going on,(6). The Ebers-Moll model is explained in detail in Appendix A.

It must be further emphasized that a non-linear model such as the Ebers-Moll model is not always the best choice for large-signal problems, too.Far simpler linear time-variant large-signal models may cut computer costs with sufficient accuracy.For this purpose a new time-variant linear transistor model is developed to represent and explain the operation of transistor switching circuits, (15).

### 2.2. A Time-Variant Linear Large-Signal Modeling of Bipolar Transistors

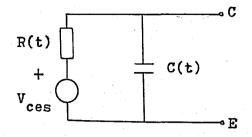

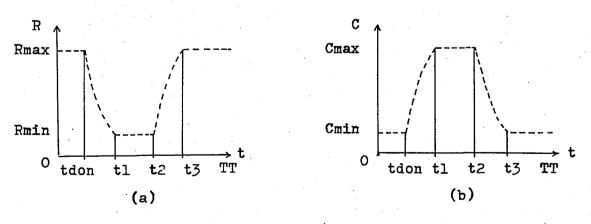

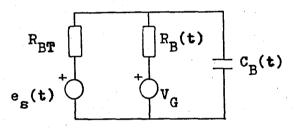

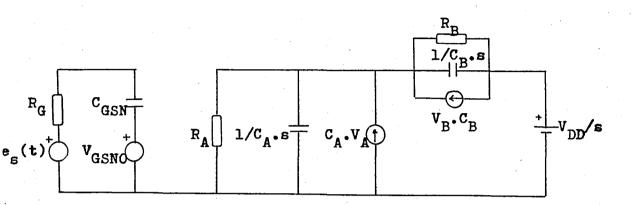

A time-variant linear large-signal model for the bipolar transistors is developed in this section. This model, basically, includes the time-variant equivalent output resistance and capacitance and the D.C. voltage source which represents the transistor saturation voltage. In this model the equivalent output capacitance is connected in parallel with the equivalent output resistance and the D.C. voltage source which are connected in series with one another. The complete model is shown in Figure (2.1).

The equivalent output resistance and capacitance of this model are taken as a constant value in the cut-off and saturation regions. They are changed only in the transient regions. For determining the variations of the output resistance and capacitance versus time, their time-variant functions must be determined at the beginning. By means of the experimental studies it is seen that if their variations versus time are taken as an exponential function the load current and output voltage waveforms which are closer to the real waveforms are obtained. The variations versus time of the output resistance and capacitance are shown in Figures(2.2.a) and (2.2.b),

respectively.

FIGURE(2.1) The new time-variant linear large-signal model for BJTs

In this model the number of calculating points within one period is considered as XN.One-step value within the timing range of one period is defined as

$$DELT = TT/XN$$

(2.2.1)

where TT is the operating period.

In the turn-on and turn-off transient regions, the numbers of the equivalent output resistance and capacitance to be changed are considered, respectively, as

FIGURE(2.2) a) Variation of the BJT output resistance versus time b) Variation of the BJT output capacitance versus time

$$XNl = XN.(tron/TT)$$

(2.2.2)

and

$$XN2 = XN.(troff/TT)$$

(2.2.3)

where tron and troff are the rise and fall times for the load current, respectively.

In the consideration of the junction transistor as a switch the calculations must be made for five regions, separately. These regions can be defined as the turn-on delay region , the turn-on transient region, the saturation region, the turn-off transient region, and the cut-off region.

For the turn-on delay and cut-off regions, the values of the equivalent output resistance and capacitance are Rmax and Cmin, respectively. Their time-variant functions in the turn-on transient regions are expressed as

$$R(t) = Rmax.e^{[((t-tdon)/tron).ln(Rmin/Rmax)]}$$

(2.2.4)

and

$$C(t) = Cmin.e \left[ ((t-tdon)/tron).ln(Cmax/Cmin) \right]$$

(2.2.5)

where tdon is the turn-on delay time.

In the saturation regions, the output resistance and capacitance have the constant values of Rmin and Cmax. In the turn-off transient region their time-variant functions are given by

$$R(t) = Rmin.e^{\left[ ((t-t2)/troff).ln(Rmax/Rmin) \right]}$$

(2.2.6)

and

$$C(t) = Cmax.e\left[((t-t2)/troff).ln(Cmin/Cmax)\right]$$

8

(2.2.7)

where t2 is the time passing up to the beginning of the turn-off transient.

2.3. Description of BJT Model Parameters

For using the proposed time-variant linear transistor model in the analysis of BJT switching circuits the model parameters must be determined at the beginning. The model parameters are the switching times, the off impedance and the on impedance of the transistor. For determining the model parameters, the parameters of

a) the forward common-emitter large-signal current gain,  $\beta_{\rm F}$ ,

b) the inverse common-emitter large-signal current gain,  $B_{p}$ ,

c) the transistor saturation current, Is,

d) the temperature at which the parameters are obtained, Tnom,

e) the emitter ohmic resistance, R<sub>EE</sub>,

f) the collector ohmic resistance, R<sub>CC</sub>,

g) the base ohmic resistance, R<sub>BB</sub>,

h) the emitter-base junction capacitance at  $V_{BE} = 0, Cje0$ ,

i) the collector-base junction capacitance at  $V_{BC} = 0, Cjc0,$

j) the emitter-base barrier potential,  $V_{ZE}$ ,

k) the collector-base barrier potential,  $V_{ZC}$ ,

1) the emitter-base capacitance gradient factor, N<sub>E</sub>,

m) the collector-base capacitance gradient factor, N<sub>C</sub>,

n) the normal-mode intrinsic gain-bandwidth product, Fn,

o) the inverted-mode intrinsic gain-bandwidth product,F1,

p) the emitter-base junction ohmic leakage resistance, R<sub>R</sub>,

q) the collector-base junction ohmic leakage resistance, R<sub>C</sub>,

r) the emission constant for emitter-base diode,  $M_{E}$ ,

s) the emission constant for collector-base diode,  $M_{c}$ ,

must be determined at the beginning. The measurement techniques for obtaining these 19 transistor parameters are given in the related references(5),(7). Useful formulas and necessary explanations are to be given in detail in the following subsections.

2.3.1. Theoretical Explanations and Formulas for Switching Times

The time required to change the operating point of a junction transistor from the cut-off to the saturation, or vice-versa, is clearly of primary importance. It is the purpose of this section to show how switching-time is related to transistor parameters and circuit conditions. The switching time is easily calculated in terms of the normal active-region parameters of the transistor. Large-signal switching time includes the turn-on and turn-off times to be used as the model parameters.

#### a. Turn-on Time

When an input pulse (forward bias to emitter-base junction) is applied to a practical transistor switch, the transistor can not turn-on in zero time. Turn-on time is the time required for the collector current to change to 90 per cent of its saturated value. The turn-on time is made up of two parts.

#### (1). The Delay Time

The delay time is the time required for the collector current to change to its 10 per cent of its saturated value.

When the transistor is switched from the OFF condition to ON condition, the emitter-base junction voltage must change from an applied reverse-bias voltage, V<sub>BE</sub>(off), to the forward voltage, V<sub>BE</sub>, associated with the forward current being switched. The charge

associated with the emitter depletion layer and corresponding to a change in emitter-base voltage affects the response time of the transistor. In particular, emitter-base transition capacitance gives rise to an additional response time(8).

For determining the delay time,tdon,a linear model of the input side of the bipolar transistor is developed and it is shown in Figure(2.3).In this model, $R_B(t)$  and  $C_B(t)$  represent the base to emitter non-linear resistance and capacitance. $R_{BT}$  is the series combination of the base resistance, $R_B$ , and the base ohmic resistance, RBB.e<sub>s</sub>(t) is used for representing the input sqare-wave generator. <sup>V</sup>G is the base to emitter cut-in voltage.

FIGURE(2.3) Linear model developed for the input side of BJTs For the turn-on delay region, the model parameters can be expressed as

$$R_{B}(t) = R_{Bmax}$$

(2.3.1)

$$C_{B}(t) = C_{Bmin} \qquad (2.3.2)$$

$$R_{BT} = R_{B} + R_{BB} \qquad (2 \cdot 3 \cdot 3)$$

and

$$\mathbf{e}_{o}(\mathbf{t}) = \mathbf{E}_{ON} \tag{2.3.4}$$

where E ON is the positive value of the input square wave, R is Bmax

the maximum value of the base to emitter time-variant resistance and  $C_{\rm Bmin}$  is the minimum value of the base to emitter time-variant capacitance. The model shown in Figure (2.3) can be redrawn for the turn-on delay region and the base to emitter voltage can be

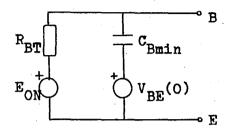

FIGURE(2.4) Equivalent circuit to be used in the calculation of tdon calculated by means of this new model. The expression of the base to emitter voltage can be written as

$$\mathbf{V}_{BE} = \left[\mathbf{E}_{ON} - \mathbf{V}_{BE}(O)\right] \cdot \left[1 - \exp(-DELT/(\mathbf{R}_{BT} \cdot \mathbf{C}_{Bmin}))\right] + \mathbf{V}_{BE}(O) \qquad (2.3.5)$$

The calculation of  $V_{\rm BE}$  must be repetead with the time intervals of DELT.Each time this equation is to be solved with the result of the previous calculation taken as the initial condition.The time which  $V_{\rm BE}$  is equal to the cut-in voltage,  $V_{\rm G}$ , is defined as the turn-on delay time, tdon.

### (2). The Rise Time

The rise time, tron, is the time required for the load current to increase from 10 per cent of the saturated load current,  $I_L$ , to 90 per cent of  $I_L$ . It can be saturated as (3), (4)

$$\operatorname{tron}_{=} \frac{1}{\bigcup_{N} \cdot (1 - \alpha_{N})} \left[ \frac{1 - 0.1(\operatorname{Ic/Ib}) \cdot (1 - \alpha_{N})/\alpha_{N}}{1 - 0.9(\operatorname{Ic/Ib}) \cdot (1 - \alpha_{N})/\alpha_{N}} \right]$$

(2.3.6)

where  $I_b$  is the base current after step is applied,  $I_c$  is the collector current at the edge of saturation region,  $\prec_N$  is the current gain, and  $\omega_N$  is the cut-off frequency.

Turn-on time clearly depends on the amount of drive, current gain, and frequency response of the transistor.

#### b. Turn-off Time

The turn-off transient from the saturation region to the cutoff region differs materially from the turn-on transient in that the junction transistor suffers from carrier storage.

The succession of events during the turn-off transient (at the end of pulse) may be described as follows:

The base current is reduced from a value corresponding to operation in the saturation region to zero, or possibly to a reverse emitter-junction current. The excess carrier density in the base layer decays until the minority carrier density in the base layer at the collector junction reaches nearly zero. During this initial stage of the turn-off transient, the collector junction is a low impedance and the collector current remains very nearly constant, at a value determined by the external circuit resistance. When the minority carrier density in the base layer at the collector approaches zero, the collector junction rapidly becomes a high impedance. The turn-off transient, after the collector junction has recovered, is controlled by the normal active region parameters. We see that for junction transistors the turn-off transient can be conveniently divided into two times.

#### (1). The Storage Time

Storage time is the time interval between the reduction of

base current to a zero, or reverse value, and the active response of the collector current. Storage time has been related to transistor parameters and circuit conditions from the fundamental considerations. The saturation delay time is given by (7), (9), (10)

$$\mathbf{T}_{S} = \overline{\mathsf{(sat.ln}} \frac{\mathbf{I}_{BF}^{+} \mathbf{I}_{BR}}{\mathbf{I}_{CF}^{/B} \mathbf{F}^{+} \mathbf{I}_{BR}}$$

(2.3.7)

where  $I_{BF}$  is the forward base current,  $I_{BR}$  is the reverse base current,  $I_{CF}$  is the forward collector current and (sat is the saturation delay time constant. (sat can be determined easily with a measurement technique which is explained in the reference (7).

### (2). Fall Time

The fall time is the time between the decrease of the load current,  $I_L$ , from 90 per cent of  $I_L$  (sat) to 10 per cent of  $I_L$  (sat) is

$$\operatorname{troff} = \frac{1}{\bigcup_{N^*} (1 - \prec_N)} \cdot \ln \left[ \frac{0.9I_{C1} - (\prec_N \cdot I_{BR}) / (1 - \prec_N)}{0.1I_{C1} - (\prec_N \cdot I_{BR}) / (1 - \prec_N)} \right] \quad (2.3.8)$$

where I c is the initial collector current.

As shown in Figure(2.2), all the switching times to be used in the analyses of switching circuits can be defined as

$$tl = tdon+tron \qquad (2.3.9)$$

$t_2 = TT/2 + Ts$  (2.3.10)

t3=t2+troff (2.3.11)

respectively.

## 2.3.2. Determination of Saturation Voltage and On and Off Impedances of Bipolar Transistors

The voltage drop between collector and emitter in the saturation region can be written as (7),(11)

$$\mathbf{v}_{CE} = \frac{\mathbf{k} \cdot \mathbf{T}}{q} \ln \frac{\boldsymbol{\swarrow}_{\mathbf{I}} (\mathbf{1} - \mathbf{I}_{C} \cdot (\mathbf{1} - \boldsymbol{\checkmark}_{N}) / \mathbf{I}_{B} \cdot \boldsymbol{\checkmark}_{N})}{\mathbf{1} + \mathbf{I}_{C} / \mathbf{I}_{B} \cdot (\mathbf{1} - \boldsymbol{\checkmark}_{I})} + \mathbf{I}_{E} \cdot \mathbf{R}_{EE} + \mathbf{I}_{C} \cdot \mathbf{R}_{CC} \quad (2.3.12)$$

As the model parameters, the value of  $V_{CES}$  can be obtained from Eq. (2.3.12) by neglecting the voltage drop on the emitter and collector ohmic resistances(3),(11)

$$V_{CES} = \frac{k \cdot T}{q} \cdot \ln \frac{\frac{1}{\sqrt{1}(1 - I_{C} \cdot (1 - \sqrt{N})/I_{B} \cdot \sqrt{N})}{1 + I_{C}/I_{B} \cdot (1 - \sqrt{1})}}{1 + I_{C}/I_{B} \cdot (1 - \sqrt{1})}$$

(2.3.13)

In this equation, since k.T/q = 0.0026 volt at room temperature this voltage can be as low as a few millivolts. As the collector current approaches  $\beta_{N} \cdot I_B$ , this voltage approaches infinity, and the transistor goes from the saturation region into the transient region.

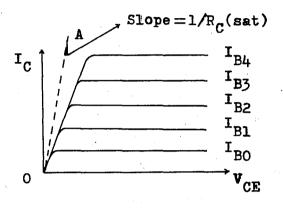

For determining the ON and OFF impedances, or Rmin, Rmax, Cmin, and Cmax, the A.C. impedance of the collector region in the closed condition, the emitter-base and collector-base junction ohmic leakage resistances, and the emitter-base and collector-base junction and diffusion capacitances must be determined.

The A.C. impedance in the collector circuit in the closed condition can be obtained from both of Eq. (2.3.12) and the related measurement technique together. It is given by (7)

$$R_{C}(Sat) = \frac{1}{Slope A} - (1+1/B_{F})R_{EE} - \frac{k \cdot T}{q} \left[ 1/(B_{F} \cdot I_{B} - I_{C}) + a \right] \quad (2 \cdot 3 \cdot 14)$$

where

$$a = 1/((1+B_R).I_B+I_C)$$

(2.3.15)

In this expression a correction is taken into account the effects of  $R_{EE}$  and the finite slope in the  $I_C$  versus  $V_{CE}$  characteristics

FIGURE(2.5) Typical  $I_{C}$  versus  $V_{CE}$  characteristics at constant  $I_{B}$

in the saturation region, Figure (2.5). Minimum equivalent output resistance or ON resistance can be expressed as (12)

$$R_{MIN} = R_{C}(sat) + R_{CC} + R_{EE} \qquad (2-3-16)$$

For determining the maximum equivalent output resistance we can use the related common emitter hybrid parameter, hoe,

R<sub>MAX</sub>= 1/hoe (2.3.17)

or if the base current were set to zero, the collector current which remains flowing through the transistor in the OFF state would be

$$\mathbf{I}_{\mathbf{C}} = \mathbf{I}_{\mathbf{C}0} / (\mathbf{1} - \boldsymbol{\alpha}_{\mathbf{N}}) = \mathbf{I}_{\mathbf{C}S} (\mathbf{1} - \boldsymbol{\alpha}_{\mathbf{N}} \cdot \boldsymbol{\alpha}_{\mathbf{I}}) / (\mathbf{1} - \boldsymbol{\alpha}_{\mathbf{N}})$$

(2.3.18)

and

$$R_{MAX} = V_{CC} (1 - \alpha_N) / I_{CS} \cdot (1 - \alpha_N \cdot \alpha_I)$$

(2.3.19)

There are two types of capacitances associated with the p-n junction. They are the junction and diffusion capacitances. The junction capacitance occurs as a consequence of the variation in the width of the depletion layer in a reverse -biased junction. An increase in reverse-bias causes majority carriers to move away from the junction and uncover fixed charges. This action causes a widening of the depletion region and because the charges moved from the depletion region must be pulled out of the diode terminals by the voltage source, the effect is that of a voltage variable capacitance.

The emitter-base and collector-base junction capacitances are expressed in the following expressions as (7),(13),(14)

$$c_{JE} = \frac{c_{JEO}}{(1 - V_{EB} / V_{ZE})^{Ne}}$$

(2.3.20)

and

$$C_{JC} = \frac{C_{JCO}}{(1 - V_{BC} / V_{ZC})^{NC}}$$

(2.3.21)

where  $V_{EB}$  and  $V_{BC}$  are the junction voltages (negative),  $V_{ZE}$  and  $V_{ZC}$  are contact potentials, and Ne and Nc are junction grading constants.

The diffusion capacitance exists across a forward-biased junction. The following expressions for the emitter-base diffusion capacitance  $C_{DE}$ , and the base-collector diffusion capacitance,  $C_{DC}$  can be written as(5), (7)

$$c_{DE} = \frac{q}{2.TI.M_{E}.k.T.Fn} \cdot \left[ I_{EF} + (I_{ES}/(1 - \alpha_{N}.\alpha_{I})) \right] \qquad (2.3.22)$$

and

$$C_{DC} = \frac{q}{2.TT.M_{C} \cdot k \cdot T \cdot Fi} \cdot \left[ I_{CF} - (I_{CS} / (1 - \mathcal{A}_{N} \cdot \mathcal{A}_{I})) \right]$$

(2.3.23)

$$\mathbf{I}_{EF} = (\mathbf{I}_{ES} / (1 - \boldsymbol{\prec}_{N^*} \boldsymbol{\prec}_{I}) \cdot \left[ \exp(q \cdot \boldsymbol{V}_{EB} / \boldsymbol{M}_{E^*} \mathbf{k} \cdot \mathbf{T}) - 1 \right]$$

(2.3.24)

$$\mathbf{I}_{CF} = (\mathbf{I}_{CS} / (1 - \prec_{N^*} \prec_{I}) \cdot \left[ \exp(q \cdot \mathbf{V}_{BC} / \mathbf{M}_{C^*} \mathbf{k} \cdot \mathbf{T}) - 1 \right]$$

(2.3.25)

$$\mathbf{Is} = \mathscr{A}_{\mathbf{I}} \cdot \mathbf{I}_{\mathbf{CS}} = \mathscr{A}_{\mathbf{N}} \cdot \mathbf{I}_{\mathbf{ES}}$$

(2.3.26)

and Fn and Fi are the normal and inverted-mode gain-bandwidth products of the intrinsic transistor.

In the cut-off region the equivalent output capacitance can be taken as a value which is equal to the value of the collector to base junction capacitance for  $V_{BC}^{=}-V_{Cav}$ . Because no current flows through the junction and we can not speak of the existence of the diffusion capacitance. Here the value of  $V_{Cav}$  is considered as the average value of the output voltage for an half period (15). The value of the output capacitance in the cut-off region is defined as the minimum equivalent output capacitance and it is given by

$$C_{\rm MIN} = \frac{C_{\rm JCO}}{(1+V_{\rm CAV}/V_{\rm ZC})^{\rm Nc}}$$

(2.3.27)

For the saturation region the equivalent output capacitance is taken as the additions of the values of the emitter-base junction for  $V_{BE} = V_{BE}(sat)$  and the collector-base diffusion capacitance for  $I_{CF} = I_{Cav}$ . The value of  $I_{Cav}$  is considered as the average value of the load current for an half period. As a result the value of the output equivalent capacitance is defined as the maximum equivalent output capacitance and it is equal to

$$C_{MAX} = \frac{C_{JEO}}{(1+V_{BE}(sat)/V_{ZE})^{NO}} + \frac{q}{2.TT Mc.k.T.Fi} \cdot \left[I_{Cav} - (I_{CS}/(1-\alpha_{N}, \alpha_{I}))\right]$$

(2.3.28)

### 2.4. General Review to VVMOS Transistors

Vertical V-groove Metal Oxide Semiconductor Field Effect Transistors (VVMOSTs) uniquely combine the advantages of the power bipolar transistors with those of the MOSFETs. The result is a high power, high-voltage, high-gain power transistor with no minoritycarrier storage time, no thermal runaway and a greatly inhibited secondary breakdown characteristic, all of which are contributing to the spectacular rise in the popularity of the VMOS power FET (16)

The vertical VMOS structure, like the power bipolar transistor, offers a large surface area for source metal and the entre backside of the chip for the drain. This is of great importance as it allows maximum current carrying capacity unavailable to a nonvertical structure.

Operationally, VVMOST is unique among power transistors. Channel conduction is proportional to gate voltage, not to any sort of injection current, typical of the bipolar transistor. Whatever input current that does exist beyond that attributed to leakage may be identified as the charging current necessary to overcome the input capacitance in very high-speed switching situations. Because the stea state gate current negligible, the familiar parameter, beta, is of litt importance. Consequently, VMOS exhibits a high input resistance that makes it ideal for many logic control applications.

In the consideration of VVMOS transistor as a switch the calculations must be made for the five regions, separately. These regions can be defined as the turn-on delay region, the pinch-off region (off to on), the resistive region, the pinch-off region (on to off), and the cut-off region, respectively. For the turn-on delay and cut-off regions  $V_{GS}$  is below threshold,  $(V_{GS} < V_T)$ , and the VVMOST is

OFF.In the pinch-off region as  $V_{GS}$  exceeds  $V_T$  drain current begins to increase until  $V_{DS}$  saturation is reached, or  $V_{GS} - V_T \ge V_{DS}$ . In the resistive region  $V_{DS}$  is saturated and no further change in  $I_D$  or  $V_{DS}$  occurs.

Useful explanations and the comparison of VVMOS transistors with the other transistors are given in Appendix B.A time-variant linear large-signal model for the VVMOS transistors is to be developed in the following section and the related model parameters and useful formulas according to them are given in section(2.6).

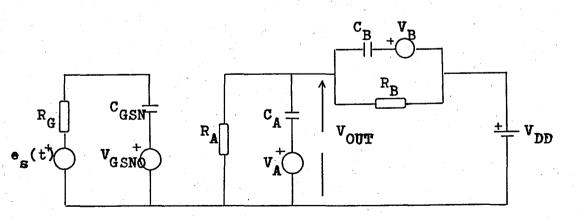

2.5. A Time-Variant Linear Modeling of VVMOS Transistors for Switching Circuits

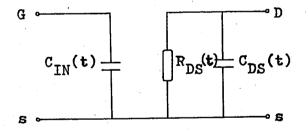

A time-variant linear large-signal model for the VVMOS transistor is developed in this section. This model, basically, is similar to the

FIGURE(2.6) A time-variant linear large-signal model for VVMOSTs

proposed new BJT model. This model includes an equivalent input capacitance between the gate and source for the input side and the parallel combination of the equivalent output resistance and capacitance for the output side. The complete model is shown in Figure (2.6).

The input side of this model consists of a FET equivalent timevariant input capacitance, C<sub>IN</sub>, only, that's why the D.C. input resistance of a VVMOS power FET is in excess of 10<sup>12</sup> ohms.

The output side includes a time-variant drain to source resistance and capacitance.For the turn-on delay and cut-off regions the equivalent output resistance,or drain to source resistance,is considered as a constant value which is equal to the maximum drain to source resistance,R<sub>DMAX</sub>. In the pinch-off and resistive regions this resistance is a function of the input voltage.The equivalent output capacitance,or drain to source capacitance,is a function of the output voltage for all regions in the VVMOS transistors.

For using this model in the analysis of the switching circuits, the VVMOS transistor model parameters must be determined at the beginning.Beyond the structural parameters, all the parameters can be obtained from the related DATA SHEETs.The structural parameters and related model parameters are explained in detail in the following section.

### 2.6. Description of VVMOST Model Parameters

For the VVMOST model to be used in the switching applications a careful analysis of the VVMOST switching parameters is required. The related switching parameters are the ON-resistance,OFF-resistance, PINCH-OFF resistance and the device capacitances.Necessary explanations for obtaining the switching times are given at the end of this section.

### 2.6.1. ON-Resistance

At low drain voltage and large-currents, the N layer acts as a simple resistance in series with the drain of a conventional MOST. The resistance of the N layer is (17)

$$R_{\bar{N}} = \frac{2 \cdot g_{\bar{n}}}{\Pi \cdot z} \cdot \ln \frac{4 \cdot d}{\Pi \cdot a}$$

(2.6.1)

where gris the N layer resistivity, z is the total channel width

(2.6.5)

of the device, d is the thickness of the N layer, and a is the half of the groove opening at the P-N interface.

The total ON-resistance of the VVMOST is made up of the series combination of the channel resistance  $R_{c}$ , the N drift layer resistance  $R_{N}^{-}$ , and the N<sup>+</sup> source and drain resistances as well as the metallization resistance. The channel and N region resistances are the dominant resistances to the ON resistance,  $R_{DS}^{-}$  (ON), which can be expressed as (17),(18)

$$R_{DS}(ON) = R_{C} + R_{N}^{-}$$

(2.6.2)

$$= 1/\beta \cdot (V_{\rm GS} - V_{\rm T})^{-1} + R_{\rm N}^{-}$$

(2.6.3)

where

$$\vec{\beta} = \frac{L}{\mathcal{M} \cdot C_0 \cdot z}$$

(2.6.4)

is a constant, L is the channel length in the VVMOS device,  $\mu$  is the surface channel mobility, C<sub>0</sub> is the effective gate oxide capacitance per unit area.

2.6.2. OFF-Resistance

For the turn-on delay and the cut-off regions the maximum drain to source resistance can be calculated by using the related transistor parameters, the zero gate voltage drain current, I<sub>DSS</sub>, and the maximum drain source voltage, V<sub>DSMAX</sub>. The expression for the maximum drain to source resistance is given by

$$R_{DSMAX} = V_{DSMAX} / I_{DSS}$$

2.6.3. PINCH-OFF Resistance

In the pinch-off regions, an internal transconductance that

initially rises with  $V_{GS}$  but eventually saturates at a constant maximum value can be written as

$$g_{mi} = 1/V_{DS} \cdot \beta \cdot (V_{GS} - V_T)^2$$

(2.6.6)

The presence of  $R_N^-$  and  $R_S^-$  results in the external pinch-off transconductance,  $g_m^-$  being reduced from its internal value. The drain to source resistance for this region can be written by using the external transconductance as

$$R_{DS} = \frac{V_{DS}}{\beta \cdot (V_{GS} - V_{T})^{2}} + R_{N}^{-}$$

(2.6.7)

2.6.4. Device Capacitances

Several capacitances affect the high-frequency and switching characteristics of the VVMOST.Figure(2.7) shows these capacitances schematically on the cross section of the VVMOST. $C_{GS}$  and  $C_{GD}$  are MOS capacitances and  $C_{DS}$  is a junction capacitance.

An approximate expression for the maximum input capacitance of the VVMOST (neglecting overlap metallization on the planar nongrooved regions of the device and space-charge capacitance under gate oxide) is (17)

$$C_{TW} \cong C_0.(1.23.Y_0.0.707).z$$

(2.6.8)

$$\cong 0.86C_0 Y_{\mathbf{g}} \mathbf{z} \tag{2.6.9}$$

where  $Y_{G}$  is the length of the groove opening. To minimize the input capacitance  $Y_{G}$  must be kept as small as possible.

More accurate expressions for the individual capacitances including overlap and space-charge capacitances can be obtained from the geometry of the device. The gate to source capacitance is made up of three components: a capacitance associated with gate overlap over the N source on the surface, and a gate to bulk capacitance component. The gate to source capacitance can be expressed as (17)

$$C_{GS} = 1.23 \cdot C_0 \cdot X_N \cdot z + C_{on} \cdot Y_{ov} \cdot z + C_{om} \cdot L \cdot z$$

(2.6.10)

where C is the capacitance per unit area of the field oxide over

the  $N^+$ source,  $C_{om}$  is the voltage variable MOS capacitance of the channel region,  $Y_{ov}$  is the gate metallization overlap over the field oxide, and  $X_N$  is the source diffusion depth. In order to reduce  $C_{GS}$ , the overlap capacitance component must be minimized.

The gate to drain capacitance at zero drain voltage is given by (17)

$$C_{qp} = 1.23 \cdot C_0 (0.707 \cdot Y_g - X_p) \cdot z$$

(2.6.11)

Since this capacitance is directly over the accumulated N region,

little variation in  $C_{\rm GD}$  with gate voltage is expected.However,at higher drain voltages the increasing space-charge region in the N<sup>-</sup>layer causes a reduction in this capacitance.In order to minimize  $C_{\rm GD}$ , the effective penetration of the groove into the N layer must be minimized.

The drain to source capacitance is given by (17)

$$C_{DS} = C_{d} \cdot (A - Za)$$

(2.6.12)

where  $C_d$  is the voltage variable space-charge region capacitance per unit area associated with the P-N junction, A is the total area of the device within groove, and Za is the area occupied by the grooves at the P-N interface. To minimize  $C_{DS}$ ,  $C_d$  must be made as small as possible by using a high resistivity N region (17). The expression of  $C_d$  is given by

$$C_{d} = C_{DSO} \cdot (1 + V_{DS} / \phi)^{-H}$$

(2.6.13)

where  $C_{DSO}$  is the junction capacitance at  $V_{DS} = 0, H$  is the grading coefficient  $0.3 < H < 0.5, \beta$  is the junction potential (18).

The VVMOST equivalent input capacitance,  $C_{IN}$ , is a function of  $V_{GS}$  and  $V_{GD}$ . In the switching applications, it changes during transition from the ON state to the OFF state or vice versa. Typically the capacity characteristics specified on the related data sheet are given for a fixed bias condition. This may present a problem in trying to estimate  $C_{IN}$ .

Driving VVMOS from logic requires an appreciation of the gate drive power needed to actuate, or turn-on, the VVMOS power transistor. First, the driver must be able to deliver sufficient current during the transition (from OFF to ON) to adequately charge the input capacitor in the desired time. As the driving voltage ramps upward

## POČAZICI ÜNIVERSITESI KÜTÜPHANESI

another phenomenon occurs called MILLER EFFECT.Once the threshold voltage of the VVMOS transistor is passed it begins to draw increasingly heavier drain current.As the drain current rises rapidly to saturation.Concurrent with this rise in transconductance is a proportional rise in gain and once low feedback capacitance now swells to enormous proportions appearing as an addition to the input capacitance

$$C_{IN} = C_{ISS} + (1 - Av) \cdot C_{GD}$$

(2.6.14)

where  $C_{ISS}$  is the common-source input capacitance,  $C_{GD}$  is the gatedrain capacity, and Av is the voltage gain.

The input capacitance,  $C_{IN}$ , in the cut-off region is fairly constant. It corresponds to the common-source input capacitance,  $C_{ISS}$ , and is approximately equal to

$$c_{IN1} = c_{ISS} + c_{GD}$$

(2.6.15)

In the pinch-off region,  $C_{IN}$  increases because the VVMOST begins to turn-on and  $V_{DS}$  begins to change, thus increasing the rate of change of  $V_{GD}$ . The MILLER EFFECT on  $C_{GD}$  causes  $C_{IN}$  to increase. This effect stops after the device is fully ON and  $V_{DS}$  ceases to change. The approximate capacitance in this region is (16)

$$C_{IN2} = C_{ISS} + (1 - Av) \cdot C_{GD}$$

(2.6.16)

where Av is equal to

$$Av = \frac{\triangle V_{DS}}{\triangle V_{GS}} = \frac{V_{DS}(ON) - V_{DS}(OFF)}{V_{DS}(ON)}$$

(2.6.17)

Substituting Eq.(2.6.17) into Eq.(2.6.16), CIN2 can be rewritten as

$$c_{IN2} \approx c_{ISS} - \frac{v_{DS}(ON) - v_{DS}(OFF)}{v_{DS}(ON)}$$

(2.6.18)

In the resistive region  $V_{\rm DS}$  is saturated at a low value and is no longer changing. The VVMOST channel is ON and  $C_{\rm IN}$  is higher than it is in the cut-off region, but not as high as in the pinchoff region. No MILLER occurring and it also corresponds  $C_{\rm ISS}$ , and it is approximately equal to (16)

$$C_{IN3} = C_{ISS} + C_{GD}$$

(2.6.19)

As a result  $C_{IN1}$  and  $C_{IN3}$  corresponds to  $C_{ISS}$  and are approximately equal to the addition of the gate to source and gate to drain capacitances. They differ in magnitude because of the differences in  $V_{DG}$  in the turn-on delay and the resistive regions.

There is a large change in the bias on  $C_{GD}$ . In the turn-on delay or cut-off regions the drain area under the gate is depleted of carriers, thus  $C_{GD}$  is greatly reduced. In the resistive region the drain region under the gate is flooded with carriers because the device is ON, that is much greater.

### 2.6.5. Switching Times

By using the input side of the VVMOST model the related switching times can be calculated.

A turn-on delay,tdon,occurs in the turn-on delay region while the gate is being charged up to threshold voltage, $V_T$ .Then turn-on of the VVMOST channel starts and is completed when  $V_{DS}$  saturation occurs at  $V_{GS} = V_T + V_{DS}$  (ON).This turn-on time is defined as the rise time,tr.

Overdrive is occurring in the resistive region. The excess charge

in the resistive region causes a turn-off delay,tdoff.This delay occurs until  $V_{GS}$  drops to the value of  $V_T + V_{DS}(ON)$ .The turn-on and turn-off delays could be decreased by pre-biasing the gate to a  $V_{GS}$  just below  $V_T$  and by avoiding overdriving into the resistive region.This,however,would decrease the switching circuit noisemargin and would require closer control of the gate drive voltage and the threshold voltage of the VVMOST.

For the value of  $V_{GS}$  just below  $V_T + V_{DS}(ON), V_{DS}$  begins to come out of saturation, and the VVMOST will be completely OFF when  $V_{GS}$ drops below the threshold voltage,  $V_T$ . The time which is passed at this state is defined as the fall time, tf.

Finally ON and OFF times can be calculated by using these definitions, respectively

$$T_{ON} = (TT/2-tr-tdon)+tdoff \qquad (2.6.20)$$

and

$$T_{OFF} = tdon_{+}(TT/2 - tdoff - tf)$$

(2.6.21)

Table(2.1) shows the approximate quantities to use in the equation for determining the switching times (16)

TABLE 2.1 Pertinent VVMOST switching relationships

| Interval       | Symbol | Gate Voltage Change                     | Capacitance                                                             |

|----------------|--------|-----------------------------------------|-------------------------------------------------------------------------|

| Turn-on Delay  | tdon   | V <sub>T</sub> -V <sub>GS</sub> (OFF)   |                                                                         |

| Rise Time      | tr     | V <sub>GSON1</sub> -V <sub>T</sub>      | $c_{1SS}^{c} \rightarrow v_{DS}^{c} c_{RSS}^{c}$                        |

| Turn-Off Delay | tdoff  | V <sub>GS</sub> (ON)-V <sub>GSON2</sub> |                                                                         |

| Fall Time      | tſ     | V <sub>GSON2</sub> -V <sub>T</sub>      | $c_{ISS}^{C} + \frac{\triangle v_{DS}}{\triangle v_{GS}} \cdot c_{RSS}$ |

Capacitance values used are the average values as  $V_{GS}$  varies over the ranges shown for the time interval of interest.Appropriate  $V_{DS}$  values must also be used to determine the capacitance.Key  $V_{GS}$ points are

| V <sub>GS</sub> (OFF) | :                                                                  | OFF state gate voltage prior to turn-on                          |  |  |

|-----------------------|--------------------------------------------------------------------|------------------------------------------------------------------|--|--|

| V <sub>T</sub>        | :                                                                  | Threshold gate voltage                                           |  |  |

| V <sub>GSON1</sub>    | : V <sub>GS</sub> corresponding to the peak value of drain current |                                                                  |  |  |

|                       |                                                                    | for capacitive or resistive loads or the value of                |  |  |

| · ·                   |                                                                    | drain current when the drain voltage enters the ohmic            |  |  |

|                       |                                                                    | region for inductive loads.                                      |  |  |

| V <sub>GS</sub> (ON)  | :                                                                  | On-state gate voltage prior to turn-off                          |  |  |

| V <sub>gson2</sub>    | :                                                                  | $v_{\rm GS}$ corresponding to the value of drain current flowing |  |  |

|                       |                                                                    |                                                                  |  |  |

2.7. General Review to VDMOS Transistors

prior to turn-off

Recent advances in processing technology and the introduction of new device structures have allowed dramatic improvements in the current,voltage, and power-handling capabilities of MOSFET devices. The impetus for much of this work is the faster switching ability of majority-carrier devices which do not suffer from the minoritycarrier charge-storage problems inherent to bipolar transistors. A second primary motivation is the negative temperature coefficient of carrier mobility which greatly decreases problems of thermal runaway, secondary breakdown, and current hogging, all of which play important roles in the design and application of power bipolar transistors. The recent commercial availability of a variety of discrete-power MOS transistors has made possible a host of new applications for these devices including switching power supplies, linear audio and high-frequency amplifiers, and power control devices.

Two main changes in the basic MOSFET structure have been responsible for these advances. The first of these is the wide-spread use of double-diffusion techniques to achieve very short channels, although not all of the new power MOSFET's use double-diffusion. Sequential diffusion of p- and n-type impurities in a manner analogous to bipolar transistor fabrication processes yields channel lengths comparable in dimension to bipolar basewidths. Historically, this process has been difficult to control because the threshold voltage of the device is determined by diffused impurity profiles rather than by bulk substrate doping levels. The wide-spread use of ion implantation has, however, largely eliminated this difficulty.

The second major change in the basic MOSFET structure has been the incorporation of a lightly doped (usually n<sup>-</sup>) drift region between the channel and the n<sup>+</sup> drain contact. This region largely supports the applied drain potential because its doping level is chosen to be much smaller than the p-channel region. These new structures, therefore, effectively separate the active portion of the device (channel) which determines device gain, from the region of the device which supports the applied voltage (drift region). This separation is exactly analogous to modern bipolar transistors in which a lightly doped collector region largely supports the applied potential and a narrow, more heavily doped base region largely determines device gain.