### 3.125Gbps FIR EQUALIZER IMPLEMENTATION IN 65nm CMOS TECHNOLOGY

by

Hande AKIN KURNAZ

B.S., Microelectronics Engineering, Sabancı University, 2004

Submitted to the Institute for Graduate Studies in Science and Engineering in partial fulfillment of the requirements for the degree of Master of Science

Graduate Program in Electrics-Electronics Engineering Boğaziçi University 2008

## 3.125Gbps FIR EQUALIZER IMPLEMENTATION IN 65nm CMOS TECHNOLOGY

## APPROVED BY:

| Prof. Günhan Dündar       |  |

|---------------------------|--|

| (Thesis Supervisor)       |  |

| Prof. Cem Ersoy           |  |

|                           |  |

| Assist. Prof. Şenol Mutlu |  |

DATE OF APPROVAL: 20.06.2008

### ACKNOWLEDGEMENTS

It is my responsibility to thank to all my professors in my education, who provided me with the background to make this work possible. Special thanks to my thesis supervisor, Prof. Günhan Dündar, for his patience, endless support and reassurance in dead ends.

Thanks to my managers and colleagues in STMicroelectronics, Istanbul Design Center, for supporting my education during my professional life.

I would like to thank to my family in advance for their love, understanding and support during this work. I cannot imagine how difficult it would be to manage all these without them.

### ABSTRACT

# 3.125Gbps FIR EQUALIZER IMPLEMENTATION IN 65nm CMOS TECHNOLOGY

This thesis describes channel degradation in a basic telecommunication system with its sources (crosstalk and metallic channel loss) and results (inter-symbol interference). Compensation of this channel degradation via methodology called equalization is focused on. Adaptive equalization techniques such as zero forcing, least mean squares (LMS), recursive least squares (RLS) and constant modulus algorithm (CMA) are theoretically explained and LMS and RLS are supported with regarding MATLAB Simulink simulations using 30inch PCB trace model as the channel model. Comparison of adaptation algorithms, equalization cost functions and tap spacing of tapped delay line in FIR equalizer in Simulink are also held for this thesis. Coefficients obtained from Simulink environment are used to verify performance of FIR equalizer designed in STMicroelectronics CMOS065 (65nm) technology for 3.125Gbps data rate. Building blocks of FIR equalizer are analyzed in detail and design limitations are summarized. Simulations showed that closed eye at the receiver after 30inch PCB channel, can be cleaned up to data eve with 28ps jitter by means of 4-tap FIR equalizer with T/8 tap spacing operating at 1.2V power supply, 3.125Gbps data rate and at the expense of only 13mA of current consumption.

## ÖZET

# 3.125Gbps HIZINDA 65nm CMOS TEKNOLOJİSİNDE FIR EŞİTLEYİCİ UYGULAMASI

Bu tez telekominikasyon sistemlerinde kanala bağlı bilgi bozulmasının sebeplerini (çapraz karışma ve metalik kanal kayıpları) ve sonuçlarını (simgeler arası karışma-ISI) açıklamaktadır. Tezin devamında bu bozulmanın eşitleyici sayesinde telafi edilmesi üzerinde yoğunlaşılmıştır. Telafi metodunun adaptif olanları (RLS, LMS, CMA, ZF) teorik olarak incelendikten sonra, MATLAB Simulink adındaki simulasyon ortamında simulasyonlarla desteklenmiştir. Simulasyonlar esnasında 30inç PCB kanal modeli Adaptasyon algoritmaları, eşitleyicilerin maliyet fonksiyonları, çıkma kullanılmıştır. aralıklarının etkisi karşılaştırmalı olarak incelenmiştir. Simulink ortamından elde edilen katsayılar sonlu dürtü yanıtı (FIR) eşitleyicinin transistor seviyesindeki tasarımın performansını, STMicroelectronics CMOS065 (65nm) teknolojisini kullanarak, 3.125Gbps hızında verifikasyonu için kullanılmıştır. FIR eşitleyicinin ana blokları detaylı olarak incelenmiş ve uygulama limitasyonları özetlenmiştir. Simulasyonlar kanal modelinden sonraki kapalı göz biçimindeki iletilmiş bilginin, eşitleyici kullanıldıktan sonra 28ps et kalınlığına kadar temizlendiğini göstermektedir. Bunun için T/8 aralıklı gecikmelerden oluşan 4-çıkmalı sonlu dürtü yanıtı eşitleyici, 1.2V güç kaynağı kullanarak, 3.125Gbps veri hızında ve sadece 13mA akım harcayarak gerçeklenmiştir.

## **TABLE OF CONTENTS**

| ACKNOWLEDGEMENTS                        | ii                                    |

|-----------------------------------------|---------------------------------------|

| ABSTRACT                                | iv                                    |

| ÖZET                                    |                                       |

| LIST OF FIGURES                         | vii                                   |

| LIST OF TABLES                          |                                       |

| LIST OF SYMBOLS/ABBREVIATIONS           | xii                                   |

| 1. INTRODUCTION                         |                                       |

| 1.1. Equalization for High Speed Comm   | unication                             |

| 1.2. Literature Survey                  |                                       |

| 1.3. Thesis Organization                |                                       |

| 2. COMMUNICATION SYSTEMS                |                                       |

| 2.1. Channel Non-idealities             |                                       |

| 2.1.1. Crosstalk                        |                                       |

| 2.1.2. Metallic Channel Loss            |                                       |

| 2.2. Channel Equalization               |                                       |

| 2.2.1. Transmitter Equalizer (Pre-E     | mphasis) 22                           |

| 2.2.2. Receiver Equalizer               |                                       |

| 2.3. Receiver Equalization Using FIR Fi | lters                                 |

| 2.3.1. Communication System Sum         | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 |

| 2.3.2. Equalization Using FIR Filte     | rs 31                                 |

| 3. ADAPTIVE EQUALIZATION                |                                       |

| 3.1. Zero Forcing Algorithm             |                                       |

| 3.2. LMS Algorithm                      |                                       |

| 3.2.1. Steepest Descent Algorithm       |                                       |

| 3.3. RLS Algorithm                      |                                       |

| 3.4. Constant Modulus Algorithm (CMA    | A) 55                                 |

| 4. MATLAB REALIZATION                   |                                       |

| 4.1. Comparison of Adaptation Algorith  | ms                                    |

| 4.1.1. Subblocks                        |                                       |

| 4.1.2. Comparative Simulations          |                                       |

| 4.2. Top Level Simulation               |                                       |

| 5. | ANALOG CMOS IMPLEMENTATION OF FIR EQUALIZER | 70  |

|----|---------------------------------------------|-----|

|    | 5.1. Block Level Design                     | 71  |

|    | 5.1.1. MDAC Design                          | 71  |

|    | 5.1.2. Common Mode Feedback                 | 77  |

|    | 5.1.3. Tap Delay Cell                       | 80  |

|    | 5.1.4. ADC (Analog to Digital Converter)    | 87  |

|    | 5.1.5. Limiting Amplifier                   | 96  |

|    | 5.2. Top Level Simulations                  | 101 |

| 6. | CONCLUSION AND FUTURE WORK                  | 105 |

| RE | FERENCES                                    | 107 |

|    |                                             |     |

## LIST OF FIGURES

| Figure 1.1.  | Block diagram of a typical high-speed digital data transceiver                                                             | 1  |

|--------------|----------------------------------------------------------------------------------------------------------------------------|----|

| Figure 1.2.  | Effect of channel equalization                                                                                             | 2  |

| Figure 2.1.  | Basic communication system [35]                                                                                            | 7  |

| Figure 2.2.  | Backplane channel characteristics [21]                                                                                     | 10 |

| Figure 2.3.  | Near End & Far End crosstalk theory [24]                                                                                   | 11 |

| Figure 2.4.  | Near End & Far End crosstalk representation in a communication system [23]                                                 | 12 |

| Figure 2.5.  | Current density J as a function of frequency. Current spread out towards the conductor surface as the frequency rises [25] | 13 |

| Figure 2.6.  | Measured S21 parameter for a PCB trace [23]                                                                                | 15 |

| Figure 2.7.  | Illustration of ISI-the transmitted signal (top) and the received signal (bottom) through a band limited channel [23]      | 16 |

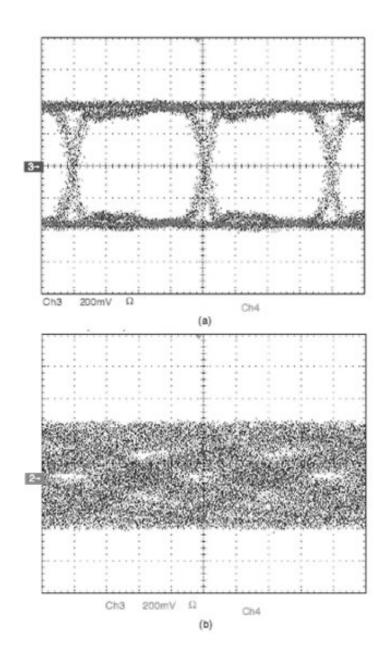

| Figure 2.8.  | Eye diagram of (a) the transmitted signal and (b) the received signal [23]                                                 | 17 |

| Figure 2.9.  | Communication channel with transmitter pulse modulation and received filter [23]                                           | 18 |

| Figure 2.10. | Illustration of ISI [23]                                                                                                   | 19 |

| Figure 2.11. | Classification of equalization techniques                                                                                  | 21 |

| Figure 2.12. | Figure 2.12. Pre-emphasis with FIR filter                                                    |    |  |  |

|--------------|----------------------------------------------------------------------------------------------|----|--|--|

| Figure 2.13. | Block diagram of de-emphasis equalizer [23]                                                  | 23 |  |  |

| Figure 2.14. | Illustration of de-emphasis equalizer functionality                                          | 23 |  |  |

| Figure 2.15. | Passive T-bridged equalizer [23]                                                             | 25 |  |  |

| Figure 2.16. | Split-path equalizer example [23]                                                            | 26 |  |  |

| Figure 2.17. | Wideband split-path amplifier (a) without feedback loop and (b) variable gain amplifier [23] | 26 |  |  |

| Figure 2.18. | Source degeneration transconductor filter [23]                                               | 27 |  |  |

| Figure 2.19. | Example channel filter with top plate S/H cells [33]                                         | 28 |  |  |

| Figure 2.20. | Basic communication system revisited                                                         | 30 |  |  |

| Figure 2.21. | Equalizer types, structures, and algorithms [36]                                             | 32 |  |  |

| Figure 2.22. | Symbol spaced equalization using FIR filter                                                  | 33 |  |  |

| Figure 2.23. | Fractionally spaced equalization using FIR filter [38]                                       | 35 |  |  |

| Figure 2.24. | Fractionally spaced equalization using FIR filter                                            | 35 |  |  |

| Figure 3.1.  | Transversal wiener filter representation                                                     | 48 |  |  |

| Figure 4.1.  | Matlab simulation summary (3 comparison sets are represented as 3 different array colors)    | 56 |  |  |

| Figure 4.2.  | Basic communication system                                                                   | 57 |  |  |

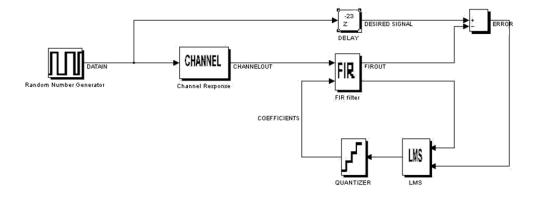

| Figure 4.3. Simulation setup for symbol spaced equalizer under mean square err criterion with LMS adaptation algorithm |                                                                                                              |    |  |  |

|------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|----|--|--|

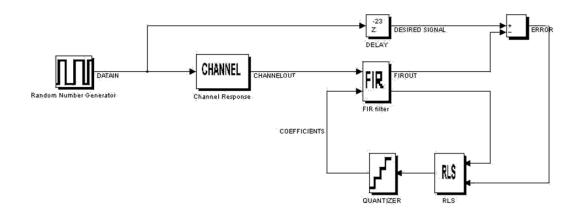

| Figure 4.4.                                                                                                            | Simulation setup for symbol spaced equalizer under mean square error criterion with RLS adaptation algorithm | 58 |  |  |

| Figure 4.5.                                                                                                            | Data source – Random number generator                                                                        | 59 |  |  |

| Figure 4.6.                                                                                                            | FIR equalizer with 4 taps                                                                                    | 60 |  |  |

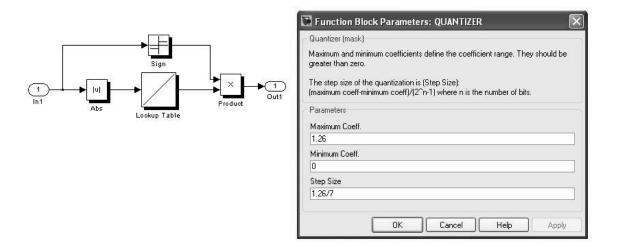

| Figure 4.7.                                                                                                            | Quantization block for FIR filter coefficients                                                               | 61 |  |  |

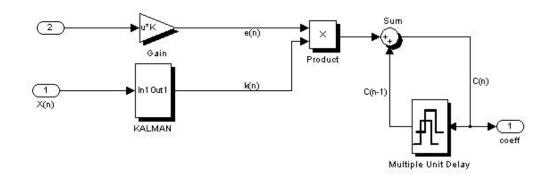

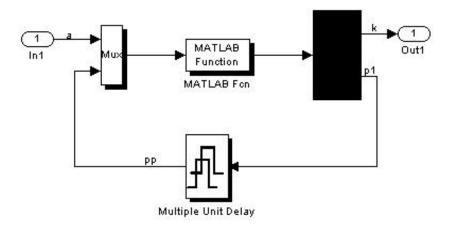

| Figure 4.8.                                                                                                            | RLS adaptation algorithm block                                                                               | 62 |  |  |

| Figure 4.9.                                                                                                            | Kalman filter matlab code                                                                                    | 63 |  |  |

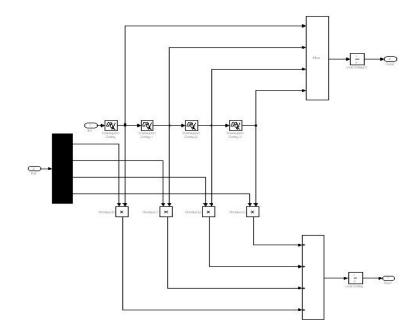

| Figure 4.10.                                                                                                           | Kalman filter block top level                                                                                | 63 |  |  |

| Figure 4.11.                                                                                                           | RLS adaptation algorithm block                                                                               | 64 |  |  |

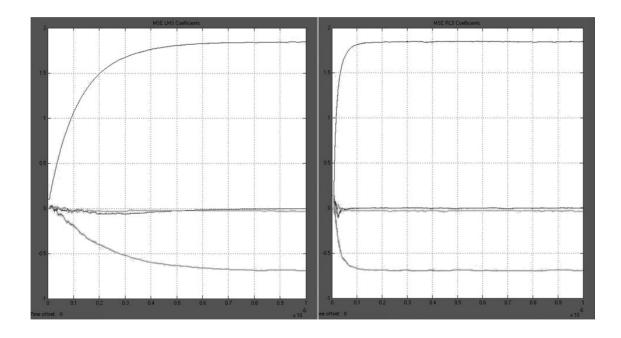

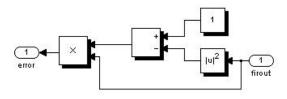

| Figure 4.12.                                                                                                           | Coefficient convergence of LMS (left plot) and RLS (right plot)                                              | 64 |  |  |

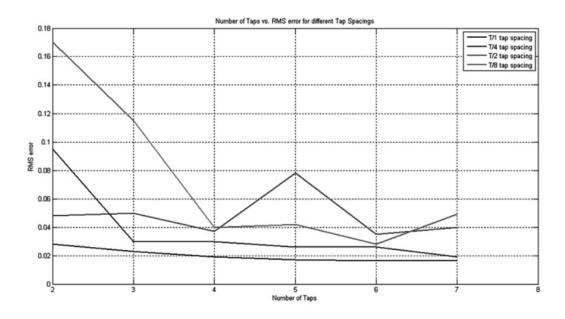

| Figure 4.13.                                                                                                           | RMS values of error versus tap spacing & number of taps                                                      | 66 |  |  |

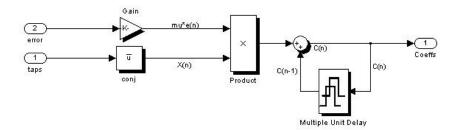

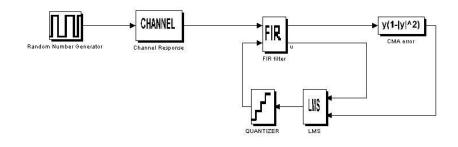

| Figure 4.14.                                                                                                           | Constant modulus algorithm (CMA) simulation setup                                                            | 67 |  |  |

| Figure 4.15.                                                                                                           | Error implementation in CMA                                                                                  | 67 |  |  |

| Figure 4.16.                                                                                                           | MSE vs. CM                                                                                                   | 67 |  |  |

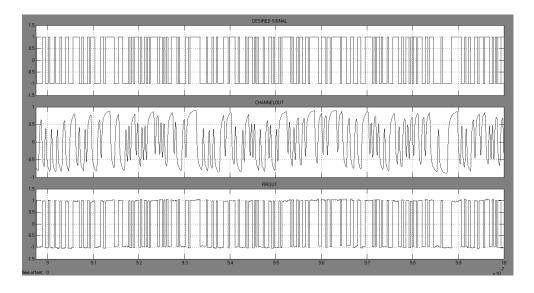

| Figure 4.17.                                                                                                           | 4 taps with T/8 tap FIR equalizer MATLAB simulation output                                                   | 69 |  |  |

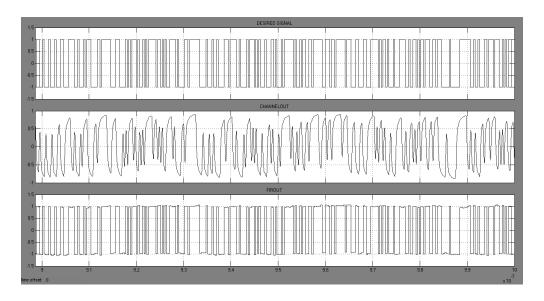

| Figure 4.18.                                                                                                           | 2 taps with T/4 tap FIR equalizer MATLAB simulation output                                                   | 69 |  |  |

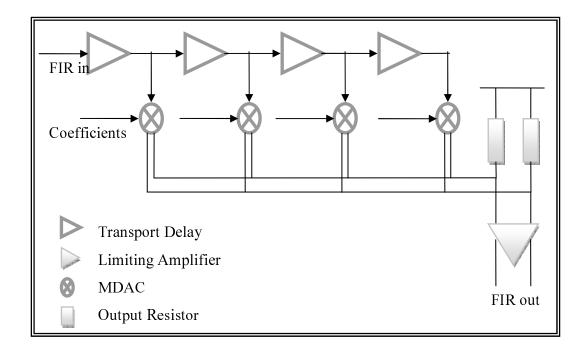

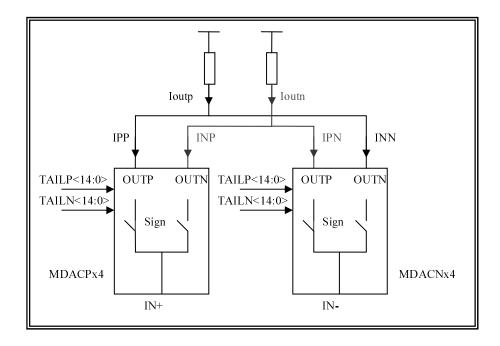

| Figure 5.1.  | Top level analog implementation                                                                                | 70 |

|--------------|----------------------------------------------------------------------------------------------------------------|----|

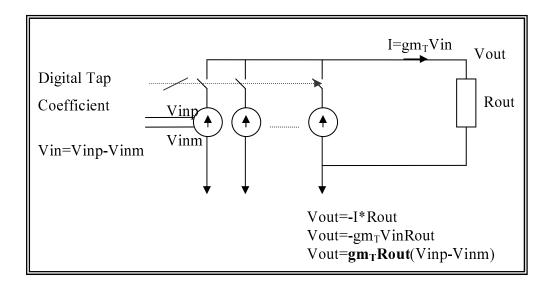

| Figure 5.2.  | MDAC theoretical representation                                                                                | 71 |

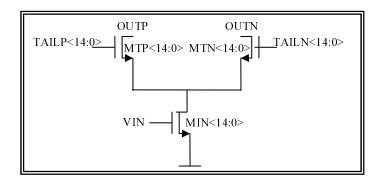

| Figure 5.3.  | Top level MDAC cell for 4 taps                                                                                 | 73 |

| Figure 5.4   | One MDAC unit cell                                                                                             | 73 |

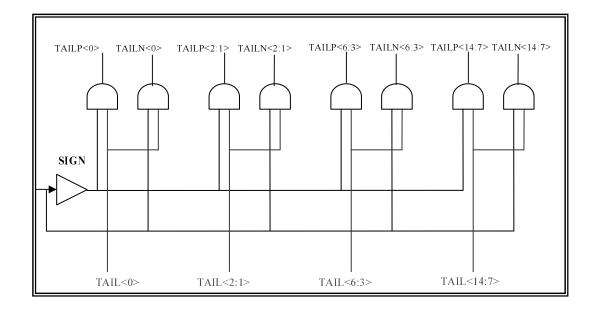

| Figure 5.5.  | Input sign multiplexer for MDAC                                                                                | 74 |

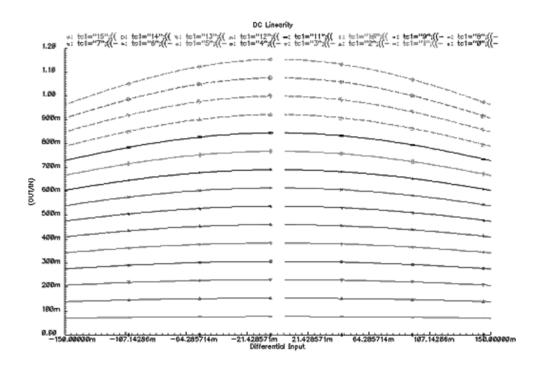

| Figure 5.6.  | One MDAC delay cell gain for different control bits over ±150mV input range                                    | 75 |

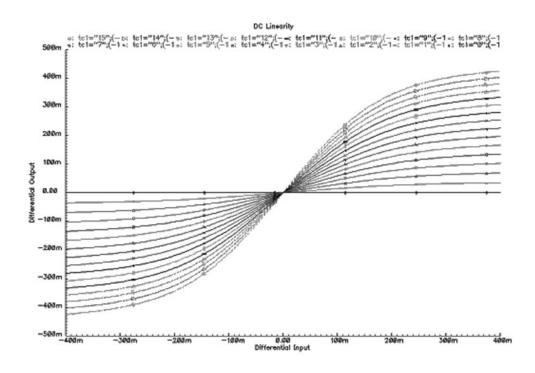

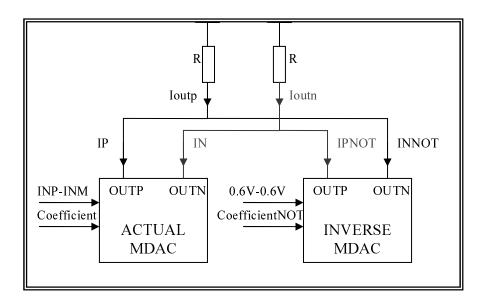

| Figure 5.7.  | Input-output linearity with the different control bits over $\pm 400 \text{mV}$ input range                    | 75 |

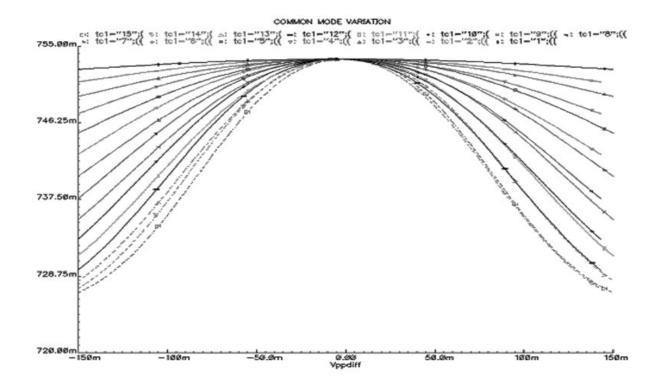

| Figure 5.8.  | Output common mode variation with the different control selections over the input range of $\pm 400 \text{mV}$ | 76 |

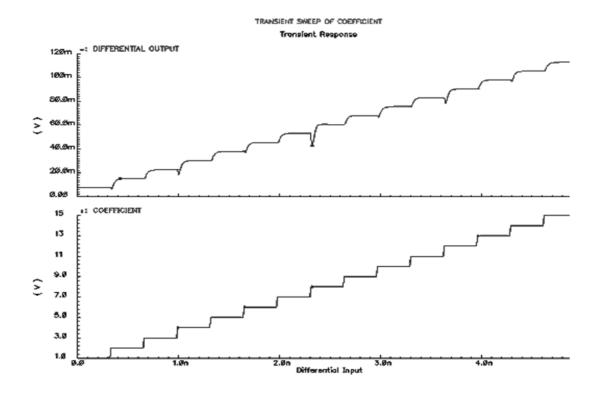

| Figure 5.9.  | MDAC delay cell differential output change with the changing coeffici-<br>ent in transient                     | 77 |

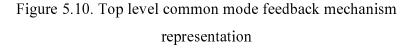

| Figure 5.10. | Top level common mode feedback mechanism representation                                                        | 78 |

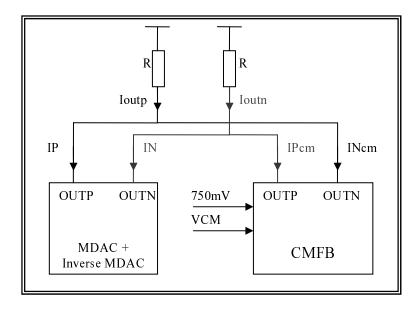

| Figure 5.11. | Common mode level up shifter mechanism                                                                         | 79 |

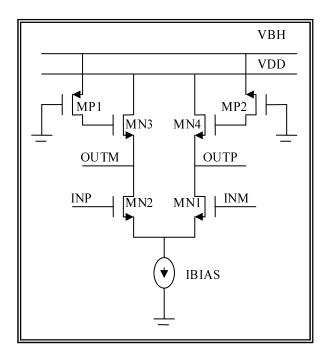

| Figure 5.12. | Common mode feedback mechanism                                                                                 | 80 |

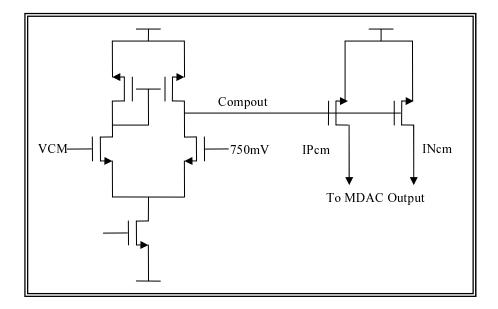

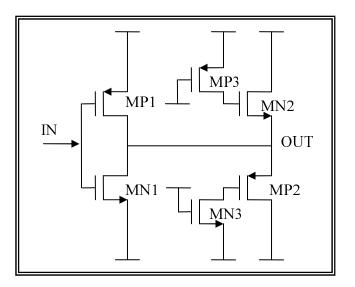

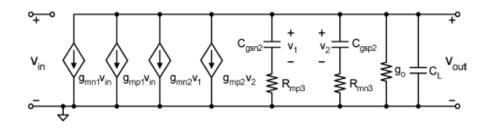

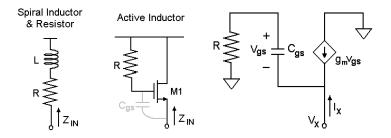

| Figure 5.14. | Small signal representation of the circuit of Figure 5.13 [17]                                                 | 81 |

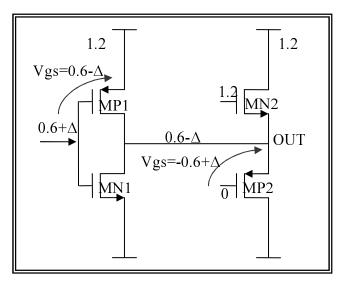

| Figure 5.13. | Inverter with active inductor representation                                                                   | 81 |

| Figure 5.15. | Node voltages of PMOS transistors at a random transient time                                                   | 82 |

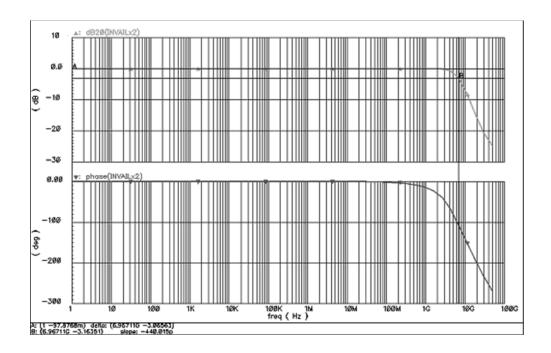

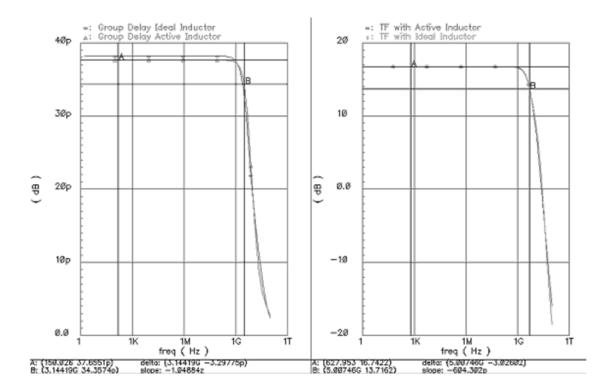

| Figure 5.16. | AC characteristics of one buffer composed of 2 INV-AIL cells                                                 | 84 |

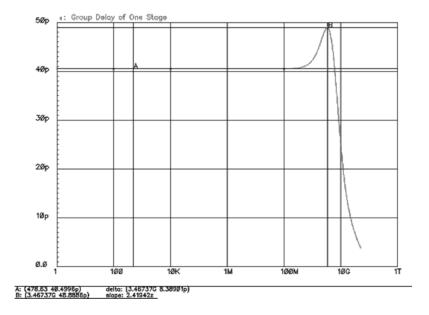

|--------------|--------------------------------------------------------------------------------------------------------------|----|

| Figure 5.17. | Group delay plot of one buffer composed of 2 INV-AIL cells                                                   | 85 |

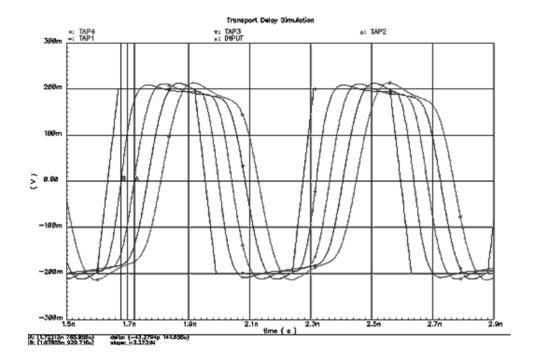

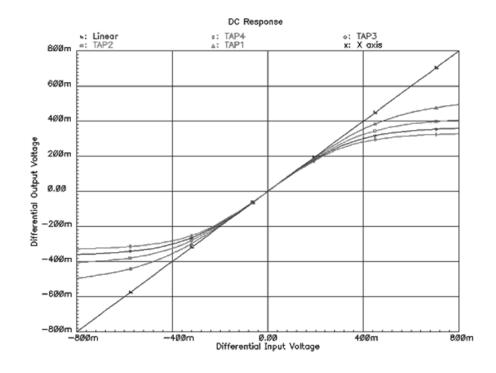

| Figure 5.18. | Transient simulation result of cascaded inverters                                                            | 86 |

| Figure 5.19. | Linearity of cascaded inverters                                                                              | 86 |

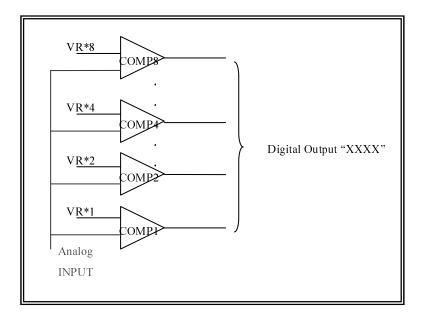

| Figure 5.20. | ADC top level representation                                                                                 | 88 |

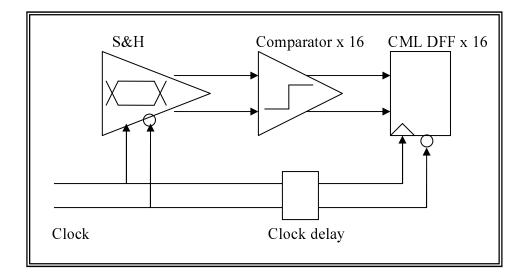

| Figure 5.21. | ADC schematic top level                                                                                      | 89 |

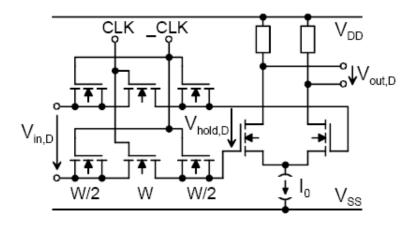

| Figure 5.22. | Track and hold circuitry which operates as Sample and Hold circuitry when cascaded with opposite clocks [42] | 89 |

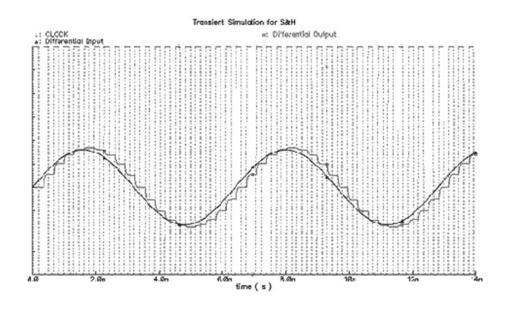

| Figure 5.23. | Sample and hold transient response                                                                           | 90 |

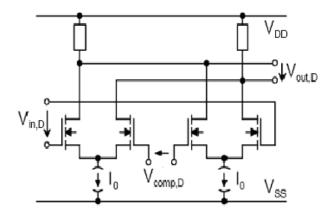

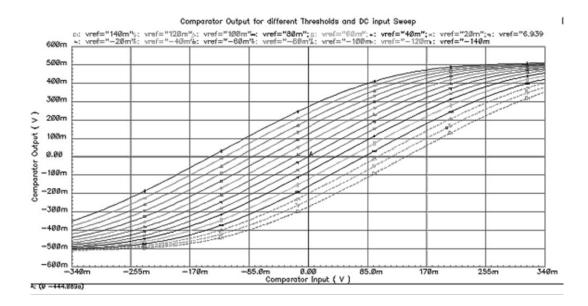

| Figure 5.24. | Comparator schematic representation [42]                                                                     | 91 |

| Figure 5.25. | Comparator DC response for different reference voltages during input sweep                                   | 92 |

| Figure 5.26. | Limiting amplifier with peaking [42]                                                                         | 92 |

| Figure 5.27. | CML latch composing CML DFF [42]                                                                             | 94 |

| Figure 5.28. | Top level ADC simulation for best and worst scenarios                                                        | 94 |

| Figure 5.29. | Converter transient simulation                                                                               | 95 |

| Figure 5.30. | Cascading limiting amplifiers                                                                                | 96 |

| Figure 5.31. | Active and passive inductor implementation                                                                   | 97 |

| Figure 5.32. | Limiting amplifier single stage transistor level implementation                            | 97  |

|--------------|--------------------------------------------------------------------------------------------|-----|

| Figure 5.33. | Ideal and active inductor transfer function and group delay comparison                     | 98  |

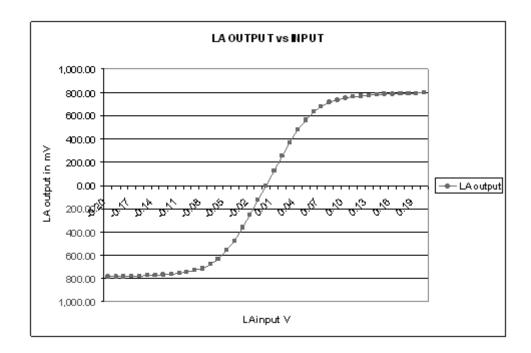

| Figure 5.34. | Limiting amplifier output saturation graph                                                 | 99  |

| Figure 5.35. | Limiting amplifier total group delay                                                       | 100 |

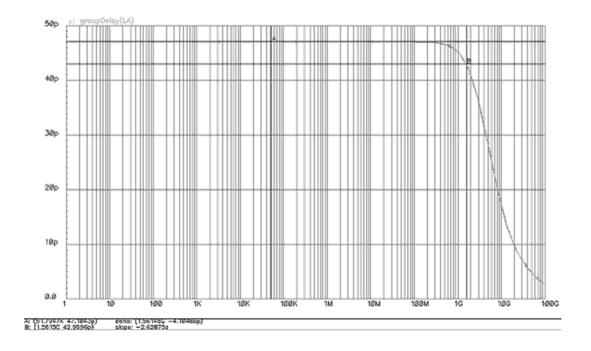

| Figure 5.36. | Limiting amplifier total transient response with different input amplit-<br>udes           | 100 |

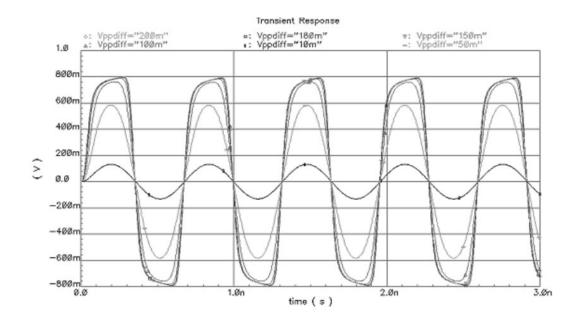

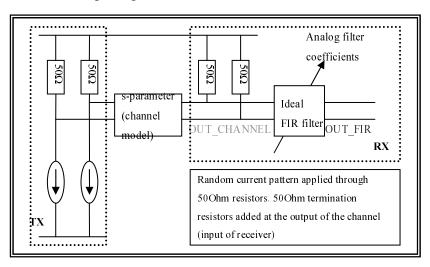

| Figure 5.37. | Simulation setup for top level system using the actual components                          | 101 |

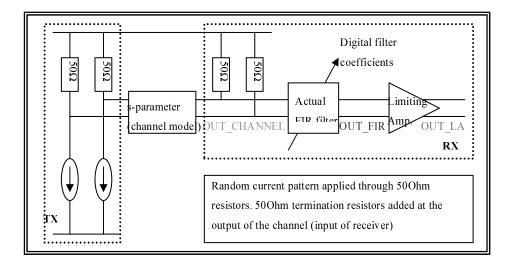

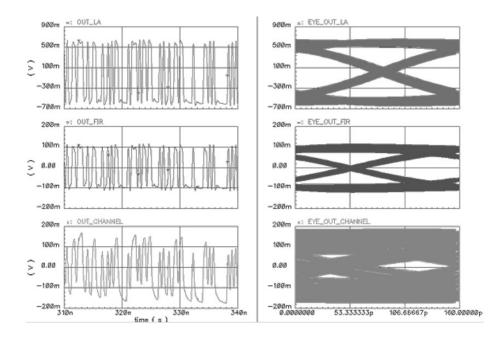

| Figure 5.38. | Simulation result of setup in Figure 5.36                                                  | 102 |

| Figure 5.39. | Simulation setup for top level system using the ideal components                           | 102 |

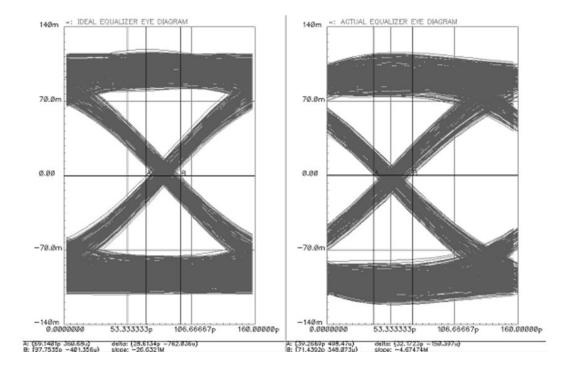

| Figure 5.40. | Simulation result comparison of setup in Figure 5.36 and 5.38 for 4 tap & x8 FIR equalizer | 103 |

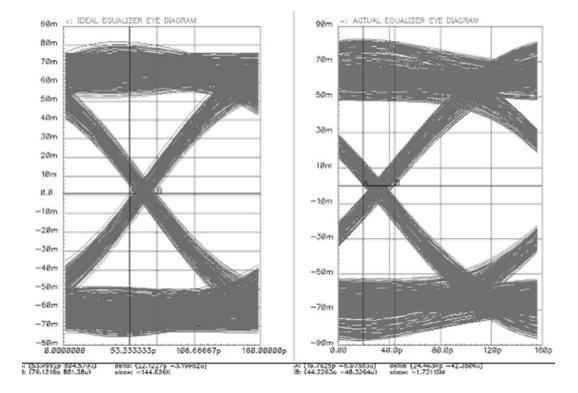

| Figure 5.41. | Simulation result comparison of setup in Figure 2.26 and 2.27 for 2 tap & x4 FIR equalizer | 104 |

## LIST OF TABLES

| Table 1.1. | Literature survey on equalizers                                            | 5   |

|------------|----------------------------------------------------------------------------|-----|

| Table 4.1. | RMS values of error versus tap spacing & number of taps                    | 65  |

| Table 4.2. | RMS values of error versus number of bits & number of taps                 | 68  |

| Table 5.1. | MDAC gain values vs. coefficient input                                     | 72  |

| Table 5.2. | Coefficient decoder                                                        | 72  |

| Table 5.3. | Gain and bandwidth features of the comparator                              | 91  |

| Table 5.4. | Gain and bandwidth features of the limiting amplifier with peaking         | 93  |

| Table 5.5. | Gain and bandwidth features of differential DFF                            | 94  |

| Table 5.6. | Limiting amplifier gain and bandwidth features                             | 98  |

| Table 5.7. | Tap coefficients for 4 tap,T/8 FIR equalizer in analog and digital format  | 101 |

| Table 5.8. | Tap coefficients for 2 tap, T/4 FIR equalizer in analog and digital format | 104 |

## LIST OF SYMBOLS/ABBREVIATIONS

| CMFB     | Common Mode Feedback          |

|----------|-------------------------------|

| СМА      | Constant Modulus Algorithm    |

| E()      | Expectation Operator          |

| FSE      | Fractionally Spaced Equalizer |

| $\nabla$ | Gradient                      |

| 0*       | Hermetian Transpose           |

| LMS      | Least Mean Squares            |

| LA       | Limiting Amplifier            |

| SSE      | Symbol Spaced Equalizer       |

| RLS      | Recursive Least Squares       |

| RMS      | Root Mean Square              |

| $O^{T}$  | Transpose                     |

| UI       | Unit Interval                 |

| ZF       | Zero Forcing                  |

|          |                               |

### **1. INTRODUCTION**

#### 1.1. Equalization for High Speed Communication

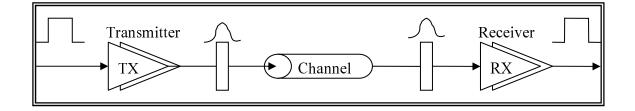

The simplest communication system (Figure 1.1) has three components, the transmitter to send the data converting the digital bits into electrical or optical data, the receiver to convert the analog data back into binary data and in-between a channel (copper wire, coaxial cable, optical fiber etc.) which makes this data transmission possible.

Figure 1.1. Block diagram of a typical high-speed digital data transceiver

Every material in nature shows filtering behavior. Since the transmission channel is not an all-pass filter, it may cause some deterioration on the transmitted data by behaving different frequency components in a different way. A transmission channel is usually a low-pass filter, and different frequency components lose different amplitude of power (frequency dependent loss) and experience different amount of phase distortion during propagation through the channel. These two most dominant effects contribute to the corruption of the original signal, which is the well-known inter-symbol interference (ISI).

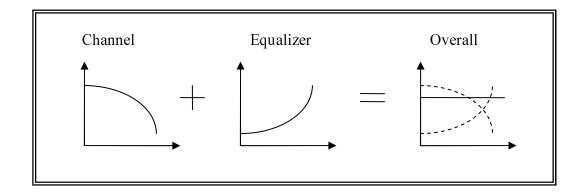

Depending on channel characteristics and receiver specifications, data might be required to be recovered to become understandable by the receiver side. Especially with the increasing data rate requirements, to take some responsibility over the shoulders of basic components of communication system for high quality transmission, additional block called equalizer started to be used. The mission of this additional block is simply recovering the data deteriorated due to non-idealistic channel characteristics, and helping the receiver to sample the arrived data correctly. It achieves this mission by removing or reducing the ISI on the data. An equalizer provides an inverse channel response such that the overall (i.e. combination of channel and equalizer) frequency response is flat over the bandwidth of interest. Since most common channel behavior is low pass filter, a high pass filter compensating the channel transfer function can be placed to the transmission path to obtain flat transfer function before data sampling. This is shown in Figure 1.2.

Figure 1.2. Effect of channel equalization

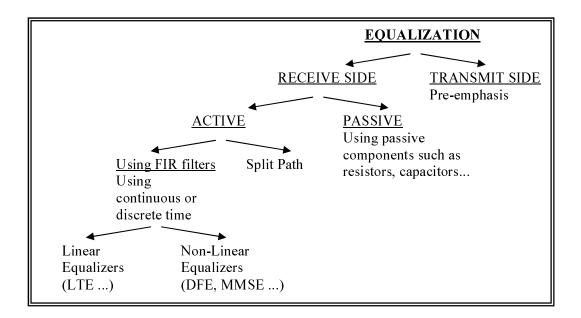

There are many ways to implement an equalizer. Equalizer can be placed either on the transmitter side or receiver side. Equalization on transmitter side is named as preemphasis. This method is used to amplify the high frequency components of the transmitted data or decrease the strength of the low frequency components. This way to equalize the transfer function of the path till receiver for all the frequency ingredients of the data stream is aimed. However, for this method to be applicable, the channel characteristics should be known a priori to be compensated before the transmission takes place. Equalization on receive side is also possible. Receiver equalizers can be composed of only passive components (passive equalizers). They can also be implemented as linear transversal filters and called linear transversal equalizers. The latter is advantageous due to its less area occupation.

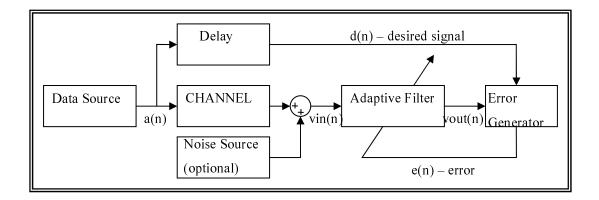

Since the channel is before the equalization in RX equalization, in case the channel characteristics are not known a priori, they can be estimated by the help of some adaptation algorithms. The most common way to achieve this is to train the equalizer by comparing the equalized data with the ideal stream and trying to minimize the error in between. This

way the channel characteristics might be estimated and compensated accordingly. This method is called adaptive equalization.

In this thesis, different examples to adaptive equalization at the receiver side are implemented using powerful tool, MATLAB Simulink. Different adaptation algorithms, cost functions and equalizer properties of linear transversal equalizers (such as number of taps, tap spacing etc.) are investigated. In the end, basic building blocks of a linear transversal equalizer is implemented in Cadence environment using STMicroelectronics CMOS 65nm technology and simulated using Spectre simulation tool. These building blocks are used to implement an equalizer operating at 3.125Gbps and compensating TYCO 30inch channel characteristics, with the coefficients obtained from its MATLAB counterpart. The improvement, managed by the equalizer is observed comparing the eye diagrams of the data at the input of the receiver (output of the channel), and the output of the equalizer is highly improved when compared to the almost closed eye at the output of the channel.

#### **1.2.** Literature Survey

When we go back in the history of equalization concept, the best summary that would come across belongs to Robert W. Lucky, inventor of adaptive equalization concept, who published a very detailed summary of equalizers designed between the years of 1968-1973 [1]. As the time passes, the market for high-bandwidth communications continues to drive the demand for higher speed transceivers and therefore, equalizers. In the wireline arena, 10Gb/s data transmission over copper channels (backplane PCB, UTP cable, etc.) for enterprise networking and data-center applications is reaching maturity and commercialization using low-cost CMOS transceivers. At the same time, up to 40Gb/s data transmission is being demonstrated over short channels [2].

The latest CMOS technology along with advances in design techniques has enabled us to continue to push the speed envelope. In addition to integrating more powerful signalprocessing functionality, such as FFE and DFE, on chip, innovative coding and circuit techniques help to overcome bandwidth limitations, adapt to different channels, and tolerate PVT variations while lowering power consumption and cost [2].

At relatively low bit rates, most adaptive equalizers have been implemented using a digital approach [3], [4]. Design of a digital equalizer at the receiver side involves a delay element and a decision circuit that requires a recovered clock. The extraction of the clock depends on the input data of the clock and data recovery (CDR) circuit, which increases the system complexity and could lead to problems with CDR locking. On the other hand, an analog approach is often preferred for higher speeds for its low power consumption and simplicity. A number of papers have been reported on analog cable equalization at bit rates on the order of 100 Mb/s [5], [6]. Some papers reported cable equalizers with bit-rates up to 3.5 Gb/s [7], [8]. In another paper, an analog adaptive equalizer running at 10 Gb/s using a BiCMOS fabrication process is represented [9]. More recently, a CMOS equalizer operating at 10 Gb/s was presented [10], [11] where more design effort was needed to overcome the gain limitations of CMOS. An analog FIR approach to 10 Gb/s equalization was presented in [12]. 20Gbps adaptive equalizer is implemented in 0.13um CMOS technology [5]. Using SiGe BiCMOS technology, even 49Gbps equalization using 7-tap transversal filter is achieved [13], [9].

For this specific thesis, a very nice paper written by Jin Liu et al. [17] is taken as a reference and implemented in 65nm, whereas the reference paper refers to 90nm CMOS technology design.

Some equalizer implementations are summarized in Table 1.1, according to their technology, input data rate, performance, chip area, power consumption and power supply values.

| REF. | ТЕСН.                    | INPUT<br>DATA<br>RATE | MAX.<br>COMPENSATED<br>LOSS | MAX.<br>P-P<br>JITTER | CHIP<br>AREA                 | POWER             | SUPPLY |

|------|--------------------------|-----------------------|-----------------------------|-----------------------|------------------------------|-------------------|--------|

| [15] | 0.35 <b>-</b> μm<br>CMOS | 200Mb/s               | 1dB at<br>100MHz            | N/A                   | 1.3<br>mm2                   | 19.5<br>mW        | 2.3V   |

| [16] | 0.25-μm<br>BiCMO<br>S    | 20Gb/s                | 20dB at<br>10GHz            | ~10ps                 | N/A                          | 32<br>mW          | 2.5V   |

| [17] | 0.25 <b>-</b> μm<br>CMOS | 2.5-<br>3.5Gb/s       | 21dB at<br>1.25GHz          | 100ps                 | 0.095<br>mm <sup>2</sup>     | 95<br>mW          | 2.5V   |

| [18] | 0.18-μm<br>CMOS          | 125Mb/s               | N/A                         | 2.61ns                | 27738<br>μm2                 | 3.7<br>mW         | 1.6V   |

| [9]  | 0.18 <b>-</b> μm<br>CMOS | 10Gb/s                | 16.7dB at<br>5GHz           | 27.11ps               | 0.86×1.28<br>mm <sup>2</sup> | 34.2<br>mW        | 1.8V   |

| [19] | 0.18-μm<br>CMOS          | 11.8Gb/s              | 12dB at<br>5.875GHz         | 47ps                  | 1175×1135<br>μm <sup>2</sup> | 201<br>mW         | 1.8V   |

| [20] | 0.13-μm<br>CMOS          | 10Gb/s                | 20dB at<br>5GHz             | 15.67ps               | 0.94x0.65<br>mm <sup>2</sup> | 133<br>mW         | 1.6V   |

| [5]  | 0.13-μm<br>CMOS          | 20Gb/s                | 15~20dB at<br>10GHz         | 14ps                  | 0.8×0.25<br>mm <sup>2</sup>  | 60<br>mW          | 1.5V   |

| [20] | 0.11-μm<br>CMOS          | 10Gb/s                | 20dB at<br>5GHz             | 27.8ps                | 47×85<br>μm <sup>2</sup>     | 13.2<br>mW        | 1.2V   |

| [21] | 90-nm<br>CMOS            | 10Gb/s                | 20-30dB at<br>5GHz          | N/A                   | N/A                          | 130mW<br>(w. PLL) | 1V     |

| [22] | 90-nm<br>CMOS            | 10Gb/s                | 23dB at<br>5GHz             | N/A                   | 270x200<br>μm <sup>2</sup>   | 22<br>mW          | 1.2V   |

Table 1.1. Literature survey on equalizers

#### 1.3. Thesis Organization

In this thesis, in Chapter 2, basic communication system components will be mentioned. It will be followed by channel non-idealities such as metallic channel loss, crosstalk noise and their effects on data transmission. ISI will also be focused on with the conditions leading to it, and its effects on the reliability of the data transmission. The next subject in this chapter is removal of ISI using equalization techniques.

Chapter 3 focuses on adaptive equalization techniques, that are used when the channel characteristics are not known a priori or when channel transfer function is time-variant. Introduction to adaptation algorithms such as Zero Forcing Algorithm, Least Mean Squares and Recursive Least Squares Algorithm and Constant Modulus will be provided.

Introducing the theoretical aspects of communication systems and adaptation methodologies, empirical phase of the study will be presented in the following chapters. Chapter 4 is a summary of equalizer implementation using MATLAB Simulink. In this chapter, comparison of different adaptation algorithms, cost functions, and comparison of linear transversal equalizers with different characteristics will take place. The coefficients obtained from MATLAB simulations will be used in CMOS implementation of the equalizer as well.

In Chapter 5, transistor level implementation of a linear transversal equalizer is discussed. Simulations with Spectre simulator are used to evaluate the performance of the equalizer by observing the eye diagrams of the data at the input and output of the equalizer. The performance of each building block used to implement the top level equalizer is also investigated.

Finally, conclusions are drawn in Chapter 6, and the directions of future work are discussed briefly.

### 2. COMMUNICATION SYSTEMS

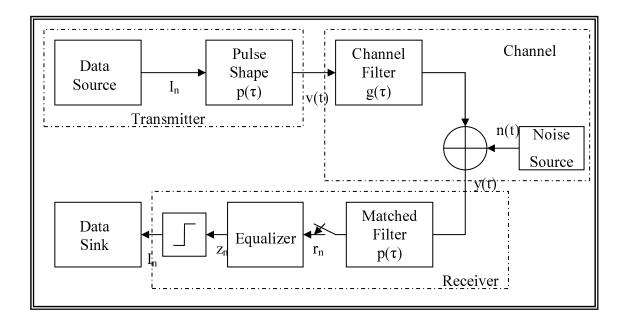

Communication systems are systems that are responsible for information transfer between transmitting and receiving parts through a channel. At its simplest, the system contains modulator, transmitter, transmission channel, receiver and demodulator (Figure 2.1).

A modulator takes the source signal and transforms it so that it is physically suitable for the transmission channel. A transmitter actually introduces the modulated signal into the channel, usually amplifying the signal. A transmission channel that is the physical link between the communicating parties. A receiver detects the transmitted signal on the channel and usually amplifies it (as it will have been attenuated by its journey through the channel). A demodulator receives the original source signal from the received signal and passes it to the sink.

Figure 2.1. Basic communication system [35]

As well as the correct functionality of transmitter and receiver, the quality of the channel also determines accuracy in data transmission, which can be quantified via BER, jitter etc. measurements. Channel quality requirement became more visible in the picture with the higher speed demand in data transmissions. Non-ideal channel characteristics, such as channel bandwidth and crosstalk noise, often deteriorate the signal quality of the received signal and causes error in data recovery. This means, it is no longer sufficient to solely increase the speed of the ICs to achieve higher data rates and that's why new research areas emerged to improve bandwidth of transmission channels for less deterioration [21].

High bandwidth need leads industry standards to be developed. These standards define the channel characteristics and I/O electrical specifications of short reach (4-in, on-board) and long reach (30-in+, inter-card) serial links operating at data rates in excess of 10 Gb/s. While serial link transceivers in the 6-Gb/s range are often intended to extend the bandwidth of "legacy" backplane channels, reliable operation above 10 Gb/s will require in many cases improved channel characteristics. Therefore, the standards above 10 Gb/s are primarily aimed at new optical backplane designs benefiting from improvements in board, connector, and chip-level package technologies.

Even with improved backplane designs, however, the need to remain pricecompetitive, complexity of implementation and lower degree of integration will discourage adoption of the most exotic (and expensive) board, connector, and package technologies. As in the recent past, advanced equalization capabilities in the I/O circuitry will be employed to compensate for the signal distortions of lower cost interconnect technologies such as PCBs. Optimizing cost tradeoffs at the system level requires knowledge of how much equalization is needed for a specific combination of board, connector, and package technologies.

Before concentrating on equalization techniques, understanding of channel distortion and its effects on data deterioration is necessary.

#### 2.1. Channel Non-idealities

There are various communication channels with distinct channel characteristics. They can be classified as on chip, chip to chip, board to board, box to box and system to system interconnects.

Interconnects less than 1cm lengths are defined as on chip interconnects. They can be manufactured from Al, Cu or CMOS compatible materials such as Si, SiO2. Chip to chip interconnects are between 1cm and 10 cm length ranges. The density of Cu traces on FR4 is constrained by EMI and crosstalk problems. On chip and chip to chip connections are

very promising interconnect candidates for the future. Board to board connection is the class for interconnects between 1m to 10m length. Due to higher bandwidth, they are potential applications for optical interconnect. Their materials are mainly polymer WG, fiber ribbon with VCSELs etc. Box to box interconnect is usually optical fiber channel which is longer than 10m.

Due to limited bandwidth of PCB trace material, optical channel has been considered for beyond 10Gbps data transmission for above chip-to-chip applications. Currently, as mentioned before, the main barriers are high cost, lower degree of integration, and complexity of implementation. For optical channels polarization mode dispersion (PMD), chromatic dispersion (CD) are the main physical effects degrading the signal integrity at very high speeds.

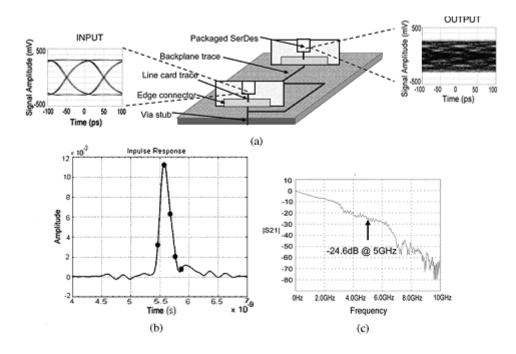

A typical backplane/line card application is shown in Figure 2.2.a. A long (30-in or more) transmission line on the backplane is used to transfer data from a processor or ASIC on one line card to a processor or ASIC on another line card. Several physical effects degrade signal integrity at data rates above a few gigabits per second. Skin effect and dielectric losses of the transmission lines become severe at these data rates. Via stubs on the circuit boards and other impedance discontinuities associated with the chip packages and connectors cause reflections easily observed in the channel impulse response (Figure 2.2.b) In the frequency domain, these reflections cause notches which further degrade the channel frequency response (Figure 2.2.c).

Figure 2.2. Backplane channel characteristics [21] a) Backplane/line card application, b) Channel impulse response, (c) Channel frequency response

Since the transmitted signal is attenuated by loss, it is easily corrupted by crosstalk from other channels. Even for greenfield backplanes with improved board technology, the loss at 5 GHz (Nyquist frequency for 10-Gb/s data) may be 20–30 dB. With the channel adding so much loss and distortion to the signal, the data eye at the far end of the link (Figure 2.2.a) is completely closed, and advanced equalization is required to recover the transmitted bits.

At this high data rate, the channel non-idealities result in signal loss and reflections as well as significant high-frequency crosstalk. Figure 2.2.b illustrates measurements of a typical legacy backplane channel with approximately 20 dB of loss at 3.125 GHz and crosstalk energy that actually exceeds the signal energy at slightly higher frequencies [21].

PCB interconnects are very popular in today's communication channels due to their low cost and less complexity and from now on this interconnection will be focused on. ISI, its effects and equalization to compensate ISI up to a certain extent will be discussed after focusing on the non-idealities - metallic channel loss, crosstalk noise - of the PCB channel.

#### 2.1.1. Crosstalk

There are various noise sources that cause errors in data and clock recovery, for example, the crosstalk noise, the power supply noise, and reflection noise.

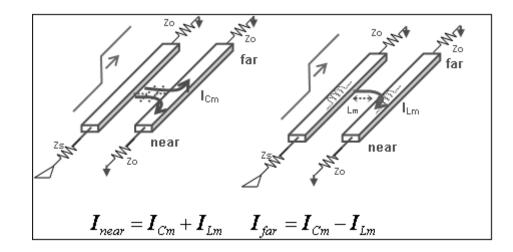

Power supply noise is induced by switching large currents in short duration across the parasitic inductance in power distribution network; it increases with the switching frequency of I/O driver, output signal swing, and number of switching drivers at the same time. Reflections are due to impedance discontinuities; common reflection noise for backplane applications includes card-to-board connectors, cable-to-card connectors, long vias with their respective end pads, wire bonds or flip-chip solder balls and orthogonal wiring [23]. Crosstalk is caused by the electromagnetic coupling between signal lines through mutual capacitance and mutual inductance. Among these various noise factors, the dominant one for backplane is the crosstalk noise, specially the near end cross talk (NEXT) at the connectors.

Figure 2.3. Near End & Far End crosstalk theory [24]

The mutual inductance will induce current on the victim line opposite of the driving current. (Lenz Law) The mutual capacitance will pass current through the mutual capacitance that flows in both directions on the victim line [24]. The near and far end victim line currents sum to produce the near and the far end crosstalk noise as represented in Figure 2.3. Since the current flowing to the near node is sum of both inductive and

capacitive currents, NEXT is always positive. FEXT is only positive when  $I_{LM}$  is less than  $I_{CM}$ , which is not very usual.

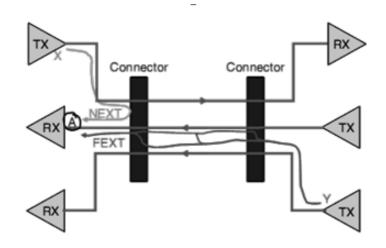

Figure 2.4 illustrates the near end crosstalk (NEXT) and the far end crosstalk (FEXT) in a representative communication system.

Figure 2.4. Near End & Far End crosstalk representation in a communication system [23]

For the receiver at point A in Figure 2.4, the crosstalk generated from nearby transmitter at point X is called NEXT. In this figure, only the major coupling path through the connector is illustrated. In reality, the PCB traces between the two connectors also contribute for NEXT. FEXT is generated from transmitter at the other end, point Y in the figure. FEXT also has multiple paths. Since the FEXT transfer channel has much longer distance than that of NEXT, the FEXT transfer function has much more severe attenuation than the NEXT transfer function. Therefore, NEXT is more critical to correct data recovery of weak received signal in receiver end. The NEXT transfer function increases with frequency [23]. For high-speed data transmissions, effective equalization method to mitigate NEXT has become necessary.

#### 2.1.2. Metallic Channel Loss

For PCB channel in chip-to-chip communications, there are mainly two non-ideal characteristics that limit the data transmission rate and distance. The first was cross talk; the latter is the limited bandwidth due to frequency dependent channel loss. For all metallic media, including PCB traces and metallic cables like unshielded twist pair (UTP) cables, shielded twisted pair (STP) cables and coaxial cables, the channel losses at higher frequencies are mainly caused by skin effect and dielectric loss [23]. Other loss scheme like radiation loss is negligible even when the signal frequency is up to 10 GHz.

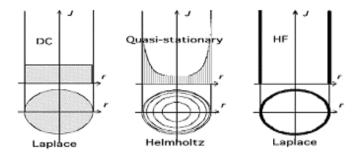

2.1.2.1. Sources of Metallic Channel Loss. When a DC signal propagates through a PCB trace, or through any wire for that matter, the current flows so that it's evenly distributed through the conductor cross section (Figure 2.5). As the signal frequency rises, the magnetic field pushes out of the conductor while the current crowds out toward the wall of the conductor. At even higher frequencies, the current is flowing mainly within the thin layer under the conductor surface, or under the "skin" of the conductor. In the absence of other conductors in proximity, the current distributes itself evenly along the perimeter of the conductor cross-section. This in turn leads to frequency dependence of the inductance and resistance. This phenomenon is called skin effect [25].

Figure 2.5. Current density J as a function of frequency. Current spread out towards the conductor surface as the frequency rises [25]

Dielectric loss is the loss of electromagnetic power due to the non-ideal characteristics of the dielectric material such as isolator around the conducting media during electromagnetic wave propagation. There are two main mechanisms responsible for non-ideal characteristics of the dielectric material. First, there is some, although very small, amount of direct current leakage through the dielectric even at zero frequency. Second, there is a polarization loss, which can be easily understood if the molecules of FR4, or other PCB materials, are viewed as dipoles. Water, for example, is a very prevalent molecule in FR4. When put in an alternating electric field, H<sub>2</sub>O molecules tend to change their orientation following the electric field, just like a weathercock in a wind constantly changing its direction. It is the signal driver that causes the current to flow in the trace, and therefore causes the high frequency field to move down the trace along with the signal. The field, in turn, forces the molecules of the surrounding dielectric to oscillate. While doing so the field loses some energy. Since the signal and the field "around it" are inseparable, the signal loses some of its strength too. The dipole molecules of the dielectric react differently to the external field at different frequencies. From DC to some high frequencies of about several hundred MHz, these molecules easily follow the external alternating field. However, at even higher frequencies, they find it harder and harder to respond to the external force. As the field frequency increases, the dipole molecules of the dielectric, first, lag behind the field, and then totally ignore it at very high frequencies. Via this mechanism the dielectric molecules drain the energy from the field – but drain it to various degrees at various frequencies. Since a digital signal comprises a bunch of various frequency components, each such signal component gets attenuated differently from others. With various frequency components being attenuated to a different degree, the signal shape changes in a rather convoluted manner [25].

Channel loss due to these two factors can be expressed by the following equation [23]:

$$C(f) = e^{-[h_s(1+j)\sqrt{f} + h_d f]l]}$$

(2.1)

where  $h_s$  is skin-effect loss coefficient,  $h_d$  is dielectric loss coefficient, l is length of the media, and f is frequency.

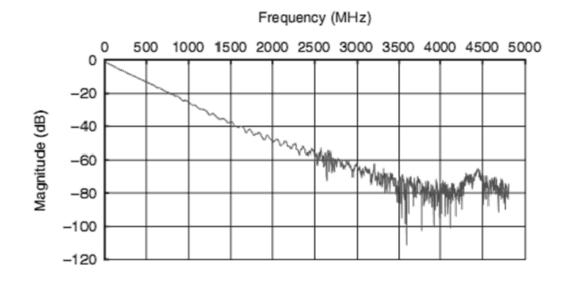

Figure 2.6 shows the measurement of the channel loss; specifically it is the S21 parameter of a single-ended 180-inch PCB micro strip with two SMT connectors. The trace width affects the loss characteristics; a wider trace introduces smaller attenuation.

Figure 2.6. Measured S21 parameter for a PCB trace [23]

Both the equation and the plot show that the channel loss increases with frequency, specifically, the attenuation due to skin effect increases exponentially with the square root of frequency and the attenuation due to dielectric loss increases exponentially with frequency. Thus, the metallic transmission media have limited bandwidth which limits the data transmission rate. Also shown in the equation is that the channel loss increases exponentially with media length, as a result, the data transmission has limited transmission rate and the transmission distance. For the same media, if the transmission distance is shorter, it is possible to transmit at higher data rate. [23]

Each different media has its own unique skin effect coefficient and the dielectric loss coefficient. For example, the UTP cables widely used for building wiring have larger attenuation coefficients than those of the coaxial cables.

Figure 2.6 shows that at 1 GHz, the channel loss for this trace is about 25 dB. The signals shown in Figure 2.7 and Figure 2.8 are for data transmission through this channel at data rate 1 Gbps. When the channel loss is the only non-ideal factor being considered, the loss characteristics can be identified by the channel loss at symbol rate frequency; for 1 Gbps data rate, the corresponding symbol rate frequency is 1 GHz. When the channel attenuation is about 25 dB at symbol rate frequency, the channel loss is quite severe and it causes the received signal to have closed eyes.

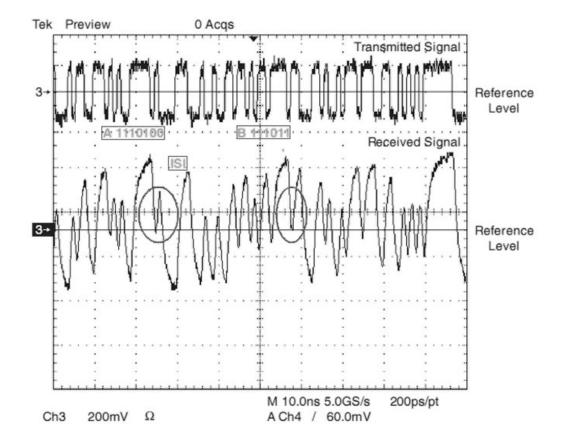

Figure 2.7. Illustration of ISI-the transmitted signal (top) and the received signal (bottom) through a band limited channel [23]

Figure 2.8. Eye diagram of (a) the transmitted signal and (b) the received signal [23]

2.1.2.2. Result of Channel Loss: Inter-Symbol Interference (ISI). The channel transfer function in the previous sections shows that different frequency suffers different degrees of attenuation and phase delay. A transmitted square wave contains many frequency components, after transmission through the channel; the frequency components suffer dispersion due to different degrees of magnitude attenuation and phase delay. Due to similar dispersion effect on light, we see the appearance of rainbow. The term, inter-symbol interference, describes the dispersion effect in discrete time domain, where the

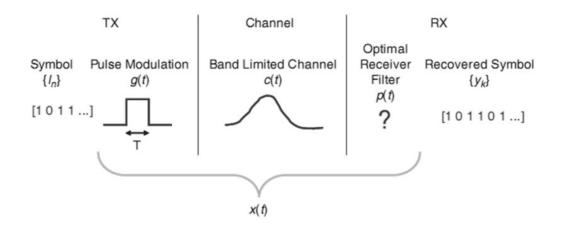

transmitted data are treated as digital symbols with pulse modulation. Figure 2.9 shows the communication channel with transmitter pulse modulation and receiver filter. For binary data, which is also known as two-level pulse amplitude modulation (2-PAM) shown in Figure 2.7, the discrete information-bearing symbol  $\{I_n\}$  is either "1" or "0" and the modulation pulse is a square pulse as shown.

Figure 2.9. Communication channel with transmitter pulse modulation and received filter [23]

For several types of digital modulation techniques the received signal after the receiver filter, without considering channel noise, can be expressed as [23].

$$y(t) = \sum_{n=0}^{\infty} l_n x(t - nT)$$

(2.2)

Where x(t) is the overall response including the transmitter modulation, channel function, and receiver filter. To obtain the recovered symbol, y(t) is sampled at times  $t = kT + \tau_0$ , k = 0, 1, ..., where  $\tau_0$  is the transmission delay. We then have:

$$y(kT + \tau_0) \equiv y_k = \sum_{n=0}^{\infty} l_n x(kT + \tau_0 - nT)$$

(2.3)

or equivalently,

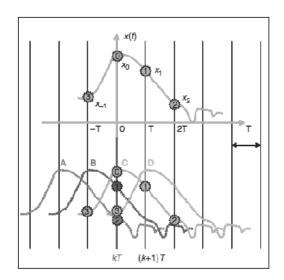

$$y_{k} = \sum_{n=0}^{\infty} l_{n} x_{k-n} = x_{0} l_{k} + \sum_{\substack{n=0\\n \neq k}}^{\infty} l_{n} x_{k-n}$$

(2.4)

The term  $x_0I_k$  represents the desired information symbol at the k<sup>th</sup> sampling point and the last term, which contains information from the previous and future samples, represents ISI.

If the channel has infinite bandwidth, the channel impulse response is an impulse,  $\delta(t)$ . Because of bandwidth limitation, the channel impulse response, c(t), is a spread pulse as shown in Figure 2.9. Convolving the modulation pulse, g(t), with c(t) results an impulse response whose pulse width is wider than T, the pulse width of g(t). The receiver filter is usually designed as match filter. The overall impulse response x(t) will have wider pulse width than T, as illustrated in the top plot in Figure 2.10. The bottom plot in the same figure shows that consecutive symbols of "1"s are transmitted. Looking at the sampling point KT, the recovered symbol is the sum of the desired symbol value labeled by point 0; it equals  $x_0$  on curve C, plus ISI from neighboring symbols, namely point 1 from curve B (= $x_1$ ), point 2 from curve A (= $x_2$ ) and point 3 from curve D (= $x_{-1}$ ). In summary, ISI occurs when the overall impulse response, x(t), has wider spread than the symbol period T.

Figure 2.10. Illustration of ISI [23]

The best way to qualitatively measure effects of ISI in signal integrity is the eye diagrams as shown in Figure 2.8. The effect of ISI and other noises can be observed on an oscilloscope displaying the output of the matched filter on the vertical input with horizontal sweep rate set at multiples of 1/T. Such a display is called an eye diagram.

The effect of ISI is to cause a reduction in the eye opening by reducing the peak as well as causing ambiguity in the timing information. Clock and data recovery is impossible and equalization is mandatory to restore the timing information in this case. In summary equalization is used to remove side effects of channel loss to improve the received signal quality for correct clock and data recovery, so that the system achieves lower bit error rate for the goal of error-proof data communications.

There are two types of equalization schemes: one is at the transmitter side; the other is at the receiver side. The communication channel characteristics vary and adaptive equalization is generally required.

#### 2.2. Channel Equalization

There are two types of equalization: transmitter pre-emphasis and receiver equalization. Both seek to either emphasize the high-frequency components or to deemphasize the low frequency components of the transmitted or received signal, in order to compensate the effect that the high-frequency components are attenuated more than the low-frequency components through the channel. Using both the transmitter and receiver equalization allows the best system performance in terms of BER (bit error rate).

The transfer function of both types of equalizer is a high-pass filter; though in practice, it is a band-pass filter. One reason is that the bandwidth limitation of semiconductor devices cannot achieve infinite bandwidth; the other is to avoid noise amplification. Though the spectrum of transmitted signal is infinite, the main slope within the symbol rate frequency contains most of the information, as shown in Figure 2.10. With additive white Gaussian noise (AWGN) and crosstalk noise, there is significant amount of

noise beyond the symbol rate frequency bandwidth. If the equalizer still has significant gain after this bandwidth, the high-frequency noise will be amplified and it deteriorates the signal quality [23].

In its broad sense, the term "equalizer" applies to any signal processing device designed to deal with ISI. Below is the classification of some of these equalization techniques:

Figure 2.11. Classification of equalization techniques

Equalization eliminates the problem of frequency-dependent attenuation by filtering the transmitted or received waveform so the concatenation of the equalizing filter and the transmission line gives a flat frequency response [26].

#### 2.2.1. Transmitter Equalizer (Pre-Emphasis)

Pre-emphasis is realized at the transmitter side. In some cases it increases the highfrequency components, which can cause EMI and more severe crosstalk problems. In other cases it reduces the power of low frequency components, known as de-emphasis. FIR filters are generally used for transmitter pre-emphasis. A simplified approach is to use two differential amplifiers, with the first one controlled by the original code, and the second by emphasis code (produced by inverting the original code and delay one symbol period). In some cases, the FIR filter was approximated by a transition filter implemented with a look-up table.

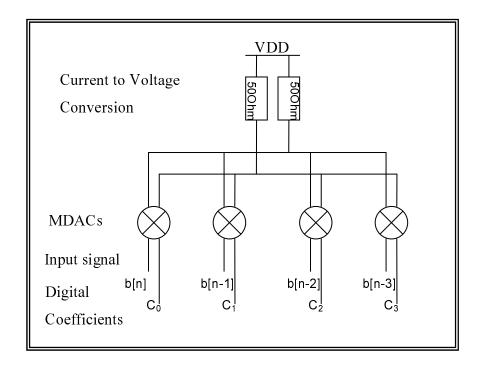

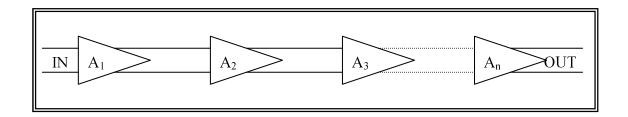

Below figure represents an example for pre-emphasis implemented by 4-tap FIR filter. The input signal comes from either data serializer if available, or tap delay line realized with simple digital delay unit. The first tap, with the input data b[n], is the main tap and the other three taps, whose inputs are one symbol to three symbols delay separately, compensate for the post cursor ISI. MDACs are used to multiply input data with the tap coefficients to build up the FIR filter required. The current outputs of MDACs are converted to voltage through off-chip or on-chip 500hm resistors.

Figure 2.12. Pre-emphasis with FIR filter

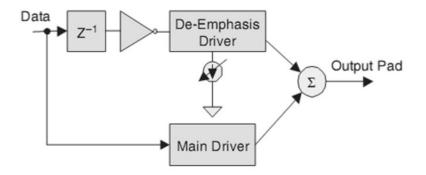

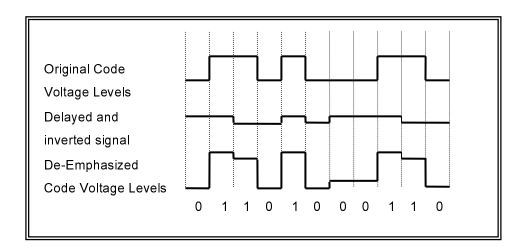

Transmitter equalizer can also be a de-emphasis filter which reduces the power of low frequency component in advance. The simplest way to implement is increasing the signal amplitude at each transition edge and reducing the signal amplitude when there is no transition. The de-emphasis equalizer uses the inverted signal of previous bit as emphasis signal. During '0' to '1' transition edge, signal amplitude is increased; in '1' to '0' transition edge, signal amplitude is further increased to negative direction. In other periods when there is no transition, the emphasis signal is opposite to the current bit and signal amplitude is reduced. To better control the strength of pulse, the auxiliary 3-bit DACs can be used to set the emphasis level [27]. Figure 2.13 shows the block diagram of deemphasis equalizer. This de-emphasis is actually a 2-tap FIR filter with a high-pass frequency response.

Figure 2.13. Block diagram of de-emphasis equalizer [23]

Figure 2.14. Illustration of de-emphasis equalizer functionality

## 2.2.2. Receiver Equalizer

Receiver equalization is a function applied at the receiver that counteracts the data degradation in the long transmission line. The equalizer could be either digital equalizer which is equivalent to applying the pre-emphasis techniques to the receiving end of the channel, or it could be the analog equalizer which employs RC filter to compensate the channel loss.

To be more specific there are generally four categories of receiver equalizers for over Gbps data transmissions: passive-component equalizer, active continuous-time equalizer using split-path amplifier, active equalizer using discrete-time FIR filter and active equalizer using continuous-time FIR filter.

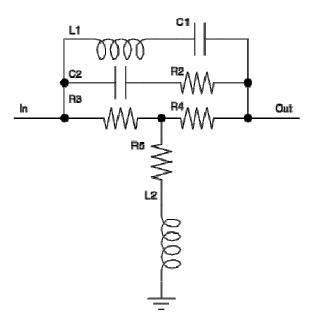

2.2.2.1. Passive Component Equalizers. Passive equalizers consist of only passive components such as capacitor, resistor and inductor. They require no power to operate. Since there is no involvement of active components, there is no noise source in the passive equalizer design. High dynamic range due to absence of power supplies to limit voltage swing is also another advantage of these equalizers. Since the passive components rarely break they are known with their extremely good reliability also. Despite their simplicity and the advantages above, they are disliked for their cost and size due to inductor involvement. Passive equalization is preferred in the case when the received signal has large amplitude and the receiver sensitivity is high. Passive compensation has been relegated to applications that correct at one specific length and bit rate and tend not to be applied to a wide range of conditions.

Below figure represents an implementation of a passive equalizer using bridged T similar network [28]. Passive components in the equalizer define frequency characteristics in different band dependently, which eases the design procedure [23]. For example, R3, R4, R5 and L2 set the characteristics impedance; C2 and R2 set the low frequency compensation; mid-band frequency compensation is set by L2; and L1 and C1 set the high frequency compensation.

Figure 2.15. Passive T-bridged equalizer [23]

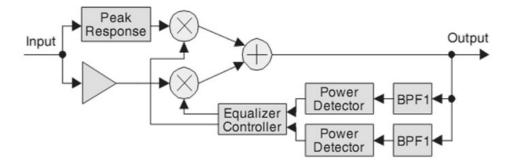

2.2.2.2. Active Continuous Time Equalizer. One way to achieve continuous time equalization with active devices is using split path amplifier: Split-path amplifier divides the signal path into two paths [23]. One path comprises a high pass filter or peak response filter to amplify the high frequency component. Another path is an all pass filter or a low pass filter to match the time delay of first path. Weighted sum of two paths is equivalent to a variant gain high pass filter, whose gain factor can be varied by controlling the weight of those two paths. Figure 2.16 shows a 3.2 Gbps adaptive cable equalizer using a peak response filter which is also a feed-forward amplifier as it is equivalent to add a zero or a feed-ward path [29]. An equalizer control circuit compares the power ratio at two specific frequency points using band-pass filters to set the weighted factor of those two paths.

Figure 2.16. Split-path equalizer example [23]

To better match phase delay in split path amplifier, the flat response path must use the same amplifier as in the feed-forward path. Wider gain control range is achieved by jointly adjusting the poles position in both paths. Traditional OPAMP-based amplifier using feedback resistor provides precise gain and low non-linearity [23]. However, negative feedback loop prevents the amplifier working in GHz range.

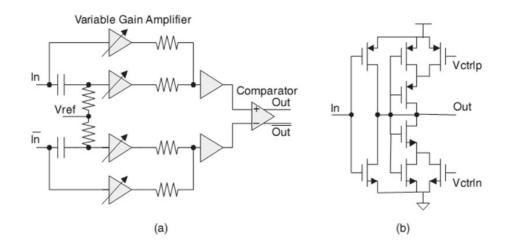

Phase mismatch between feedback loop and input signal also limit using a feedback loop amplifier in high frequency range. Figure 2.17 shows a wide band split-path amplifier without feedback loop; the amplifier gain is controlled through the load resistor instead of using feedback resistor.

Figure 2.17. Wideband split-path amplifier (a) without feedback loop and (b) variable gain amplifier [23]

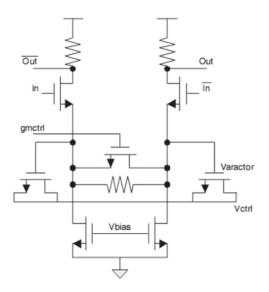

It is known that the transconductance of a source degeneration transconductor is close to the conductance, 1/R of the degeneration resistor. If the degeneration comprises a resistor and a capacitor, the resistor corresponds to an all path loop while the capacitor corresponds to a high pass path. Therefore, such a transconductor cell serves as a compact split-path amplifier. To tune the high frequency gain and low frequency gain, the capacitor and resistor are implemented with varactor and a linear MOS transistor. Figure 2.18 shows the schematic of the source degeneration transconductor. Varying the controlling voltage of varactor and MOS transistor, Vctrl and gmctrl, will change the high frequency boosting and low frequency gain.

Figure 2.18. Source degeneration transconductor filter [23]

More common way to achieve continuous time equalization with active devices is using FIR filters. FIR filters can be either discrete time or continuous time. Traditional discrete-time transversal FIR filters have been widely used in hard disk read channel equalization and in broadband modems equalizer [23].

Depending on the circuit realization of tap delay line and multiplier, the discrete-time FIR filters can be grouped into following four categories:

- Fully digital realization [9] [10]

- Digital tap delay line + multiplying digital to analog converter (MDAC) [32]

- Serial sampling analog tap delay line + analog multiplier

- Parallel sampling analog tap delay line + analog multiplier

Structures of the first two types require high speed ADC to convert received analog signal into digital bits, which is hard to realize with CMOS technology at Gbps data rate. Tap delay line of the third type has been realized with unity gain sample-and-hold (S&H) cell. Analog input signal passes through the delay line directly and there is no need for high-speed ADC. The disadvantage of this structure is that each S&H cell introduces distortion and attenuation to the delayed signal. All distortion and attenuation due to nonlinearity, clock feed through and limited bandwidth of S&H cell will accumulate along the line [33]. Another main drawback of serial sampling delay is that each delay unit must settle down in one symbol period which requires high frequency clock and wide bandwidth S&H. To avoid error accumulation, parallel sampling units of the fourth type sample input signal in sequence and switch them to the corresponding multipliers through rotating switch matrix [33].

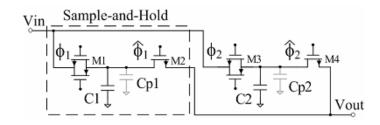

Below is one example of realization of switched capacitor FIR filter for channel equalization for the fourth type.

Figure 2.19. Example channel filter with top plate S/H cells [33]

Figure 2.19 shows an example, passive filter channel with two S/H cells that use bottom-plate sampling. At first, ignore the parasitic capacitors and assume the transistors act as ideal switches. The odd numbered transistors are switched so that Vin is sampled onto  $C_1$  and  $C_2$  during consecutive sampling periods. Then the even numbered switches are closed, connecting  $C_1$  and  $C_2$  in parallel between ground and the output node. Charge sharing gives an output that is a weighted sum of two consecutive input samples, as desired. The following equation describes the ideal transfer function, including a signal inversion [34].

$$\frac{Vout}{Vin}(z) = -K \left[ \frac{C_1 z^{-2} + C_2 z^{-1}}{(C_1 + C_2)} \right]$$

(2.5)

The capacitors in the equalizer are chosen to give this transfer function. The scale factor K depends on the output parasitic capacitances.

Instead of using sample and hold cells for one period delay in FIR filter, delay of one period can also be implemented using continuous time transport delay cells. This method is known as continuous time FIR equalization. This way clock and data synchronization complexity can be exterminated. One method to obtain transport delay is to use source followers [23]. However, due to bandwidth limitation of CMOS circuit, the frequency range of filter will be limited. Artificial transmission line implementation can be used to overcome this bandwidth limitation in expense of area due to long line requirements.

## 2.3. Receiver Equalization Using FIR Filters

From now on receiver equalization with FIR filters will be focused on. These are discrete time equalizers that are designed to overcome data distortions due to ISI and/or noise at the receiver end.

#### **2.3.1.** Communication System Summary

Before defining the channel and equalizer characteristics in discrete time domain, it is useful to revisit the basic communication system again as follows [35]:

Figure 2.20. Basic communication system revisited

$I_n$  is the input data to the pulse shape circuitry (modulator) and the output of pulse shape cell is the convolution of input signal with the pulse shape transfer function and can be represented as follows:

$$v(t) = \sum_{n} I_n p(t - nT)$$

(2.6)

The signal then passes through the channel with transfer function  $g(\tau)$  and reaches the receiver end as signal y(t) after addition of noise n(t). Transmit filter and the channel can be combined to one filter with transfer function  $h(\tau)$  due to their linearity. The frequency response of this combined filter is as follows:

$$H(f) = P(f)G(f)$$

(2.7)

The receiver input after combined filter and addition of noise will be represented as:

$$y(t) = \sum_{n} I_{n}h(t - nT) + n(t)$$

(2.8)

Receiver then takes this signal and passes it through the matched-filter to form the signal r(t):

$$r(t) = \int y(t)p(t-\tau)d\tau \qquad (2.9)$$

This signal r(t) is sampled to form the discrete time signal  $r_n=r(nT)$ . If the above two equations are combined to one equation, the relation between the input symbols and received signals becomes more obvious:

$$r_n = \sum_k I_k q(nT - kT) + \eta_n \tag{2.10}$$

where q is convolved transmit and channel responses with the receive filter;

$$q(\tau) = h(\tau) * p(\tau) \tag{2.11}$$

and noise component of the received symbol is found by passing the noise through the receive filter:

$$\eta_n = \int n(t)p(nT-t)dt \qquad (2.12)$$

## 2.3.2. Equalization Using FIR Filters

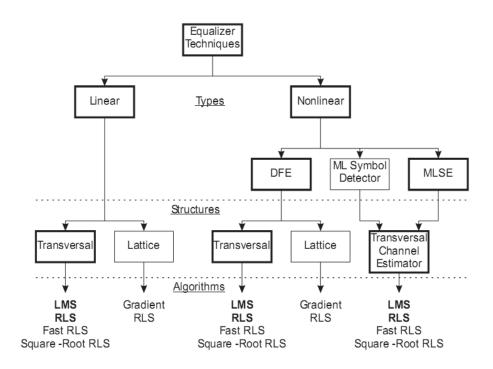

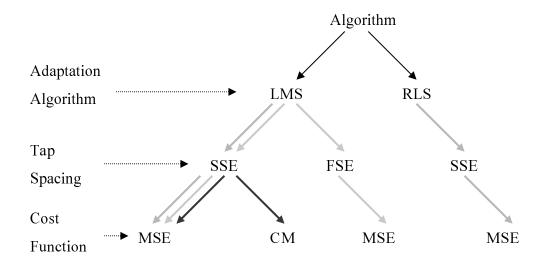

The equalization techniques that can be implemented with the use of FIR filters can be summarized in the following table:

Figure 2.21. Equalizer types, structures, and algorithms [36]

If the channel is time invariant, there is no need for adaptive equalization technique involvement. However, in some applications the channel characteristic may vary with the time, and the equalizer should adapt its coefficients for data recovery according to the varying channel response. Some examples to these adaptive algorithms are LMS and RLS.

Non linear equalizers are beyond the scope of this thesis and also ZF, LMS, RLS and CMA algorithms will be shortly described in the following chapter.

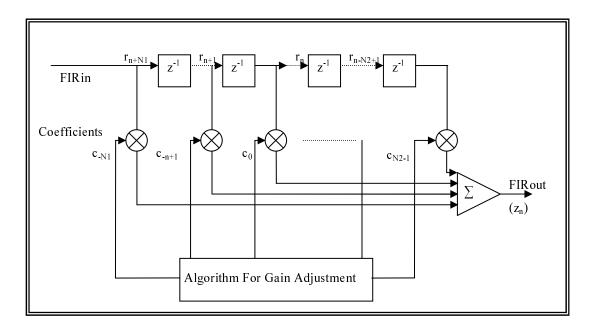

<u>2.3.2.1. Linear Equalizers.</u> If an equalizer uses only received signal samples in its calculations and do not need any previously detected symbols, it is referred as linear equalizer. There are two commonly used types of linear equalizers: the linear transversal equalizer and the fractionally spaced equalizer.

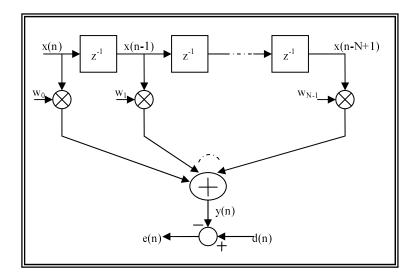

Linear transversal equalizer is one of the most common equalizer in the literature due to its implementation simplicity. As represented in Figure 2.21, it consists of tapped-delay line with tap spacing equal to the symbol rate. Its input is the sampled output of the matched filter at the receiver side. As mentioned in the previous chapter, these delay cells can be either continuous or discrete. If the tap delays are discrete, the clock should be synchronized to these sample-hold cells first. Each delay cell can be considered as a register and shift register behavior results after cascading these delay cells. The contents of these registers are shifted at each symbol period, and they are added after being multiplied by specific coefficients. This sum of multiplications makes up the estimate of the current symbol. This operation can be simplified by the following equation:

$$z_n = \sum_{k=N_1-1}^{N_2-1} c_k r_{n-k}$$

(2.13)

where  $z_n$  is the estimated output of the filter,  $r_n$  is the input sequence to the equalizer,  $c_k$  is the coefficient of  $k^{th}$  tap,  $N_1$  is the number of non-causal equalizer taps (future taps) and  $N_2$ is the number of causal equalizer taps (previous taps) and  $z^{-1}$  is tap delay which is equal to symbol period.

Figure 2.22. Symbol spaced equalization using FIR filter

The causal part of the linear transversal equalizer is used to remove ISI due to the symbol interference with the previous symbols, whereas the non-causal part represents the interference with the future symbol tails. Non-causal taps are only needed when the current received signal is not the strongest element, otherwise  $N_1$  can be assumed to be set to 0.

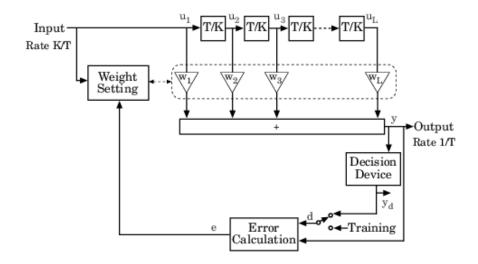

In the receiver, decisions are taken at the symbol rate  $f_b$  to retrieve the data. So far, it has been assumed that all the functions in the receiver are carried out at that rate, including the equalization. However, it is known that the signal spectrum exceeds the symbol rate by the amount of the roll-off the Nyquist filter.

Therefore sampling at the symbol rate generates aliasing and the image of the base band spectrum occurs around the frequency  $f_b$ . According to the sampling theory, the phase of this image is linked to the sampling times. A shift in timing produces a rotation of the phase, and the base-band spectrum and the image no longer add up in phase, in the filter transition band  $\Delta f$ . Therefore the equalizer is sensitive to the sampling times, and equalization may become impossible for frequencies in the vicinity of half the symbol rate. As is well known in multi-rate filtering, the solution to the problem is to increase the sampling rate sufficiently to avoid aliasing, which leads to the so-called fractionally spaced equalizer, which is yet another type of linear equalizers [37].

A fractionally spaced equalizer is a linear equalizer that is similar to a symbol-spaced linear equalizer. By contrast, however, a fractionally spaced equalizer receives K input samples before it produces one output sample and updates the weights, where K is an integer. In many applications, K is 2. The output sample rate is expressed as 1/T, while the input sample rate is K/T. The weight-updating occurs at the output rate, which is the slower rate. Below is a schematic of a fractionally spaced equalizer [38].

Figure 2.23. Fractionally spaced equalization using FIR filter [38]

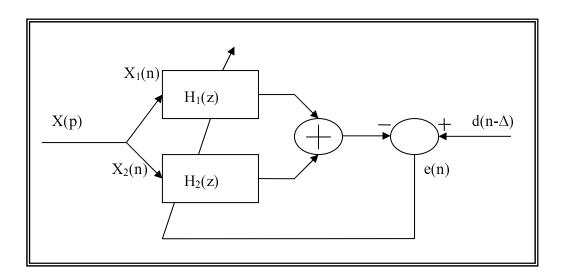

Another expression of an equalizer with double sampling is shown in below figure. The input signal sample sequence is split into two sequences which are fed to two separate equalizers  $H_1(z)$  and  $H_2(z)$  operating at the symbol rate.

Figure 2.24. Fractionally spaced equalization using FIR filter

The output error in that case is [37]:

$$e(n) = d(n - \Delta) - \left(H_1'X_1(n) + H_2'X_2(n)\right)$$

(2.14)

The optimal coefficient vectors are given by:

$$\begin{bmatrix} H_{1opt} \\ H_{2opt} \end{bmatrix} = \begin{bmatrix} R_{11} & R_{12} \\ R_{21} & R_{22} \end{bmatrix}^{-1} \begin{bmatrix} r_{d1} \\ r_{d2} \end{bmatrix}$$

(2.15)

for i=1,2 and j=1,2:

$R_{ij} = E[X_i X_j], r_{di} = E[d(n - \Delta)X_i(n)]$

The updating of the coefficients is carried out at the symbol rate. It is worth pointing out that the input signal spectrum, except for the noise, goes to zero in the vicinity of the symbol frequency  $f_b$ .

As in any transversal equalization, the fractionally spaced equalizers also suffer from noise amplification. The best solution is to complete FSE by a feedback section, to make the so-called fractionally spaced DFE. This combination is generally recognized to be the most efficient approach to adaptive equalization [37].

2.3.2.2. Equalization Criteria. Considerable research has been performed on the criterion for optimizing the filter coefficients  $\{c_k\}$ . Since the most meaningful measure of performance for a digital communications system is the average probability of error, it is desirable to choose the coefficients to minimize this performance index. However, the probability of error is a highly nonlinear function of  $\{c_k\}$ . Consequently, the probability of error as a performance index for optimizing the tap weight coefficients of the equalizer is impractical. Two criteria have found widespread use in optimizing the equalizer coefficients [36]. One is the peak distortion criterion and the other is the mean square error criterion.

The worst case ISI that occurs at the output of an equalizer is defined as the peak distortion. Minimization of peak distortion by optimizing the filter coefficients is called the peak distortion criterion. The ideal ISI removal could be achieved if equalizer with infinite taps could be realizable. In real case, peak distortion criterion stands for ISI removal over the range of the filter taps.

Assuming infinite non-causal and causal filter taps, the overall response of channel and equalizer could be represented as follows:

$$q_n = \sum_{j=-\infty}^{\infty} c_j f_{n-j} \tag{2.16}$$

where  $\{f_n\}$  is the impulse response of the discrete time linear channel model,  $\{c_n\}$  is the equalizer impulse response and  $q_n$  is the cascade of these filters.

If the input is represented as  $I_k$ , the output of the receiver output sampled at  $k^{th}$  instant is represented as follows:

$$\hat{I}_{k} = q_{0}I_{k} + \sum_{n \neq k} I_{n}q_{k-n} + \sum_{j=-\infty}^{\infty} c_{j}\eta_{k-j}$$

(2.17)

The first term is desired symbol scaled by the channel and equalizer transfer functions. The second term represents ISI and the final term is the noise. The peak value of the second term is shown as follows [36]:

$$\mathcal{D}(c) = \sum_{\substack{n=-\infty\\n\neq 0}}^{\infty} |q_n|$$

$$= \sum_{\substack{n=-\infty\\n\neq 0}}^{\infty} \left| \sum_{j=-\infty}^{\infty} |c_j f_{n-j}| \right|$$

(2.18)

In order to obtain the desired signal back at the output of equalizer D(c) should be forced to 0. The tap values that forces D(c) to 0 can be obtained from the solution of the following equation:

$$q_n = \sum_{j=-\infty}^{\infty} c_j f_{n-j} = \begin{cases} 1 & (n=0) \\ 0 & (n\neq 0) \end{cases}$$

(2.19)

In z-domain, this condition can be summarized as

$$Q(z) = C(z)F(z) = 1$$

(2.20)

or simply:

$$C(z) = \frac{1}{F(z)} \tag{2.21}$$

From above equations, it is understood that minimization of ISI is the same as having the inverse of channel transfer function as the equalizer transfer function. In other words, complete elimination of ISI requires the use of an inverse filter of F(z).

Assuming L non-causal and L+1 causal filter taps, the overall response of channel and equalizer could be represented as follows:

$$b_{k} = \sum_{l=-L}^{L} c_{l} q_{k-l} = \begin{cases} 1 & k = 0\\ 0 & k = \mp 1, \pm 2, \dots, \mp L \end{cases}$$

(2.22)

where  $\{q_n\}$  is the impulse response of the discrete time linear channel model,  $\{c_n\}$  is the equalizer impulse response and  $b_k$  is the cascade of these filters.

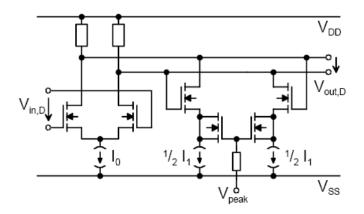

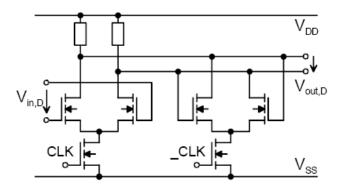

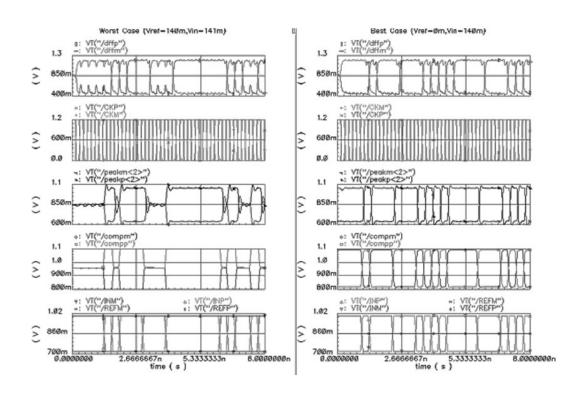

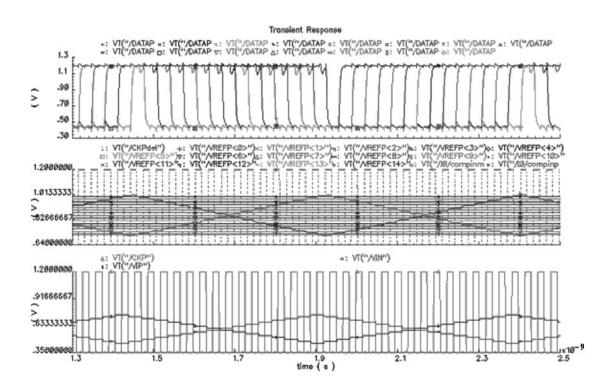

This convolution can be visualized using a matrix representation as follows [35]: