## ANALOG LAYOUT SYNTHESIZER FOR A PARASITIC AWARE DESIGN LOOP

by

Ahmet Unutulmaz

B.S., Electrical and Electronics Engineering, Boğaziçi University, 2006

Submitted to the Institute for Graduate Studies in Science and Engineering in partial fulfillment of the requirements for the degree of Master of Science

Graduate Program in Electrical and Electronics Engineering Boğaziçi University 2009

## ANALOG LAYOUT SYNTHESIZER FOR A PARASITIC AWARE DESIGN LOOP

## APPROVED BY:

| Prof. Günhan Dündar            |  |

|--------------------------------|--|

| (Thesis Supervisor)            |  |

|                                |  |

| Prof. Levent Akın              |  |

|                                |  |

| Asst. Prof. Arda D. Yalçınkaya |  |

DATE OF APPROVAL: 28.01.2009

## ACKNOWLEDGEMENTS

I would like to express my sincere gratitude to Professor Günhan Dündar and Professor Francisco Fernandez for their invaluable guidance and help during the preparation of this dissertation. I would like to mention their patience, giving me inspiration and hope when I was stuck at dead-ends.

I also would like to thank to my family for their infinite patience, support and love. Besides, I thank them very much for everything they sacrificed.

Finally, I would like to thank to TÜBİTAK for its support through BIDEB-2210.

## ABSTRACT

# ANALOG LAYOUT SYNTHESIZER FOR A PARASITIC AWARE DESIGN LOOP

Analog design automation is being studied for a couple of decades and many researchers developed their own tools. However, there are no standards for these tools. The work done in this M.S. thesis aims to define standard interfaces for layout automation tools, making the integration of different tools possible. In addition to these interfaces, an interface for a layout database is defined. This interface is designed to hold any kind of layout structure and to cooperate with any kind of layout tool.

Additionally, implementations for these interfaces are done. A floor-planner tool, a device generator, a fast database and a simple router are implemented in Java. The implemented tools are combined and a template based layout synthesizer is constructed. This layout synthesizer requires templates files coded in Java. Implementing the floor-planner, a new floor-plan representation and a new inequality solver are developed and used.

Moreover, a novel synthesis loop is defined. In this synthesis strategy, contrary to the old synthesis approaches, the effects of the parasitic are considered in the synthesis loop. The layout synthesizer implemented in this thesis is preferable in this novel synthesis loop, due to the very short running time.

## ÖZET

# PARASİTİK ETKİLERİ İÇEREN BİR TASARIM DÖNGÜSÜ İÇİN ANALOG SERİM SENTEZLEYİCİ

Analog devre tasarımı son yirmi yıldır üzerinde çalışılan bir konudur ve birçok araştırmacı bu alanda kendi otomasyon aracını geliştirmiştir. Maalesef, bu araçlar için tasarlanmış standart bir ara-yüz yoktur. Bu yüksek lisans tezi, tasarım otomasyon araçları için ara-yüzler tanımlamayı hedefliyor. Tasarım araçları için tanımlanan ara-yüzlere ek olarak, serim veri tabanı için de bir ara-yüz tanımlanmıştır. Bu ara-yüz herhangi bir yapıyı tutacak ve herhangi bir serim aracı ile uyumlu olacak şekilde tasarlanmıştır.

Ek olarak, bahsedilen bu ara-yüzler gerçeklenmiştir. Yerleşim aracı, cihaz sentezleyici, hızlı bir serim veritabanı ve basit bir bağlayıcı Java kodlama dilinde gerçekleştirilmiştir. Gerçeklenen bu parçalar birleştirilerek, otomatik serim sentezleyici oluşturulmuştur. Bu sentezleyici Java dilinde yazılmış şablonlarla çalışmaktadır. Yerleşim aracını gerçeklemek için yeni bir yerleşim gösterimi ve yeni bir eşitsizlik çözücü ortaya konulmuştur.

Bütün bunlara ek olarak, yeni bir sentez döngüsü tanımlanmıştır. Bu yeni döngüde parazit etkiler sentez döngüsünün içinde değerlendirilmektedir. Bu tezde geliştirilen otomatik serim sentezleyici hızlı çalışması sebebi için tanımlanan yeni tasarım döngüsünde kullanılabilir.

# **TABLE OF CONTENTS**

| AC  | KNO  | WLEDGI    | EMENTS                                     | iii |

|-----|------|-----------|--------------------------------------------|-----|

| AB  | STRA | СТ        |                                            | iv  |

| ÖZ  | ЕТ   | •••••     |                                            | v   |

| LIS | T OF | FIGURE    | ES                                         | ix  |

| LIS | T OF | TABLES    | 5                                          | xii |

| LIS | T OF | SYMBO     | LS/ABBREVATIONS                            | xiv |

| 1.  | INTF | RODUCT    | TION                                       | 1   |

| 2.  | DES  | IGN TOO   | DLS                                        | 3   |

|     | 2.1. | Design l  | Flow                                       | 3   |

|     | 2.2. | Automa    | tion Tools                                 | 3   |

|     |      | 2.2.1.    | Numerical Simulators                       | 4   |

|     |      | 2.2.2.    | Symbolic Analyzers of Analog Circuits      | 4   |

|     |      | 2.2.3.    | Analog Circuit Synthesizers and Optimizers | 5   |

|     |      | 2.2.4.    | Analog Layout Synthesis                    | 6   |

|     |      | 2.2.5.    | Yield Estimation and Optimization          | 7   |

| 3.  | LAY  | OUT DA    | ATABASE                                    | 9   |

|     | 3.1. | Data Str  | uctures                                    | 9   |

|     |      | 3.1.1.    | List of Blocks Structure                   | 10  |

|     |      | 3.1.2.    | Bin-Based Structure                        | 10  |

|     |      | 3.1.3.    | Neighbor Pointers Structure                | 10  |

|     |      | 3.1.4.    | Corner Stitching Structure                 | 10  |

|     | 3.2. | Interface | e                                          | 12  |

|     |      | 3.2.1.    | Building Instances from a Master           | 13  |

|     |      | 3.2.2.    | Supporting Grouping and Hierarchy          | 13  |

|     |      | 3.2.3.    | Transforming Coordinates                   | 13  |

|     | 3.3. | Impleme   | entation                                   | 14  |

| 4.  | FLO  | OR-PLA    | NNER                                       | 17  |

|     | 4.1. | Constrai  | ints                                       | 18  |

|     |      | 4.1.1.    | Absolute Constraints                       | 19  |

|     |      | 4.1.2.    | Relative Constraints                       | 19  |

|    |      |          | 4.1.2.1. Alignment Constraints    | 19 |

|----|------|----------|-----------------------------------|----|

|    |      |          | 4.1.2.2. Abutment Constraints     | 19 |

|    |      | 4.1.3.   | Symmetry Constraints              | 20 |

|    | 4.2. | Floor P  | lan Representation                | 21 |

|    |      | 4.2.1.   | Slicing Structures                | 21 |

|    |      | 4.2.2.   | Non-Slicing Structures            | 22 |

|    |      |          | 4.2.2.1. Sequence Pair            | 22 |

|    |      |          | 4.2.2.2. O-Tree                   | 24 |

|    |      |          | 4.2.2.3. B*-Tree                  | 26 |

|    |      |          | 4.2.2.4. BSG                      | 26 |

|    |      |          | 4.2.2.5. TCG                      | 26 |

|    |      |          | 4.2.2.6. CBL                      | 28 |

|    |      | 4.2.3.   | P-Sequence                        | 28 |

|    |      |          | 4.2.3.1. Compaction of P-Sequence | 29 |

|    |      |          | 4.2.3.2. Analysis of P-Sequence   | 31 |

|    | 4.3. | Layout   | Description Script (LDS)          | 31 |

|    |      | 4.3.1.   | Alignment Commands                | 31 |

|    |      | 4.3.2.   | Abutment Commands                 | 31 |

|    |      | 4.3.3.   | Insertion Commands                | 32 |

|    |      | 4.3.4.   | Command for General Constraints   | 32 |

|    |      | 4.3.5.   | Update Commands                   | 33 |

|    |      | 4.3.6.   | Basic Commands                    | 34 |

|    | 4.4. | Constra  | ints and Inequalities             | 34 |

|    |      | 4.4.1.   | Classification of Constraints     | 34 |

|    |      |          | 4.4.1.1. Soft Constraints         | 34 |

|    |      |          | 4.4.1.2. Hard Constraints         | 35 |

|    |      | 4.4.2.   | Constraints and Inequalities      | 35 |

|    |      | 4.4.3.   | Inequalities and Graphs           | 36 |

|    |      | 4.4.4.   | Solving the Inequalities          | 36 |

|    |      | 4.4.5.   | Loop Breaking                     | 37 |

|    | 4.5. | Floor-p  | lanner Implementation             | 38 |

| 5. | DEV  | VICE GE  | NERATOR AND ROUTER                | 40 |

|    | 5.1. | Interfac | e                                 | 40 |

vii

|    |      | 5.1.1. E | xample     |                   | 41 |

|----|------|----------|------------|-------------------|----|

|    | 5.2. | Devices  | 5          |                   | 41 |

|    |      | 5.2.1.   | NMOS T     | ransistor         | 41 |

|    |      | 5.2.2.   | PMOS T     | ansistor          | 42 |

|    | 5.3. | Routing  | ç          |                   | 42 |

|    |      | 5.3.1.   | Classifica | tion of Routers   | 43 |

|    |      |          | 5.3.1.1.   | Area Routing      | 44 |

|    |      |          | 5.3.1.2.   | Channel Routing   | 44 |

|    |      | 5.3.2.   | Required   | Capabilities      | 45 |

|    |      | 5.3.3.   | Routing S  | Styles            | 46 |

| 6. | IMP  | ORTER    | AND EXP    | ORTER             | 47 |

|    | 6.1. | Importe  | er         |                   | 47 |

|    | 6.2. | Exporte  | er         |                   | 48 |

| 7. | LAY  | OUT GE   | ENERATO    | R                 | 49 |

| 8. | CON  | ICLUSIC  | ON AND F   | UTURE WORK        | 53 |

|    | 8.1. | Conclus  | sion       |                   | 53 |

|    | 8.2. | Future V | Work       |                   | 54 |

| AP | PENC | OIX A: C | OMPUTA     | TIONAL COMPLEXITY | 55 |

| AP | PENC | OIX B: A | LGORITM    | IIC GRAPHS        | 57 |

| AP | PENC | DIX C    |            |                   | 60 |

| RE | FERE | NCES .   |            |                   | 71 |

## LIST OF FIGURES

| Figure 2.1. | Design flow                                                                                                                    | 3  |

|-------------|--------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 3.1. | Linked list of blocks                                                                                                          | 10 |

| Figure 3.2. | Bin-based representation                                                                                                       | 11 |

| Figure 3.3. | Neighbor pointers structure                                                                                                    | 11 |

| Figure 3.4. | Corner stitches                                                                                                                | 11 |

| Figure 3.5. | Transformation is needed                                                                                                       | 13 |

| Figure 3.6. | Transformations                                                                                                                | 14 |

| Figure 3.7. | Fast Transformations                                                                                                           | 15 |

| Figure 3.8. | Structure of the database                                                                                                      | 16 |

| Figure 4.1. | Absolute constraint                                                                                                            | 19 |

| Figure 4.2. | Relative constraint                                                                                                            | 19 |

| Figure 4.3. | Alignment constraints (a) alignment of the left boundaries, (b) alignment of the centers,(c) alignment of the right boundaries | 20 |

| Figure 4.4. | Abutment constraint                                                                                                            | 20 |

| Figure 4.5. | Symmetry constraint                                                                                                            | 20 |

| Figure 4.6. | Slicing floor-plan structure                                                                                                   | 21 |

| Figure 4.7.  | Floor-plan for the sequence pair: $(\Gamma^+, \Gamma^-) = (abdecf, cbfaed)$                  | 23 |

|--------------|----------------------------------------------------------------------------------------------|----|

| Figure 4.8.  | An O-tree representation                                                                     | 25 |

| Figure 4.9.  | A B*-tree representation                                                                     | 26 |

| Figure 4.10. | Bounded Slicing Grid                                                                         | 27 |

| Figure 4.11. | Transitive Closure Graphs                                                                    | 27 |

| Figure 4.12. | Floor-plan is represented as (S, L, T)=(fcegbad, 001100, 001010010)                          | 28 |

| Figure 4.13. | Modules are projected onto x and y axis                                                      | 29 |

| Figure 4.14. | Floor-plan is represented as (H, V) = ({baif, b, aie, g, e, h}, {bg, hg, ba, ai, e, i, ehf}) | 30 |

| Figure 4.15. | Four modules separate the axis at most to 7 pieces.                                          | 31 |

| Figure 4.16. | Constraints in the floor-planer                                                              | 35 |

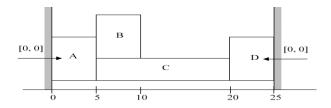

| Figure 4.17. | (a) The plan and the constraints (b) The representation of constraints in a graph            | 37 |

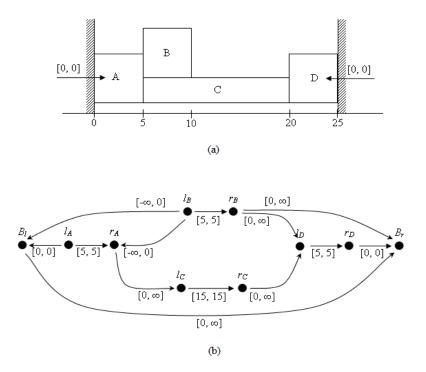

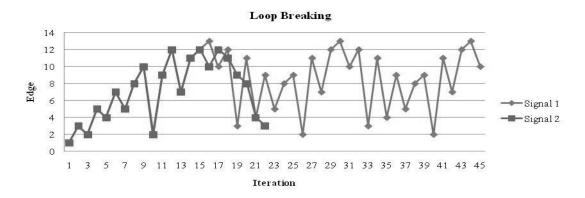

| Figure 4.18. | Block diagram of the loop breaker                                                            | 37 |

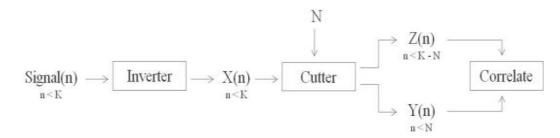

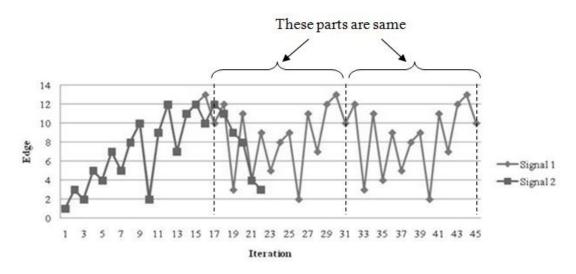

| Figure 4.19. | Sample signals (visited edges)                                                               | 38 |

| Figure 4.20. | Periodicity in the signal                                                                    | 38 |

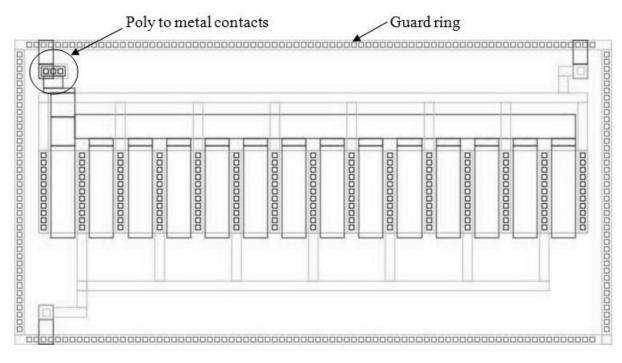

| Figure 5.1.  | NMOS Transistor                                                                              | 42 |

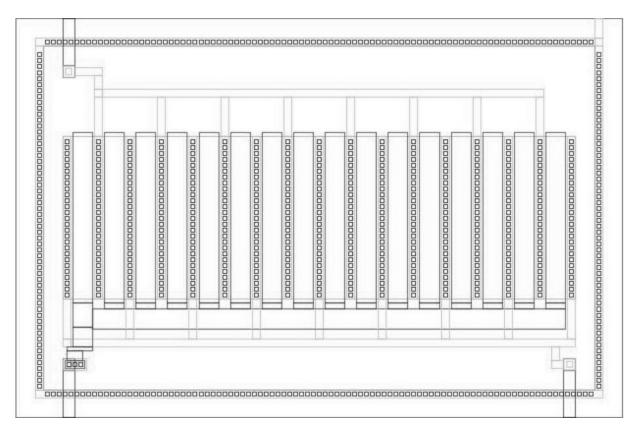

| Figure 5.2.  | PMOS Transistor                                                                              | 43 |

х

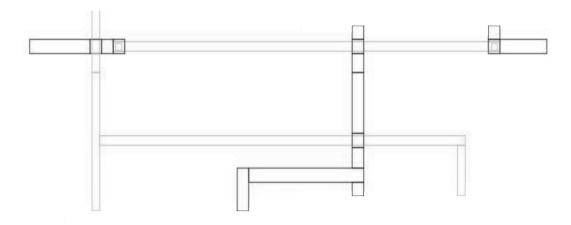

| Figure 5.3. | Template based routing                        | 43 |

|-------------|-----------------------------------------------|----|

| Figure 6.1. | Design loop                                   | 47 |

| Figure 7.1. | Differential pair                             | 49 |

| Figure 7.2. | Code for the template                         | 49 |

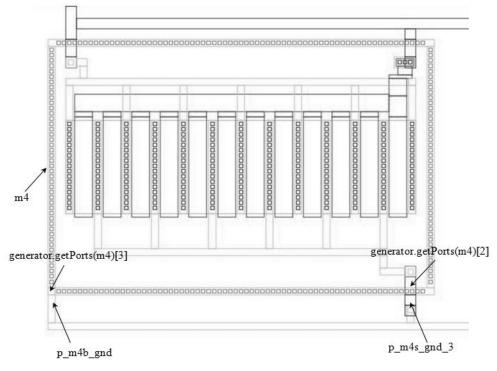

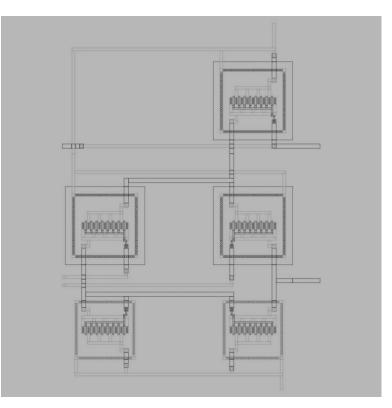

| Figure 7.3. | Template based construction                   | 50 |

| Figure 7.4. | Block diagram of the layout generator         | 50 |

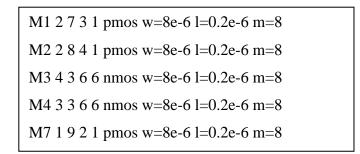

| Figure 7.5. | SPICE code                                    | 51 |

| Figure 7.6. | SPICE code                                    | 51 |

| Figure 7.7. | Constructed layout (spice code in Figure 7.5) | 51 |

| Figure 7.8. | Constructed layout (spice code in Figure 7.6) | 52 |

xi

## LIST OF TABLES

| Table 4.1.  | Decoding the Sequence Pair representation                     | 23 |

|-------------|---------------------------------------------------------------|----|

| Table 4.2:  | Required types of perturbations for SP representation         | 24 |

| Table 4.3.  | Required types of perturbations for the O-tree representation | 25 |

| Table 4.4.  | Perturbations inspired from TCG                               | 27 |

| Table 4.5.  | Perturbations                                                 | 28 |

| Table 4.6.  | Commands for alignment                                        | 32 |

| Table 4.7.  | Command for abutment                                          | 32 |

| Table 4.8.  | Module insertion                                              | 33 |

| Table 4.9.  | Adding general constraints                                    | 33 |

| Table 4.10. | Command for updating                                          | 33 |

| Table 4.11. | Basic commands                                                | 34 |

| Table 5.1.  | Interface for adding new devices                              | 40 |

|            |                               | xiii |

|------------|-------------------------------|------|

| Table 5.2. | Device types for CMOS process | 40   |

| Table 5.3. | Interface to get the ports    | 41   |

| Table 6.1. | Formats for exchange          | 48   |

| Table 6.2. | Interface for the importer    | 48   |

| Table 6.3. | Interface for the exporter    | 48   |

## LIST OF SYMBOLS/ABBREVATIONS

| TOLAS | Tool Oriented Layout Automation System |

|-------|----------------------------------------|

| EDA   | Electronic Design Automation           |

| Diff  | Differential Pair                      |

## **1. INTRODUCTION**

Advances in technology have provided the opportunity of integrating more devices into a single chip. This opportunity is becoming more difficult to utilize with every technology generation. Fortunately, in the digital world, the designers can utilize this opportunity and cope with a large number of transistors, using design automation tools. Development of these tools requires extensive amount of research on the topic. Since 1970's many researchers have been trying to advance the electronic design automation (EDA) tools. Note also that, the systematic structures in the digital circuitry ease the development of digital EDA tools. Unfortunately, when analog design is considered, there is almost no mature automation tool in the field.

One can argue that analog circuitry contains at most a few hundred transistors and can be designed by a few engineers without the need of an automation tool. However, one should consider that the VLSI IC industry tries to maximize its profit and a main consideration is the time to market. A very fast response to the market will increment the profit considerably. Unfortunately, without a design automation tool, a single design cycle may not be adequate for the designer to complete the design, and time consuming trials may be required. Additionally the SOC designs (System on Chip) are very popular and more analog circuitry is being integrated.

Many researchers are trying to develop EDA tools to ease the design challenge of the analog world. Some EDA tools contain hard-coded synthesizers which construct the circuitry through the instructions in the code. Another group of tools try to construct templates and use them for further synthesis. Also, there are tools searching for the solution: heuristic and optimization based tools. However, there is not a complete solution for analog design automation. Unfortunately, due to the lack of a standard in the field, it is almost impossible to combine the available tools to obtain a complete solution.

An aim of this thesis is to define standard interfaces for the layout automation tools, making the integration of different tools possible. These interfaces are defined by reviewing literature about related tools. In addition to these interfaces, an interface for a database is defined. This interface is designed to hold any kind of layout structure and to cooperate with any kind of tool (floor-planner, router, etc...).

During the thesis study, an implementation of a floor-planner and an implementation of a layout database were performed. These implementations were written in Java and they comply with the related standards defined. Further, the codes are combined into a template based layout synthesizer.

While implementing the floor-planner, a new floor-plan representation (*P-Sequence*) is developed and used. Also a new inequality solver is designed and used in the implemented floor-planner.

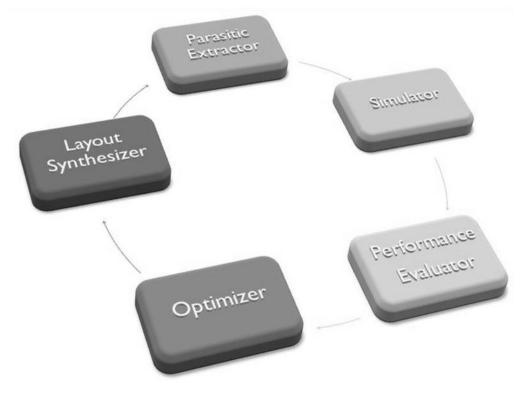

Moreover, a novel synthesis loop is defined. In this synthesis strategy, contrary to the old synthesis approaches, the effects of the parasitic are considered in the synthesis loop. The layout synthesizer implemented in this thesis is preferable in this novel synthesis loop, due to the very short running time (a few seconds).

In section 2, some of the available design tools and approaches are introduced. In section 3, the interface for the layout database and an implementation of this interface are presented. Section 4 defines the interface for the floor-planner and includes a floor-planner implementation. This section also reviews some common floor-plan representations and includes the description of P-Sequence representation. Additionally, an inequality solver is presented in this section. In section 5, a device generator and a template-based router are described. Section 6 contains information about the exchange formats between the available EDA tools. All of the implemented tools are combined and a layout synthesizer is constructed, this synthesizer is described in section 7. Section 8 concludes this work and proposes some future work.

## **2. DESIGN TOOLS**

## 2.1. Design Flow

Analog design is a time consuming process; many iterations are required to finalize the design. In general, the design is separated into three parts. These parts are *behavioral description*, *structural description* and *physical description*.

A design is described behaviorally through a HDL (hardware description language), such as VHDL-AMS. This description is then converted to structural description, which includes the circuitry as blocks. These blocks are implemented with transistors and this implementation is called the physical description.

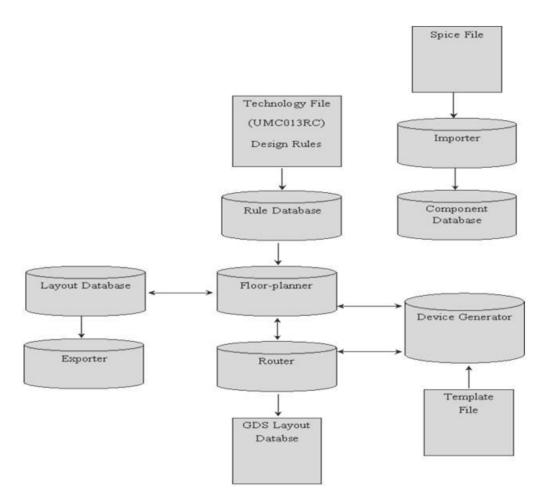

The design flow is schematically shown in Figure 2.1.

Figure 2.1. Design flow

## 2.2. Automation Tools

Researchers developed many tools for EDA and these tools are classified according to their functionality in [1], [2], [3] and [4]. Also a brief review for some of these tools is going to be presented in the following sub sections.

## 2.2.1. Numerical Simulators

Hand analysis of analog circuits is a complicated task and involves solving many differential equations simultaneously. As the circuit includes many devices, it becomes almost impossible to analyze the circuitry by hand. Fortunately, the early development of analog simulators helped the designer through the design of today's complicated analog circuits.

Analog simulation is a critical task for design verification. Verification is needed to avoid performance degradation of an analog circuit after fabrication. The degradation should be accounted by the designer during the design process and analog simulators with circuit extractors give this opportunity to the designer.

*Circuit simulation* began with the development of the SPICE tool and nowadays there are many commercially available variants of SPICE. These circuit simulators are used in the design and verification processes. The circuit simulations may require considerable amount of time. To speed up the simulation of a module, including many analog circuits, *circuit models* are derived. The VHDL-AMS or Verilog-A are the standardized analog description languages. These circuit models not only speed up the simulation processes but also make it possible to simulate a group of analog circuitry without an implementation at the transistor level.

There also exist dedicated simulators for special purposes; i.e. switched capacitor simulation tools, RF simulation tools, etc...

## 2.2.2. Symbolic Analyzers of Analog Circuits

Designing analog circuitry requires an insight into the circuitry. Thus, it is desirable to have the design equations of a circuit. For circuits of few transistors, one can derive the required equations (i.e. small signal gain, bandwidth, etc...) by hand. However, as more transistors are added to the circuit, it will not be practical to analyze the behavior of the circuit by hand. Symbolic analyzers, capable of handling circuits with around 10 transistors, emerged late 1980's. These tools were simplifying the expressions as done in

the hand analysis. However, these tools were not able to handle complicated circuits due to the extensive computational requirements. A new technique of *simplification before and during the symbolic expression generation* reduced the computation time considerably and enabled the symbolic analysis of practical circuits.

#### 2.2.3. Analog Circuit Synthesizers and Optimizers

*Topology* selection is a very important problem in analog design. This problem arises when there are multiple topologies for an implementation. A good topology meets the specifications for the circuit at the minimal implementation cost (i.e. Power, Area, Robustness ...). Unfortunately, it is hard to formulate the solution of the topology selection problem quantitatively. Thus, the primary synthesis tools used rule sets for the selection of the best topology.

Later approaches constructed more quantitative ways to select a topology. Feasible performance space of each topology is defined. According to the specs, the best matching topology is selected and optimization techniques are also applied to the problem.

Once a topology is selected, the next step is the *performance translation*. According to the performance specifications of the overall circuit, the performance specifications of the sub blocks are determined. These sub-blocks may be composed of single devices, then the problem can be stated as the *device sizing* problem. Extracting the device sizes from the given performance specifications is an under constrained problem. The degrees of freedom in the problem can be handled by knowledge based and optimization based approaches.

In the knowledge based approaches, the design knowledge is coded into a computer executable form. This method uses the heuristic methods. Most of the knowledge based synthesis tools require design plans. Unfortunately, construction of these design plans is more time consuming than simply designing the circuit.

On the other hand, optimization approaches are based on numerical optimization techniques. These techniques try to solve the degrees of freedom of a design, under the constraint of the performance specifications. Optimization based approaches also try to extract the required design knowledge using analysis techniques (i.e. symbolic analysis) or try to use equation-free simulation-oriented approaches. Running an optimization loop depends upon evaluating the performance of an instance circuit. This performance evaluation is done by evaluating the design equations or by simulating the circuit.

Although evaluation of the performance through circuit simulations does not require design plans and precise design equations, it requires high computational power and advanced numerical algorithms. In recent years, with the development of high speed computers, this approach started to become popular.

#### 2.2.4. Analog Layout Synthesis

Due to the adaptation of the digital layout synthesis techniques to the analog counterpart, analog layout synthesis is the most mature part of the analog design automation. The goal of the layout synthesizer is to convert the schematic of a circuit into a producible layout. A fully automated layout synthesizer is expected to floor-plan, place and route the circuit elements by taking the performance considerations into account.

The earliest approaches rely on *procedural module generation*, which is based on pre-coded software. The software constructs the layout according to the input parameters. For this approach, development and maintenance of a module generator for each circuit topology is necessary. *Template driven module generation* is a similar approach and uses geometric templates for each circuit. The template fixes the position and the routing of the circuit. Template driven approach is a fast synthesis method. This approach is suitable, if the layout structure is given and changes from circuit to circuit are minor.

Due to the parasitic effects induced in analog layouts, the resulting circuit may not satisfy the performance specifications. Sometimes, big changes in the layout may be required for both satisfying the performance specs and having a compact layout. *Optimization-based macro-cell place and route layout generation* approach uses optimization techniques to optimally place and route to combine macro-cells. Macro-cell is defined to be a single device (i.e. transistor, capacitor) or a group of devices (matched pairs). This approach depends upon a pre-defined cost function and the optimizer which

tries to minimize the area and tries to satisfy the performance specs using this function. This approach requires large CPU times and the quality of the generated layout is sensitive to the introduced cost function. ILAC [5] and KOAN/ANAGRAM II [6] are samples for this approach which relies on macro-cells. The ILAC tool is inspired from digital automation tools; the problem with tool is that, it is not always possible to handle sensitive analog designs with the digital automation techniques. KOAN/ANAGRAM II tool set is a combination of KOAN which is a device generator and an optimization based placer, and ANAGRAM II which is a maze-style area router. Also tools like LADIES [7] and ALSYN [8] operate similarly.

The next generation of tools is based on *performance-driven or constraint-driven* approaches. These approaches try to quantitatively measure the performance degradations, considering the parasitic and secondary effect. The area routers ROAD [9] and ANAGRAM III [10], the placement tool PUPPY-A [11] and are examples of this approach. The LAYLA [4] tool also consists of performance-driven placer and router.

A new approach is to separate the device placement task into two separate tasks: device stacking followed by stack placement. By considering the circuit as a connected graph of sources and drains, the optimum merging is observed, called device stacking. In the stack placement phase, the devices are merged and placed accordingly. Also separate placing and routing phases result in non-optimal solutions. Thus, there are attempts to simultaneously place and route the circuits.

The performance degradation due to the layout parasitic is also considered. The affect of parasitic to analog layout synthesis is mentioned in [12], [13] and [14].

#### 2.2.5. Yield Estimation and Optimization

Due to fluctuations in the fabrication process, the performance of fabricated circuits may vary. These variations may result in malfunctioning or badly performing circuits, which do not meet the performance specifications. The circuits need to be designed in such a way that maximizes the number of the functional circuits; this is also known as *design for*

*manufacturability*. As well as designing for manufacturability, the designs have to be robust and that is called *design for robustness or design for quality*.

It is desired to know the fluctuations and the acceptability region for the parameter space or for the performance space. Then, according to the statistical fluctuations, the statistics for the well-functioning circuits can easily be obtained. However, the statistical fluctuations in the design parameters in the performance space and the acceptability region in the parameter space are not known. A simple approach is the *worst-case analysis*; as the name implies, some combination of the device parameters are used to calculate the worst case performance. A statistical approach is *Monte-Carlo simulations*. In this approach, according to the statistics of the parameter space are space are space is obtained. This approach is a CPU intensive process; some approximations are present to speed up this process.

## **3. LAYOUT DATABASE**

A database is defined to be the core of an analog layout tool. Thus, the implementation becomes very critical, if the speed of the layout tool is considered. To code layout automation tools compatible with the database, it is required to define a general interface for the database.

This chapter defines the necessary functionality for a layout database. After a detailed literature review, interface for the database is defined. Operations needed by the database and their corresponding definitions are presented. Also, an implementation for the defined interface is performed.

### 3.1. Data Structures

The database structure for an analog layout is in essence with a floor-plan structure. However, there are major differences. The database holds separate layers such as poly, diffusion, etc... On the other hand, the floor-plan structure holds the blocks; i.e. transistors, capacitors, matched pairs, etc...

The data structures for a database can be classified into two main groups; the *absolute coordinate based database* and *relative coordinate based database*. The absolute coordinate based database holds the absolute positions of the elements, as well as the layout properties. Thus, the database returns the coordinates immediately; however, the neighborhood information for the elements is not present in the database. On the other hand, the relative coordinate based database hold the neighborhood information (the local information). However, it cannot immediately return the coordinates of the blocks. Thus, layout manipulations (move, remove, etc...) cannot be immediately applied. In this database, the global information is first transformed into local information.

Some common structures are listed in [15]. The *List of Blocks Structure* holds the absolute coordinates of the elements in a list. Also, the *Bin Based Structure* holds absolute

coordinates in a more compact way. The *Neighbor Pointers Sucture* and the *Corner Stitching Structure* hold relative positions of the elements.

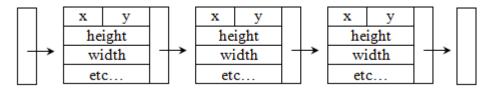

#### 3.1.1. List of Blocks Structure

This structure handles the components of a layout in a linked-list. The positions of the components are recorded into a structure and this structure is than added into the linked-list. The structure of the list is depicted in Figure 3.1.

Figure 3.1. Linked list of blocks

## 3.1.2. Bin-Based Structure

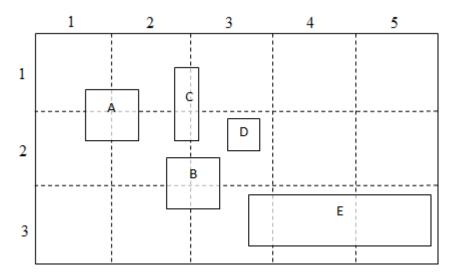

Bin-based layout representation, superimposes a virtual grid over the layout. A bin B(m,n) contains the list of elements it includes. In Figure 3.2, the bin B(2,2) contains the components in the set S (S = {A, C, B}). These bins are held in a two-dimensional array.

### 3.1.3. Neighbor Pointers Structure

The list of blocks and the bin based methods do not hold the local information. In contrast, this structure holds pointers to keep local information. However, it is not easy to maintain this structure. A simple change in the layout may require all the pointers in the data structure be updated. Neighbor-pointers structure is symbolically depicted in Figure 3.3.

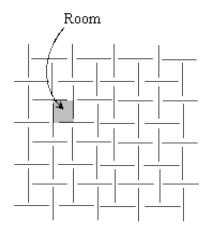

### 3.1.4. Corner Stitching Structure

Corner stitching data structures hold relative positions similar to the neighbor pointers data structure. However, they could be manipulated much faster than the neighbor pointers data structure. Unlike the previous structure, this structure holds only four pointers. These point the components around the lower-left and upper-right corner.

Figure 3.2. Bin-based representation

Figure 3.3. Neighbor pointers structure

Figure 3.4. Corner stitches

### 3.2. Interface

Through the new framework for the layout automation; router, floor-planner, circuit extractor or any code manipulating the layout is called a tool. All the tools communicate with the layout through an interface; existence of this interface facilitates compatibility. Tool development will be much easier and any new tool will cooperate easily with the previously written codes. This will yield faster code development and code reusability.

Also, one can implement his/her own database, obeying the rules in the interface. If the new implementation is correctly coded, the new database will also work with the previously developed tools. The required functionalities for a database are stated below:

- 1. Add new element or remove old one,

- 2. Set or to get the properties of an element (i.e. layer, shape, etc...),

- 3. Rotate or flip an element.

In addition to the listed core functions the following functionality is added to the interface. These functionalities make the database compatible with digital automation tools

- 1. Build instances from a master

- 2. Support grouping and hierarchy

- 3. Transform coordinates from a frame to another

#### 3.2.1. Building Instances from a Master

It may be desirable to clone an element, for instance to construct an array of transistors or to construct a symmetrical layout. The database interface supports generation of new elements from an initially generated element; the initial one is called a master. This functionality makes it possible to construct a layout from objects (like an object oriented language). The objects may be transistors, current mirrors or differential pairs; however dislike object oriented languages the instances are exact copies of the master.

## 3.2.2. Supporting Grouping and Hierarchy

The database interface can be used to group some elements; such as the transistors in a differential pair. This functionality contributes the concept of hierarchy into the database; the user may define a hierarchy in the layout. Moving a group will move all the components inside the group, which will speed up most of the floor-plan functionalities.

## 3.2.3. Transforming Coordinates

If a hierarchy is built in the layout, it will be required to calculate the positions of an element with respect to hierarchical frames. In Figure 3.5, the coordinate of the point in the outer frame can be calculated by summing the coordinate of the inner frame with the coordinate of the point. This is the simplest case and it may be more complicated if rotation and flip operations are included.

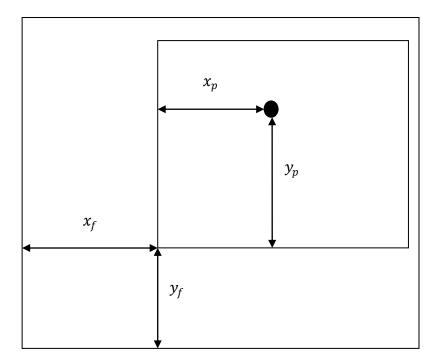

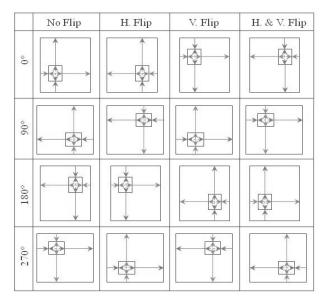

There are two types of transformations (except translation), these are rotation and flipping. These transformations are done by multiplying the coordinates of a point by the related matrix in Figure 3.6.

Figure 3.5. Transformation is needed

Figure 3.6. Transformations

#### **3.3. Implementation**

The implementation of the interface supports hierarchical structures. A group (module) is a parent and contains elements (transistors, capacitors, wires, etc...). An element may also be a parent, thus the implementation is capable of holding any degree of hierarchy.

A mathematical formulation of the implementation is given; the formulation is based on a previous work [16]. The layout is composed of groups (group of circuit elements or a single element). A set of groups is denoted by  $G = \{g_1, g_2, ..., g_n\}$ . A group consists of many elements; for instance, in a CMOS process, the layout will be composed of elements such as: diffusion region, metal region, poly region, etc... The set of elements are denoted by  $E(g) = \{e_1, e_2, ...\}$ . Similarly for a process, the set of available layers is donated by  $L = \{l_1, l_2, ..., l_k\}$ . Then the layer to which an element  $(e_i)$  belongs is denoted by  $l(e_i) \in L$  and similarly the width and height of an element are denoted by  $w(e_i)$  and  $h(e_i)$ , respectively. The absolute coordinates of an element  $(o_i)$  belonging to a group (g) is denoted by  $(x(g) + x(e_i), y(g) + y(e_i))$ ; where x(g) and y(g) are the x and y coordinates of a group (g), respectively. The  $x(e_i)$  and  $y(e_i)$  are the relative coordinates of an element  $(e_i)$  with respect to a group (g). In this representation, all the elements (circuit components, wires or any kind of structure) are denoted by groups (a collection of regions).

Generally, simple structures are involved in layouts; thus, the layout tool is designed to support rectangular shapes. Any elliptic shape is approximated by a polygon. The implemented tool also supports rectangular shapes and polygons. Due to the embedded objects, the code may be upgraded easily to elliptic shapes.

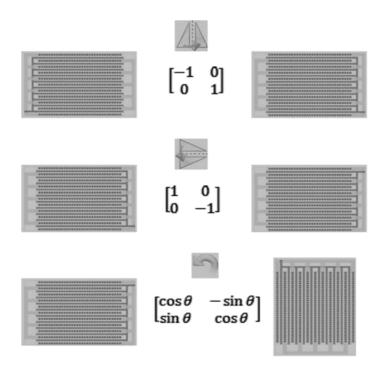

The implementation has the capability of rotating and flipping modules (groups). If a module is rotated or flipped, the entire sub modules are also affected; however, their coordinates are not modified. Thus, the database implementation runs extremely fast. The modifications are hierarchically stored. The coordinate of a module is calculated, when it is asked. This property speeds the floor-planner tremendously. Thus, a floor-planner may also run over the database, without holding a data structure.

The transformations may be calculated through the given transformation matrix. However, the sine and cosine functions -in the matrix- are time consuming and rarely required. Through the available tools, only simple rotations are involved. Thus to speed up the code, the sine and cosine are replaced by conditional code according to Figure 3.7.

Figure 3.7. Fast Transformations

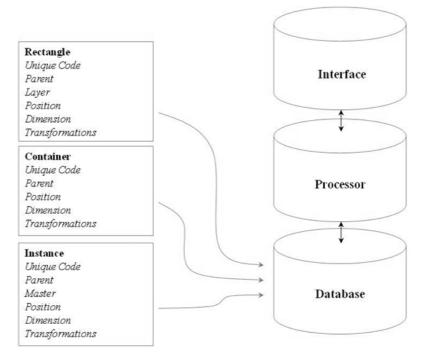

The database is graphically illustrated in Figure 3.8. The elements are held in the database and when these elements are called through the interface, they are processed. The processing unit applies the related transformations to these elements.

Figure 3.8. Structure of the database

## **4. FLOOR-PLANNER**

The positions of the modules in a layout affect the performance of the circuit. Due to the omitted parasitic effects, the performance of the circuit degrades from the targeted value. These effects are the parasitic wire resistances and capacitances, potential variations in the bulk material, cross-talk effects etc... These parasitic wire resistances and capacitances can be minimized by carefully placing the modules in the layout. The placement of the modules in the layout is called floor-planning. Generally, floor-planners focus on the placement of the modules (transistors, macro-cells, capacitors, etc...), rather than placing each layer (poly regions, metal regions, and contacts). This speeds up the search for a solution by reducing the solution space. There are some approaches also trying to place the layers. The approach in [17] formulates the layout as equations. These equations and the cost functions are solved with a non-linear optimizer.

Some approaches consider the floor-planning problem as a *rectangular packing problem* (RP) [18]. With M being a set of rectangular modules, the RP is to place the modules in M without any overlaps into a minimum bounding rectangle. This approach only aims to minimize the chip area. Another approach considers the wire length, pre-place blocks and the density of the floor-plan [19]. The approaches in [20] and [21] optimize the wire length and the area. The approach in [21] also considers the density. Moreover, some approaches consider parasitic affects [17].

This chapter defines a general interface that can represent any floor-planner. The interface is also compatible with optimizers. The floor-plan can be modified not only by the internal optimizer but also by different optimizers, i.e. the optimizer of the router, etc...

The interface is constructed through a detailed literature review about the floorplanning structures and optimizers.

Additionally, an implementation for the floor-planner interface is presented. This implementation does not include an optimizer. However, it reads the placement from a template.

#### 4.1. Constraints

It is important for the designer to control the absolute positions of some blocks, such as I-O pads. The designer also desires to control the relative positions of modules, i.e. symmetric modules. These constraints are needed to be passed through the floor-planner. Thus, the interface of the floor-planner should be capable of holding such constraints. In general, the constraints can be grouped as follows:

- 1. Absolute positions

- 2. Ranges for module positions

- 3. Positions with respect to the boundaries

- 4. Alignment of modules

- 5. Abutment of modules

- 6. Clustering of modules

- 7. Symmetric placement of modules

A method to handle these placement constraints is presented in [22]. Below, a short description of the idea, to hold these constraints, is stated.

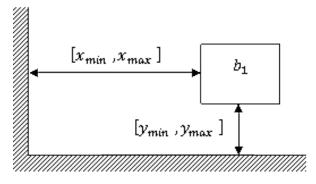

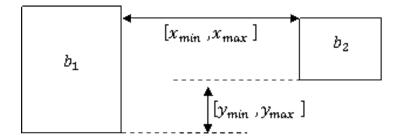

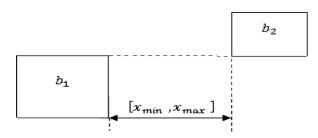

For two blocks A and B, the horizontal and vertical displacement between the lower left corners of the blocks are denoted by h(A,B) and v(A,B), respectivelly. The displacement may be positive or negative. If the lower left corner of A is to the left of that of B, the displacement h(A,B) will be positive. Similarly the vertical displacement (v(A,B)) can take positive or negative values. The relative placement constraints (alignment, abutting, clustering and symmetry constraints) between these modules (A, B) can be written as  $v(A,B) = [\alpha,\beta]$  where  $\alpha,\beta$  are real numbers and  $\alpha \leq \beta$ , meaning that the vertical displacement between A and B is in the interval  $[\alpha,\beta]$ . Absolute placement constraints (absolute positions, position ranges with respect to the boundaries) are handled by replacing A or B with LL, RR, BB and TT. These correspond to left, right, bottom and top boundaries of the chip. For instance h(A, RR) denotes the horizontal displacement of the module A from the right boundary.

### 4.1.1. Absolute Constraints

These constraints are used to impose the position of a module with respect to boundaries. A sample constraint is depicted in Figure 4.1.

Figure 4.1. Absolute constraint

## 4.1.2. Relative Constraints

These constraints are used to describe the position of a module with respect to another module. The most general case -for relative constraints- is depicted in Figure 4.2. Special cases of the relative constraints are listed in the sub sections.

Figure 4.2. Relative constraint

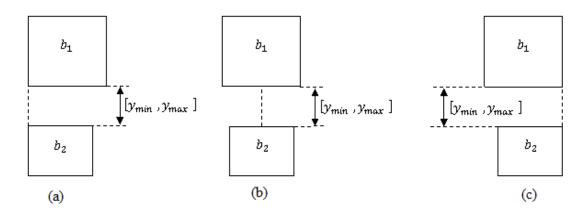

<u>4.1.2.1. Alignment Constraints</u>. These are used to align the top, bottom, left or right boundaries of modules. A sample drawing is depicted in Figure 4.3.

<u>4.1.2.2. Abutment Constraints.</u> These types of constraints are used to bond two modules. It is possible to abut the left boundary of an element with the right boundary of another one

or top boundary of an element with the bottom boundary of another one. In Figure 4.4, the top of module  $b_1$  is abutted with the bottom of module  $b_2$ .

Figure 4.3. Alignment constraints (a) alignment of the left boundaries, (b) alignment of the centers,(c) alignment of the right boundaries

Figure 4.4. Abutment constraint

### 4.1.3. Symmetry Constraints

These constraints guarantee that two modules are symmetrically places with respect to a reference point. A descriptive drawing is given in Figure 4.5.

Figure 4.5. Symmetry constraint

#### 4.2. Floor Plan Representation

There are many approaches to solve the problem of floor-planning. These approaches propose floor-plan structures to hold and manipulate the placement. In general floor-plans can be grouped into two; *slicing* and *non-slicing*.

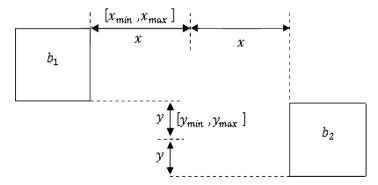

### 4.2.1. Slicing Structures

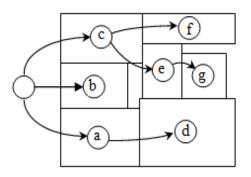

Due to the complexity of the problem, hierarchical methods have been extensively used. For the slicing representation, Otten [23] proposed a binary tree representation. Then, a formal representation -normalized Polish expression- for this slicing structure was proposed by Wong and Liu [24]. A simple slicing floor-plan structure and the corresponding slicing tree representation are presented in Figure 4.6. The polish expression of the given floor-plan is (312\*+654+\*\*).

It is commonly believed that the slicing structure is not a complete representation. The structure seems not being capable of holding non-slicing floor-plan solutions. However, Lai and Wong [25] showed that applying many vertical and horizontal compactions, slicing tree representation can be converted into a non-slicing floor-plan having the minimum area.

Figure 4.6. Slicing floor-plan structure

## 4.2.2. Non-Slicing Structures

Many non-slicing structures have been proposed, such as: *BSG* [26], *Sequence Pair* [18], *O-tree* [27], *B\*-tree* [28], *TCG* [29], *CBL* [30] and *Q Sequence* [31], etc...

These structures are separated into sub categories in [32]. BSG and sequence pair can represent general floor-plans and describe relative positions between blocks, such as left-of, below, etc... The second category is composed of O-tree and B\*-tree, and these describe relative positions of the blocks in 1-D. These two representations have smaller solution space however they do not directly hold the geometric relations between blocks. The last category contains the CBL and Q-sequence. These coding schemes are called *Mosaic* where the chip is divided into rectangular rooms. The mosaic structures cannot represent all kinds of floor-plans unless empty space is added.

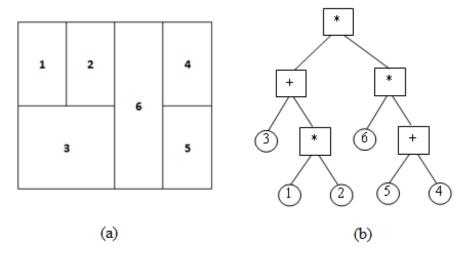

<u>4.2.2.1. Sequence Pair.</u> A widely accepted and used floor-plan structure is the Sequence Pair [18]. This representation resembles the *above-below* and *left to-right to* representation in [33]. The difference is that each packing is represented by a pair of module name sequences ( $\Gamma_+$  and  $\Gamma_-$ ) in sequence pair representation

In the original paper, a set of requirements for the floor-plan representation are listed. First, the solution space -represented by the floor-plan structure- should be finite and every solution in the representation should be feasible. The paper lists more: every solution should be realizable in polynomial time. The last requirement is that the best solution evaluated in the representation, should be the optimum solution. The solution space satisfying these requirements is called *P-admissible*. It is also stated that the Sequence pair representation is P-admissible.

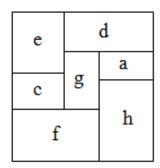

A floor-plan and the corresponding representation are presented in Figure 4.7.  $\Gamma_+$  and  $\Gamma_-$  are ordered pair of module name sequences. A decoding scheme for the Sequence Pair is tabulated for any module *x* and *y*.

The packing (positions of the blocks) is calculated through the longest path algorithm on a vertex weighted directed acyclic graph. The vertices in this graph are the modules and the weights of the edges are the dimensions of the modules.

Figure 4.7. Floor-plan for the sequence pair:  $(\Gamma_+, \Gamma_-) = (abdecf, cbfaed)$

| Order in the sequences                              | Description     |

|-----------------------------------------------------|-----------------|

| y is after x in both $\Gamma_+$ and $\Gamma$        | y is right to x |

| x is after y in both $\Gamma_+$ and $\Gamma$        | y is left to x  |

| y is before x in $\Gamma_+$ and after x in $\Gamma$ | y is above x    |

| x is before y in $\Gamma_+$ and after y in $\Gamma$ | y is below x    |

Table 4.1. Decoding the Sequence Pair representation

Optimization algorithms are used to search for the best floor-plan. These algorithms require perturbations in the layout to obtain the optimum placement. The original paper [18] presented two perturbations through searching the optimum layout. The applied perturbations to the layout are:

- Changing the orientation either vertically or horizontally (this set includes 2<sup>m</sup> perturbations)

- Altering the order of the modules in the sequence pairs (this set includes (m!)<sup>2</sup> perturbations)

These perturbations have to be supported by the interface. The *iterate* function generates a new solution, the *isValid* function decides whether the solution is valid or not. The *getCost* function returns the cost of the floor-plan. All these functions have to be

defined in the implementation, however the perturb function should input the type of the perturbation. Required types for the perturbations for the given Sequence Pair implementation are tabulated.

Although just two perturbations are considered, finding the best placement is very time consuming. Two approaches are proposed to decrease the time complexity. The first approach is to speed up the calculations by special methods. The original packing algorithm has  $O(n^2)$  complexity and a faster packing algorithm is presented in [34] with a complexity of  $O(n \log n)$ . The algorithm presented in [35] is based on *longest common subsequence* and obtains the coordinates of the modules and the total width and height of the floor-plan in  $O(n \log \log n)$ . The second approach, to speed up the search process, decreases the solution space, as done in [36].

These algorithms are directly related to the implementation. Solution space reduction should be implemented in the *autoPlace* function. This function runs the placement engine in the floor-planner. Note that the floor-plan implementation may not have a placement engine.

| Type of Perturbation | Description                                                                         |  |

|----------------------|-------------------------------------------------------------------------------------|--|

| PERTURB_ROTATE_90    | Rotates the given module (equivalent to changing the orientation)                   |  |

| PERTURB_SWAP_P       | Swaps the positions of two modules (there should not be constraints on the modules) |  |

Table 4.2: Required types of perturbations for SP representation

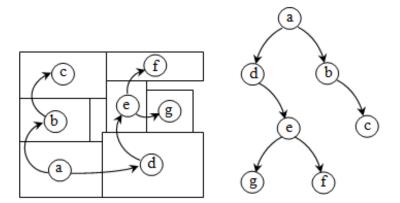

<u>4.2.2.2. O-Tree.</u> In [27] an ordered tree (O-tree) structure, to represent non-slicing floorplans, is presented. In this paper, an admissible placement is defined; this placement is obtained through abutting the modules to the left and to the bottom. This process is called *compaction*. Also, in the paper, it is shown that the solution space of the O-tree representation is smaller than that of Sequence Pair. A sample O-tree is given in Figure 4.8. The tree represents the horizontal placement; also, a tree for the vertical placement is required. Note that the O-tree represents compacted floor-plans.

In the original paper, a contour structure is used to reduce the required time during the conversion from the O-tree to constraint graph representation. Algorithms for conversion from the O-tree representation to the constraint graph representation and vice versa are also proposed.

Figure 4.8. An O-tree representation

The perturbations used to search the solution space are deleting and insertion (see Table 4.3). However, these perturbations may not result in an admissible (compact) floorplan. A post processing is needed to be applied to the resulting floor-plan. The post processing is done through the *postProcess* function. This function constructs an admissible tree and it is not included in the perturb function (This speeds up the algorithms including successive perturbations).

Table 4.3. Required types of perturbations for the O-tree representation

| Type of Perturbation | Description                              |  |

|----------------------|------------------------------------------|--|

| PERTURB_DELETE       | Removes a module from the representation |  |

| PERTURB_INSERT       | Inserts a module into the representation |  |

<u>4.2.2.3. B\*-Tree.</u> The B\*-tree [28] is based on ordered binary trees. Similar to the O-tree, the B\*-tree represents compact (admissible in [27]) floor-plans. The B\*-tree is constructed according to *above* and *right to* relations (A sample B\*-tree is given in Figure 4.9) and the operations search, insertion, and deletion are very fast compared to the O-tree representation.

Figure 4.9. A B\*-tree representation

The paper presents deleting and insertions as the floor-plan perturbations. The structure, in terms of the interface, is very similar to the O-tree representation. There are many B\*-tree based floor-planners considering boundary constraints [37], pre-placed modules [38], etc...

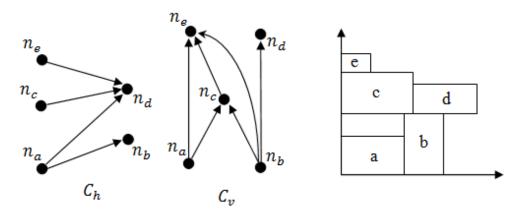

<u>4.2.2.4. BSG.</u> Bounded slicing grid representation, presented in [26], cuts the plane into rooms with horizontal and vertical line segments. These rooms are represented by utilizing two directed graphs in [26]. The structure of the bounded slicing grid and a room are shown in Figure 4.10.

The BSG representation incurs redundancy [28], a packing may have multiple representations. The redundancy in the representation degrades the complexity of the search process. The BSG is extended to handle pre-placed modules and soft modules.

<u>4.2.2.5. TCG.</u> Transitive closure graph based representation is presented by Lin and Chang in [29]. TCG based representation holds the relative positions of the blocks in two TCG graphs (Figure 4.11). TCG based representation is reported to satisfy the four properties of

P-admissibility, defined in [18] (Also defined in section 4.2.2.1). The packing is calculated using the longest path algorithm.

Figure 4.10. Bounded Slicing Grid

In addition to the perturbation defined (swap and rotate) the floor-plan is perturbed through reverse and move operations. These perturbations are added to the interface (Table 4.4).

Table 4.4. Perturbations inspired from TCG

| Type of Perturbation | Description                              |  |

|----------------------|------------------------------------------|--|

| PERTURB_MOVE_UP      | Places a module above another module     |  |

| PERTURB_MOVE_RIGHT   | Places a module at right side of another |  |

Figure 4.11. Transitive Closure Graphs

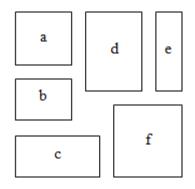

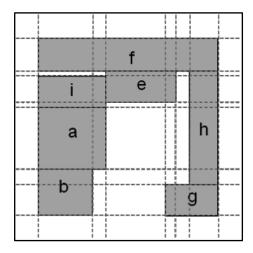

<u>4.2.2.6. CBL.</u> Corner block list representation is presented in [30]. The floor-plan structure is based on the mosaic structure. This structure is also defined in the paper.

*Corner block* is defined and the representation is constructed by deleting the corner blocks. The representation includes a sequence S of block names, a list of orientations L, and a list T of *T*-junctions (intersection of an edge of a module with corner of another module). The (S, L, T) sequence is called a corner block list. The corner block list of the floor-plan in Figure 4.12 is (S, L, T) = (fcegbad, 001100, 001010010). Note that, all CBL representations may not lead to a correct floor-plan, and this limits the representation.

The CBL representation is used to optimize the floor-plan in [30]. Rotation, reflection and perturbations of S, L, T lists are used to construct new solutions. The perturbations in the list are not general and should not be included in the interface.

Figure 4.12. Floor-plan is represented as (S, L, T) = (fcegbad, 001100, 001010010)

Table 4.5. Perturbations

| Type of Perturbation       | Description                      |  |

|----------------------------|----------------------------------|--|

| PERTURB_REFLECT_HORIZONTAL | Mirrors the modules horizontally |  |

| PERTURB_REFLECT_VERTICAL   | Mirrors the modules vertically   |  |

# 4.2.3. P-Sequence

P-Sequence (Projection Sequence) is a new representation developed through the study of this thesis. This representation is used to hold the floor-plan of the implemented floor-planner.

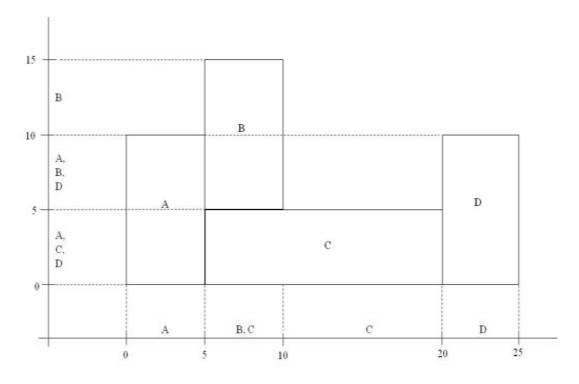

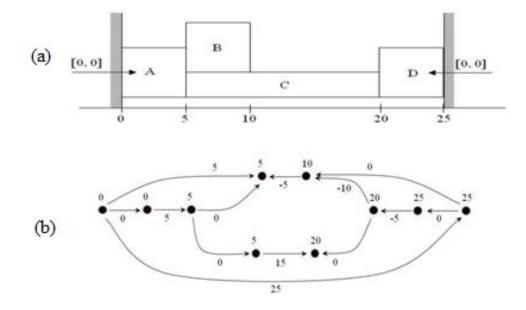

Two sequences of module name are used; these sequences are held for the vertical and horizontal projections of the modules. These projections are constructed by projecting the modules onto x and y axis. The axis is divided into segments according to these projections. In Figure 4.13, the segments are regions between the two dashed lines.

The floor-plan may be represented as  $(H, V) = (\{A, BC, C, D\}, \{ACD, ABD, B\})$ . The groups of the module names (such as ACD) are the modules in the segments on the axis. ACD is a group of module names whose projections are in the first segment on the *y* axis.

P-Sequence is superior to other representations; the neighborhoods of a module are easily extracted from this representation. Also this representation does not require a compact layout; a layout with spaces is easily handled through this representation.

<u>4.2.3.1. Compaction of P-Sequence.</u> Most of the time the following segments include similar modules and it is not required to hold their names many times. Through the following this representation is more compacted.

Figure 4.13. Modules are projected onto x and y axis

- 1. If the name of the module is recorded in segment *i* and is not present in segment i + 1 add the name to i + 1th group.

- 2. If the name of the module is not present in segment *i* and is recorded in segment i + 1 add the name to i + 1th group.

- If the name of the module is recorded in segment *i* and it is also recorded in segment *i* + 1 do not change *i* + 1th group.

- If the name of the module is not present in segment *i* and it is also not present in segment *i* + 1 do not change *i* + 1th group.

For instance, the representation for Figure 4.13 is found as  $(H, V) = (\{A, BC, C, D\}, \{ACD, ABD, B\})$ . After the compaction the representation is  $(H, V) = (\{A, ABC, B, CD\}, \{ACD, CB, AD\})$ .

For the floor-plan in Figure 4.14, normal representation is  $(H, V) = (\{baif, aif, ef, gef, gf, ghf\}, \{bg, bh, ah, ih, ieh, eh, f\})$  and the compacted representation is  $(H, V) = (\{baif, b, aie, g, e, h\}, \{bg, hg, ba, ai, e, i, ehf\})$ . As the number of module increases the compact representation becomes much shorter than the normal representation.

Figure 4.14. Floor-plan is represented as (H, V) = ({baif, b, aie, g, e, h}, {bg, hg, ba, ai, e, i, ehf})

<u>4.2.3.2. Analysis of P-Sequence.</u> The number of segments for the worst case is calculated. For the worst case, projection of a module separates the axis into three parts. An example is given for four modules in Figure 4.15. In general, the axis is separated into 2n - 1segments, for *n* modules and for the worst case.

Figure 4.15. Four modules separate the axis at most to 7 pieces.

Again, for the worst case segment at the center includes n modules and the first and last segments include a single module. Thus the total number pointers required to hold the modules are:

$$N = \frac{n(n-1)}{2} + n + \frac{n(n-1)}{2} = n^2$$

#### 4.3. Layout Description Script (LDS)

This section presents the description of the floor-plan through java script. This description uniquely defines a placement for the chip.

The command in this description language describes an interface for the floorplanner. This description language is directly related to the layout constraints (See Section 4.1). The required commands for the script are stated under the subsections.

#### 4.3.1. Alignment Commands

Alignment commands are used to align to modules. The predefined command handles aligning the top, bottom or middle (vertical) points of two different modules. It is also possible to align the left, right and center (horizontal) points of these modules.

### 4.3.2. Abutment Commands

The abutment commands are used to bond two different modules. It is mostly used to connect wires to modules. Due to electrical rules in the design all wires are required to touch the ports.

| Definition                             | Description                                  |  |

|----------------------------------------|----------------------------------------------|--|

| int alignLeft(int reference, int e);   | Aligns left boundaries of modules            |  |

| int alignRight(int reference, int e);  | Aligns right boundaries of modules           |  |

| int alignCenter(int reference, int e); | Aligns center points (horizontal) of modules |  |

| int alignTop(int reference, int e);    | Aligns top boundaries of modules             |  |

| int alignBottom(int reference, int e); | Aligns bottom boundaries of modules          |  |

| int alignMiddle(int reference, int e); | Aligns center points (vertical) of modules   |  |

Table 4.6. Commands for alignment

Table 4.7. Command for abutment

| Definition                            | Description                                                                                   |

|---------------------------------------|-----------------------------------------------------------------------------------------------|

| int abutRight(int reference, int e);  | Aligns right boundary of module reference<br>module with the left boundary of input module    |

| int abutLeft(int reference, int e);   | Aligns left boundary of module reference<br>module with the right boundary of input<br>module |

| int abutAbove(int reference, int e);  | Aligns top boundary of module reference<br>module with the bottom boundary of input<br>module |

| int abutBelove(int reference, int e); | Aligns bottom boundary of module reference<br>module with the top boundary of input module    |

# 4.3.3. Insertion Commands

Previously defined commands are used to add constraints into the layout and they are converted to constraints. However, the following commands are not constraints and they are used to define the order of the modules.

# 4.3.4. Command for General Constraints

This command adds general constraints. Previously defined alignment and abutment commands are special cases for this command.

| Definition                               | Description                                            |  |

|------------------------------------------|--------------------------------------------------------|--|

| int insertAt(int e, double x, double y); | Adds a new module at the x and y coordinates           |  |

| int insertRight(int reference, int e);   | Adds a new module to the left of the reference module  |  |

| int insertLeft(int reference, int e);    | Adds a new module to the right of the reference module |  |

| int insertAbove(int reference, int e);   | Adds a new module above the reference module           |  |

| int insertBelove(int reference, int e);  | Adds a new module below the reference module           |  |

Table 4.8. Module insertion

# 4.3.5. Update Commands

These commands are used to update the layout database or update the floor-plan. An update to the database will load the coordinates of the modules to the database from the floor-planner.

Table 4.9. Adding general constraints

| Definition                                                                                        | Description                                                                                                                                                                                                         |  |

|---------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| void setLocation(int e, int reference,<br>double xMin, double xMax, double<br>yMin, double yMax); | Places two modules in such a way that the difference between their x coordinates is in the range $[x_{min}, x_{max}]$ . Similarly the difference between their y coordinates is in the range $[y_{min}, y_{max}]$ . |  |

Table 4.10. Command for updating

| Definition                           | Description                                                            |  |

|--------------------------------------|------------------------------------------------------------------------|--|

| void updatePlan(DataBase dB, int e); | Reloads the properties of a module into the floor-planer               |  |

| void updateBase(DataBase dB);        | Updates the database according to the coordinates in the floor-planner |  |

#### 4.3.6. Basic Commands

Basic commands are used to delete/add modules, remove constraints, and undo the last modification.

| Definition                    | Description                                     |  |

|-------------------------------|-------------------------------------------------|--|

| void iterate();               | Forces the floor-planer to find a valid solutio |  |

| int redo(int n);              | Redo                                            |  |

| int undo(int n);              | Undo                                            |  |

| void removeConstraint(int e); | Removes the input constraint                    |  |

| void delete(int e);           | Removes a module from the floor-planner         |  |

Table 4.11. Basic commands

#### 4.4. Constraints and Inequalities

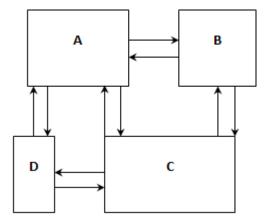

In section 4.3, the commands for the layout description script are stated. Most of these commands add constraints to the floor-planner. In Figure 4.16, a simple floor-plan is shown. The arrows indicate the input constraints. In this example, left edge of module A is abutted with the left boundary of the floor-plan and the right edge of module D is abutted with the right boundary of the floor-plan. Also, there are constraints due to the static modules, the width of A is constant and this is another constraint. Moreover, module D cannot come closer to module B, because it cannot pass over module C. A classification for the constraints is stated in the next subsection.

#### 4.4.1. Classification of Constraints

In general, constraints in a floor-plan may be grouped into two: soft and hard constraints.

<u>4.4.1.1. Soft Constraints.</u> Soft constraints are not static, and they can disappear. For instance, the module B in Figure 4.16 cannot touch the left boundary of the floor-plan, due to module A; however if module B moves up it can touch the left boundary. Thus, the constraint that B should be after A is a soft constraint and it can disappear.

Figure 4.16. Constraints in the floor-planer

<u>4.4.1.2. Hard Constraints.</u> Hard constraints are static and they do not disappear unless the user removes it. In Figure 4.16, the width of module C is fixed to 15 and it will not change.

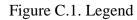

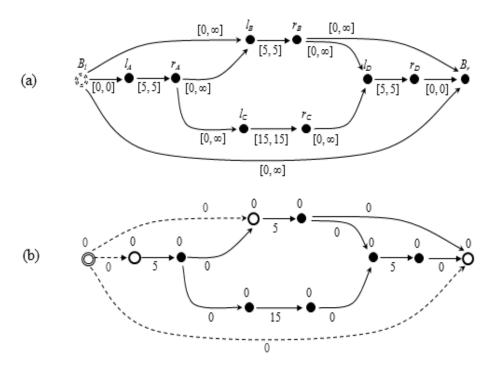

## 4.4.2. Constraints and Inequalities

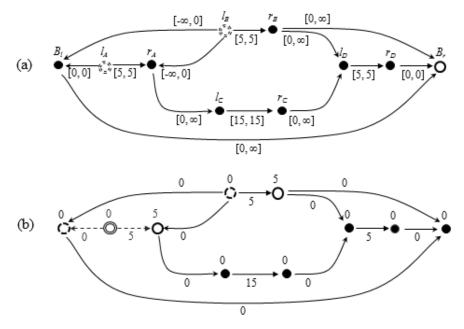

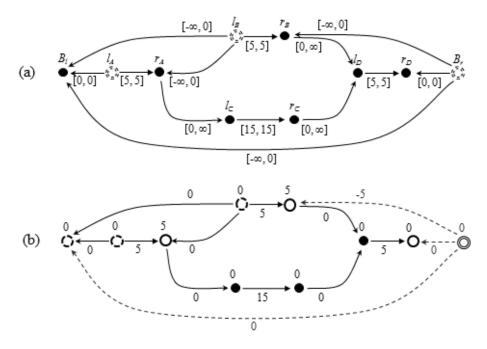

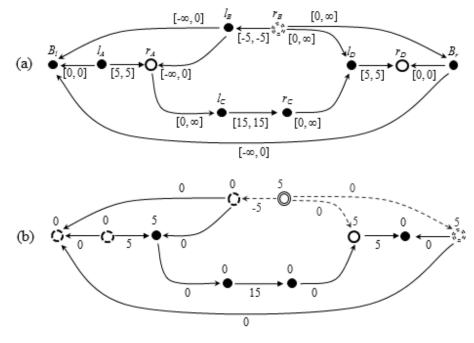

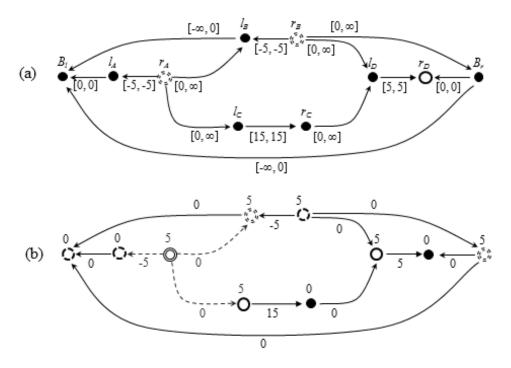

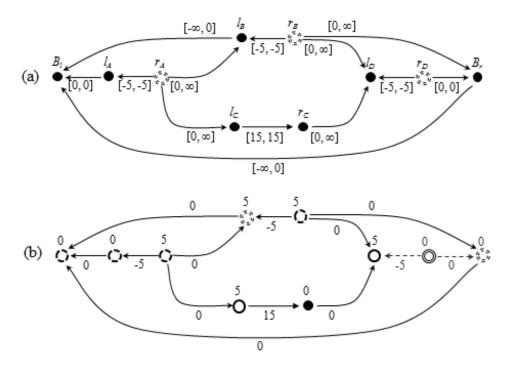

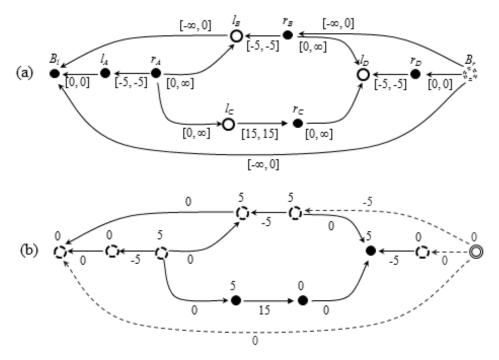

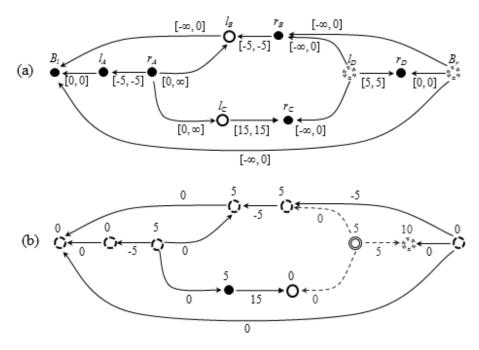

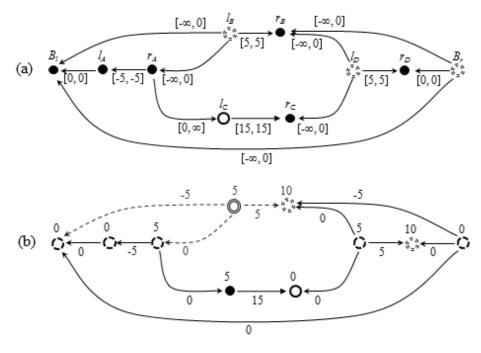

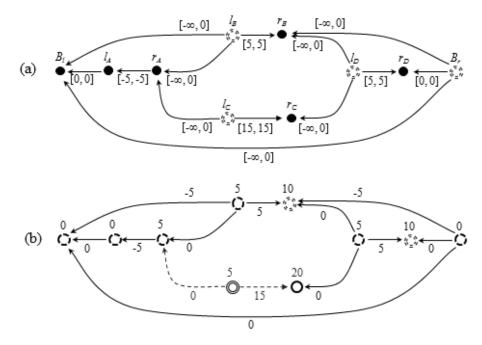

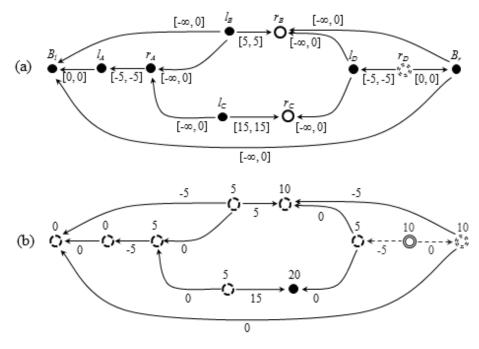

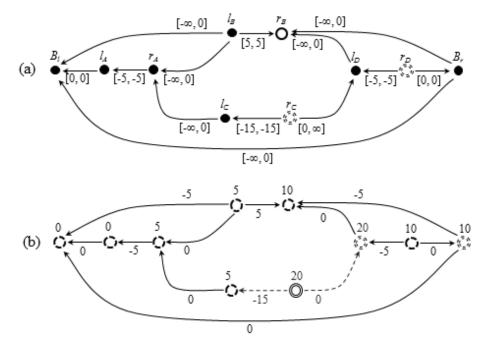

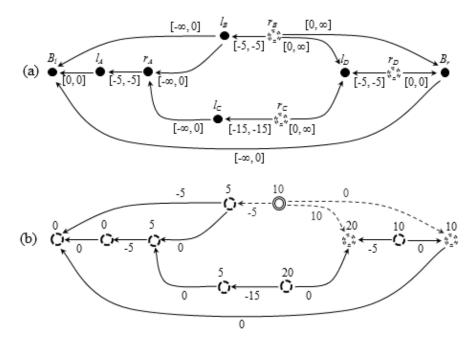

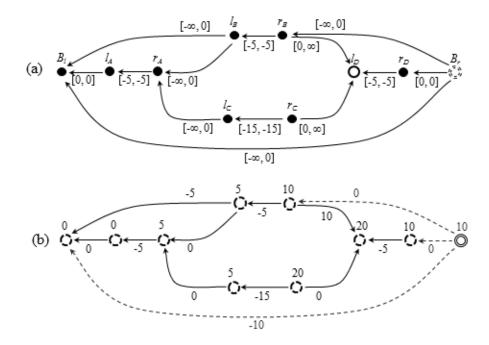

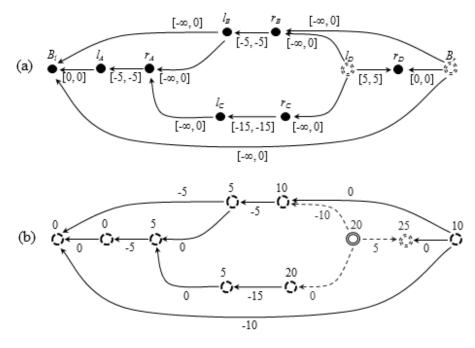

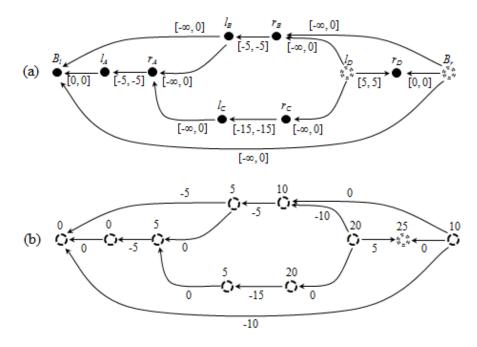

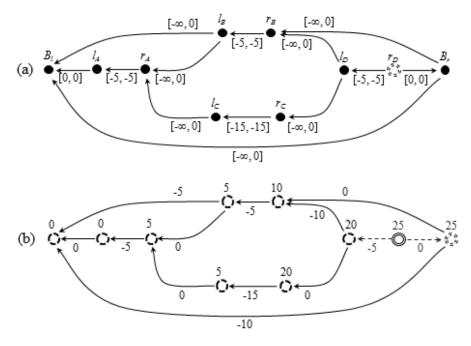

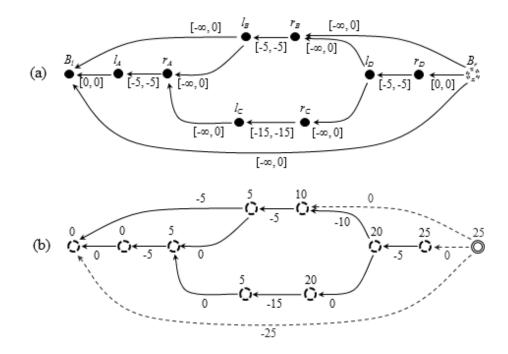

The boundaries of the floor-plan are denoted by B and the subscript indicates which boundary it is.  $B_l$  represents the left boundary,  $B_r$  represents the right boundary and similarly  $B_b$  and  $B_t$  represents the bottom and the top boundaries, respectively.

The positions of the edges of the modules are represented like  $l_A$ , where the *l* represents the left edge and *A* represents the module name. The letter *r* represents the right edge, and similarly the *b* and *t* represents bottom and top edges, respectively.

The following equation is obtained through an observation of Figure 4.16 and states that the position of left boundary  $(B_l)$  equals to the position of the left edge of module A  $(l_A)$ .

$$B_l \leq l_A \leq B_l \leftrightarrow l_A = B_l$$

Similarly the following equations are obtained from the floor-plan in Figure 4.16.

| $l_A = B_l$     | $r_D = B_r$        | $B_l \leq B_r$  |

|-----------------|--------------------|-----------------|

| $B_l \leq l_A$  | $r_A \leq l_B$     | $B_l \leq l_B$  |

| $r_A \leq l_C$  | $r_{C} \leq l_{D}$ | $r_B \leq l_D$  |

| $r_D \leq B_r$  | $r_B \leq B_r$     | $r_A = l_A + 5$ |

| $r_B = l_B + 5$ | $r_C = l_C + 15$   | $r_D = l_D + 5$ |

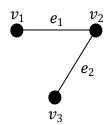

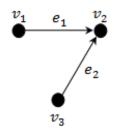

## 4.4.3. Inequalities and Graphs

It is shown in section 4.4.2 that the floor-plan problem is a set of inequalities. The inequalities have to be solved in order to obtain a valid solution.

In this thesis, a new algorithm is developed to solve a set of inequalities. The solution is found by making use of graph theory.

In section 4.4.2, inequalities for the floor-plan in Figure 4.17.(a) are extracted and in Figure 4.17.(b) these inequalities are converted to a directed graph. The presented graph holds ranges as well as values, and the nodes also hold values. The edges in the graph are allowed to be inverted. Inversion of an edge is done as follows:

- Value of the edge is negated.

- The range is negated. When the range  $[\alpha, \beta]$  is inverted, it becomes  $[-\beta, -\alpha]$ .

# 4.4.4. Solving the Inequalities

The proposed solver deals with any set of constraints and detects if the solution does not exist. Starting from any node the algorithm runs and the procedure is as follows:

- 1. Change the directions of the surrounding edges as outgoing.

- 2. Start visiting the surrounding (directly connected) nodes.

- 3. Calculate the difference between the value of this node and the connected node.

- 4. Assign the difference to the edge and if the capacity of the edge is not enough to hold the difference, update the value of the connected node.

- 5. Add any updated or unvisited node to the queue.

- 6. If there is not any node to be visited, leave the loop. The node values are the solutions.

- 7. Use Breadth-first algorithm to visit the nodes.

As an example, the solution of the graph in Figure 4.17 is present in APPENDIX C.

#### 4.4.5. Loop Breaking

It is not always possible to find a solution to a set of inequalities. In this case, the presented algorithm tries to find the solution, which is not present. It is expected that the algorithm locks. However, in that case, the presented algorithm realizes that the inequalities (constraints) conflict.

When a solution does not exist, the algorithm starts to visit the edges periodically. The order of the visited edges is considered as a signal and checked for replications. This signal (list of the visited edges) is processed with the system presented in Figure 4.18.

Figure 4.17. (a) The plan and the constraints (b) The representation of the constraints in a graph

Figure 4.18. Block diagram of the loop breaker

Two sample signals (visited edges) are plotted in Figure 4.19. In this figure, the second signal is obtained from a set of solvable inequalities and the first signal is obtained from a set of unsolvable inequalities. As depicted in the plot, the visited edges in the first signal has some periodic components, these are pointed out in Figure 4.20. Loop breaking property of the solver prevents blocking of the software.

#### 4.5. Floor-planner Implementation

In this thesis, the implemented floor-plan is based on the P-sequence representation in section 4.2.3 and the inequality solver in section 4.4.4. The implementation is compatible with the layout description script (LDS) described in section 4.3.

Figure 4.19. Sample signals (visited edges)

Figure 4.20. Periodicity in the signal

The P-Sequence representation is used to hold the ordering of the modules. This structure is used to extract the soft constraints described in section 4.4.1. The hard constraints are installed through the template (LDS). All these inequalities (constraints) are solved and the database is updated according to the solution.

# **5. DEVICE GENERATOR AND ROUTER**

Device generator tool is one of the basic parts of a layout synthesizer. Similar to the other tools, this tool is connected to the data base and adds new structures to it. It is possible to construct any type of device through the device generators. These device generators are written in java and they depend on the available technology. It is required to update the device generator when the technology file updates. As an example, a CMOS transistor structure will be different that a bipolar one. To construct the bipolar device a new code is required. Thus it will be a good practice to define a interface for the device generator, just to make it general. In section 5.1, a general interface is defined.

### 5.1. Interface

The definition of the command, needed to construct a new device, is explained in Table 5.1.

| Definition                       | Description                              |

|----------------------------------|------------------------------------------|

| int newDevice(int type, double[] | Adds a new device to the layout database |

| parameters, int[] nets);         | Adds a new device to the layout database |

Table 5.1. Interface for adding new devices

The *newDevice* command in Table 5.1 takes the device type as an input parameter. For a CMOS device technology, devices types are tabulated in Table 5.3.

Device generator constructs the requested devices, however the ports of the device are not known. Thus, the generator should somehow return the positions of the ports. This is done through the *getPorts* command, defined in Table 5.2.

| Table 5.2. Interf | ace to get t | he ports |

|-------------------|--------------|----------|

|-------------------|--------------|----------|

| Definition                        | Description                       |

|-----------------------------------|-----------------------------------|

| <pre>int[] getPorts(int e);</pre> | Returns references for the ports. |

| Device    | Value for the Type Parameter |

|-----------|------------------------------|

| NMOS      | 1                            |

| PMOS      | 2                            |

| RESISTOR  | 3                            |

| CAPACITOR | 4                            |

| INDUCTOR  | 5                            |

Table 5.3. Device types for CMOS process

#### 5.1.1. Example

The following code constructs a PMOS device.

int

$$t = x$$

.newDevice(PMOS, new double[] {w, l, m}, new int[] {d, g, s, b});

Where w is the width of the transistor, 1 is the length of the transistor; m is the number of folds, d is the reference of the drain node, g is the reference of the gate node, s is the reference of the source node and b is the reference of the bulk node.

#### 5.2. Devices

In the implementation of this thesis, the device generator constructs NMOS and PMOS devices. The details for the constructed devices are explained in the sub sections.

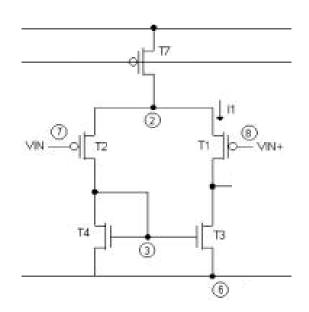

# 5.2.1. NMOS Transistor