### ASYNCHRONOUS SIGMA-DELTA ANALOG TO DIGITAL CONVERTERS

by

Balkır Kayaaltı

B.S. Microelectronics, Electrical and Electronics Engineering Department, 2000M.S. Microelectronics, Electrical and Electronics Engineering Department, 2003

Submitted to the Institute for Graduate Studies in Science and Engineering in partial fulfillment of the requirements for the degree of Doctor of Philosophy

Graduate Program in Electrical and Electronics Engineering Boğaziçi University

2011

## ASYNCHRONOUS SIGMA-DELTA ANALOG TO DIGITAL CONVERTERS

## APPROVED BY:

| Prof. Ömer Cerid           |  |

|----------------------------|--|

| (Thesis Supervisor)        |  |

|                            |  |

| Prof. Günhan Dündar        |  |

|                            |  |

| Prof. Uğur Çilingiroğlu    |  |

|                            |  |

| Prof. Oğuzhan Çiçekoğlu    |  |

|                            |  |

| Assoc. Prof. Johannes Hegt |  |

DATE OF APPROVAL: 27.9.2010

### ACKNOWLEDGEMENTS

I would like to thank Prof. Ömer Cerid for being thesis supervisor and his guidance and helps through the Phd study.

I would like to express my gratitude to Asoc. Prof. Johannes Hegt for taking time to attend my defense, being a thesis committee member and his very valuable corrections about the thesis.

I would like to thank Prof. Günhan Dündar for being a thesis committee member, valuable helps and thesis corrections.

I would like to thank Prof. Uğur Çilingiroğlu for being a thesis committee member valuable contributions and suggestions during the Phd. study.

Many thanks to Prof. Oğuzhan Çiçekoğlu for being in my thesis committee and corrections in my thesis.

I would like to thank my dear friend Özsun Sönmez for his friendship from undergraduate years till now.

Finally, i would like to thank my family for their supports.

### ABSTRACT

# ASYNCHRONOUS SIGMA-DELTA ANALOG TO DIGITAL CONVERTERS

Analog to digital conversion is the process of translating analog real world signals to their corresponding binary encoded form which digital devices need. Among the examples for analog signal sources storage devices like harddisks and sensor devices can be given. Analog to digital converters are key components that make this translation. There are different types of analog to digital converter circuits. A specific topology can be selected according to its achievable number of bits, speed, power and according to its area of usage. Sigma-delta analog to digital conversion is a popular type which can be used in applications where high resolution with moderate bandwidth is desired. High resolutions are achieved due to the consequence of the inherent noise suppression by the loop filter. Oversampling, which corresponds to the sampling of the input signal with a higher rate than that of the regular Nyquist rate is their other advantage. This process pushes the quantization noise away from the baseband, and thereby higher signal to noise ratios are achieved. There are mainly two sub-types of sigma delta converters. The first, is the discrete time version which uses discrete time signals and components. The second is the continuous time version which uses entire continuous time signals and components except the quantizer and the Digital to analog converter (DAC) in the feedback. These two types are both clocked with an external clock signal, so the output is synchronous i.e. synchronized with a clock. Designing a new type of the circuit which does not use an external clock; but instead using the self oscillation created in the converter loop can be a an alternative third type. This type of the converter will not use sampling process inside the loop, so clock jitter due to the sampling can be eliminated in the sigma-delta loop, where usually a high frequency signal is sampled. If the sampling is done with a lower frequency compared to the one in the loop, effect of the clock jitter can be reduced. Asynchronous sigma-delta

converters contain some nonlinear control theory concepts such as limit cycle periodic modes of the loop and the presence of the quantizer nonlinearity on the spectrum and performance. This thesis is about the theory of such converters and their design procedure with a real circuit implementation.

# ÖZET

# ASENKRON SİGMA-DELTA ANALOG DİJİTAL ÇEVİRİCİLER

Analog dijital çeviriciler gerçek kaynaklı analog sinyalleri dijital kodlanmış hallerine çeviren araçlardr. Bu dijital sinyaller, ardından gelen dijital sinyal işleme devrelerinde kullanılır. Analog sinyal kaynaklarına harddisk gibi kayıt cihazları ve optik sensörler örnek olarak gösterilebilir. Analog dijital ceviricilerin bir çok çeşidi vardır. Barındırdıkları avantaj ve dezavantajlara göre istenilen bir topoloji seçilebilir. Deltasigma analog dijital çeviriciler sağladıkları yüksek çözünürlük sayesinde günümüzde oldukça yaygın ve popülerdirler. Yüksek çöznürlük devredeki filtrenin içsel gürültü bastırmasından kaynaklanır. 'Yüksek örnekleme' yani işaretin standart 'Nyquist örnekleme' frekansından daha yüksek bir frekansla örneklenmesi ile basamaklama gürültüsü sinyal bandından uzağa doğru itilir. Böylelikle daha yüksek işaret gürültü oranı elde edilir. Sigma-delta analog dijital çeviriciler iki çeşittir. Birincisi örneklenmiş işaretler ve örnekleyici devre elemanları ile çalşan örneklenmiş zaman sigma delta çeviricilerdir. Ikinci çeşit ise, sürekli zaman işaret ile çalışan ve basamaklayacı hariç sürekli zaman devre elemanları kullanan sürekli zaman delta sigma çeviricilerdir. Bu iki devre de senkron devrelerdir; yani daarıdan verilen bir saat sinyaline senkronizedir. Dışardan bir saat işareti verilmeksizin kendi salınımlarını üretip kullanan yeni bir çevirici mevcut ikisine yeni bir alternatif olacaktır. Bu devre dışarıdan bir saat işareti almayacağı için, saat seğirmesi engellenecektir. Bu tip çeviricilerde daha önce karşılaşılmayan limit döngü ve doğrusal olmayan basmaklayıcının yarattğı distorsiyon etkileri vardır. Bu tez bu tip çeviricilerin matematiksel analizi ve devre gerçeklemesi ile ilgilidir.

# TABLE OF CONTENTS

| AC  | CKNC | OWLEDGEMENTS                                                            | iii |

|-----|------|-------------------------------------------------------------------------|-----|

| AF  | BSTR | ACT                                                                     | iv  |

| ÖZ  | ХЕТ  |                                                                         | vi  |

| LIS | ST O | F FIGURES                                                               | ix  |

| LIS | ST O | F TABLES                                                                | XV  |

| LIS | ST O | F SYMBOLS/ABBREVIATIONS                                                 | xvi |

| 1.  | INT  | RODUCTION                                                               | 1   |

|     | 1.1. | Motivation for Asynchronous Sigma-Delta Analog to Digital Conversion    | 1   |

|     | 1.2. | Objective of the Thesis                                                 | 5   |

|     | 1.3. | Key features and Contributions                                          | 6   |

|     | 1.4. | Thesis Organization                                                     | 7   |

| 2.  | SIGI | MA DELTA ADC BACKGROUND                                                 | 8   |

|     | 2.1. | Overview and Background of Sigma-Delta ADC's                            | 8   |

|     |      | 2.1.1. Types of Sigma-Delta Modulation                                  | 9   |

| 3.  | MAT  | THEMATICAL ANALYSIS OF ASDM's                                           | 16  |

|     | 3.1. | Describing Function Approach                                            | 18  |

|     | 3.2. | Time Domain Approach                                                    | 19  |

|     | 3.3. | Tsypkin's Frequency Domain Approach                                     | 22  |

|     | 3.4. | Spectral Analysis of ASDM's                                             | 28  |

|     | 3.5. | Simulink model for ASDM for behavioral simulations                      | 33  |

|     | 3.6. | Frequency Scaling                                                       | 33  |

|     | 3.7. | Effect of Finite Slope of the Nonlinearity                              | 34  |

|     | 3.8. | Spectrum of behavioral simulation of first order ASDM                   | 35  |

| 4.  | DE   | CIMATION FILTERS IN $\Sigma - \Delta$ ADC's                             | 38  |

|     | 4.1. | Introduction                                                            | 38  |

|     | 4.2. | Digital Filter Basics                                                   | 39  |

|     | 4.3. | Cascaded Integrator Comb (CIC) Filters                                  | 40  |

|     | 4.4. | Filtering and Down Sampling of PWM Modulated Signals                    | 42  |

|     | 4.5. | Analog Filtering of Digital Signals and Time to Digital Converters(TDC) | 43  |

|    | 4.6.  | Conclusion                                                          | 44 |

|----|-------|---------------------------------------------------------------------|----|

| 5. | CIR   | CUIT IMPLEMENTATION                                                 | 45 |

|    | 5.1.  | Introduction                                                        | 45 |

|    | 5.2.  | The Impact of Linearity of the Components used in ASDM to the Total |    |

|    |       | Performance                                                         | 46 |

|    | 5.3.  | Voltage to Current Converter                                        | 47 |

|    | 5.4.  | Current-mode Integrator                                             | 50 |

|    | 5.5.  | Current Comparator with Current Output                              | 55 |

|    |       | 5.5.1. Comparator with Adjustable Delay                             | 57 |

|    | 5.6.  | 2's Complement Encoder and Pre-delay Circuit                        | 61 |

|    | 5.7.  | Creating Pulse Delay with Current Starved Inverter                  | 63 |

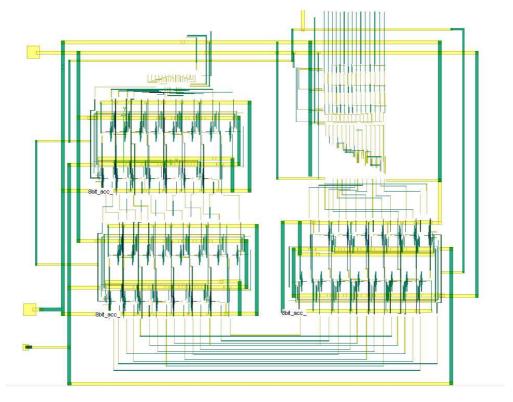

|    | 5.8.  | Accumulator                                                         | 64 |

|    | 5.9.  | Sampler                                                             | 65 |

|    | 5.10. | Phase Restorer                                                      | 66 |

|    | 5.11. | Comb Filter                                                         | 66 |

|    |       | 5.11.1. Problem of Generated Glitches in the Integrators            | 67 |

| 6. | CH    | IP DESIGN OF THE ADC                                                | 69 |

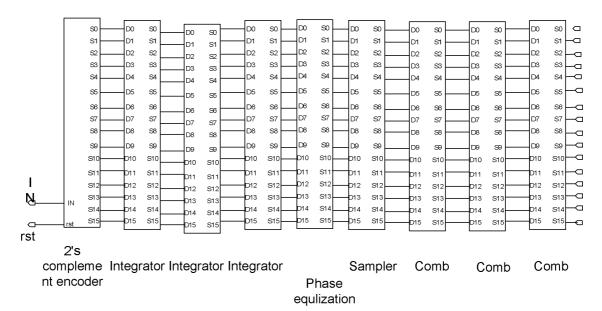

|    | 6.1.  | Filter Part                                                         | 70 |

| 7. | RES   | SULTS AND DISCUSSION                                                | 72 |

|    | 7.1.  | Introduction                                                        | 72 |

|    | 7.2.  | ASDM Part                                                           | 72 |

|    | 7.3.  | Filter Results                                                      | 78 |

| 8. | CON   | CLUSION AND FUTURE WORK                                             | 81 |

| RE | EFER  | ENCES                                                               | 82 |

## LIST OF FIGURES

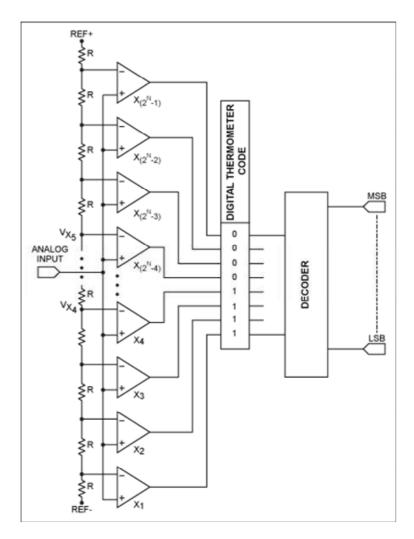

| Figure 1.1.  | Diagram of the flash ADC                                                                 | 3  |

|--------------|------------------------------------------------------------------------------------------|----|

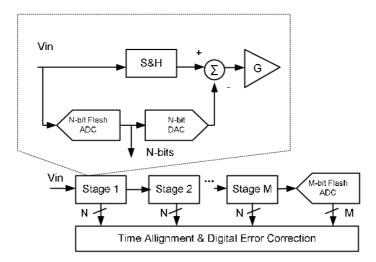

| Figure 1.2.  | Diagram of the pipeline ADC                                                              | 4  |

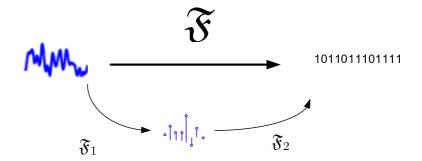

| Figure 2.1.  | ADC operations depicted as a function across the signal domains .                        | 8  |

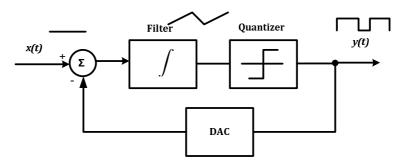

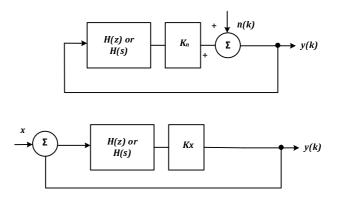

| Figure 2.2.  | Delta sigma ADC block diagram                                                            | 9  |

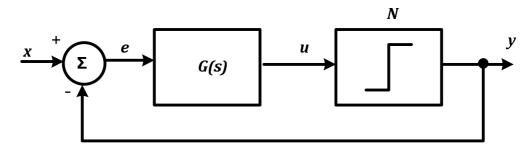

| Figure 2.3.  | Sigma-delta modulator                                                                    | 9  |

| Figure 2.4.  | Block diagram of a discrete time $\Sigma - \Delta$ ADC                                   | 11 |

| Figure 2.5.  | Block diagram of a continuous time $\Sigma - \Delta$ ADC                                 | 11 |

| Figure 2.6.  | Multistep quantizer transfer characteristics $\Sigma - \Delta$ ADC                       | 12 |

| Figure 2.7.  | Separated circuits for noise and signal as given in $[9]$                                | 12 |

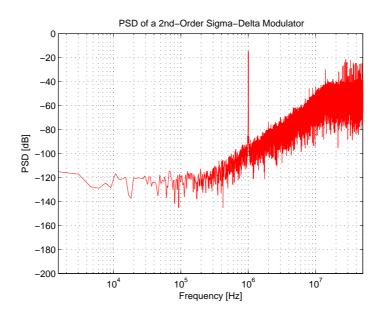

| Figure 2.8.  | Typical spectrum of a second order synchronous modulator $\ . \ . \ .$                   | 13 |

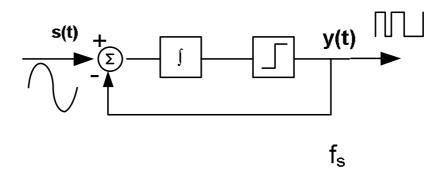

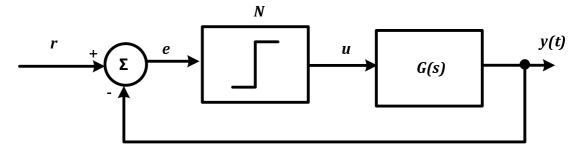

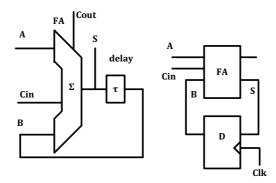

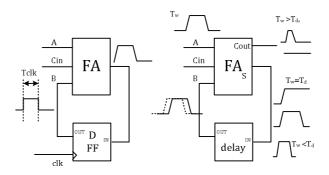

| Figure 2.9.  | The asynchronous $\Sigma - \Delta$ modulator (ASDM)                                      | 13 |

| Figure 2.10. | Possible sampling and filtering combinations of ASDM signals to get a digital ADC output | 15 |

| Figure 3.1.  | A first order ASDM block diagram                                                         | 16 |

| Figure 3.2.  | A relay system                                                                           | 17 |

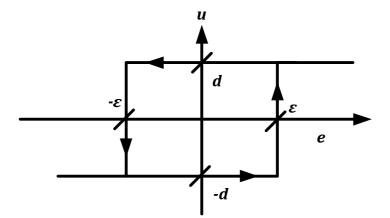

| Figure 3.3.  | Hardlimiter with hysterisis characteristics                                                                                                                                                   | 17 |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

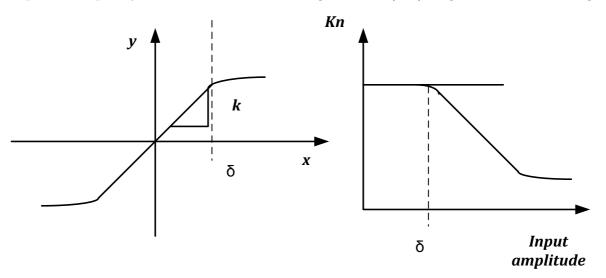

| Figure 3.4.  | Hardlimiter characteristics (left), DF gain according to amplitude (right)                                                                                                                    | 18 |

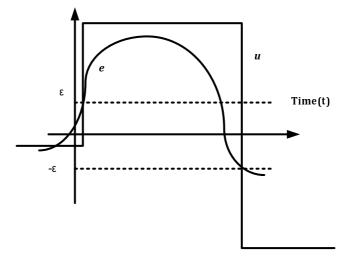

| Figure 3.5.  | Waveforms in the hardlimiter circuit. 'e' is signal before the non-<br>linearity and u is the output of the nonlinearity. Dashed lines<br>correspond to hysteresis levels of the nonlinearity | 21 |

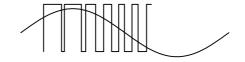

| Figure 3.6.  | Sinusoidal signal modulated PWM                                                                                                                                                               | 28 |

| Figure 3.7.  | Integrator output of the first order sigma delta modulator                                                                                                                                    | 28 |

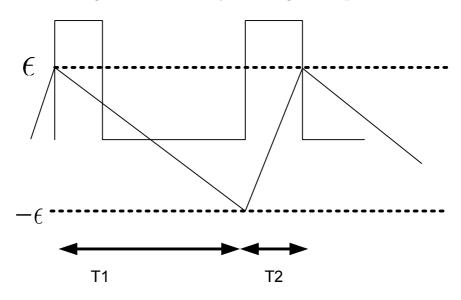

| Figure 3.8.  | Duty cycle modulated wave                                                                                                                                                                     | 29 |

| Figure 3.9.  | Calculated spectrum of the above signals using Eq. 3.72                                                                                                                                       | 32 |

| Figure 3.10. | Filter outputs of a first order (dashed) and second order(solid) ASDM                                                                                                                         | 33 |

| Figure 3.11. | Matlab Simulink model for behavioral simulation of first order ASDM                                                                                                                           | 34 |

| Figure 3.12. | Filter outputs of a first order (dashed) and second order(solid) ASDM                                                                                                                         | 34 |

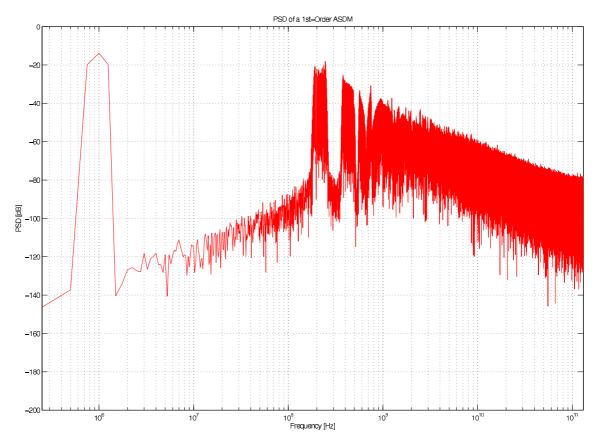

| Figure 3.13. | Spectrum of the Simulink simulated first order ASDM                                                                                                                                           | 36 |

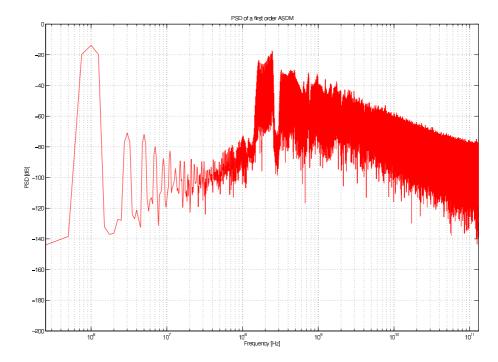

| Figure 3.14. | Spectrum of the Simulink simulated first order ASDM with odd<br>order distortion                                                                                                              | 36 |

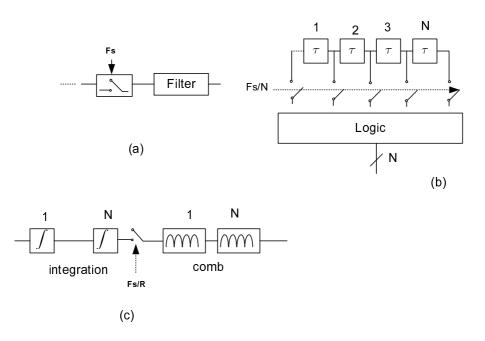

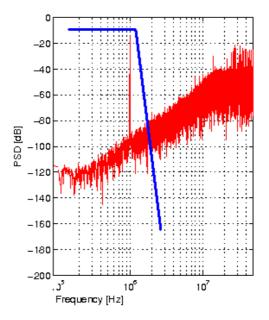

| Figure 4.1.  | Decimation filter frequency response shown on the PSD of a syn-<br>chronous sigma delta modulator output graph                                                                                | 38 |

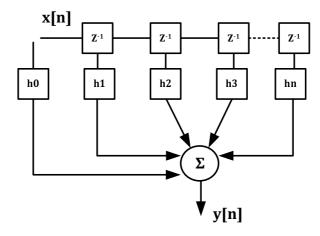

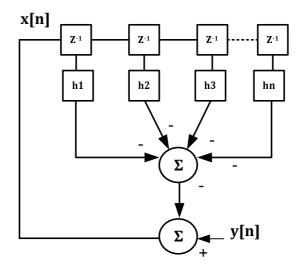

| Figure 4.2.  | Conventional FIR filtering                                                                                                                                                                    | 39 |

х

| Figure 4.3.  | IIR filter                                                                                                                                    | 40 |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------|----|

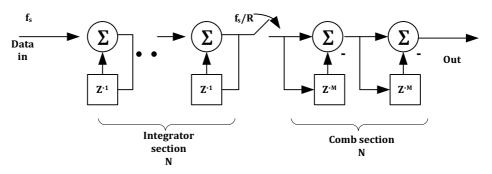

| Figure 4.4.  | Block diagram of CIC filtering                                                                                                                | 40 |

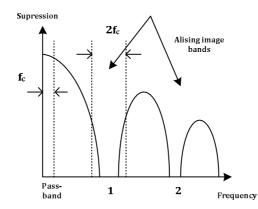

| Figure 4.5.  | Frequency response of CIC filters                                                                                                             | 41 |

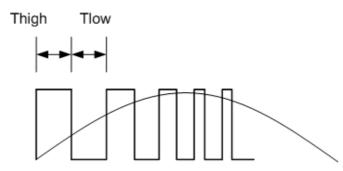

| Figure 4.6.  | Resolution information in the pulse duration of PWM $\ . \ . \ .$ .                                                                           | 42 |

| Figure 4.7.  | Analog accumulator with delay line<br>(left) , digital accumulator (right) $% \left( \left( {{{\rm{Analog}}} \right)_{{\rm{Analog}}} \right)$ | 43 |

| Figure 4.8.  | Block diagram of the TDC                                                                                                                      | 44 |

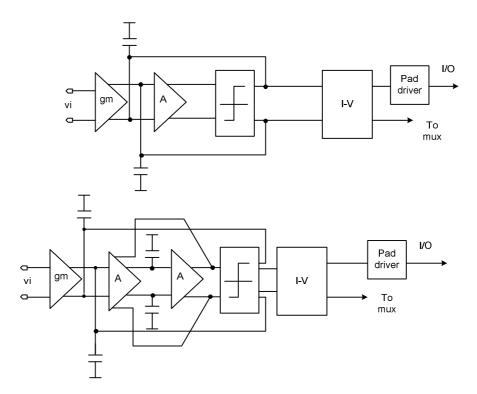

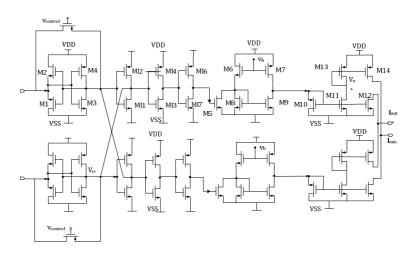

| Figure 5.1.  | Designed analog circuits showing its building blocks                                                                                          | 46 |

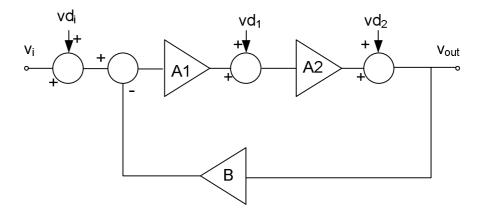

| Figure 5.2.  | Block diagram of a closed loop system with several gain stages $\ .$ .                                                                        | 47 |

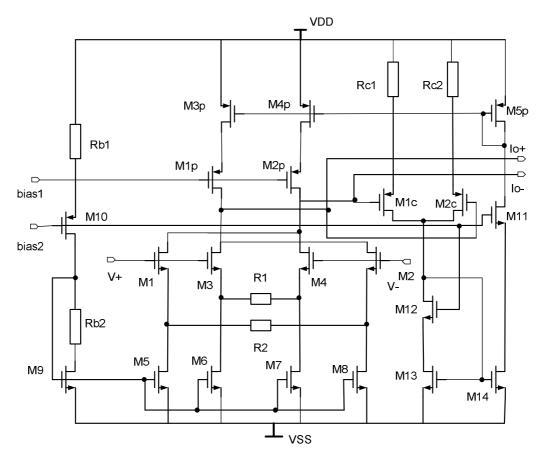

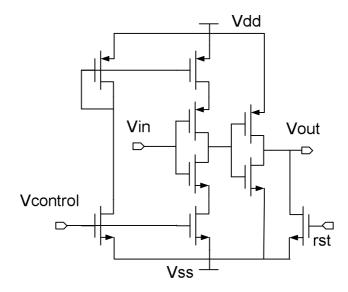

| Figure 5.3.  | Voltage to current converter used in the modulators                                                                                           | 48 |

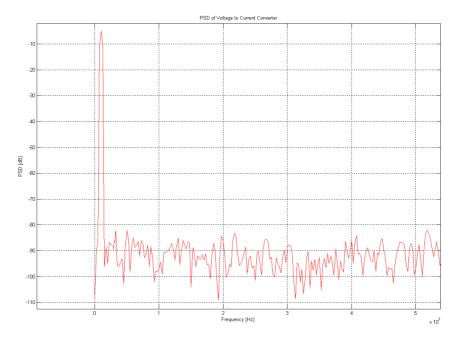

| Figure 5.4.  | Voltage to current converters harmonics                                                                                                       | 49 |

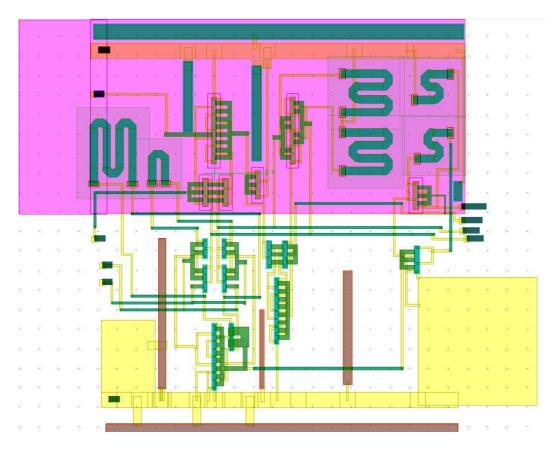

| Figure 5.5.  | Voltage to current converter layout used in the modulators $\ldots$ .                                                                         | 49 |

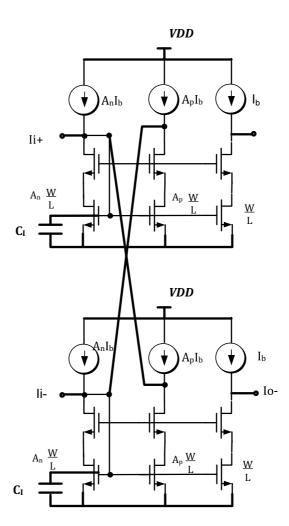

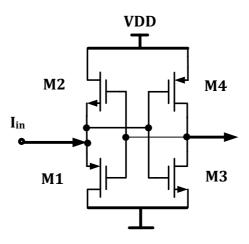

| Figure 5.6.  | Current-mode integrator proposed in [45]                                                                                                      | 51 |

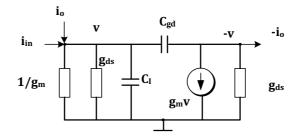

| Figure 5.7.  | Small signal model of the current-mode integrator                                                                                             | 52 |

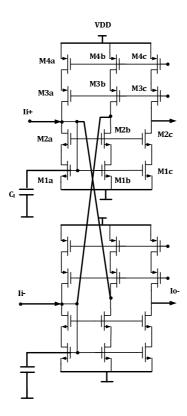

| Figure 5.8.  | The integrator used for better $gain(A_0)$ and transfer characteristics                                                                       | 52 |

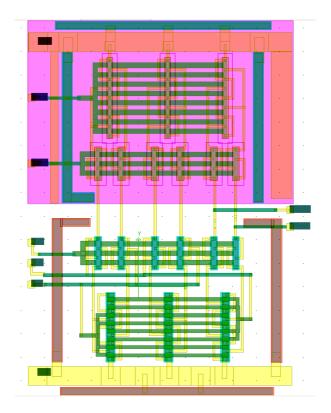

| Figure 5.9.  | The layout of the integrator used in the first order $\Sigma-\Delta$ modulator                                                                | 53 |

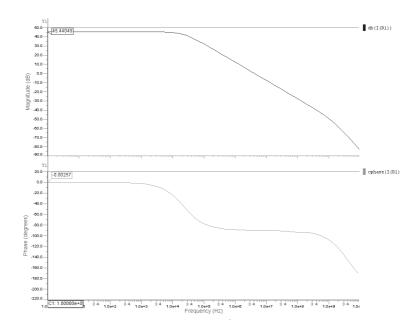

| Figure 5.10. | The AC response of the integrator                                                                                                             | 54 |

xi

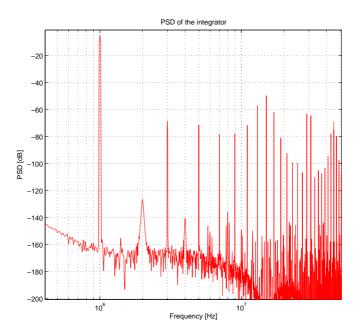

| Figure 5.11. | The PSD of the integrator showing more than 70dB suppression of spurious harmonics                                         | 54 |

|--------------|----------------------------------------------------------------------------------------------------------------------------|----|

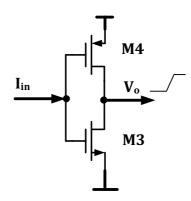

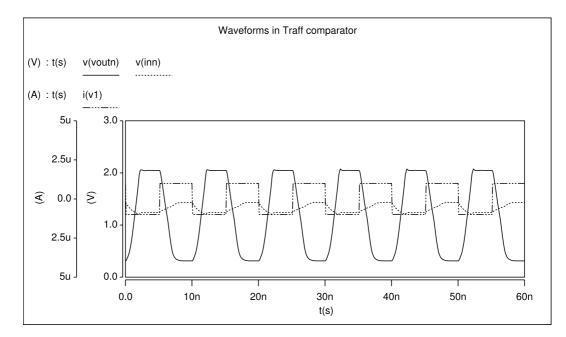

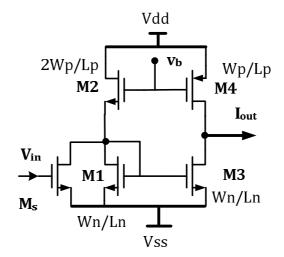

| Figure 5.12. | Comparator proposed in $[48]$                                                                                              | 56 |

| Figure 5.13. | Comparator proposed in [30]                                                                                                | 56 |

| Figure 5.14. | Waveforms of Traff comparator Vin, Iin and Vout, when square-<br>wave input of $\pm 1\mu A$ is applied                     | 56 |

| Figure 5.15. | Voltage to current converter                                                                                               | 57 |

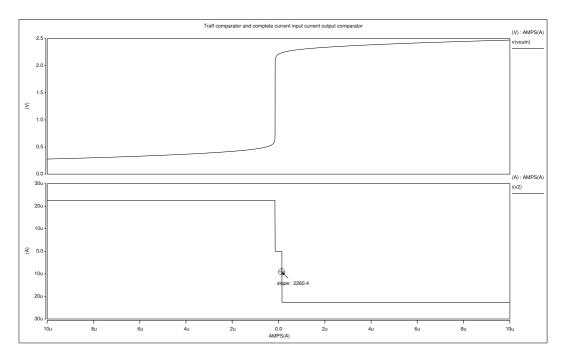

| Figure 5.16. | Transfer curves of the: a)Traff comparator(voltage output) and (b)the whole comparator with V-I converter                  | 58 |

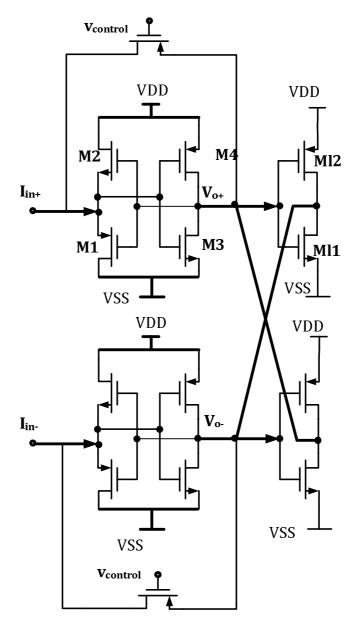

| Figure 5.17. | Latch and feedback circuit added to the original comparator $\ . \ .$ .                                                    | 59 |

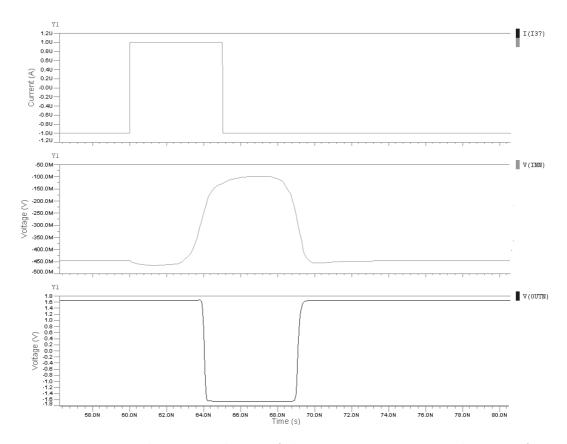

| Figure 5.18. | Input and output voltages of the comparator upon application of 1 $\mu$ A square input current                             | 60 |

| Figure 5.19. | The complete current comparator consisting of: the comparator, voltage to current converter and current differencing parts | 61 |

| Figure 5.20. | 2's complement encoder and predelay circuit layout                                                                         | 62 |

| Figure 5.21. | 2's complement encoder and predelay circuit diagram                                                                        | 62 |

| Figure 5.22. | Current starved inverter with its control bias circuit to generate delayed pulses                                          | 63 |

| Figure 5.23. | Layout for the current starved inverter                                                                                    | 64 |

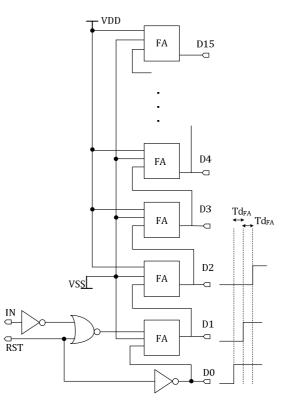

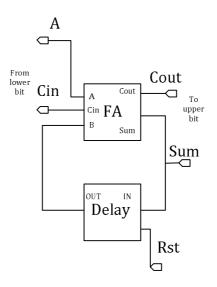

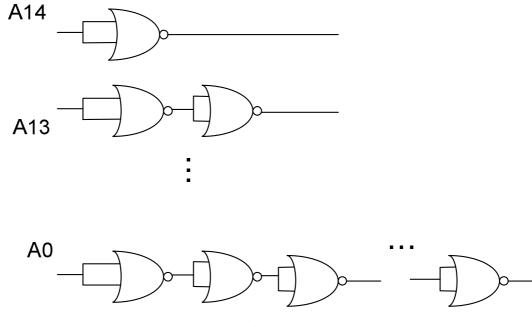

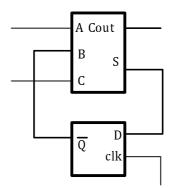

| Figure 5.24. | 1-bit analog accumulator                                                                                                            | 64 |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------|----|

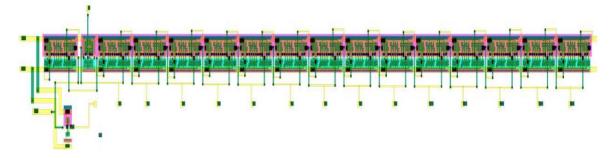

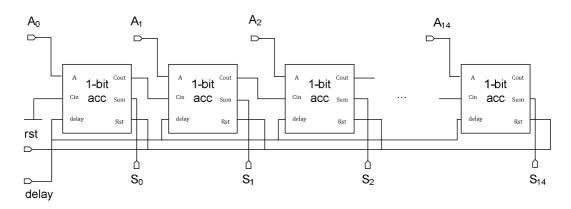

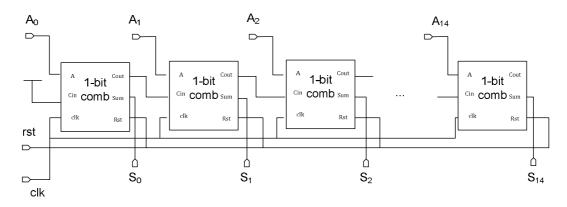

| Figure 5.25. | 15-bit analog accumulator using cascaded 1 bit structures                                                                           | 65 |

| Figure 5.26. | 15 bit sampling register                                                                                                            | 65 |

| Figure 5.27. | 15 bit sampling register layout                                                                                                     | 65 |

| Figure 5.28. | Phase restorer circuit                                                                                                              | 66 |

| Figure 5.29. | 1-bit comb filter                                                                                                                   | 67 |

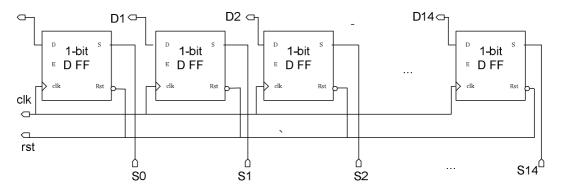

| Figure 5.30. | 15-bit comb filter                                                                                                                  | 67 |

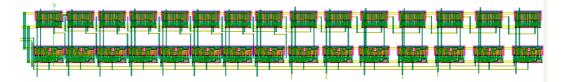

| Figure 5.31. | 15-bit comb filter layout                                                                                                           | 67 |

| Figure 5.32. | Demonstration of possible glitch problem caused by asynchronous data                                                                | 68 |

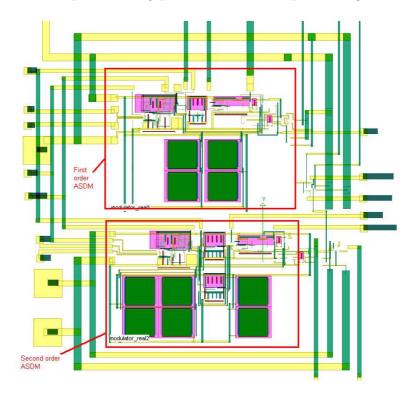

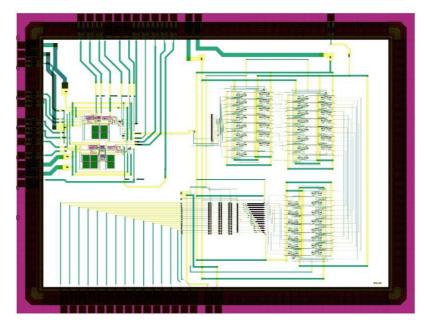

| Figure 6.1.  | The complete modulators part ASDM in the prototype $\ . \ . \ .$ .                                                                  | 69 |

| Figure 6.2.  | Block diagram of the filter section                                                                                                 | 70 |

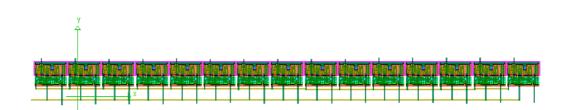

| Figure 6.3.  | Layout of the filter section                                                                                                        | 71 |

| Figure 6.4.  | The full chip layout with I/O pads                                                                                                  | 71 |

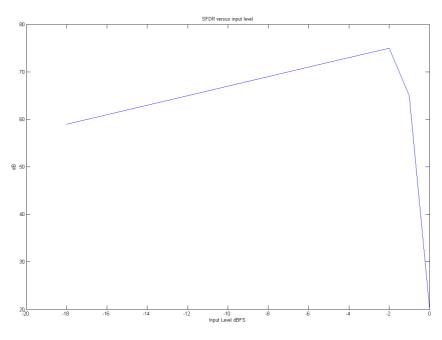

| Figure 7.1.  | Spectrum of the circuit simulation first order modulator: $\%$ 80 modulation index for 1MHz sinusoidal test signal applied $\ldots$ | 73 |

| Figure 7.2.  | Simulation of the first order ASDM spectrum with modulation in-<br>dex of 0.3                                                       | 74 |

xiii

| Figure 7.3. | SFDR variation with the input signal amplitude                                                         | 74 |

|-------------|--------------------------------------------------------------------------------------------------------|----|

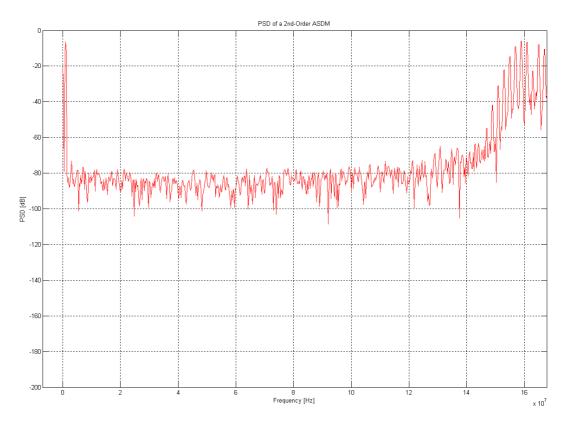

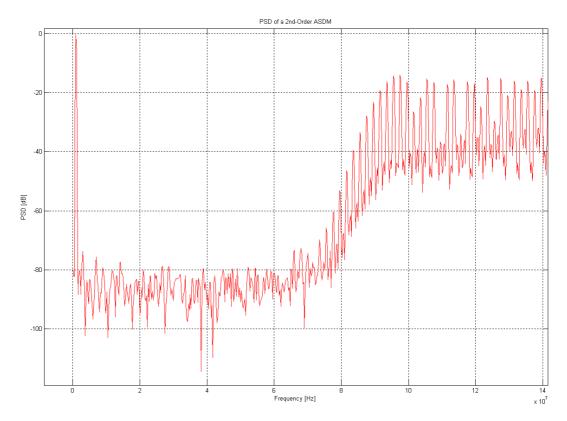

| Figure 7.4. | Simulated spectrum of the second order ASDM: 50% modulation depth and 1MHz sinusoidal input signal     | 75 |

| Figure 7.5. | Simulated spectrum of the second order ASDM: $\%$ 80 modulation depth and 1MHz sinusoidal input signal | 76 |

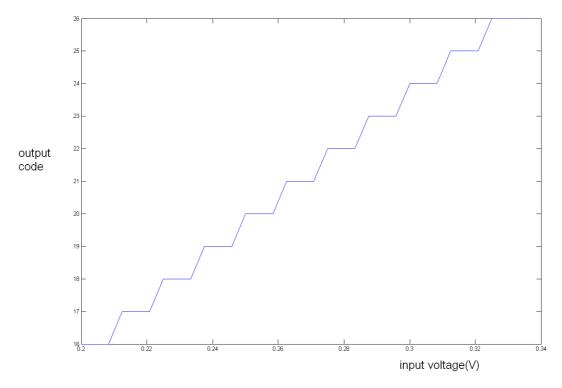

| Figure 7.6. | Simulated output code of the complete ADC                                                              | 79 |

## LIST OF TABLES

| Table 1.1. | Different domains in signal processing depending on the sampling                                                                                                                                                                                              |          |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|            | at either time or amplitude $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                                                                                                                         | 5        |

| Table 2.1. | ADC operations depicted as a function across the signal domains. Arrow<br>showing possible domain transitions for ADC's. A discrete-time $\Sigma - \Delta$ ADC between domain 1,2 and 4. Continuous time $\Sigma - \Delta$ ADC<br>between in domains 1 and 4. | vs<br>10 |

| Table 5.1. | Transistor aspects of the integrator                                                                                                                                                                                                                          | 53       |

| Table 5.2. | 2's complement encoding of the $\Sigma - \Delta$ modulator output                                                                                                                                                                                             | 61       |

| Table 7.1. | Summary of simulated performance of the layout                                                                                                                                                                                                                | 77       |

| Table 7.2. | Summary of simulated layout performance                                                                                                                                                                                                                       | 78       |

| Table 7.3. | Summary of ADC FOM's                                                                                                                                                                                                                                          | 79       |

# LIST OF SYMBOLS/ABBREVIATIONS

| $A_{CM}$          | Differential gain                  |

|-------------------|------------------------------------|

| $A_{DC}$          | Zero frequency gain                |

| $A_{dif}$         | Common mode gain                   |

| $C_{gd}$          | Gate to drain capacitance          |

| $C_I$             | Integration capacitance            |

| $g_{ds}$          | Drain to source transconductance   |

| $g_m$             | Gate transconductance              |

|                   |                                    |

| Λ                 | Tsypkin fuction                    |

| $\Sigma - \Delta$ | Sigma-Delta                        |

| $\omega_u$        | Unity gain frequency               |

|                   |                                    |

| ADC               | Analog to Digital Converter        |

| AMS               | Austrian Micro Systems             |

| ASDM              | Asynchronous Sigma-Delta Modulator |

| CIC               | Cacaded Integrator Comb            |

| DAC               | Digital to Analog Converter        |

| DF                | Sinusoidal Describing Function     |

| $\mathbf{FFT}$    | Fast fourier transform             |

| FOM               | Figure of Merit                    |

| FIR               | Finite Impulse Response            |

| HDTV              | High definition television         |

| IIR               | Infinite Impulse Response          |

| IM3               | Third Harmonic Intermodulation     |

| kHz               | Kilo Hertz                         |

| LSB               | Least significant bit              |

| MHz               | Mega Hertz                         |

| MOS               | Metal Oxide Semiconductor          |

| Msps              | Megasamples per second             |

|                   |                                    |

| NTF   | Noise Transfer Function           |

|-------|-----------------------------------|

| PCM   | Pulse Code Modulation             |

| PWM   | Pulse Width Modulation            |

| OSR   | Over Sampling Ratio               |

| SAR   | Successive Approximation Register |

| SFDR  | Spurious Free Dynamic Range       |

| SINAD | Signal to Noise and Distortion    |

| SNR   | Signal to Noise Ratio             |

| VDD   | Drain to Drain Voltage            |

| Vgs   | Gate to Source Voltage            |

| VSS   | Source to Source Voltage          |

| xDSL  | Digital subscriber lines          |

### 1. INTRODUCTION

# 1.1. Motivation for Asynchronous Sigma-Delta Analog to Digital Conversion

Signal processing is the art of shaping an electrical signal, by means of linear and nonlinear circuit elements which transform an input signal to a desired output signal. In the years till 70's, signal processing was done in purely analog domain. With the advances in electronic fabrication techniques; it was possible to integrate many digital devices in a small area and digital signal processing became more popular. Despite numerous advantages of the digital domain, some of the signal path is still analog, thus some signal processing still has to be done in the analog domain. Mixed signal circuits where analog and digital signals are translated to each other, are receiving much attention due to their impact on the performance of the whole signal processing circuit. Analog to digital conversion is the process to convert the analog signal to digital codes. Different types of analog to digital converters (ADC) offer different performance parameters such as: conversion rate, resolution, power consumption and dynamic range. Some ADC types can be given as: successive approximation, integrating, flash, pipe-line and sigma delta. The most popular ones are flash, pipe-line and sigma delta.

Integrating ADC's are used in very slow applications such as instrumentation and have limited usage.

Successive approximation register (SAR) ADC's are mainly used for speeds up to 5 megasamples per second (Msps). They achieve resolutions from 8 to 16 bits with low power consumption. Therefore they are used widely in portable battery-powered instruments, pen digitizers, industrial controls, and data/signal acquisition. Their main disadvantage is the high performance requirement of the DAC and comparator inside the ADC structure used internal. Because of its internal search algorithm, the comparator works at higher speed than the ADC. The used comparator should be very fast and low input referred noise. Therefore, offset cancellation techniques are widely used. The DAC should also be accurate and needs to be calibrated.

Flash analog-to-digital conversion is the fastest way to convert an analog signal to a digital signal. A typical flash ADC diagram is given in Fig. 1.1. A N-bit Flash ADC is composed of  $2^{N-1}$  comparators. A resistive-divider with 2N resistors provides the reference voltage. The reference voltage for each comparator is one least significant bit (LSB) greater than the reference voltage for the comparator below it. Each comparator produces a high output when its analog input voltage is higher than the reference voltage applied to it. This type of converter is also known as parallel ADC. They are mainly used where large bandwidths are required. Typical used areas include data acquisition, satellite communication, radar processing, sampling oscilloscopes, and high-density disk drives. They consume considerable power. The resolution is limited usually to 8-bits, due to component matching limits. Also, every additional bit causes doubling the die area. Achievable Signal to Noise Ratio (SNR) is highly degraded when clock jitter is present, especially at high input frequencies.

The pipelined analog-to-digital converter (ADC) architecture have received interest due to their wide range of sampling rates from a few megasamples per second (MSPS) up to hundreds Msps. Typical pipelined ADC is given in Fig. 1.2. Resolutions range from 8 bit at high sample rates to 16 bit at low rates. This performance metrics makes it suitable to be used in applications including CCD imaging, ultrasonic medical imaging, digital receivers, base stations, digital video (for example, HDTV), xDSL, cable modems, and fast ethernet. The resolution limitation is due to the capacitor and resistor mismatches of the components used inside.

Among the other analog to digital converters, Sigma-Delta  $(\Sigma - \Delta)$  analog to digital Pulse Code Modulation (PCM) converters are currently popular in the fields covering wireless communication due to their high resolutions for medium bandwidth, ease of design, and low power consumption. High resolution is the consequence of the inherent quantization noise suppression by the loop filter. With higher order loop filters, even better signal to noise ratios (SNR) can be achieved. Oversampling is the

Figure 1.1. Diagram of the flash ADC

process of sampling the signal at the output of the quantizer with a higher sampling rate than that of the conventional 'Nyquist rate'. This pushes the quantization noise outside the signal band and enables to achieve dramatic signal to noise ratios. Resolutions up to 20 bits are achievable at low frequency (several hundered kilo hertz (kHZ)) input signals. Inputs of frequencies above one megahertz (MHz) requires filter orders of four and more. The achievable resolutions at that frequency range 12 to 14 bits. The building blocks of  $\Sigma - \Delta$  ADC's are relatively easy to design and do not require high performance and precise circuits. A decimation filter is used after the  $\Sigma - \Delta$  converter to filter the high frequency noise and also slow down the rate of conversion. This requires some additional die area.

Sigma-delta converters mainly have two types. The first is the discrete time ver-

Figure 1.2. Diagram of the pipeline ADC

sion, which is currently the most popular type. It uses discrete time input signals and also discrete time electronic components. The power consumption which is caused from switching actions in discrete data is its biggest disadvantage. Another disadvantage is the requirement of relatively high bandwidth circuit blocks to work with the sampled input signal.

Continuous versions are better in terms of power consumption than the discrete time working ones. However, this type of converter suffers from performance degradation caused by the clock jitter noise injected at the quantizer. This noise can not be eliminated by the loop filter and deteriorates the SNR by a significant amount.

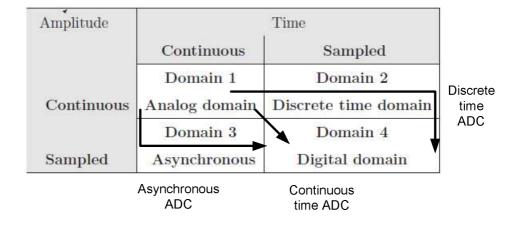

Besides the conventional synchronous circuit approach, converters can be built to not generate digital words but a periodic train of pulses modulated according to the input signal level. Such an operation can be better studied with the help of Table 1.1.

All signals can be classified as a member of four domains. Time sampled signals belong to 'domain 2 and 4'. 'Domain 4', is the digital signal domain where amplitude is discretized and binary coded at fixed time instants. 'Domain 2' is the discrete time signals domain, where amplitude value is sampled at certain time samples. 'Domain 3' is the asynchronous signal domain where signals are discretized only according to their amplitude value. Working in asynchronous signal domain may bring the opportunity to reduce power consumption for slow activity signals. While the technology advances,

| Amplitude  | Time          |                      |

|------------|---------------|----------------------|

|            | Continuous    | Sampled              |

|            | Domain 1      | Domain 2             |

| Continuous | Analog domain | Discrete time domain |

|            | Domain 3      | Domain 4             |

| Sampled    | Asynchronous  | Digital domain       |

Table 1.1. Different domains in signal processing depending on the sampling at either time or amplitude

supply voltages tend to decrease and circuit sizes tend shrink further. Reduction in the supply voltage threatens the dynamic range of the analog to digital converters. If the required bandwidth with improved technologies is considered, one can observe that the signal bandwidth is increasing continuously. Nowadays, wireless standards using increasing bandwidths such as WiFi and WiMax are in demand. Increasing the loop filter degree and oversampling can be utilized to attain higher bandwidths as stated earlier. However, they come at a cost. High order loop filters bring problems of stability, namely a phenomenon called limit cycle where the modulator oscillates at a low frequency. Increasing the oversampling ratio to high levels is dependent on technology. The other problem for continuous time converters is excess loop delay, which causes stability problems. In this thesis, asynchronous sigma delta converters will be investigated. Their potential according to their advantages and disadvantages will be outlined.

#### 1.2. Objective of the Thesis

The main objective of the thesis is to investigate the performance of asynchronous sigma delta ADC's and explore the feasibility to their usage. To additional objectives are construction of an adjustable frequency ASDM and to construct a decimation filter for asynchronous PWM output. The available number of bits and the parameters that influence it is to be investigated.

There are two main objectives of the thesis. The first is to build a current-mode

asynchronous  $\Sigma - \Delta$  modulator with adjustable loop delay. The loop delay will be realized with the quantizer delay. Through adjusting this delay ASDM working in a desired limit cycle frequency can be realized. The second objective is to build an asynchronous decimation filter which will process the PWM data generated by the ASDM and outputs digital converted data.

#### 1.3. Key features and Contributions

The asynchronous ADC represented in this dissertation has the following key features and contributions

- The control theory analysis of loop delay based ASDM's is done. The previous implementations of the asynchronous  $\Sigma \Delta$  modulators are using quantizers with hysteresis. The analysis of the ASDM's with quantizer delay has been given.

- Stability and limit cycle operating region of ASDM's is given analytically. ASDM's have also stability concern; i.e, the limit cycle oscillation can change frequency and even can break with time. Stability analysis to ensure a working design is also given.

- Current mode comparator with adjustable delay is given. Previous ASDM implementations are using comparators with hysteresis. Since the implementation in this dissertation is based on a loop delay asynchronous modulator, an adjustable delay current comparator is given.

- Current mode implementation of a first and second order ASDM is given. Their advantages and disadvantages compared to implementation are outlined.

- A Feedforward second order ASDM design is given. Previous second order ASDM's are of feedback type.

- A decimation filter to process the ASDM's PWM output is given. The filter is based on Cascaded Integration Comb (CIC) architecture and the integration parts are using delay lines. The data is sampled after it is integrated with a slow clock signal.

- Reduced clock jitter affect for the overall ADC is shown. Since the sampling operation is not done in the  $\Sigma \Delta$  loop, the output is less sensitive to the

sampling clock jitter.

#### 1.4. Thesis Organization

The organization of the thesis is as follows:

Chapter 2 presents background of sigma delta ADC's and summarizes the previous studies related to the thesis. Chapter 3 gives the control theory methods for analyzing limit cycle behavior as, stability analysis. Also, a subchapter to derive the output spectrum of the ASDM is given. Chapter 4 provides the decimation filter background for the proposed filtering scheme in this dissertation. Chapter 5 is dedicated to the circuit implementation of the asynchronous modulator.Circuit schematics and associated layouts for selected and newly proposed circuit blocks are given as schematics and associated layout. Chapter 6 gives the integrated circuit (IC) implementation of the ASDM modulators and the decimation filter. Chapter 7 details the results of the implemented ADC. Chapter 8 concludes the thesis.

### 2. SIGMA DELTA ADC BACKGROUND

Analog to digital converters are electronic devices that translate an analog domain signal (Table 1.1 upper-left) to a digital signal (Table 1.1 down-right). They implement nonlinear and linear operations to sample the signal information carried on amplitude and time axes and produce a digital code as output. The translation function ' $\mathfrak{F}$ ' in Figure 2.1 can be further divided into some sub-functions which translate the signals to other domains. However, the parent function ' $\mathfrak{F}$ ' as a whole should carry the operation to go from the analog domain to the digital.

Different techniques for building ADC's are present among which are flash, pipeline and sigma-delta architectures. Depending on the performance requirements and the topology's advantages and disadvantages of the topology, a particular topology can be selected. In the general case, a specific ADC type exhibits an optimum performance for a specific bandwidth and resolution requirement. Sigma delta ADC's are applicable for medium bandwidth and high resolution[1]. High resolutions in this topology are

Figure 2.1. ADC operations depicted as a function across the signal domains

achievable due to oversampling and noise shaping through loop filtering. A detailed explanation of  $\Sigma - \Delta$  ADC's is given in the next section.

#### 2.1. Overview and Background of Sigma-Delta ADC's

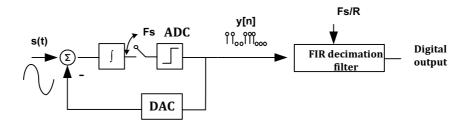

The block diagram of a typical sigma delta ADC is given in Fig. 2.2. The ADC is composed of two succeeding stages: The first is the delta sigma modulator which

converts the analog input signal to a pulse code modulated train of pulses. The second stage is the digital low pass filter and the decimator. The operation of this stage will be explained later. If the modulator given in Fig. 2.3 is examined in detail, it can be

Figure 2.2. Delta sigma ADC block diagram

Figure 2.3. Sigma-delta modulator

seen that the modulator in its simplest form consists of a negative feedback loop with a filter and a comparator in the feed-forward path. In first order implementations, the filter is an integrator. The output of the comparator is fed back to the input to generate an error signal. If a two value output quantizer is used the error signal cannot reach to zero value and always makes the comparator generate an alternating output PCM pulse.

#### 2.1.1. Types of Sigma-Delta Modulation

Depending of the domain of operation, sigma-delta modulators can be constructed in two types: Discrete-time sigma delta and continuous time sigma-delta ADC's . Both ADC's are synchronous since domain 3 in Table 2.1 is not visited in any part of their operation. Table 2.1. ADC operations depicted as a function across the signal domains. Arrows showing possible domain transitions for ADC's. A discrete-time  $\Sigma - \Delta$  ADC between

domain 1 ,2 and 4. Continuous time  $\Sigma - \Delta$  ADC between in domains 1 and 4.

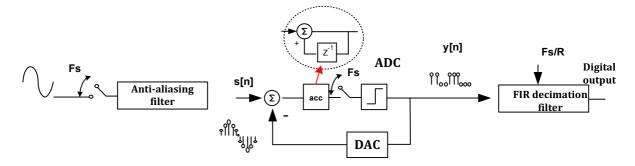

These ADC's use synchronous circuit elements. In Fig. 2.4 a discrete time ADC is shown. The signal is sampled first and then passed through an anti-aliasing filter. The resulting sampled signal passes through a discrete time modulator. The integrator here is implemented as its discrete-time counterpart which is an accumulator. At every clock period, the state of the output changes. Although it is still the most popular  $\Sigma - \Delta$  architecture, it suffers from two big problems. The first is the power consumption generated by switching all the discrete time components in succeeding clock cycles. The other problem is the bandwidth requirement of the analog blocks such as the filter to handle sampled and held version of the input signal which are composed of multiple harmonics of the sampling clock frequencies. Despite its disadvantages, this type was very popular and still is the dominant architecture in usage, due to the relative simplicity of design. Continuous time versions of  $\Sigma - \Delta$  ADC's use continuous time components except the quantizer and the DAC in the feedback, which are clocked elements to realize the time sampling of the signal. A typical continuous time  $\Sigma$  –  $\Delta$  ADC is given in Fig. 2.5. This architecture solves some problems of its discrete time counterpart like excess power consumption and high bandwidth requirements for the components. Unfortunately, it introduces a new problem: clock jitter. Since all the components in the loop work in the analog domain, a shift in the frequency of the sampling clock is directly reflected to the whole signal path. This is a severe

Figure 2.4. Block diagram of a discrete time  $\Sigma - \Delta$  ADC

problem which deteriorates the performance and limits the usage of continuous time  $\Sigma - \Delta$  converters [5], [6].

Figure 2.5. Block diagram of a continuous time  $\Sigma - \Delta$  ADC

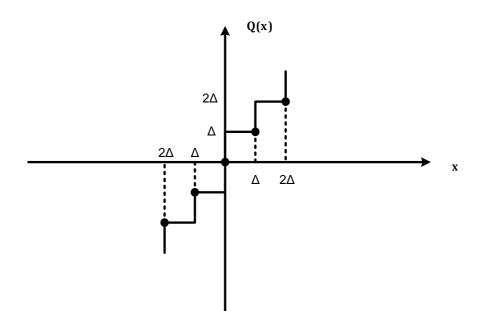

In all of the topologies, comparator is the building block of a quantizer. Quantization refers to discretization of the amplitude of the coming signal at certain time instants. A typical voltage transfer curve of a multi-bit quantizer is shown in Fig. 2.6. Quantization noise is the main noise source in the  $\Sigma - \Delta$  ADC's. The spectrum of the quantized signal was of interest and investigated in [7], [8]. It is worth to remind that in ADC's quantization, generally refers to discretization of the amplitude at certain time instants. Hence, it contains time sampling operation, too. Under these conditions assuming that quantization error and input signal is uncorrelated, this noise can be treated as having a white spectrum. In fact these signals have a correlation to some extend and this is more obvious when input signal is an exact multiple of the sampling frequency. But for calculations, white noise assumption is accurate enough to make coarse performance calculations of the modulator. Therefore, the quantizer can be replaced by a noise source with flat spectrum which is added to the signal in the loop. It has been shown that the circuit can be separated to two circuits for noise signal and input signal [9]. The resulting circuits are shown in Fig. 2.7. In this work, after

Figure 2.6. Multistep quantizer transfer characteristics  $\Sigma - \Delta$  ADC

some cumbersome calculations, the expression for SNR and NTF were given, which relate the performance to filter order and oversampling ratio . A typical second order

Figure 2.7. Separated circuits for noise and signal as given in [9].

synchronous sigma-delta modulator output spectrum is given in Fig 2.8. The signal is at 1 MHz and the sampling rate  $F_s$  is 100 MHz. The noise is shaped according to the NTF, hence the loop filter. The action of oversampling is seen as pushing the quantization noise away from the in-band.

A third possibility to build  $\Sigma - \Delta$  ADC's is the asynchronous  $\Sigma - \Delta$ . A coarse block diagram is given in Fig. 2.9. The output of the ASDM unlike the other two topologies is a PWM signal, and is not time sampled; i.e., not synchronized. This type

Figure 2.8. Typical spectrum of a second order synchronous modulator

Figure 2.9. The asynchronous  $\Sigma - \Delta$  modulator (ASDM)

of modulators is not new indeed. Nonlinear control applications such as heaters use this structure. The first studies were about the control aspects of these systems [10], [11]. The first possible use of ASDM in communication devices was given in [12], [13]. However, these devices have not received any attention until near time to be used in communication systems. The next work was on the use of ASDM's in electric inverter circuits as a Pulse Width Modulation (PWM) generator where an analytical treatment for ASDM's was also given in [14]. The possibility of applying ASDM to ADC is further investigated by design equations and performance metrics in [15]. Also, the causes that limit the performance were treated analytically. The first disadvantage is the lack of quantization noise suppression in the loop, since sampling is done after the ASDM. The second disadvantage is that the spectrum of an ASDM is much more noisy (contains signal harmonics) and distorted compared to ordinary SDM's. However, there are some advantages such as the possibility of operations at very high speeds without the need of an external clock signal. Moreover the inherent variation of the limit cycle frequency due to jitter does not corrupt input signal, because the Bessel components are sufficiently suppressed in the in-band. Working at high speeds help to separate the noise harmonics from the baseband sufficiently. An implementation of a monolithic ASDM is given in [16].

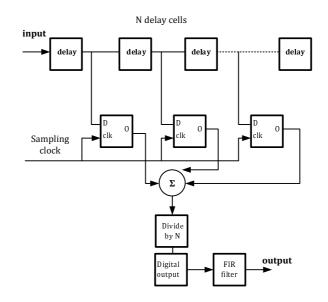

If ASDM is aimed to be used in an ADC application, it has to be followed by a sampler and filter to get a final digital signal. Possible structures are depicted in Fig. 2.10. Type (a) is the option where an ordinary sampler at a rate equal to a high sampling frequency ( $F_s$ ) is used. The sampled signal should be fed to an ordinary FIR filter or a Cascaded Integration Comb (CIC) filter [26]. Type (b) is an analog implementation of a FIR filter with delay lines called Time to Digital converter (TDC). When using this option, a lower sampling rate can be used.

The last configuration (c) which is the contribution of this dissertation to directly use an semi-analog version of the CIC filter. The detailed operation of this filter is given in Section four. To get rid of sampling at high frequencies, the integrator parts of the filter which are basically digital accumulators are build with a full adder and an analog delay. The incoming pulses from the ASDM are counted in terms of this delay. In integration parts, the signal will be slowed. Then a sampler samples the signal and finally the digital signal passes through a digital comb filter.

Figure 2.10. Possible sampling and filtering combinations of ASDM signals to get a digital ADC output

### 3. MATHEMATICAL ANALYSIS OF ASDM's

The aim of this chapter is to provide readers with the following:

- To give different control theory approaches to study the behavior of nonlinear ASDM systems in a unified manner

- To give period and frequency expressions of the delay and hysteresis quantizer based ADSM.

- To give the possible use of a quantizer with time delay as a building block of an ASDM.

Figure 3.1. A first order ASDM block diagram

A typical first order ASDM is given in Fig. 3.1. The nonlinear function of the quantizer is depicted as 'N(u)'. To write a differential equation of the output and input, a mathematical function is needed for presenting the nonlinearity 'N'. The function tanh(n.u) can serve this purpose, because of its saturation characteristics.

$$N(u) = \tanh(n.u) \tag{3.1}$$

$$e(t) = x(t) - y(t)$$

(3.2)

$$e(t) = u(t) = x(t) - y(t) = \frac{d \left[ \tanh^{-1} y(t) \right]}{d(t)} = \frac{n}{1 - n^2 y^2} (dy/dt)$$

(3.3)

Finally a differential equation is obtained as below:

$$\frac{dy}{dt}n - n^2y^3 + n^2xy^2 + y - x = 0$$

(3.4)

(3.4) is of Abel type and has no known closed type solution [25]. For 'x = 0' a transient exponential decay is observed. As another alternative, control theory techniques should be used. Let's consider a nonlinear system based on hard limiter called relay systems in control theory. The block diagram of such a system is given in Fig. 3.2. Most of the

Figure 3.2. A relay system

time, it is of interest to have dead-zones in the relay characteristics. The characteristics of the hard limiter are given in Fig. 3.3 and the analytical expression in (3.5).

Figure 3.3. Hardlimiter with hysterisis characteristics

$$u(t) = \left\{ \begin{array}{ll} e > \varepsilon & or \quad (e > -\varepsilon \quad and \ u(t-) = \ d) \ then \ u(t) = \ d \\ e < -\varepsilon & or \quad (e < \ \varepsilon \quad and \ u(t-) = -d) \ then \ u(t) = -d \end{array} \right\}$$

(3.5)

#### 3.1. Describing Function Approach

One way to deal with the nonlinearity in the loop is linearizing it. A process called 'quasi-linearization' allows one to represent a nonlinear function as a variable gain linear function [17], [18]. The idea can be better understood by the use of Fig. 3.4. The variable gain should be defined only for a specific signal; e.g, sinusoidal signal with a specific frequency. 'The sinusoidal describing function (DF)' is given as the following

Figure 3.4. Hardlimiter characteristics (left), DF gain according to amplitude (right)

relation:

$$N(a,\omega) = \frac{phasor\ representation\ of\ the\ output\ component\ at\ frequency\ \omega}{phasor\ representation\ of\ the\ input\ component\ at\ frequency\ \omega} = \frac{A_1(a,\omega)}{A} e^{j\phi_1(A,\omega)}$$

(3.6)

'DF' is the complex first harmonic gain of a nonlinearity driving a sinusoidal signal. It should be noted that there exist also exponential and gaussian describing functions [17], [18]. But in  $\Sigma - \Delta$  applications, use of the sinusoidal function is sufficient when limit cycle properties are studied. However, noise added by amplitude discretization can be studied using the other DF's. From now on, the term DF is used only for sinusoidal signals. For the ideal relay type characteristics the DF is given as [17]:

$$N(A) = \frac{4}{\pi} \frac{D}{A} \tag{3.7}$$

where A denotes the amplitude of the input signal and D is the saturation output. For the relay with hysteresis, the DF equation is [17]:

$$N(a,\phi) = \frac{4D}{\pi A}\sqrt{1 - (h/A)^2} - j\frac{4h}{\pi A^2} = \frac{4D}{\pi A}e^{-j(sin^{-1}h/A)}$$

(3.8)

To find the point of oscillation, hence the limit cycle frequency, 'Harmonic Balance equation' which is analogous to 'Barkhausen criterion' in oscillators is used. The oscillation occurs when the following condition is satisfied [18].

$$1 + N(A)G(i\omega) = 0 \tag{3.9}$$

If  $G(s) = 1/i\omega$  an integrator, Eq. 3.9 gives

$$\frac{1}{\omega i} \left( \frac{4D}{\pi A} \sqrt{1 - (h/A)^2} - i \frac{4h}{\pi A^2} \right) = -1$$

(3.10)

$$\omega = \frac{4h}{\pi\epsilon} \tag{3.11}$$

This expression is valid for  $G(s) = \frac{1}{s}$ ; for different filter functions, a direct expression may not necessarily be found.

#### 3.2. Time Domain Approach

Time domain approach has been utilized mostly in early papers [20],[19]. Especially, the work in [19] is concerned with state space analysis of nonlinear systems.

A system like that in Fig. 3.2, may sustain periodic oscillations called 'limit cycle oscillation' when no input is applied. If the input to the circuit is zero, e = -y. The ASDM circuit is the same as the system in Fig. 3.2 with zero input condition. It should be noted that if no input is applied, the position of the relay is not important for the limit cycle behavior. For the linear part of the circuit, state space representation is as

follows.

$$\frac{dx}{dt} = Ax + Bu$$

$$y = Cx$$

(3.12)

The state space equation can be integrated to obtain the transfer function related to the time as:

$$f(t) = C(I + e^{At})^{-1} \int_0^t (e^{A\tau} B d\tau)$$

(3.13)

The initial state x(0), state x(t) and output y(t) can be calculated accordingly with the formulas below:

$$a = x(0) = (I + e^{Ah})^{-1} \int_0^h (e^{A\tau} B d\tau) d$$

(3.14)

$$x(t) = e^{At}x(0) + \int_0^t e^{A(t-\tau)}Bu(\tau)d\tau$$

(3.15)

$$y(t) = C\left(e^{At}x(0) + \int_0^t e^{A(t-\tau)}Bu(\tau)d\tau\right) + Du(t) > -\epsilon$$

(3.16)

Defining some symbols as the following will put the above equations in a more convenient form.

$$\phi = e^{At} \qquad \Gamma = \int_0^t e^{As} ds B$$

$$x(h) = \phi a - \Gamma d \qquad (3.17)$$

It will be clearer if the waveforms in the circuit are examined through Fig. 3.5. In the analysis, it is first assumed that periodic oscillation with period T=2h exists. Then, necessary conditions for these oscillations are investigated. It is clear that the quantizer switches at time instants of multiple of 'h'. At the instant of switching (t=h) the gain

Figure 3.5. Waveforms in the hardlimiter circuit. 'e' is signal before the nonlinearity and u is the output of the nonlinearity. Dashed lines correspond to hysteresis levels of the nonlinearity.

of the nonlinearity should be exactly  $\left(\frac{\epsilon}{d}\right)$  [21]

$$f(h) = C(I + e^{Ah})^{-1} \int_0^h (e^{A\tau} B d\tau) = \frac{\epsilon}{d}$$

(3.18)

Eq. 3.18, refers to the gain of the nonlinearity block at switching instants. If this function intersects the necessary gain at the frequency where the intersection is, an oscillation should exist. A second condition for oscillation is that y(t) should not switch to the other threshold. That is,

$$y(t) > -\epsilon \quad for \quad 0 < t < h. \tag{3.19}$$

A third necessary condition for limit cycle oscillation is that the signal 'd(e(t))/dt' should be positive or in other words 'd(y(t))/dt' should be negative at time=h. That is the same to say it is negative at t=0. To put in formal form it should be ensured that:

$$\frac{dy(0)}{dt} = \frac{dx(0)}{dt}C > 0 \tag{3.20}$$

This is called the velocity condition and used to check for local stability. However, it should be also checked if the oscillation will change frequency or it is asymptotically stable.

## 3.3. Tsypkin's Frequency Domain Approach

There is some frequency domain related work done in this field [23],[24]. The main idea is that: A pulse response of a linear system can be found exactly by sampling the response with zero order hold with period 'h', where '2h' denotes the limit cycle period. Considering zero order sampled version of G(s) as H(z) the following equations are obtained.

$$H(z) = C((zI - \phi)^{-1})\Gamma$$

(3.21)

The value H(-1) gives the gain of G(s) at the switching instants so [22]:

$$H(-1) = \frac{-\epsilon}{d} \tag{3.22}$$

An alternative representation of the H(z) is given as,

$$H(z) = \sum_{n=-\infty}^{\infty} \frac{1 - z^{-1}}{\log z + 2\pi i n} G(\frac{1}{h} \log z + \frac{2\pi i n}{h})$$

(3.23)

The velocity function which is  $H_v(-1) = sG(s)$ , can be calculated as

$$H_v(-1) = \frac{4\omega}{\pi} \sum_{n=0}^{\infty} Re \ G(i\omega(1+2n))$$

(3.24)

The Tsypkin function is defined as the sum of H(z) and K(z) as:

$$\Lambda(i\omega) = \frac{4\omega}{\pi} \sum_{n=0}^{\infty} Re \ G(i\omega(1+2n)) + i\frac{4}{\pi} \sum_{n=0}^{\infty} \frac{Im \ G(i\omega(1+2n))}{2n+1}$$

(3.25)

The Tsypkin function is the complex function of the pulse response of G(s) and velocity of 'G(s)s'. The polar plot of ' $\Lambda(i\omega)$ ' is called 'Typskin plot' or 'hadograph'. In order to obtain the point of the limit cycle, this curve should be intersected with  $y = \frac{-\epsilon}{d}$ . The real part of the intersection should be negative to ensure velocity considerations. Normally, this is done by plots but numeric calculations are also possible. Especially when ' $G(i\omega)$ ' decreases rapidly, as in the case of SDM's which have integrators, approximations are also possible. In the case of a first order ASDM, since  $G(i\omega) = \frac{1}{s}$ ,

$$H(-1) = \frac{4}{\pi} \sum_{n=0}^{\infty} \frac{ImG(i\omega(1+2n))}{1+2n} \approx \frac{4}{\pi} ImG(i\omega)$$

(3.26)

and

$$H_v(-1) = \frac{4\omega}{\pi} \sum_{n=0}^{\infty} ReG(i\omega(1+2n)) \approx \frac{4\omega}{\pi} ReG(i\omega)$$

(3.27)

Thus the point of intersection gives:

$$\omega_c \approx \frac{4}{\pi} \frac{d}{\epsilon} \tag{3.28}$$

If the terms in the series is also taken into account:

$$\omega = \frac{4}{\pi} \frac{d}{\epsilon} \left( 1 + \frac{1}{9} + \frac{1}{25} \right) \tag{3.29}$$

So the actual frequency is about 15.1% off. This deviation is also present with the describing function method which is based on the principle of the gain for the first harmonic of the pulse. The amount of error caused by DF approximation is small where the order of G(s) is high, however large deviations are present when the order is small. Stability of the limit cycle can be checked with the Jacobian of the Poincaré map as below:

$$W = (I - \frac{vC}{Cv})\Phi \tag{3.30}$$

According to its accurate solutions, Typskin method is better for our analysis. Since a first order system is already investigated in the above sections, it is better to look for a second order system. This time  $G(s) = \frac{1}{s^2}$ .

$$\Phi = e^{Ah} = 1 + Ah + A^2 h^2 / 2 + \dots$$

$$= \begin{bmatrix} 1 & 0 \\ 0 & 1 \end{bmatrix} + \begin{bmatrix} 0 & h \\ 0 & 0 \end{bmatrix} = \begin{bmatrix} 1 & h \\ 0 & 1 \end{bmatrix}$$

(3.31)

$$\Gamma = \int_0^h e^{As} B ds = \int_0^h \begin{bmatrix} 1 & s \\ 0 & 1 \end{bmatrix} \begin{bmatrix} 0 \\ 1 \end{bmatrix} ds = \int_0^h \begin{bmatrix} s \\ 1 \end{bmatrix} ds = \begin{bmatrix} h^2/2 \\ h \end{bmatrix}$$

(3.32)

$$H(z) = C(zI - \phi)^{-1}\Gamma = \begin{bmatrix} 1 & 0 \end{bmatrix} \begin{bmatrix} z - 1 & -h \\ 0 & z - 1 \end{bmatrix}^{-1} \begin{bmatrix} h^2/2 \\ h \end{bmatrix} = \frac{h^2(z+1)}{2(z-1)^2} \quad (3.33)$$

Clearly, H(-1) = 0 so limit cycles exist when there is no hysteresis i.e. when  $\epsilon = 0$ , but with arbitrary period (depending on the initial condition of x). Any value of 'h' will give H(-1)=0. The stability of the limit cycle should also be checked. To find a = x(0), applying  $a = \Phi a - \Gamma d$  and taking d=1 and solving the equation below gives the 'a' value as,

$$a = \begin{bmatrix} 1 & h \\ 0 & 1 \end{bmatrix} a - \begin{bmatrix} h^2/2 \\ h \end{bmatrix} and a = \begin{bmatrix} 0 \\ h/2 \end{bmatrix}$$

(3.34)

$$v = Aa + Bd = \begin{bmatrix} 0 & 1 \\ 0 & 0 \end{bmatrix} \begin{bmatrix} 0 \\ h/2 \end{bmatrix} = \begin{bmatrix} h/2 \\ 0 \end{bmatrix}$$

(3.35)

$$W = (I - \frac{vC}{Cv})\Phi = \begin{bmatrix} 0 & 0\\ -2/h & -1 \end{bmatrix}$$

(3.36)

$$det(SI - W) = \begin{bmatrix} z & 0 \\ 0 & z \end{bmatrix} - \begin{bmatrix} 0 & 0 \\ -2/h & -1 \end{bmatrix} = \begin{bmatrix} z & 0 \\ 2/h & z+1 \end{bmatrix}$$

(3.37)

The roots are inside the limit circle so the oscillations are locally stable but not asymptotically stable. It is worth to note that when hysteresis exists, no oscillations will be present.

Time delay circuit components might be also interesting, since all quantizers in ADC's have some delay. So when the loop filter G(s) has a finite delay, the state space equations become:

$$\frac{dx(t)}{dt} = Ax(t) + Bu(t - \tau)$$

$$y(t) = Cx(t)$$

(3.38)

In order to hold the zero order sampling conditions assuming that the delay time is  $0 < \tau < h$ , where h is the first switching time, the following formula holds for the state vector 'x':

$$x(kh+h) - \Phi x(kh) = \int_{kh}^{kh+h} e^{A(kh+h-s')} Bu(s'-\tau) ds'$$

(3.39)

Defining functions  $\Gamma_0$  and  $\Gamma_1$

$$x(kh+h) - \Phi x(kh) = \underbrace{\int_{kh}^{kh+\tau} e^{A(kh+h-s')} ds' B}_{\Gamma 0} \quad u(kh-h) + \underbrace{\int_{kh+\tau}^{kh+h} e^{A(kh+h-s')} ds'}_{\Gamma 1} \quad u(kh)$$

(3.40)

$$x(kh+h) = \Phi x(kh) + \Gamma_1 u(kh-h) + \Gamma_0 u(kh)$$

(3.41)

The transfer function at time h and the equivalent value is:

$$f(h) = C(I + \Phi(h))^{-1}(\Gamma_0(h) - \Gamma_1(h)) = \epsilon/d$$

(3.42)

It is worth to investigate any possibility of first or second order systems for our ASDM converter which is either a delayed integrator or an delayed low-pass filter. In the general case, when the state space equation is as follows

$$\frac{dx(t)}{dt} = \alpha x(t) + \beta u(t-\tau)$$

(3.43)

$$\Gamma_0 = \int_0^\tau e^{As} ds B = \int_0^\tau e^{\alpha s} ds \beta = \beta \frac{e^{\alpha(h-\tau)} - 1}{\alpha}$$

(3.44)

$$\Gamma_1 = \int_{\tau}^{h-\tau} e^{As} ds B = \int_{\tau}^{h-\tau} e^{\alpha s} ds = \beta \frac{e^{\alpha(h)} - e^{\alpha(h-\tau)}}{\alpha}$$

(3.45)

The gain at the switching instants is

$$f(h) = C(I + \Phi(h))^{-1} (\Gamma_0(h) - \Gamma_1(h))(-1)^m = \epsilon/d = \beta \frac{2e^{\alpha(h-\tau)} - e^{\alpha h} - 1}{\alpha(1 + e^{\alpha h})}$$

(3.46)

If the delay is adjusted, it is wiser to not allow any hysteresis (hardlimiter), not to increase the dimension of the equation. If that is the case,

$$h = \frac{1}{\alpha} ln \frac{1}{2e^{\alpha \tau} - 1} \tag{3.47}$$

The integrator with delay is when  $\alpha = 0$

$$h = \tau/2 \tag{3.48}$$

So  $T = 4\tau$ . If  $\alpha = 1$  which corresponds to the system with a delayed lowpass filter.

$$h = ln \frac{1}{2e^{\tau} - 1} \tag{3.49}$$

Exploring a second order integrator as a loop filter, which is  $G(s) = \frac{e^{-s\tau}}{s^2}$ , the following relations are obtained.

$$\Phi = \begin{bmatrix} 1 & h \\ 0 & 1 \end{bmatrix}$$

(3.50)

$$\Gamma_0 = \int_0^{h-\tau} e^{As} ds B = \left\{ \int_0^{h-\tau} \begin{bmatrix} 1 & s \\ 0 & 1 \end{bmatrix} ds \right\} \begin{bmatrix} 0 \\ 1 \end{bmatrix} = \begin{bmatrix} (h-\tau)^2/2 \\ h-\tau \end{bmatrix}$$

(3.51)

$$\Gamma_1 = \int_{h-\tau}^h e^{As} ds B = \left\{ \int_{h-\tau}^h \begin{bmatrix} 1 & s \\ 0 & 1 \end{bmatrix} ds \right\} \begin{bmatrix} 0 \\ 1 \end{bmatrix} = \begin{bmatrix} h\tau - \tau^2/2 \\ \tau \end{bmatrix}$$

(3.52)

$$\Gamma_0 - \Gamma_1 = \begin{bmatrix} h^2/2 + \tau^2 - 3h\tau \\ h - 2\tau \end{bmatrix}$$

(3.53)

$$f(h) = C(I + \Phi)^{-1}(\Gamma_0 - \Gamma_1) =$$

(3.54)

$$\begin{bmatrix} 1 & 0 \end{bmatrix} \begin{bmatrix} 2 & -h \\ 0 & 2 \end{bmatrix} \begin{bmatrix} h^2/2 + \tau^2 - 3h\tau \\ h - 2\tau \end{bmatrix} =$$

(3.55)

$$\tau^2/2 - h\tau \tag{3.56}$$

For no hysteresis, period of the oscillations is found as  $T = 2h = 2\tau$ . It is seen that increasing the integration order halved the period of oscillations. The oscillations however are not stable. A basic idea for this is that the double integrator gives a 180 degrees phase shift and the delay an additional amount. Since the total phase is above 180 degrees and the NL(Non-linear) block will also provide a delay, the oscillations will grow over time.

## 3.4. Spectral Analysis of ASDM's

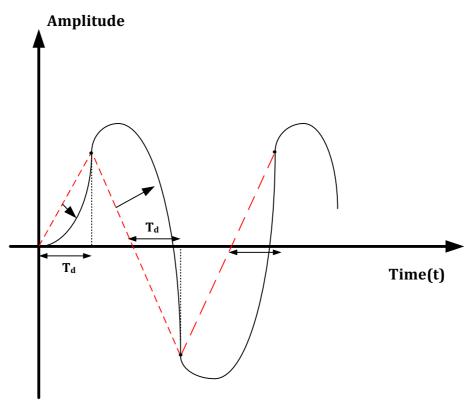

The first order ASDM in the input signal modulates the duty cycle of the square wave output. But this type of modulation is a little different from original PWM signals; since the frequency of the signal changes also with the amplitude of the input as in Fig. 3.6.

Figure 3.6. Sinusoidal signal modulated PWM

Analyzing the circuit given in Fig. 3.1. If the hysteresis levels are at  $\pm \epsilon$ , the integrator output signal which will be a ramp function, changes direction when reaching one of the thresholds. The total period  $T = T_1 + T_2$  is the sum of up and down ramps. Time spent in these regions are related by the integrator input as follows:

Figure 3.7. Integrator output of the first order sigma delta modulator

$$T_1 = 2 \frac{\epsilon}{K(1+v)}$$

$$T_2 = 2 \frac{\epsilon}{K(1-v)}$$

(3.57)

Then, the period of one cycle of oscillation and the expression for the duty cycle will be as follows,

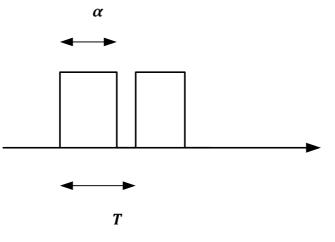

$$T = T_1 + T_2 = \frac{4\epsilon}{k(1 - v^2)}$$

$$\alpha = (the \ high \ period) = \frac{T_1}{T} = \frac{(1 + v)}{2}$$

(3.58)

Since the formula of the duty cycle shows a relation to the input, this configuration can be used as a modulator. Frequency domain analysis can be done using Fourier series representation of a pulse width modulated signal. For a pulse width modulated

Figure 3.8. Duty cycle modulated wave

signal with constant carrier frequency and a modulated duty cycle the Fourier series expansion is as follows:

$$s(t) = A_0 + \sum_{n=0}^{\infty} A_n \cos(\omega_c n + \Phi_n)$$

(3.59)

$$A_0 = V_{dc}(\alpha - \frac{1}{2})$$

$$A_n = \frac{V_{dc}}{(n\pi)} sin(n\pi\alpha)$$

If a sinusoidal signal is used as input :

$$v(t) = Msin(\omega_m t) \tag{3.60}$$

$$\alpha = \frac{1}{2} + \frac{Msin(\omega_m t)}{2} \tag{3.61}$$

The phase ' $\Phi_n$ ' and the frequency change with the input signal was given in the previous part. It can be seen the period, hence the frequency is modulated with the inverse of the square of the input amplitude. The instantaneous frequency of the carrier wave is as below:

$$f_i = f_c (1 - v^2) \tag{3.62}$$

If the input is a sinusoidal time varying signal  $Msin(\omega_m t)$ , then,

$$\omega_i = \omega_c (1 - M^2 \sin^2(\omega t)) = \omega_c \left( 1 - \frac{1}{2}M^2 + \frac{1}{2}M^2 \cos(2\omega_m t) \right) = \omega_o + \omega_\Delta \qquad (3.63)$$

$$\omega_0 = \omega_c (1 - \frac{1}{2}M^2) \tag{3.64}$$

$$\omega_{\Delta} = \frac{1}{2}M^2 \cos(2\omega_m t) \tag{3.65}$$

The ' $\omega_c + \phi$ ' expression is in the frequency modulated signal form. In frequency mod-

ulation, the deviation index  ${}^{\prime}\!\beta$  ' is defined a follows:

$$\beta = \frac{\omega_{\Delta}}{2\omega_m} \tag{3.66}$$

$$\beta_M = v_m \frac{\pi}{2} \tag{3.67}$$

The 'nth harmonic' of the output square wave is in Euler form as:

$$S_n = A_n \Re e \left\{ e^{jn\omega_c t} e^{jn\beta sin(2\omega_m t)} \right\}$$

(3.68)

This expression results in a Bessel series form,

$$S_n = A_n \sum_{k=-\infty}^{\infty} J_k(n\beta) \cos(n\omega_c t + n2\omega_m t)$$

(3.69)

Besides the frequency dependency of the carrier frequency ' $\omega_c$ '; the amplitude of the Fourier series components are also modulated, which generates also an Amplitude Modulation

$$A_n(t) = \frac{V_{dc}}{n\pi} sin \left[ n \frac{\pi}{2} (1 + M sin(\omega_m t)) \right]$$

(3.70)

Combining these two modulation types, the final expression becomes:

$$S_{n}(t) = \frac{V_{dc}}{n\pi} sin(n\frac{\pi}{2}) \sum_{k=-\infty}^{\infty} J_{k}(n\beta) cos(n\beta_{M}sin(\omega_{M}t)) \cdot cos(n\omega_{c}t + n2\omega_{M}t) + \frac{V_{dc}}{n\pi} sin(n\frac{\pi}{2}) \sum_{k=-\infty}^{\infty} J_{k}(n\beta) sin(n\beta_{M}sin(\omega_{M}t)) \cdot cos(n\omega_{c}t + n2\omega_{M}t)$$

(3.71)

In our design, mostly the baseband and the first harmonic of the carrier wave is of

importance (since the first harmonic contents are in the band of interest) which are

$$S_0(t) = \frac{s(t)Vdc}{2}$$

$$S_1(t) = \frac{V_{dc}}{\pi} \sum_{n=-\infty}^{\infty} \sum_{m=-\infty}^{\infty} J_{2n}(\beta)J_k(\beta_M) \cdot \cos(\omega_c t + (2n+m)\omega_M t)$$

(3.72)

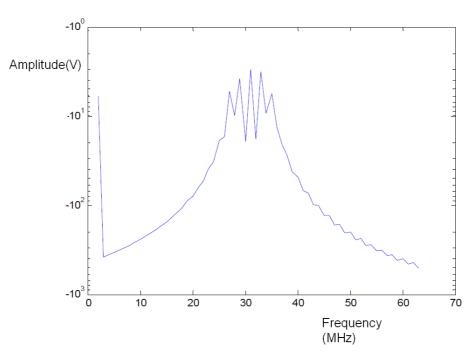

A carrier frequency ' $\omega_c$ ' 32 MHz and a input signal of 1 MHz with amplitude of 0.5V denoted by 'M', the computed spectrum looks like in Fig. 3.9.

$$\beta = \frac{\omega_{\Delta}}{2\omega_m} = \frac{1/2M^2\omega_c}{2\omega_m} = \frac{M\omega_c}{4\omega_m} = 4$$

(3.73)

$$\beta_M = M \frac{\pi}{2} = 0.79 \tag{3.74}$$

Although it was shown before that the double integrator with delay is unstable, let's

Figure 3.9. Calculated spectrum of the above signals using Eq. 3.72

still investigate a stable second order polynomial type  $G(s) = (s+a)(s+b) = s^2 + (a+b)s + ab$  and its spectrum characteristics. Note that a stable G(s) does not necessarily

mean a stable limit cycle. Limit cycle stability also depends on the time delay. Its typical waveform is given in the Fig. 3.10. Since the system has a stable limit cycle the output of the filter is bounded.

Figure 3.10. Filter outputs of a first order (dashed) and second order(solid) ASDM

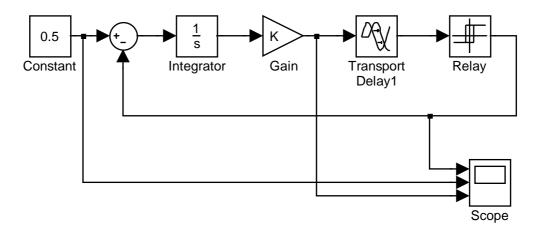

# 3.5. Simulink model for ASDM for behavioral simulations

The behavioral simulations for ASDM's can be done using Matlab Simulink. Since simulink works at discrete time steps, the simulation time should be chosen such that it is much smaller compared to the loop delay. The Simulink model of the first order ASDM constructed in this dissertion is given in Fig. 3.11.

#### 3.6. Frequency Scaling

To operate in any desired frequency, scaling properties may be used. To change the frequency of the limit cycle, delay times and hysteresis values can be modified

Figure 3.11. Matlab Simulink model for behavioral simulation of first order ASDM

accordingly. The filter DC gain( $A_0$ ) should also be scaled to the desired frequency. This property can be used as follows. If a first order ASDM system is designed with a 1 second loop delay and filter DC gain as 1, if changing loop delay to 1 micro second, filter gain should be changed to  $10^6$ .

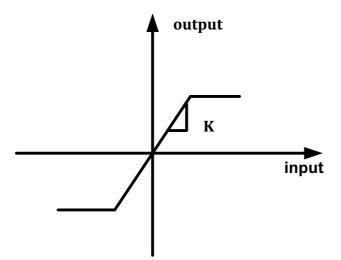

#### 3.7. Effect of Finite Slope of the Nonlinearity

Unfortunately, in real circuit design, ideal relay characteristics are not achievable. The real transfer characteristics of saturation type. The finite slope of these character-

Figure 3.12. Filter outputs of a first order (dashed) and second order(solid) ASDM

istics may have an effect on the operation of the circuit. If the delay is not large enough

to let the filter output reach the saturation region, the oscillation may die out. The condition of oscillation can be found precisely to replace the nonlinearity by a linear function with slope 'K'; and investigate the Nyquist stability criterion. For the first order filter with delay and no hysteresis:

$$G(s)K = -1 \tag{3.75}$$

$$KT_d \ge \pi/2 \tag{3.76}$$

In the designs it will be of great importance to use high gain comparators if the delay is not controllable.

#### 3.8. Spectrum of behavioral simulation of first order ASDM

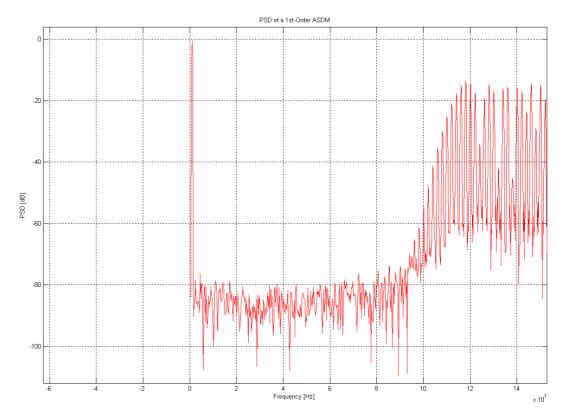

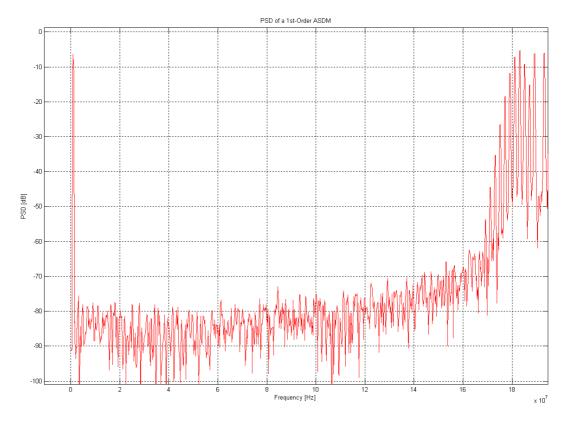

The spectrum of the behavioral simulation of an ASDM with a limit cycle frequency is given in Fig. 3.13. As it can be seen for a 1 MHz input signal with a bandwith of 10 MHz simulated spectrum can give a signal to noise ratio about 90 dB when limit cycle frequency is 90 dB. So large SNR values can be achievable. If the system has an element with distortion e.g creating a 3rd harmonic the spectrum in Fig. 3.14 is obtained. As it can be seen the possible nonlinearity in the filter or input signal creates odd harmonics which creates a noise floor. So, in order to achieve high SINAD values, the linearity of the ASDM should be as high as possible. One interesting thing is the case when both 3rd order distortion and a DC offset is present in both time. This time second order harmonics will exist in the spectrum and the magnitude is directly depended on the magnitude of the offset voltage.

In this section, using the describing function approach, an approximate oscillation frequency was found for a first order ASDM. The time-domain approach was utilized to derive an oscillation condition. Then, Tsypkin's frequency domain approach was investigated in order to calculate the oscillation frequency more accurately. The same approach was also applied to find the oscillation criteria. Also, the comparator with hysteresis was exchanged with a delayed comparator in order to be closer to practical

Figure 3.13. Spectrum of the Simulink simulated first order ASDM

Figure 3.14. Spectrum of the Simulink simulated first order ASDM with odd order distortion

implementation. Finally, spectral analysis was utilized to study the characteristics of oscillation in more detail.

# 4. DECIMATION FILTERS IN $\Sigma - \Delta$ ADC's

## 4.1. Introduction

In sigma delta modulators oversampling is used to spread the quantization noise over much higher frequencies than the in-band. The limit cycle frequency which is usually much higher than the input bandwidth in ASDM's, is also a similar concept. This time, the intermodulated signal components are pushed away from in band. In both sigma delta modulators, the output is a 1-bit signal with a high rate. Also this high bit stream contains noise at high frequencies. In order to make it usable, the high frequency noise should be removed by low pass filtering. Secondly, the bit rate should be lowered to a more useful value. This process is called decimation filtering. A typical decimation filtering operation is shown in Fig. 4.1.

Figure 4.1. Decimation filter frequency response shown on the PSD of a synchronous sigma delta modulator output graph

#### 4.2. Digital Filter Basics

In synchronous  $\Sigma - \Delta$  ADC's digital filtering is used, to get rid of the high frequency noise components due to the oversampling. The first method to realize a digital low-pass filter is to use conventional FIR filtering where the block digram is shown in Fig. 4.2. This type of a filter is a non-recursive filter. The signal and its delayed versions are summed after multiplications with distinct coefficients to get the desired filter function.

$$H(z) = h_0 + h_1 z^{-1} + h_2 z^{-2} + \dots + h_n z^{-n}$$

(4.1)

FIR filters are easy to build and are always stable. Therefore they are preferred to

Figure 4.2. Conventional FIR filtering