# FAST CIRCUIT TOPOLOGIES FOR FINDING THE MAXIMUM OF n k-BIT NUMBERS

by

Bilgiday Yüce B.S., Electrical & Electronics Engineering, TOBB University of Economics and Technology, 2010

Submitted to the Institute for Graduate Studies in Science and Engineering in partial fulfillment of the requirements for the degree of Master of Science

Graduate Program in Electrical & Electronics Engineering Boğaziçi University

2013

# FAST CIRCUIT TOPOLOGIES FOR FINDING THE MAXIMUM OF $n\ k$ -BIT NUMBERS

#### APPROVED BY:

| Prof. Günhan Dündar              |  |

|----------------------------------|--|

| (Thesis Supervisor)              |  |

|                                  |  |

| Assoc. Prof. H. Fatih Uğurdağ    |  |

| (Thesis Co-supervisor)           |  |

|                                  |  |

| Assoc. Prof. Şenol Mutlu         |  |

|                                  |  |

| Assoc. Prof. Sezer Gören Uğurdağ |  |

|                                  |  |

| Assist. Prof. İ. Faik Başkaya    |  |

DATE OF APPROVAL: 11.06.2013

#### ACKNOWLEDGEMENTS

It would not have been possible to bring about this thesis without the support and help of several individuals around me, to only some of whom it is possible to give particular mention here.

First, I would like to thank my thesis advisors Assoc. Prof. H. Fatih Uğurdağ and Prof. Günhan Dündar for their invaluable guidance and support throughout the development of this thesis. I would like to express my deepest gratitude to Assoc. Prof. H. Fatih Uğurdağ for his guidance, care, and patience. He also provided me an excellent atmosphere throughout my research. His continuous help with all kind of difficulties, which I encountered during my M.S. years, and his trust in me always kept me motivated. I am also really thankful to Prof. Günhan Dündar for dedicating his valuable time for my thesis and for his suggestions that have enhanced this thesis.

I would like to thank Assoc. Prof. Sezer Gören, Assoc. Prof. Şenol Mutlu and Asst. Prof. İ. Faik Başkaya for taking part in my thesis committee and for their time. In particular, Assoc. Prof. Sezer Gören's helpful comments, insightful discussions, and constructive feedback have greatly improved the quality of this work.

Also, I want to thank all of my friends who made my life enjoyable throughout my graduate education. Especially, I want to mention Abdullah Sarıduman, Barış Esen, Berkan Yaman, Doğan Ulus, Erdem Ulusoy, Fatih Temizkan, Furkan Şahin, Gökhan Güner, İsmail Kara, İsmail Terkeşli, Kenan Türksoy, Mert Kaya, and Waqas Hussain.

In addition, I would also like to thank TÜBİTAK for supporting me through BİDEB scholarship program between 2010-2012 and through ARDEB in 2013.

Finally, I am most grateful to my family members for their endless support and love throughout my life.

#### ABSTRACT

## FAST CIRCUIT TOPOLOGIES FOR FINDING THE MAXIMUM OF n k-BIT NUMBERS

Finding the value and/or address (position) of the maximum (or similarly minimum) element of a set of binary numbers is a fundamental arithmetic operation. Numerous systems, which are used in various application areas, require fast (low-latency) circuits to carry out this operation. In this thesis, we present a detailed literature survey of previous works and propose three circuit topologies that determine both value and address of the maximum (or similarly minimum) element within an n-element set of kbit binary numbers. Our proposed topologies are Array-based Topology (AbT), Hybrid Binary tree Topology (HBT), and Quad tree Topology (QT). The timing complexity of the fastest proposed architecture (AbT) is  $O(\log_2 n + \log_2 k)$ , whereas the timing complexity of the fastest topology in previous work is  $O(\log_2 n \log_2 k)$ . We wrote RTL code generators for the proposed topologies as well as their competitors. These automated generators are scalable to any value of n and k. Then, we applied a standard-cell based iterative synthesis flow, which finds the optimum timing through binary search. We obtained area, power consumption, and timing results for the proposed topologies as well as their competitors. Using these results, we also compute some combined performance metrics such that area-timing product (ATP), area-timing-square product (AT2P), power-timing product (PTP), and energy-timing product (ETP). The synthesis results showed that on the average, AbT is 1.61 times, QT is 1.28 times, and HBT is 1.01 times faster than the fastest in the literature.

### ÖZET

## n ADET k-BİT SAYININ EN BÜYÜĞÜNÜ BULMAK İÇİN HIZLI DEVRE TOPOLOJİLERİ

Bir sayı kümesinin maksimum (ya da minimum) elemanının değerini ve/veya adresini (pozisyonunu) bulmak en temel aritmetik işlemlerden biridir. Çeşitli uygulama alanlarındaki birçok sistem, bu işlemi yerine getiren hızlı devrelere ihtiyaç duyar. Bu tezde, *n* tane *k*-bit uzunluğunda sayının en büyüğünün (benzer biçimde en küçüğünün) hem değerini hem de adresini bulan devreler için detaylı bir literatür taraması ve üç tane veni devre topolojosi sunuvoruz. Onerdiğimiz topolojileri su şekilde adlandırıyoruz: "Array-based Topology (AbT)", "Hybrid Binary tree Topology (HBT)" ve "Quad tree Topology (QT)". Önerilen topolojilerden en hızlısı (AbT) işini  $O(\log_2 n + \log_2 k)$  sürede tamamlarken, literatürdeki en hızlı topolojinin işini tamamlaması için $O(\log_2 n\,\log_2 k)$ süre gerekir. Hem literatürdeki topolojiler hem de önerilen topolojiler için HDL kod üreteçleri yazdık. Bu otomatik kod üreteçleri herhangi bir n ve k değeri için ilgili topolojinin HDL kodunu üretebilecek yetenektedirler. Daha sonra ise, en iyi zaman kısıtını ikilik arama algoritmasına benzer bir yaklaşım ile bulan, yinelemeli ve standarddevre tabanlı bir sentez süreci uyguladık. Böylece, hem önerilen topolojiler hem de literatürdeki topolojiler için alan, güç tüketimi ve zaman sonuçlarını elde ettik. Ayrıca, bu sonuçları kullanarak şu birleşik başarım kıstaslarını da hesapladık: alan-zaman carpımı (AZC), alan-zaman-kare çarpımı (AZ2C), güç-zaman çarpımı (GZC) ve enerjizaman çarpımı (EZÇ). Sentez sonuçları, literatürdeki en hızlı devrenin, ortalamada AbT'den 1.61 kat, QT'den 1.28 kat ve HBT'den 1.01 kat daha yavaş olduğunu gösterdi.

## TABLE OF CONTENTS

| AC  | KNC   | OWLEDGEMENTS                                 | ii |

|-----|-------|----------------------------------------------|----|

| AB  | STR   | iACTi                                        | iv |

| ÖΖ  | ET .  |                                              | v  |

| LIS | ST OI | F FIGURES                                    | İx |

| LIS | ST OI | F TABLES                                     | xi |

| LIS | ST OI | F SYMBOLS                                    | ii |

| LIS | ST OI | F ACRONYMS/ABBREVIATIONS                     | V  |

| 1.  | INTI  | RODUCTION                                    | 1  |

|     | 1.1.  | Motivation                                   | 1  |

|     | 1.2.  | Contributions of the Thesis                  | 2  |

|     | 1.3.  | Outline of the Thesis                        | 3  |

| 2.  | PRE   | ELIMINARIES                                  | 4  |

|     | 2.1.  | Problem Definition                           | 4  |

|     | 2.2.  | Circuit Complexity and Performance Modeling  | 5  |

|     |       | 2.2.1. Area Modeling                         | 5  |

|     |       | 2.2.2. Delay Modeling                        | 6  |

|     |       | 2.2.3. Power Consumption Modeling            | 7  |

|     |       | 2.2.4. Combined Circuit Performance Measures | 7  |

|     |       | 2.2.5. Asymptotic <i>O</i> -notation         | 8  |

| 3.  | PRE   | EVIOUS WORK                                  | 0  |

|     | 3.1.  | Array Topology (AT)                          | 0  |

|     |       | 3.1.1. Theoretical Complexity of AT          | 2  |

|     | 3.2.  | Row Topology (RT)                            | 3  |

|     |       | 3.2.1. Theoretical Complexity of RT          | 4  |

|     | 3.3.  | Selection Topology (ST)                      | 5  |

|     |       | 3.3.1. Theoretical Complexity of ST          | .6 |

|     | 3.4.  | Traditional Binary Tree Topology (TBT)       | .6 |

|     |       | 3.4.1. Theoretical Complexity of TBT         | 9  |

|     | 3.5.  | Parallel Binary Tree Topologies (PBTs)       | 20 |

|    |      | 3.5.1.  | Ripple Carry Parallel Binary Tree Topology (RCT) $\ldots$          | 23 |

|----|------|---------|--------------------------------------------------------------------|----|

|    |      | 3.5.2.  | Carry Select Parallel Binary Tree Topology (CST)                   | 23 |

|    |      | 3.5.3.  | Carry Look-ahead Parallel Binary Tree Topology (CLT) $\ . \ . \ .$ | 25 |

|    |      | 3.5.4.  | Theoretical Complexity of PBTs                                     | 26 |

|    | 3.6. | Leadin  | ng-zero Counting Topology (LCT)                                    | 27 |

|    |      | 3.6.1.  | Theoretical Complexity of LCT                                      | 28 |

|    | 3.7. | Multi-  | Level Topology (MLT)                                               | 29 |

|    |      | 3.7.1.  | Theoretical Complexity of MLT                                      | 30 |

| 4. | PRC  | POSEI   | D MF CIRCUIT TOPOLOGIES                                            | 31 |

|    | 4.1. | Array   | Based Topology (AbT)                                               | 31 |

|    |      | 4.1.1.  | Comparator Array Unit (CAU)                                        | 32 |

|    |      | 4.1.2.  | Address Generation Unit (AGU)                                      | 35 |

|    |      | 4.1.3.  | Data Selection Unit (DSU)                                          | 36 |

|    |      | 4.1.4.  | Theoretical Complexity of AbT                                      | 38 |

|    |      | 4.1.5.  | Other Useful Features of AbT                                       | 39 |

|    | 4.2. | Hybrid  | d Binary Tree Topology (HBT)                                       | 42 |

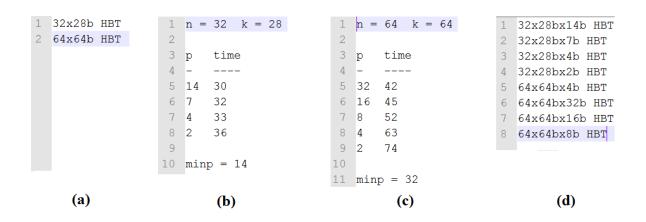

|    |      | 4.2.1.  | Theoretical Complexity of HBT                                      | 44 |

|    |      | 4.2.2.  | Delay Estimator for HBT                                            | 45 |

|    | 4.3. | Quad    | Tree Topology (QT)                                                 | 46 |

|    |      | 4.3.1.  | Theoretical Complexity of QT                                       | 48 |

| 5. | RTL  | GENE    | RATION AND SYNTHESIS METHODOLOGY                                   | 49 |

|    | 5.1. | Creati  | ng the Input File                                                  | 50 |

|    | 5.2. | Autom   | natic Generation of Verilog Files                                  | 50 |

|    | 5.3. | Pre-Sy  | vnthesis Verification                                              | 52 |

|    | 5.4. | Iterati | ve Synthesis                                                       | 52 |

|    |      | 5.4.1.  | Obtaining Timing Results                                           | 53 |

|    |      | 5.4.2.  | Obtaining Area Results                                             | 54 |

|    |      | 5.4.3.  | Obtaining Power Consumption Results                                | 54 |

|    | 5.5. | Post-S  | ynthesis Verification                                              | 54 |

|    | 5.6. | Extrac  | ction of Synthesis Results                                         | 55 |

| 6. | EXF  | PERIMI  | ENTAL WORK                                                         | 56 |

|    | 6.1. | Experi  | imental Setup                                                      | 56 |

| 6.2.   | Exper  | imental Results                           |

|--------|--------|-------------------------------------------|

|        | 6.2.1. | Timing Results                            |

|        | 6.2.2. | Delay Overhead of DSU                     |

|        | 6.2.3. | Evaluation of HBT Estimator               |

|        | 6.2.4. | Area Results                              |

|        | 6.2.5. | Area-Timing Product (ATP) Results         |

|        | 6.2.6. | Area-Timing-Square Product (AT2P) Results |

|        | 6.2.7. | Power Consumption Results                 |

|        | 6.2.8. | Power-Timing Product (PTP) Results        |

|        | 6.2.9. | Energy-Timing Product (ETP) Results       |

| 7. COI | NCLUS  | IONS AND FUTURE WORK                      |

| REFER  | ENCES  | 8                                         |

### LIST OF FIGURES

| Figure 3.1.  | Array Topology [1]                                                                                                                | 11 |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 3.2.  | Row Topology [2]                                                                                                                  | 13 |

| Figure 3.3.  | Selection Topology [3]                                                                                                            | 16 |

| Figure 3.4.  | Traditional Binary Tree Topology $(n = 8)$                                                                                        | 17 |

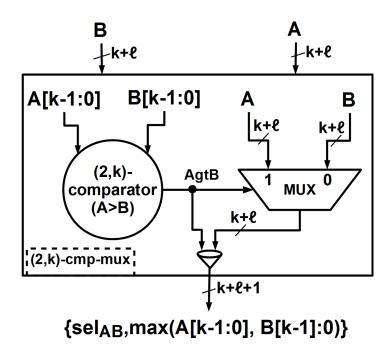

| Figure 3.5.  | Internal structure of a $(2,k)$ - <i>cmp-mux</i>                                                                                  | 18 |

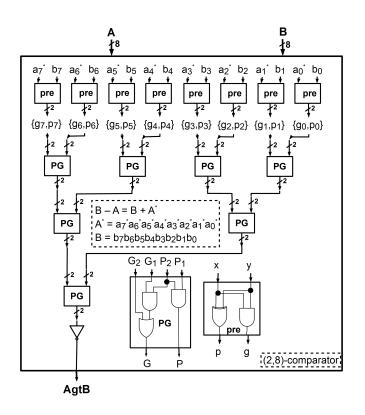

| Figure 3.6.  | Internal structure of a $(2,k)$ -comparator                                                                                       | 19 |

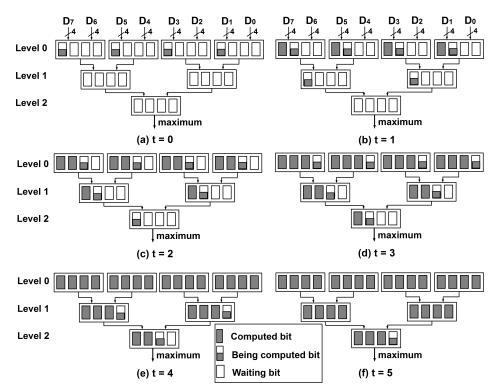

| Figure 3.7.  | An example $(8,4)$ - <i>PBT</i> circuit                                                                                           | 21 |

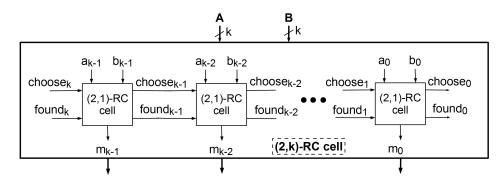

| Figure 3.8.  | A node $((2,k)-RC-cell)$ of Ripple Carry PBT [4]                                                                                  | 23 |

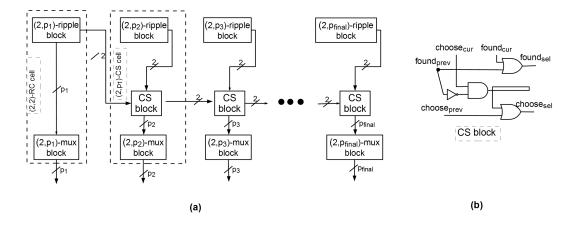

| Figure 3.9.  | (a) Linear configuration of a $(2,k)$ - $CS$ - $cell$ [4]. (b) Internal structure of the CS-block.                                | 24 |

| Figure 3.10. | Square-root configuration of a $(2,k)$ - $CS$ - $cell$ [4]                                                                        | 25 |

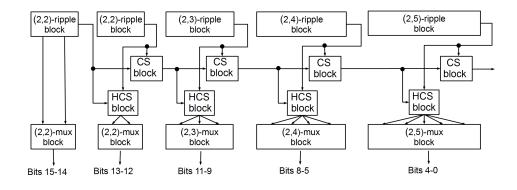

| Figure 3.11. | Four baseline PPN topologies for CLT: (a) Ladner-Fisher (LF). (b)<br>Kogge-Stone (KS). (c) Brent-Kung (BK). (d) Han-Carlson (HC). | 26 |

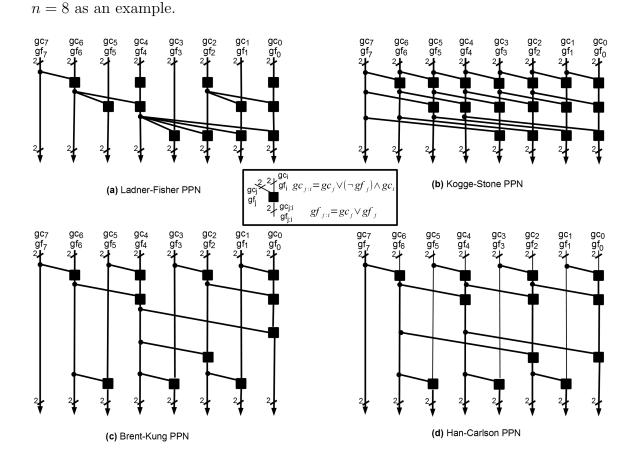

| Figure 3.12. | Leading-zero Counting Topology [5] $(n = 8)$                                                                                      | 28 |

| Figure 3.13. | Multi-Level Topology [5] $(n = 8)$                                                                                                | 29 |

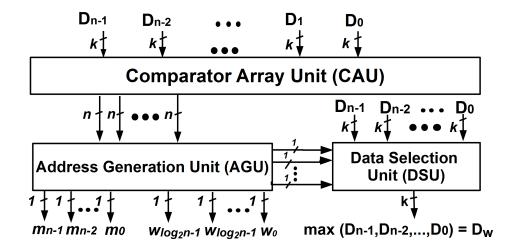

| Figure 4.1.  | High-level block diagram of AbT                                                                                                   | 31 |

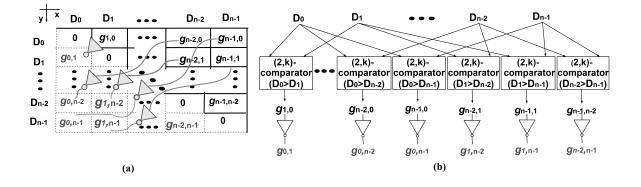

| Figure 4.2.  | Block diagram of CAU: (a) Conceptual array view. (b) Intercon-<br>nection of CAU blocks.                                                                                                              | 35 |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 4.3.  | (a) Interconnection of CAU and AGU. (b) Block diagram of AGU.                                                                                                                                         | 36 |

| Figure 4.4.  | An example for AbT without DSU $(n = 4, k = 5)$                                                                                                                                                       | 37 |

| Figure 4.5.  | Data selection unit (DSU) with OR trees of AGU                                                                                                                                                        | 38 |

| Figure 4.6.  | An example AbT-based selection circuit.                                                                                                                                                               | 40 |

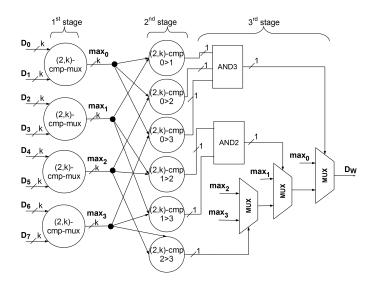

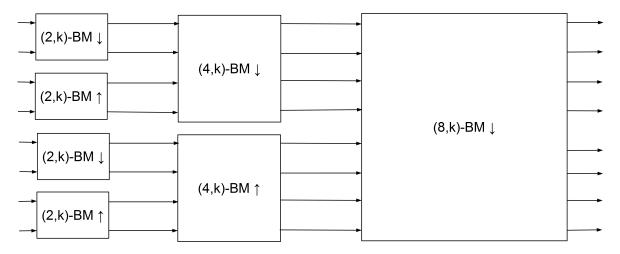

| Figure 4.7.  | An example $(8,4)$ - <i>HBT</i> circuit                                                                                                                                                               | 42 |

| Figure 4.8.  | Block diagram for an $(n,k)$ -HBT consisting of cascaded $(n,p)$ -TBTs.                                                                                                                               | 43 |

| Figure 4.9.  | Internal structure for a $(2,p)$ - <i>cmp-mux</i> of HBT                                                                                                                                              | 44 |

| Figure 4.10. | <ul><li>(a) Input file of the estimator (job-list). (b) Output for the first line of the job-list. (c) Output for the second line of the job-list.</li><li>(d) Result file of the estimator</li></ul> | 47 |

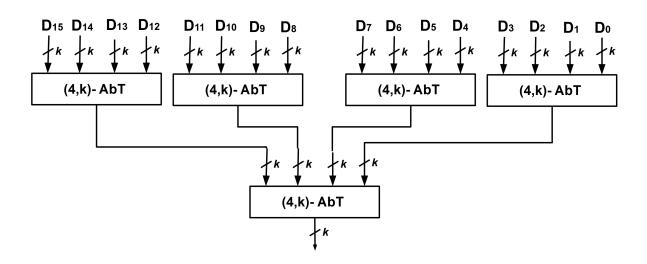

| Figure 4.11. | Block diagram of QT $(n = 16)$                                                                                                                                                                        | 47 |

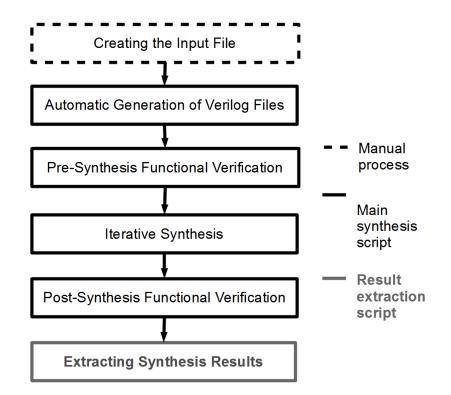

| Figure 5.1.  | Flow diagram of the automated synthesis methodology                                                                                                                                                   | 50 |

| Figure 5.2.  | (a) Structure defined by the testbench file. (b) Structure defined by the wrapper file                                                                                                                | 51 |

| Figure 7.1.  | Computing multiple order statistics with AbT                                                                                                                                                          | 82 |

| Figure 7.2.  | A $(8,k)$ -bitonic sorter circuit                                                                                                                                                                     | 83 |

## LIST OF TABLES

| Table 2.1.  | Frequently used orders of functions and their aliases                                                                                       | 9  |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------|----|

| Table 3.1.  | Theoretical complexity expressions of PBTs                                                                                                  | 27 |

| Table 4.1.  | Implementation options for CAU.                                                                                                             | 41 |

| Table 6.1.  | Theoretical comparison of all MF topologies                                                                                                 | 58 |

| Table 6.2.  | Comparison of two AbT variants in terms of timing (in nanoseconds): $AbT_1$ (value + one-hot address) and $AbT_2$ (value + binary address). | 60 |

| Table 6.3.  | Timing results for the proposed and competitor topologies in nanosec-<br>onds.                                                              | 62 |

| Table 6.4.  | Timing results for the five variants of CLT in nanoseconds. $\ . \ . \ .$                                                                   | 64 |

| Table 6.5.  | Delay overhead of DSU                                                                                                                       | 65 |

| Table 6.6.  | Timing results of different HBT implementations                                                                                             | 66 |

| Table 6.7.  | Normalized area results                                                                                                                     | 68 |

| Table 6.8.  | Normalized ATP results                                                                                                                      | 70 |

| Table 6.9.  | Normalized AT2P results                                                                                                                     | 72 |

| Table 6.10. | Normalized power consumption results.                                                                                                       | 74 |

| Table 6.11. | Normalized PTP results. | • | • | • | • | • | • | • | • | • | • | • | • | • | • |  | • | • | • | 76 |

|-------------|-------------------------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|--|---|---|---|----|

|             |                         |   |   |   |   |   |   |   |   |   |   |   |   |   |   |  |   |   |   |    |

| Table 6.12. | Normalized ETP results. |   |   |   |   |   |   |   |   |   |   |   |   |   |   |  |   |   |   | 78 |

## LIST OF SYMBOLS

| A             | Area                                                 |

|---------------|------------------------------------------------------|

| D             | Set of $n$ $k$ -bit numbers                          |

| $D_i$         | $i$ -th element of $\mathbf{D}$                      |

| $d_{n-1:0,j}$ | bit-slice $j$ of the $n$ input elements              |

| $D_W$         | Maximum (Winner) element of $\mathbf{D}$             |

| f             | Frequency                                            |

| k             | Bitwidth of an input element                         |

| n             | Number of input elements                             |

| 0             | Asymptotic O-notation                                |

| Р             | Power Consumption                                    |

| t             | Time                                                 |

| $V_{DD}$      | Supply voltage                                       |

| W             | The address (index) of the maximum element           |

|               |                                                      |

| $\alpha$      | Switching activity (Node transition activity factor) |

# LIST OF ACRONYMS/ABBREVIATIONS

| AbT           | Array based Topology                          |

|---------------|-----------------------------------------------|

| AGU           | Address Generation Unit                       |

| AT            | Array Topology                                |

| AT2P          | Area-Timing-Square Product                    |

| ATP           | Area-Timing Product                           |

| ВКТ           | Brent-Kung Topology                           |

| BM            | Binary Merger                                 |

| CAU           | Comparator Array Unit                         |

| CET           | Carry-lookahead Equation Topology             |

| CLT           | Carry Lookahead parallel binary tree Topology |

| CST           | Carry Select parallel binary tree Topology    |

| DSU           | Data Selection Unit                           |

| $\mathbf{FF}$ | Flip-Flop                                     |

| FPGA          | Field Programmable Gate Array                 |

| HBT           | Hybrid Binary tree Topology                   |

| НСТ           | Han-Carlson Topology                          |

| HDL           | Hardware Description Language                 |

| KST           | Kogge-Stone Topology                          |

| LCT           | Leading-zero Counting Topology                |

| m LFT         | Ladner-Fischer Topology                       |

| LSB           | Least Significant Bit                         |

| MF            | Maximum Finder                                |

| MLT           | Multi-Level Topology                          |

| MSB           | Most Significant Bit                          |

| PBT           | Parallel Binary tree Topology                 |

| PPN           | Parallel Prefix Network                       |

| PT2P          | Power-Timing-Square Product                   |

| PTP           | Power-Timing Product                          |

| QT            | Quad tree Topology                            |

|               |                                               |

| RCT | Ripple Carry parallel binary tree Topology |

|-----|--------------------------------------------|

| RT  | Row Topology                               |

| RTL | Register-Transfer Level                    |

| ST  | Selection Topology                         |

| TBT | Traditional Binary tree Topology           |

| WLM | Wire-Load Model                            |

#### 1. INTRODUCTION

This chapter introduces the motivation behind this thesis and familiarizes the readers with the subject. Summary of contributions and outline of the thesis also appear in this chapter.

#### 1.1. Motivation

Fast (low-latency) maximum (or similarly minimum) finder (MF) circuits, which determine the maximum (or minimum) number in an unsorted (arbitrary) list of unsigned binary numbers and/or its address (position) in the list, play an important role in a wide range of application areas such as communication systems [6], video processing [7], computer networks [8], real-time systems [9], and sorting networks [10]. Since any minimum finder circuit can be easily converted into a maximum finder circuit with minor modifications (such as swapping operands in comparisons), and vice versa, we include minimum as well as maximum finder circuits in the set of possible applications. In other words, any MF topology is both a maximum and minimum finder topology.

Depending on the application, MF circuits are required to produce the value and/or address of the maximum element. For instance, the motion estimation hardware proposed in [7] requires only the value of the maximum element. On the other hand, the schedulers in [8] need only address of the maximum. Other examples are the realtime task managers in [9], and the channel estimation architecture in [6], which require both the value and address of the maximum. Hence, fast computation of both the value and address of the maximum element become equally important.

Moreover, the number of elements (n) to be compared and bit-width (k) of each element are also dependent upon the application. For the circuits in [6–10], n and k are in the range of 8 to 64. However, we cannot constrain the range and combinations of parameters (n,k) with only these values, since finding the maximum is a fundamental problem, and thus, it can be used in numerous applications.

#### 1.2. Contributions of the Thesis

In this thesis, we analyze existing MF circuit topologies and then propose three new fast MF circuit topologies, which can determine both the value and the address of the maximum element within an *n*-element set of *k*-bit binary numbers. The address may be one-hot (*n* bits) and/or binary ( $\log_2 n$  bits).

Additionally, to evaluate the performance of existing and proposed topologies, we wrote Perl scripts for HDL code generation of all topologies. Our scripts also generate self-checking testbench code for functional verification besides RTL code (which will be synthesized). In addition, we also wrote synthesis (batch) scripts for a standard-cell based iterative flow that finds the optimum timing through binary search [11–13]. In other words, we automated not only design and functional verification but also synthesis of both existing and proposed MF circuits.

Our contributions can be summarized as follows:

- We provide a detailed literature survey of existing MF topologies, including Array Topology (AT) [1], Row Topolgy (RT) [2], Selection Topology (ST) [3], Traditional Binary tree Topology (TBT), Parallel Binary tree Topology (PBT) [4,14], Multi-Level Topology (MLT) [5], and Leading-zero Counting Topology (LCT) [5].

- While implementing Carry Lookahead PBT (CLT), we employed four pioneering *Parallel Prefix Network (PPN)* topologies such that Brent-Kung (BK) [15], Han-Carlson (HC) [16], Kogge-Stone (KS) [17], and Ladner-Fischer (LF) [18]. In addition, we implemented another version of CLT, in which we directly wrote the carry lookahead equations in Verilog.

- We propose three MF circuit topologies, namely, Array based Topology (AbT), Hybrid Binary tree Topology (HBT), and Quad tree Topology (QT).

- We provide a comparison of existing and proposed topologies in terms of theoretical time, area and power consumption costs.

- The contribution of AbT is providing the fastest MF topology of which timing complexity is  $O(\log_2 n + \log_2 k)$ . On the contrary, state-of-the-art has a timing

complexity of  $O(\log_2 n \log_2 k)$ .

- QT is an hybrid topology, which combines the speed advantage of AbT and area advantage of quad tree configuration. Its timing complexity (O(log<sub>4</sub> n log<sub>2</sub> k)) is better than any existing topology as well as its area complexity (O(log<sub>2</sub> n log<sub>2</sub> k)) is same as area complexity of the most area-efficient existing topology.

- HBT is another hybrid topology, which provides a generalization for PBT by thinking of an (n,k)-HBT as a combination of  $\lceil k/p \rceil$  cascaded (n,p)-TBTs. The timing complexity of HBT  $(O((k/p + \log_2 n) \log_2 p))$  depends on the value of the partition (p) parameter, while its area complexity is  $(O(\log_2 n \log_2 k))$  is same as area complexity of the most area-efficient existing topology.

- We wrote an estimator script in Perl to find the optimum partition (p) value of HBT that leads to the maximum clock frequency for a given (n,k) combination.

- We developed HDL code generators (in Perl) for almost all of the MF topologies mentioned above. Due to their high theoretical time complexities, we did not write generators for AT, RT, and ST. The code generators produces a Verilog RTL to be synthesized, an automatic testbench for pre- and post-synthesis functional verification, and a wrapper for proper timing computation after synthesis.

- We obtained a rich set of timing, power consumption and area results using an automated standard-cell based logic synthesis flow. The flow includes wire-load models and uses an iterative synthesis strategy [11–13].

- We also provide a comparison of proposed topologies and their competitors (existing topologies) in terms of empirical time, power consumption, and area results.

#### 1.3. Outline of the Thesis

Rest of the report is organized as follows. In Chapter 2, we introduce the basic concepts and notations used in this thesis. Chapter 3 gives an overview of the related work. Chapter 4 presents the details of the proposed topologies. In Chapter 5, we explain our synthesis methodology and RTL code generators. Chapter 6 provides experimental results for the proposed topologies and their competitors. And Chapter 7 gives the conclusions and future work.

#### 2. PRELIMINARIES

Since finding the maximum (or similarly minimum) element of a set of binary numbers and/or its address is a fundamental arithmetic operation, it can take part in numerous applications in different formats. Therefore, we first give a formal definition of the problem, and we introduce the notations as well as definitions we use in the thesis (Section 2.1). Next, we give circuit complexity and performance models, which are used for theoretical comparison of MF circuit topologies (Section 2.2).

#### 2.1. Problem Definition

The problem of finding the maximum of n k-bit unsigned binary numbers is formally defined as follows:

Given a set  $\mathbf{D} = \{D_0, D_1, \dots, D_{n-1}\}$  of *n* unsigned binary numbers, an MF circuit produces output(s)  $D_W$  and/or *W*, where  $D_W$  denotes the maximum (winner) element of  $\mathbf{D}$  ( $D_W \ge D_i, \forall D_i \in \mathbf{D}$ ) and *W* denotes its address (position).

We use the following notations throughout this thesis report:

- We will use (n,k)-name notation to denote a circuit/topology, which is called name and has n k-bit inputs.

- We will represent the binary version of the address as W = (w<sub>⌈log<sub>2</sub> n<sub>⌉</sub>−1w<sub>⌈log<sub>2</sub> n<sub>⌉</sub>−2

... w<sub>0</sub>).

</sub></sub>

- We will represent the one-hot version of the address as  $W = (m_{n-1}m_{n-2}...m_0)$ .

- We will represent each element  $D_i$  as a k-bit unsigned number such that  $D_i = (d_{i,k-1}d_{i,k-2} \dots d_{i,1}d_{i,0}).$

- We will also use d<sub>n-1:0,j</sub> notation to denote bit-slice (i.e., collection) j (d<sub>n-1,j</sub>d<sub>n-2,j</sub>

... d<sub>0,j</sub>) of n elements.

Note also that the maximum element does not necessarily have to be unique. In

the case of multiple maximum elements, MF circuits choose one of those maximum elements as the winner element applying a priority scheme. Hence, we assumed as if the maximum element was unique in our definition and the assumption will continue to be valid throughout this report.

In this thesis, we will examine several MF circuits and topologies. The topology of an MF circuit specifies how basic building blocks of the circuit are connected to each other (independent of n and k parameters). Topology does not deal with the exact internal implementation of building blocks; it deals with how the building blocks are interconnected. In other words, changing the implementation of some or all instances of a building block does not cause any topological change. On the other hand, we will use the term *circuit* to denote any specific hardware implementation of a topology.

#### 2.2. Circuit Complexity and Performance Modeling

We use simple complexity and performance models for a rough characterization of gate-level MF circuits. Given a circuit, specified by a logic equation or a netlist built from basic logic gates, we need estimations of the expected area, time (speed), and power consumption for a synthesized circuit as a function of the parameters n and k.

#### 2.2.1. Area Modeling

The silicon real estate a VLSI circuit occupies is the sum of its logic cells as well as their interconnections. Total *logic cell area* can be estimated from logic equations and gate-level netlists. In addition, wiring area is proportional to total wire length, which can be estimated from the sum of cell fanout. Since total cell fanout is also proportional to total circuit size, we can claim that total *wiring area* is also proportional to the number of transistors [19].

Taking into account the above criteria, we use *unit-gate area model* [20] in this thesis to estimate the area of a circuit from logical equations and netlists consisting of

simple logic gates. Unit-gate area model can be summarized as follows:

- A unit-gate is an elementary 2-input gate, such as AND, NAND, OR, and NOR, except XOR gate.

- An XOR gate is counted as two unit gates.

- Areas of inverters and buffers are ignored.

- Area of an elementary *m*-input gate is m-1 because the *m*-input gate is thought of as a binary tree configuration of m-1 2-input simple gates.

#### 2.2.2. Delay Modeling

Delay of a VLSI circuit is determined by logic cells and wires on the critical path of the circuit, which can be defined as the path between an input and an output with the maximum delay. Critical path evaluation is done by "static timing analysis", which is a method of computing expected timing of digital circuits utilizing graph algorithms. Although timing is also dependent on temperature, voltage, and process variations, we assume they affect all circuits equally.

The total critical path delay is the sum of logic cell delays, output transition delays, and wire delays on the respective path. Logic cell delay is determined by transistor-level implementation and complexity of the cell. Output transition delay is the time it takes for a logic cell output to charge/discharge capacitances, which consists of interconnect and cell input loads and are proportional to the fanout of the cell. The wire delay is the RC-delay of interconnects [19].

Considering the above factors, we use *unit-gate delay model*, similar to the unitgate area model in this thesis to estimate the delay of a circuit from logical equations and netlists consisting of simple logic gates. Unit-gate delay model can be summarized as follows:

• A unit-gate is an elementary 2-input gate, such as AND, NAND, OR, and NOR, except XOR gate.

- An XOR gate is counted as two unit gates.

- Delays of inverters and buffers are ignored.

- Delay of an elementary *m*-input gate is  $\lceil \log_2 m \rceil$  because the *m*-input gate is thought of as a binary tree configuration of m 1 2-input simple gates.

#### 2.2.3. Power Consumption Modeling

The power dissipation of a CMOS circuit is dominated by the dynamic dissipation resulting from charging and discharging capacitances. If we ignore the dynamic shortcircuit currents and static leakage power, the total power consumption can be written as:

$$P_{total} = \sum_{i} C_{total} \, V_{DD}^2 \, f_{clk} \, \alpha$$

Here,  $C_{total}$  is the total load capacitance at node *i*,  $V_{DD}$  is the supply voltage,  $f_{clk}$  is the clock frequency, and  $\alpha$  is the power consuming switching activity (or node transition activity factor) at node *i*. Switching activity of a node can be defined as the probability that a clock event results in a power consuming transition at this node. Total capacitance is roughly proportional to the circuit size. Supply voltage and clock frequency can be considered as constant throughout the circuit and therefore is not relevant in circuit comparisons. Switching activity is a function of nature and statistics of input signals as well as overall circuit topology and function to be implemented.

Hence, if we assume supply voltage, clock frequency, and input switching activity values are the same for all circuits, power consumption of the circuit becomes approximately proportional to circuit size. Therefore, *unit-gate area* model can be used for estimation of power consumption of a circuit.

#### 2.2.4. Combined Circuit Performance Measures

Depending on the requirements of the design, circuit performance can be measured in terms of either area, time, power consumption, or combination of those. Some of the most common combined performance measures are area-timing product (ATP), power-timing product (PTP), area-timing-square product (AT2P), and area-square-timing product (A2TP). ATP roughly indicates the circuit size per data items processed per time unit. AT2P tries to stress time objective than area while A2TP stresses area objective more than time. PTP can be regarded as the power dissipation per computation. The common property of all those combined performance metrics is that the smaller the used combined metric is, the higher the performance of the corresponding circuit is. Also, we can use aforementioned unit-gate models to calculate these combined performance metrics.

#### 2.2.5. Asymptotic O-notation

Using the circuit complexity and performance models given in Sections 2.2.1 up to 2.2.4, we obtain a *complexity function*, mathematical function of input parameters, for the circuit. For MF circuits examined in this thesis, input parameters are the count of the numbers to be compared (n) and the bitwidth of each number (k). Hence, we obtain complexity functions such that  $g_{complexity} = g(n, k)$ .

In comparing the complexities of different circuits, not all terms of a circuit's complexity function is essential. Instead, only the *rate of growth* or the *order of magnitude* of the complexity function is typically of the most concern [21]. Asymptotic *notations* are symbols used in computational complexity theory [22] to express the efficiency of algorithms with a focus on their orders of growth. In this thesis, we use one of the most widely-used asymptotic notations to compare efficiency of our circuits' complexity functions: *O*-notation.

*O*-notation denotes the asymptotic upper bounds of the complexity functions. Given to functions g(n) and h(n) that map a natural number n to some positive value, it is said that g(n) = O(h(n)) (pronounced as "g(n) is big-oh of h(n)" or as "g(n) is of order at most h(n)) if two constants c and  $n_0$  exist such that the following proposition is true:

$$\forall n \ge n_0 : g(n) \le c g(n)$$

Note also that O(h(n)) denotes a set of functions and the equality sign in g(n) = O(h(n)) denotes the set membership, namely  $g(n) \in O(h(n))$ . The following are legal expressions in computational theory:

$$\frac{1}{3}n^2 = O(n^2)$$

$$n^3 + 1000n^2 + n = O(n^3)$$

$$4n\log n + n = O(n\log n)$$

$$2n^3 = O\left(\frac{1}{7}n^3\right)$$

$$2n^3 = O\left(n^3 + n^2\right)$$

Although the last three expressions are valid, we do not prefer them while describing complexities of our circuits. We choose the asymptotic notation to be as simple and as informative as possible. Table 2.1 lists some of the most common *O*-notations and their aliases in ascending complexity order.

| <b>O</b> -notation | Alias                                    |

|--------------------|------------------------------------------|

| O(1)               | Constant complexity                      |

| $O(\log n)$        | Logarithmic complexity                   |

| $O(n\log n)$       | linearithmic, loglinear, or quasi linear |

| $O(n^2)$           | Quadratic complexity                     |

| $O(n^3)$           | Cubic complexity                         |

| $O(n^c), c > 1$    | Polynomial complexity                    |

| $O(c^n), c > 1$    | Exponential complexity                   |

| O(n!)              | Factorial complexity                     |

Table 2.1. Frequently used orders of functions and their aliases.

#### 3. PREVIOUS WORK

In this chapter we shall examine the existing MF circuit topologies: Array Topology (AT) [1], Row Topolgy (RT) [2], Selection Topology (ST) [3], Traditional Binary tree Topology (TBT), Parallel Binary tree Topology (PBT) [4,14], Multi-Level Topology (MLT) [5], and Leading-zero Counting Topology (LCT) [5].

#### 3.1. Array Topology (AT)

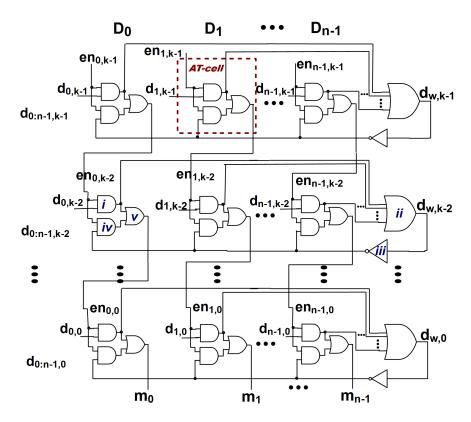

AT [1] is best described as a filter. It starts with all elements being candidates for the maximum, looks at each bit from most significant bit (MSB) to least significant bit (LSB), and narrows down the candidates in each iteration until only one is left. An (n,k)-AT circuit is organized as a k-by-n array of AT-cells as shown in Figure 3.1. Row r of the array consists of n AT-cells that form bit-slice r of n elements. Each column c of the array consists of k AT-cells corresponding to  $D_c$ . AT first initializes the enable signals  $(en_{0:n-1,k-1})$  of the AT-cells residing in (k - 1)-th row of AT, and then applies the following steps for each bit-slice (row) r (r = k - 1 DOWNTO 0) of AT, as shown in the second row of Figure 3.1:

- (i) Each cell c in the bit-slice performs an AND operation on its input  $d_{c,r}$  and its corresponding enable signal  $(en_{c,r})$  using a 2-input AND gate (labelled with i in Figure 3.1).

- (ii) An *n*-input OR gate (labeled with *ii* in Figure 3.1) computes the  $d_{W,r}$  (*r*-th bit of the winner element  $D_W$ ) using the 1-bit signals produced in Step (*i*).

- (iii) Computed  $d_{W,r}$  is inverted by an inverter (labeled with *iii* in Figure 3.1).

- (iv) Each cell c in the bit-slice performs an AND operation on its input en<sub>c,r</sub> with the inverted signal in Step (*iii*) using a 2-input AND gate (labeled with *iv* in Figure 3.1).

- (v) Each cell c in the bit-slice computes the enable signal  $en_{c,r-1}$  of the corresponding AT-cell in the next bit-slice r-1 with an 2-input OR gate(labeled with v in Figure 3.1).

As it can be seen, the two 2-input AND gates (i and iv in Figure 3.1) filters out the elements, whose enable signal is zero. If the enable signal of an element is 1, the 2-input AND gate (iv in Figure 3.1) checks whether the corresponding bit of the element is the same as the corresponding bit of the winner element, which is computed by the n-input OR gate (ii in Figure 3.1). If these two bits are equal, the enable signal of the corresponding element becomes 1 for the next row and becomes zero otherwise. In AT,

Figure 3.1. Array Topology [1].

enable (en) signals ripple down from MSB to LSB. Thus,  $d_{W,j}$  cannot be determined until the  $en_{n-1:0,j+1}$  signals settle down.

As it can be seen in Figure 3.1, AT produces the value and one-hot address of the maximum (winner) element.

#### 3.1.1. Theoretical Complexity of AT

An AT-cell consists of two 2-input AND gates and one 2-input OR gate, and thus, we can write the following complexity expressions for an AT-cell, using the complexity models discussed in Section 2.2:

$$t_{AT-cell} = t_{AND2} + t_{OR2} = 1 + 1 = 2 \tag{3.1}$$

$$A_{AT-cell} = 2 \times A_{AND2} + A_{OR2} = 2 \times 1 + 1 = 3$$

(3.2)

$$P_{AT-cell} = A_{AT-cell} = 3 \tag{3.3}$$

Complexity functions of each *n*-input OR gate that resides in the rows of AT:

$$t_{ORn} = \log_2 n \times t_{OR2} = \log_2 n \tag{3.4}$$

$$A_{ORn} = (n-1) \times A_{OR2} = n-1 \tag{3.5}$$

$$P_{ORn} = A_{ORn} = n - 1 \tag{3.6}$$

The total complexity of AT:

$$t_{AT} = k \times (1 + t_{ORn} + t_{AT-cell}) = k \times (1 + \log_2 n + 2)$$

$$= k \times (\log_2 n + 3)$$

$$= O(k \times \log_2 n + k)$$

$$A_{AT} = k \times n \times A_{AT-cell} + k \times A_{ORn}$$

$$= k \times n \times 3 + k \times (n - 1) = 4 \times k \times n - k$$

$$= O(k \times n)$$

(3.8)

$$P_{AT} = A_{AT} = 4 \times k \times n - k = O(k \times n)$$

(3.9)

#### 3.2. Row Topology (RT)

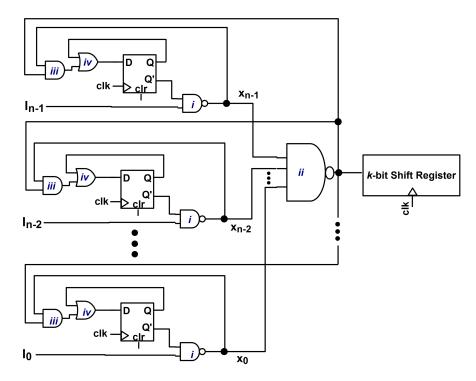

RT [2] determines the maximum of n elements in k cycles, where k is the width of each element. RT can be thought of as a row of AT with additional storage elements within *RT-cells* as seen in Figure 3.2. RT also uses a shift register to store the value

Figure 3.2. Row Topology [2].

of the maximum element. RT computes one bit of the maximum value in each cycle, from MSB to LSB. After k cycles, the maximum value becomes available in the shift register. One-hot address of the maximum element is also available in cycle k. RT first clears all the flip-flops with a *start pulse* and then applies the following steps for each clock cycle c (c = k - 1 DOWNTO 0), as shown in Figure 3.2:

- (i) The bit-slice  $d_{n-1:0,c}$  is made available at the input ports  $I_{n-1:0}$  respectively.

- (ii)  $x_{n-1:0}$  signals are concurrently computed using 2-input NAND gates (labeled with i in Figure 3.2).

- (iii) An *n*-input NAND gate (labeled with *ii* in Figure 3.2) computes the  $d_{W,c}$  (*c*-th most significant bit of the winner element  $D_W$ ) using  $x_{n-1:0}$  signals produced in

Step (i).

- (iv) When an input x of the n-input NAND gate equals to the  $d_{W,c}$  computed in Step (*iii*), the corresponding D flip-flop changes its state (Q signal in Figure 3.2) in the next clock cycle c 1. This operation is concurrently carried out by 2-input AND gates (labeled with *iii* in Figure 3.2) and 2-input OR gates (labeled with *iv* in Figure 3.2).

- (v) Finally, computed  $d_{W,c}$  value is moved into the shift register with the next clock pulse.

Note also that  $x_{n-1:0}$  signals at the final cycle give the one-hot address of the maximum element. In addition, RT is not our competitor as it computes the maximum element in multiple clock cycles.

#### 3.2.1. Theoretical Complexity of RT

An RT-cell consists of a 2-input AND gate, a 2-input OR gate, a 2-input NAND gate, and a D flip-flop. Hence, we can write the following complexity expressions for an RT-cell, using the complexity models discussed in Section 2.2:

$$t_{RT-cell} = t_{NAND2} + t_{AND2} + t_{OR2} = 1 + 1 + 1 = 3$$

(3.10)

$$A_{RT-cell} = A_{NAND2} + A_{AND2} + A_{OR2} + A_{DFF} = 1 + 1 + 1 + 4 = 7$$

(3.11)

$$P_{RT-cell} = A_{RT-cell} = 7 \tag{3.12}$$

In above calculations, we ignore clock-to-q delay and setup time of the D flip-flop. Also, we take the area of the flip-flop as 4 unit gates as indicated in [2].

Complexity expressions for the *n*-input NAND gate:

$$t_{NANDn} = \log_2 n \times t_{NAND2} = \log_2 n \tag{3.13}$$

$$A_{NANDn} = (n-1) \times A_{NAND2} = n-1$$

(3.14)

$$P_{NANDn} = A_{NAND2} = n - 1 (3.15)$$

The total complexity of RT:

$$t_{RT} = k \times (t_{NANDn} + t_{RT-cell}) = k \times (\log_2 n + 3)$$

$$= O(k \times \log_2 n + k)$$

(3.16)

$$A_{RT} = n \times A_{RT-cell} + A_{NANDn} + AShiftReg$$

$$= n \times 7 + (n - 1) + (4 \times k) = 8 \times n + 4 \times k - 1$$

$$= O(n + k)$$

(3.17)

$$P_{RT} = A_{RT} = O(n + k)$$

(3.18)

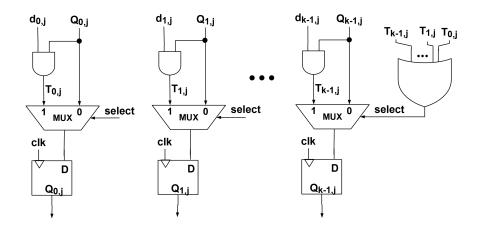

#### 3.3. Selection Topology (ST)

In [3], finding the maximum is thought of as a subset of selection operation, which refers to finding an element of given order from an ordered set of elements. And an MF circuit topology, which we call Selection Topology (ST), was proposed. ST computes the position(s) of the maximum element(s) of a set of n k-bit numbers in k cycles, and outputs the result as an n-bit signal. In Figure 3.3, ST with the signals at the *j*-th cycle is given. Similar to AT and RT, it successively operates on bits of all numbers. Initially, each element is a candidate for the maximum element. Hence, flip-flops of Figure 3.3 are initially set to 1. In each cycle *j*, ST observes the *j*-th bit-slice  $d_{n:0,j}$  of the input elements and decides if a particular element should remain as a candidate, or if it should be permanently rejected. Thus, we obtain a subset of the initial set that does not include the rejected elements, after each cycle *j*. After *k* cycles, we obtain the set of the maximum element(s) and outputs of the flip-flops show the positions of the maximum element(s). In order to select the maximum value we need an additional priority encoder followed by a multiplexer circuit. In addition, ST is not our competitor as it computes the maximum element in multiple clock cycles.

Figure 3.3. Selection Topology [3].

#### 3.3.1. Theoretical Complexity of ST

Total complexity of ST:

$$t_{ST} = k \times (t_{AND2} + t_{ORn} + t_{mux2}) = k \times (1 + \log_2 n + 2)$$

=  $k \times (\log_2 n + 3) = O(k \times \log_2 n + k)$  (3.19)

$$A_{ST} = n \times (A_{AND2} + A_{mux2} + A_{DFF}) + A_{ORn}$$

=  $n \times 7 + (n - 1) = 8 \times n - 1$

=  $O(n)$  (3.20)

$$P_{ST} = A_{ST} = O(n)$$

(3.21)

#### 3.4. Traditional Binary Tree Topology (TBT)

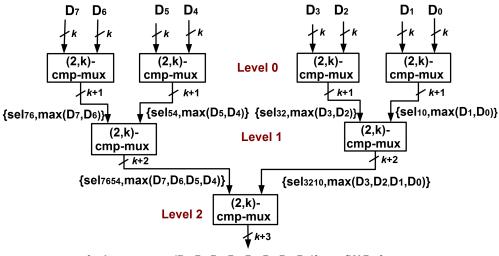

The most widely used MF circuit topology in the literature is traditional binary tree topology (TBT), in which (2,k)-*cmp-mux* blocks are connected in a binary tree configuration. In Figure 3.4, an (8,k)-*TBT* is given as an example.

A (2,k)-cmp-mux in  $\ell$ -th level of the binary tree, given in Figure 3.5, has two  $(k + \ell)$ -bit inputs (A and B in Figure 3.5) and a  $(k + \ell + 1)$ -bit output. The most

{sel76543210,max(D7,D6,D5,D4,D3,D2,D1,D0)} = {W,Dw}

Figure 3.4. Traditional Binary Tree Topology (n = 8).

significant  $\ell$  bits of an input signal represent the address of winner element determined by the preceding sub-tree rooted at this input port. And, the remaining k bits of an input signal is the value of the aforementioned winner element. For instance, in Figure 3.4,  $sel_{7654}$  is the address of the maximum of elements  $D_7$ ,  $D_6$ ,  $D_5$ , and  $D_4$ , while  $max(D_7, D_6, D_5, D_4)$  is the value of the maximum one. Each (2,k)-cmp-mux in  $\ell$ -th level of the binary tree consists of a (2,k)-comparator (cmp) (denoted as A > Bin Figure 3.5) to determine which one of its two inputs is greater, and a  $(k + \ell)$ -bit 2-to-1 multiplexer (mux) to select the greater input. The multiplexer uses the output of the comparator ( $sel_{AB}$  in Figure 3.5) to make the selection. Data inputs of the multiplexers in the  $\ell$ -th level of the tree are  $(k + \ell)$ -bit signals in order to transfer the binary addresses and the values of the maximum elements so far computed to the next level of the binary tree.

In TBT, efficient hardware implementation of (2,k)-comparators is crucial to reduce the latency. To determine the greater one of two k-bit binary numbers A and B, we only need to apply a subtraction operation, (A - B) or (B - A), and then to check only the final carry bit of the operation. Hence, we can utilize parallel prefix adders to implement delay- and area-efficient (2,k)-comparators, as in [23]. Parallel prefix adders concurrently compute generate  $(g_i)$  and propagate  $(p_i)$  signals as a preprocessing step,

Figure 3.5. Internal structure of a (2,k)-cmp-mux.

which takes O(1) time. Then, they compute group generate  $(G_{i;j})$  and group propagate  $(P_{i;j})$  signals between bit positions i and j using parallel prefix structures, which can compute the final carry in  $O(log_2k)$  time. Finally, they calculate the sum in O(1) time. Since we only need to compute the final carry bit, we do not need to compute the sum and to determine carry bit for each bit position. Thus, we only use preprocessing logic and a binary tree part of the parallel prefix structure, which produces the final carry in order to implement a (2,k)-comparator circuit. A (2,8)-comparator is shown in Figure 3.6 as an example and as a reference for theoretical complexity calculations in Section 3.4.1.

Figure 3.6. Internal structure of a (2,k)-comparator.

#### 3.4.1. Theoretical Complexity of TBT

Complexity expressions for (2,k)-comparator:

$$t_{comparator} = (\log_2 k) \times t_{PG} + t_{pre}$$

=  $(\log_2 k) \times (t_{OR2} + t_{AND2}) + t_{pre} = (\log_2 k) \times (1+1) + 2$

=  $2 \times \log_2 k + 2 = O((\log_2 k))$  (3.22)

$A_{comparator} = k \times A_{pre} + (k-1) \times A_{PG}$

$$= k \times (A_{XOR} + A_{AND2}) + (k - 1) \times (A_{OR2} + 2 \times A_{AND2})$$

$$= k \times (2 + 1) + (k - 1) \times (1 + 2 \times 1) = 6 \times k - 1 = O(k)$$

(3.23)

$$P_{comparator} = A_{comparator} = 6 \times k - 1 = O(k)$$

(3.24)

Complexity expressions for (2,k)-*cmp*-mux:

$$t_{cmp-mux} = t_{comparator} + t_{mux2}$$

=  $(2 \times \log_2 k + 2) + (t_{AND2} + t_{OR2}) = 2 \times \log_2 k + 4$

=  $O(\log_2 k)$  (3.25)

$$A_{cmp-mux} = A_{comparator} + k \times A_{mux2}$$

$$= (6 \times k - 1) + k \times (2 \times A_{AND2} + A_{OR2}) = 6 \times k - 1 + 3 \times k$$

$$= 9 \times k - 1 = O(k)$$

(3.26)

$$P_{cmp-mux} = A_{cmp-mux} = 9 \times k - 1 = O(k)$$

$$(3.27)$$

Complexity functions for (n,k)-TBT:

$$t_{TBT} = \log_2 n \times t_{cmp-mux} = \log_2 n \times (2 \times \log_2 k + 4)$$

$$= 2 \times \log_2 n \times \log_2 k + 4 \times \log_2 n = O(\log_2 n \times \log_2 k + \log_2 n)$$

(3.28)

$$A_{TBT} = (n-1) \times A_{cmp-mux} + A_{extra}$$

$$= (n-1) \times (9 \times k - 1) + (\log_2 n - 1) \times A_{mux2}$$

$$= (9 \times k \times n - n - 9 \times k + 1) + (\log_2 n - 1) \times 3$$

$$= O(k \times n)$$

(3.29)

$$P_{TBT} = A_{TBT} = O(k \times n)$$

(3.30)

The  $A_{extra}$  term of Equation 3.29 denotes the area overhead caused by the fact that we convey both the value and the address of the maximum element to the next level of TBT.

#### 3.5. Parallel Binary Tree Topologies (PBTs)

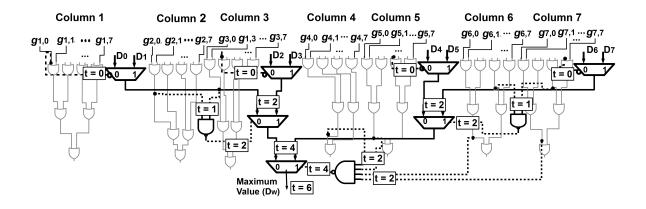

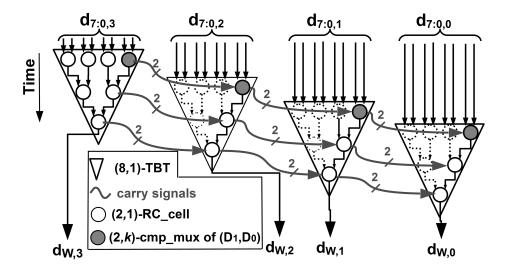

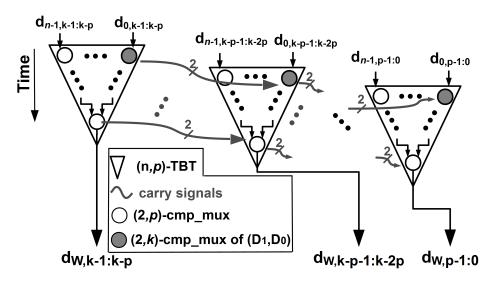

Since the (2,k)-comparators of TBT propagates signals from LSB to MSB, a node ((2,k)-cmp-mux) at the level  $(\ell + 1)$  of TBT cannot start comparison before its two descendant nodes at level  $\ell$  computes all k bits of their results. Authors of [4, 14] propose an MF topology, which we call *Parallel Binary Tree (PBT)*, to reduce the

overall propagation delay of TBT by using (2,k)-*cmp-mux* circuits that propagate the signals from MSB to LSB. Using this kind of (2,k)-*cmp-mux* circuits, more significant result bits of a (2,k)-*cmp-mux* circuit in the tree become available to its descendant (2,k)-*cmp-mux* circuit and the descendant can start comparison operation before the end of the comparison in the predecessor. In other words, each level of the binary tree concurrently operates on the different bit positions of its inputs. Hence, we call this topology as PBT to distinguish it from TBT. To illustrate the operation of PBT, a conceptual (8,4)-*PBT* example is given in Figure 3.7. In this conceptual PBT circuit, each node of the tree computes its result bit-by-bit from MSB to LSB. The sequence of the events and propagation of the results through (8,4)-*PBT* of Figure 3.7 can be summarized as follows:

Figure 3.7. An example (8,4)-PBT circuit.

- (t = 0). (2,4)-comparators at Level-0 start to compare MSBs (4th bits) of their corresponding inputs.

- (t = 1). The winners of MSB comparisons at Level-0 conveyed to corresponding

(2,4)-comparators at Level-1. At the same time, (2,4)-comparators at Level-0 start to compare 3rd bits of their inputs.

- (t = 2). (2,4)-comparators at Level-0 start to compare 2nd bits of their inputs and (2,4)-comparators at Level-1 start to compare 3rd bits of their inputs. Concurrently, (2,4)-comparators at Level-2 start to compare MSBs of their inputs.

- (t = 3). (2,4)-comparators at Level-0 start to compare LSBs (1st bits) of their inputs and (2,4)-comparators at Level-1 start to compare 2nd bits of their inputs.

Concurrently, (2,4)-comparators at Level-2 start to compare 3rd bits of their inputs.

- (t = 4). (2,4)-comparators at Level-0 complete their jobs. (2,4)-comparators at Level-1 start to compare 1st bits of their inputs. Concurrently, (2,4)-comparators at Level-2 start to compare 2nd bits of their inputs.

- (t = 5). (2,4)-comparators at Level-1 finish their jobs. Concurrently, (2,4)comparators at Level-2 start to compare 1st bits of their inputs. And all bits of

the result will be available at t = 6.

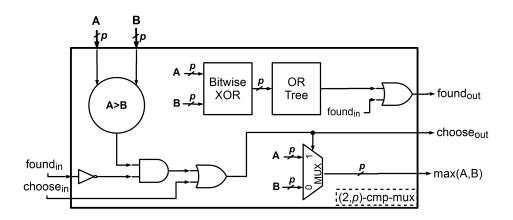

In [4, 14], three PBT variants are proposed, each of which utilizes a different well-known adder topology: Ripple Carry parallel binary tree Topology (RCT), Carry Lookahead parallel binary tree Topology (CLT), and Carry Select parallel binary tree Topology (CST). They define a 2-bit carry signal ({choose, found}) propagating from MSB to LSB. The found bit of the carry signal at bit-position *i* indicates if the winner is determined so far by comparators between MSB and the bit-position *i*. The choose bit of the carry signal at bit-position *i* indicates which one of the inputs is the winner. For instance, a (2,k)-cmp-mux of RCT consists of *k* cascaded (2,1)-RC-cells (a kind of (2,1)-cmp-mux). Each RC-cell at bit-position *i* computes the carry input of bitposition i - 1 and select signal for the multiplexer that selects bit *i* of the result. We shall examine each of the three variants in a separate subsection (in Sections 3.5.1 -3.5.3) to show more clearly the differences between them.

# 3.5.1. Ripple Carry Parallel Binary Tree Topology (RCT)

In RCT, each node of the tree is a (2,k)-RC-cell, which is functionally equivalent to a (2,k)-cmp-mux and consists of serially connected k (2,1)-RC-cells as shown in Figure 3.8. A (2,1)-RC-cell at the bit position i produces bit i of the winner element  $(m_i$  in Figure 3.8) as well as carry signal for the bit position i - 1. The (2,1)-RC-cell

Figure 3.8. A node ((2,k)-RC-cell) of Ripple Carry PBT [4].

at the bit position i computes its outputs using the following equations [4]:

$$choose_i = choose_{i+1} + \overline{found_{i+1}}.(a_i.\overline{b_i})$$

(3.31)

$$found_i = found_{i+1} + (a_i \oplus b_i) \tag{3.32}$$

$$m_i = \overline{choose_i} \cdot b_i + choose_i \cdot a_i \tag{3.33}$$

#### 3.5.2. Carry Select Parallel Binary Tree Topology (CST)

In a (2,k)-RC-cell, each (2,1)-RC-cell has to wait for an incoming carry signal to compute its result bit. To reduce this linear dependency, CST adapts the idea of carry select adders to the comparison operation, and uses (2,k)-CS-cells (see Figure 3.9) at the nodes of PBT. Internal structure of the (2,k)-CS-cell is similar to that of carry select adders. A (2,k)-CS-cell consists of cascaded  $(2,p_i)$ -CS-cells. A  $(2,p_i)$ -CS-cell consists of three blocks: A  $(2,p_i)$ -ripple-block,  $(2,p_i)$ -mux-block, and a  $(2,p_i)$ -CS-block. The ripple-block is the carry generator part of the RC-cell and the mux-block is a  $p_i$  bit 2-to-1 multiplexer. The CS-block takes carry signals from the previous CS-cell as well as from the current ripple-block, and then computes select signals of the current mux-block besides carry signals for the next CS-cell. At the beginning, each  $(2,p_i)$ -CScells starts to compute corresponding  $p_i$  bits of the winner as if higher order bits of the inputs were equal and then the CS-block selects the correct result when the true value of the incoming carry signal is determined.

Figure 3.9. (a) Linear configuration of a (2,k)-CS-cell [4]. (b) Internal structure of the CS-block.

In CST, a mismatch between the arrival time of the input carry signals and preparation time of the out carry signals: The closer a  $(2,p_i)$ -CS-cell to LSB is, the earlier it prepares the output carry signal and the later its input carry arrives. In order to get around the mismatch, a square-root configuration was designed in [4]. In the square-root configuration the  $p_i$  values are chosen as  $\{p_1 = \sqrt{2k}, p_2 = p_1 + 1, \ldots, p_{final} = p_{final-1} + 1\}$  to obtain a timing complexity of  $O(\sqrt{k})$ . We shall use this version in Chapter 6 while we are obtaining synthesis results. In Figure 3.10, the authors also introduces a new type of block, namely half carry-select block (HCS-block), which is a simplified version of CS-block. The purpose of HCS-block is reducing the fanout on the critical path of (2,k)-CS-cell. Further details can be found in [4].

Figure 3.10. Square-root configuration of a (2,k)-CS-cell [4].

# 3.5.3. Carry Look-ahead Parallel Binary Tree Topology (CLT)

CLT eliminates the ripple effect in RCT and CST using the following Boolean equations:

$$gc_i = a_i.\overline{b_i} \tag{3.34}$$

$$gf_i = a_i \oplus b_i \tag{3.35}$$

$$choose_i = \sum_{x=k-1}^{i} \left(\prod_{y=x+1}^{i+1} \overline{gf_y}\right) . gc_x \tag{3.36}$$

$$found_i = \sum_{x=k-1}^{i} gf_x \tag{3.37}$$

Using this equations, carry signals for each bit position can be computed as soon as the inputs A and B becomes available to the corresponding node of the PBT.

Although it was not mentioned in [4, 14], we can use parallel prefix networks (PPNs) to compute  $choose_i$  and  $found_i$  signals in Equations 3.36 and 3.37. Hence, we also implemented four different PPN variants of CLT, each of which uses a different PPN topology: *Brent-Kung PBT (BKT)* [15], *Kogge-Stone PBT (KST)* [17], *Han-Carlson PBT (HCT)* [16], and *Ladner-Fischer PBT (LFT)* [18]. Note that we shall name the MF topology, which directly implements the Equations 3.34 –3.37 in Verilog, as *Carry-lookahead Equations Topology (CET)*. In Figure 3.11, we show the PPNs for

Figure 3.11. Four baseline PPN topologies for CLT: (a) Ladner-Fisher (LF). (b) Kogge-Stone (KS). (c) Brent-Kung (BK). (d) Han-Carlson (HC).

# 3.5.4. Theoretical Complexity of PBTs

In Table 3.1, we give the theoretical complexities of seven different PBT variants: RCT, CST, CLT, LFT, BKT, KST, and HCT. As the detailed analysis of RCT, CST, and CLT can be found in [4], we do not give detailed complexity equations for them. Since area and power consumption are the same according to our complexity models explained in Section 2.2, we do not list the power consumption complexity functions in Table 3.1.

| Topology | Timing Complexity                                        | Area Complexity                 |

|----------|----------------------------------------------------------|---------------------------------|

| RCT      | $O(\log_2 n + k)$                                        | $O(n \times k)$                 |

| CST      | $O(\sqrt{k}) + O((\sqrt{k} - \log_2 n) \times \log_2 n)$ | $O(n \times k)$                 |

| CET      | $O(\log_2 n \times \log_2 k)$                            | $O(n \times k)$                 |

| LFT      | $O(\log_2 n \times \log_2 k)$                            | $O(n \times k \times \log_2 k)$ |

| BKT      | $O(\log_2 n \times \log_2 k)$                            | $O(n \times k)$                 |

| KST      | $O(\log_2 n \times \log_2 k)$                            | $O(n \times k \times \log_2 k)$ |

| НСТ      | $O(\log_2 n \times \log_2 k)$                            | $O(n \times k \times \log_2 k)$ |

Table 3.1. Theoretical complexity expressions of PBTs.

# 3.6. Leading-zero Counting Topology (LCT)

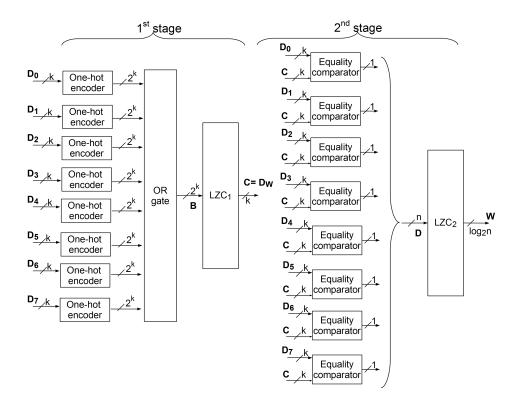

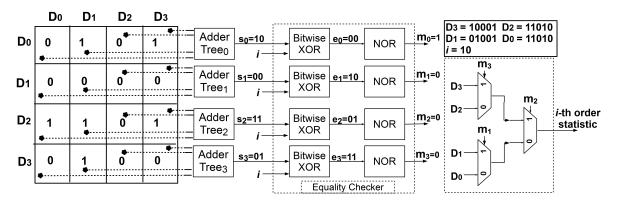

Leading-zero Counting Topology (LCT) [5] consists of two cascade stages. In the first stage, value of the winner (i.e. maximum) element is determined. And in the second stage, binary address of the winner is computed. In the first stage, each of the n elements is converted into a one-hot code and then a  $2^k$ -bit vector B is obtained by applying OR operation on the one-hot elements. Finally, the k-bit value of the winner element is computed using an a leading-zero counting (LZC) algorithm (a priority encoder). In the second stage, each element is first compared with the winner element to obtain n-bit vector D. Finally, the LZC is used to determine  $\log_2 n$ -bit address of the winner element from D. As a result, LCT outputs both value and binary address of the winner. In Figure 3.12, we present a (8,k)-LCT circuit as an example.

Figure 3.12. Leading-zero Counting Topology [5] (n = 8).

# 3.6.1. Theoretical Complexity of LCT

Complexity formulas for a (n,k)-LCT :

$$t_{LCT} = t_{one-hot} + t_{ORn} + t_{LZC_1} + t_{Equality-comparator} + t_{LZC_2}$$

$$= (k+1) + 2 \times \log_2 k + 2 \times \log_2 n + 3 = O(k + \log_2 k + \log_2 n) \qquad (3.38)$$

$$A_{LCT} = A_{one-hot} + A_{ORn} + A_{LZC_1} + A_{Equality-comparator} + A_{LZC_2}$$

$$= (2^k \times (k-1)) + (2^k \times (k-1)) + (\frac{2^k}{2} \times k)$$

$$+ (k \times 2 + k - 1) + (\frac{n}{2} \times \log_2 n)$$

$$= 2^k \times (\frac{3 \times k}{2} + n - 2) + 2k + 1 + \frac{n}{2} \times \log_2 n$$

$$+ (\frac{n^2 - 2 \times n + 8}{8}) + (\frac{n - 2}{2}) \times k \times 3$$

$$= O(2^k \times (n + k)) \qquad (3.39)$$

$P_{LCT} = A_{LCT} = O(2^k \times (n+k)) \tag{3.40}$

#### 3.7. Multi-Level Topology (MLT)

In Multi-Level Topology (MLT) [5], inputs are first divided into 2-element groups and the winner of each group is determined by a (2,k)-*cmp-mux* circuit. Then, a parallel comparison (i.e., every pair is compared each other) is applied between groups using (2,k)-*comparators*. Finally, the value of the winner is transferred to the output through a serial configuration of the multiplexers. A (8,k)-*MLT* is given in Figure 3.13 as an example. Second stage of MLT topology has the same architecture as *comparator*

Figure 3.13. Multi-Level Topology [5] (n = 8).

array unit of our AbT, which we shall explain in Section 4.1. However, MLT does not utilize the concurrency between comparison and selection operations ( $3^{rd}$  stage of MLT) in contrast to our approach. Also, MLT outputs only the value of the winner element. We can serially connect the second stage of LCT to the output of MLT to obtain the binary address of the maximum element.

# 3.7.1. Theoretical Complexity of MLT

Complexity formulas for a  $(n,k)\operatorname{-MLT}$  :

$$t_{MLT} = t_{1^{st}stage} + t_{2^{nd}stage} + t_{3^{rd}stage}$$

=  $t_{cmp-mux} + t_{comparator} + (\frac{n}{2} - 1) \times t_{mux2}$

=  $(\log_2 k + 2) + \log_2 k + (\frac{n}{2} - 1) \times 2$

=  $\frac{n}{2} + 2 \times \log_2 k = O(n + \log_2 k)$  (3.41)

$$A_{MLT} = A_{1^{st}stage} + A_{2^{nd}stage} + A_{3^{rd}stage}$$

$$= \frac{n}{2} \times A_{cmp-mux} + \left(\frac{n^2 - 2 \times n}{8}\right) \times A_{comparator}$$

$$+ \left(\frac{n^2 - 2 \times n + 8}{8}\right) \times A_{AND2} + \left(\frac{n - 2}{2}\right) \times k \times A_{mux2}$$

$$= \frac{n}{2} \times (9 \times k - 1) + \left(\frac{n^2 - 2 \times n}{8}\right) \times (6 \times k - 1)$$

$$+ \left(\frac{n^2 - 2 \times n + 8}{8}\right) + \left(\frac{n - 2}{2}\right) \times k \times 3$$

$$= O(k \times n^2)$$

(3.42)

$$P_{MLT} = A_{MLT} = O(k \times n^2) \tag{3.43}$$

# 4. PROPOSED MF CIRCUIT TOPOLOGIES

In this chapter, we present the details of our proposed topologies: Array based Topology (AbT), Hybrid Binary tree Topology (HBT), and Quad tree Topology (QT).

# 4.1. Array Based Topology (AbT)

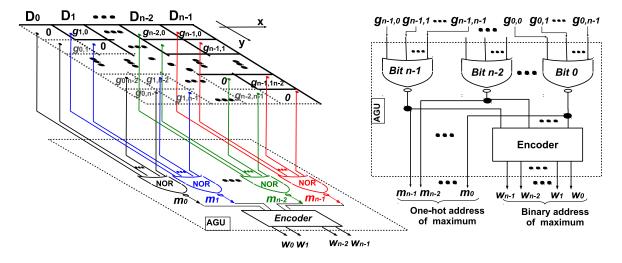

AbT is a fast MF circuit topology, where the main idea is first producing an  $n \times n$ array of 1-bit comparison results by comparing every pair of input elements in parallel, and then concurrently generating the address as well as the value of the maximum element via output logic. Carrying out all possible comparisons in parallel allows us to avoid  $\log_2 n$  stages of the binary tree topologies, and thus, AbT ends up with just one comparator on the critical path followed by some selection logic.

The conceptual block diagram of AbT is given in Figure 4.1. AbT consists of three blocks in the top-level: *Comparator Array Unit* (CAU), *Address Generation Unit* (AGU), and *Data Selection Unit* (DSU). CAU computes all magnitude relations

Figure 4.1. High-level block diagram of AbT.

in parallel, which are necessary to compute one-hot address of the maximum. AGU rapidly generates one-hot and/or binary address of the maximum by processing the

results of CAU. DSU operates concurrently with AGU and conveys the maximum element to the output. DSU uses the signals produced by intermediate stages of AGU, and hence, it does not bring any (theoretical) delay overhead on AGU.

Detailed structure of AbT will be described in the following subsections.

# 4.1.1. Comparator Array Unit (CAU)

CAU can be thought of as a preprocessing unit that constructs an  $n \times n$  array (see Figure 4.2) of 1-bit comparison results  $g_{xy}$  ( $g_{xy} = D_y > D_x$ , where  $\forall x, y \in [0, n-1]$ ) by concurrently computing all required magnitude relations between the inputs ( $D_i$ ) to produce the one-hot address of maximum. Note that x and y denote the corresponding column and row of the array, respectively, throughout this subsection.

In order to determine if a specific element  $D_i$  is the maximum  $(D_W)$  of the *n* elements, we need to compare the element  $D_i$  with all of the other elements  $(D_j$ , where  $j \neq i$ ) and thus we need (n-1) comparison operations. For instance, the following logic equation gives us if  $D_0$  is the maximum element of our input set **D**.

$$m_0 = (D_0 \ge D_1) \cdot (D_0 \ge D_2) \cdot (D_0 \ge D_3) \cdot \dots \cdot (D_0 \ge D_{n-1})$$

$$= \overline{(D_1 < D_0) + (D_2 < D_0) + (D_2 < D_0) + \dots (D_{n-1} < D_0)}$$

(4.1)

If we apply the same operations to each element of the set  $\mathbf{D}$ , we obtain Equation 4.2. In Equation 4.2, each bit  $m_i$  specifies whether the element  $D_i$  has the maximum value or not. In regards to Equation 4.2, we need  $n \times (n-1)$  comparison operations to determine the position(s) of the maximum element(s). We can do all of these operations in parallel as there is no data dependency between the required comparison operations.

However, Equation 4.2 cannot handle the cases in which more than one element has the maximum value. In such cases, the computed *n*-bit vector  $(m_{n-1}m_{n-2} \dots m_1m_0)$ shall not be one-hot. Thus, we need a priority encoder circuit to obtain the one-hot address of the maximum element. This priority encoder brings an extra area and delay overhead to the AGU. Fortunately, this problem can be solved by embedding the priority information into Equation 4.2. As a result, we obtain Equation 4.3.

$$m_{0} = (D_{0} \ge D_{1}) \cdot (D_{0} \ge D_{2}) \cdot (D_{0} \ge D_{3}) \cdot \dots \cdot (D_{0} \ge D_{n-1})$$

$$= \overline{(D_{0} < D_{1}) + (D_{0} < D_{2}) + (D_{0} < D_{3}) + \dots + (D_{0} < D_{n-1})}$$

$$m_{1} = (D_{1} \ge D_{0}) \cdot (D_{1} \ge D_{2}) \cdot (D_{1} \ge D_{3}) \cdot \dots \cdot (D_{1} \ge D_{n-1})$$

$$= \overline{(D_{1} < D_{0}) + (D_{1} < D_{2}) + (D_{1} < D_{3}) + \dots + (D_{1} < D_{n-1})}$$

$$\vdots$$

$$m_{n-1} = (D_{n-1} \ge D_{0}) \cdot (D_{n-1} \ge D_{2}) \cdot (D_{n-1} \ge D_{3}) \cdot \dots \cdot (D_{n-1} \ge D_{n-2})$$

$$= \overline{(D_{n-1} < D_{0}) + (D_{n-1} < D_{2}) + (D_{n-1} < D_{3}) + \dots + (D_{n-1} < D_{n-2})}$$

$$m_{0} = (D_{0} > D_{1}) \cdot (D_{0} > D_{2}) \cdot (D_{0} > D_{3}) \cdot \dots \cdot (D_{0} > D_{n-1})$$

$$= \overline{(D_{0} \le D_{1}) + (D_{0} \le D_{2}) + (D_{0} \le D_{3}) + \dots + (D_{0} \le D_{n-1})}$$

$$= \overline{\sum_{y=1}^{n-1}} (D_{0} \le D_{y})$$

$$m_{1} = (D_{1} \ge D_{0}) \cdot (D_{1} > D_{2}) \cdot (D_{1} > D_{3}) \cdot \dots \cdot (D_{1} > D_{n-1})$$

$$= \overline{(D_{1} < D_{0}) + (D_{1} \le D_{2}) + (D_{1} \le D_{3}) + \dots + (D_{1} \le D_{n-1})}$$

$$= (D_{1} < D_{0}) + \sum_{y=2}^{n-1} (D_{0} \le D_{y})$$

$$\vdots$$

$$(4.3)$$

$$m_{n-1} = (D_{n-1} \ge D_0) \cdot (D_{n-1} \ge D_2) \cdot (D_{n-1} \ge D_3) \cdot \dots \cdot (D_{n-1} \ge D_{n-2})$$

=  $\overline{(D_{n-1} < D_0) + (D_{n-1} < D_1) + (D_{n-1} < D_2) + \dots + (D_{n-1} < D_{n-2})}$

=  $\overline{\sum_{y=0}^{n-2} (D_2 < D_y)}$

We can also rewrite Equation 4.3 as in Equation 4.4:

$$m_{x} = \overline{\left(\sum_{y=0}^{x-1} (D_{x} < D_{y})\right) + \left(\sum_{y=x+1}^{n-1} (D_{x} \le D_{y})\right)}$$

$$= \overline{\left(\sum_{y=0}^{x-1} (g_{xy})\right) + \left(\sum_{y=x+1}^{n-1} (\overline{g_{yx}})\right)}$$

(4.4)

In this embedded priority scheme, the greater the address of an element  $D_i$  is, the greater its priority is. Using this priority scheme, we break the tie when multiple inputs possess the maximum value, and we obtain a one-hot *n*-bit address vector  $(m_{n-1}m_{n-2}\ldots m_1m_0)$  without any delay and area overhead. The priority scheme also leads to an area optimization in CAU, which shall be clear in the following paragraphs.

As seen in Equation 4.4, in order to find any  $m_x$ , we first compute *n* magnitude relations and then apply a NOR operation on the computed relations. Hence, we should compute  $n^2$  magnitude relations and should apply *n* NOR operations to obtain the whole one-hot address. The required relations are concurrently computed by CAU, while NOR operations are applied by AGU.

Fortunately, we can reduce the number of (2,k)-comparators required to obtain  $g_{xy}$  values. First, we do not need to compute  $g_{xy}$  values on the diagonal of the array because they are all zero. Second, we can compute the lower triangular part (x < y) of the array by transposing and inverting the upper triangular part (x > y) owing to our priority scheme. Hence, we can find  $g_{xy}$  value residing in column x and row y of the array using Equation 4.5.

$$g_{xy} = \begin{cases} 0 & if \ y = x, \\ D_y > D_x & if \ y < x \quad \forall x, y \in [0, n-1] \\ \overline{g_{yx}} & if \ y > x \end{cases}$$

(4.5)

Based on Equation 4.5, we compute n(n-1)/2  $g_{xy}$  values within the upper triangular part with n(n-1)/2 (2,k)-comparators. Then, we use n(n-1)/2 inverters

to compute n(n-1)/2  $g_{xy}$  values within the lower triangular part, as illustrated in Figure 4.2. In this figure, we use gray dotted lines to show the array cells computed by inverters, while we use gray solid lines for inverters and their connections. On the other hand, we use black solid lines for the cells computed directly by (2,k)-comparators. Each (2,k)-comparator of Figure 4.2 determines whether its first input  $(D_y)$  is greater than its second input  $(D_x)$  and produces a 1-bit output  $(g_x y)$ . We utilize PPN adder topologies to implement (2,k)-comparators of CAU as mentioned in Section 3.4. As a result, CAU can compute the required  $n^2$  relations, in Equation 4.5, in  $O(\log_2 k)$  time.

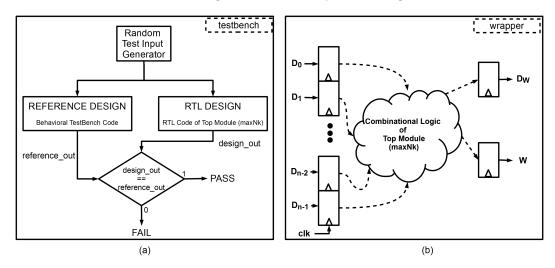

Figure 4.2. Block diagram of CAU: (a) Conceptual array view. (b) Interconnection of CAU blocks.

#### 4.1.2. Address Generation Unit (AGU)

AGU computes one-hot and/or binary address of the maximum element using n(n-1) magnitude relations computed by CAU.

AGU uses an n-input NOR gate to compute each bit of one-hot address and an encoder circuit to compute binary address, as shown in 4.3b. The *n*-element NOR gate, which produces  $m_x$  of Equation 4.4, uses  $(n-1) g_{xy}$  values within the column x of CAU. We implement an *n*-input NOR gate as a binary tree of 2-input OR gates with a final inverter. Similarly, we implement the encoder circuit as a binary tree of 2-input OR gates. Hence, AGU can generate one-hot and/or binary address of the maximum

Figure 4.3. (a) Interconnection of CAU and AGU. (b) Block diagram of AGU.

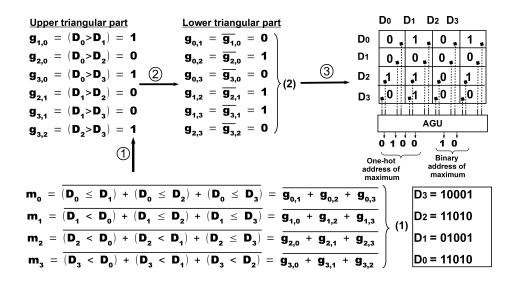

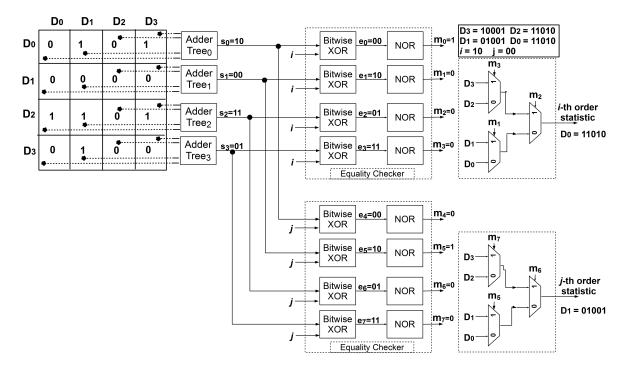

The following example, which is also shown in Figure 4.4 is useful to understand how CAU and AGU function together. Let **D** be  $\{D_3, D_2, D_1, D_0\} = \{10001, 11010, 01001, 11010\}$ . In this case, we have n = 4 and k = 5. In Figure 4.4, we explicitly give equation sets obtained from Equations 4.3 and 4.4. As it can be seen in the figure, we first compute each row of the upper triangular part of the array via (2,5)-comparators. Then, we compute the values within the lower triangular part of the array using only inverters. In this example, the maximum element is  $D_2$ , and our (4,5)-AbT example outputs one-hot address as "0100" and binary address as "10" in Figure 4.4.

#### 4.1.3. Data Selection Unit (DSU)