# FABRICATION AND CHARACTERIZATION OF A PLANAR WATER GATED TRANSISTOR UTILIZING ULTRA THIN SINGLE CRYSTALLINE SILICON FILM

by

Ozan Ertop

B.S., Electrical and Electronics Engineering, Boğaziçi University, 2012

Submitted to the Institute for Graduate Studies in Science and Engineering in partial fulfillment of the requirements for the degree of Master of Science

Graduate Program in Electrical and Electronics Engineering Boğaziçi University

2014

# FABRICATION AND CHARACTERIZATION OF A PLANAR WATER GATED TRANSISTOR UTILIZING ULTRA THIN SINGLE CRYSTALLINE SILICON FILM

APPROVED BY:

| Assoc. Prof. Şenol Mutlu   |  |

|----------------------------|--|

| (Thesis Supervisor)        |  |

| Prof. Günhan Dündar        |  |

| Assoc. Prof. Amitav Sanyal |  |

DATE OF APPROVAL: 21.07.2014

### ACKNOWLEDGEMENTS

In these past two years of my graduate education I have had several up and downs as in every stage of life and I am very grateful that I have some nice people around, who share my good times and also support me in my bad times.

I would like to start with my supervisor, Assoc. Prof. Şenol Mutlu. I am delighted that I had the great chance to work with him and look forward to continue working with him in the upcoming years as well. Here I would like to thank him for his huge understanding, valuable experience and unlimited patience. When I was starting to feel hopeless at some of the failures during the project, he always encouraged me and showed me new aspects with his original and practical ideas and suggestions.

Another person, who was always ready to help me whatever my problem was, is Gürkan Sönmez. When I had questions about my study, my project or the department, most of the times he was the one who cleared my mind. Also when we were working together in the clean room, he shared his knowledge and experience with me. He taught me some practical tricks and methods which are not found in the books.

There are some other dearest people that I like to mention here. I'm thankful to Emre for his warmest friendship. His presence in the lab made it more fun to work there. I'm also grateful to Gözde, without whom this thesis would have been finished two months earlier; but life wouldn't be as beautiful then. Other valuable friends who made the life more bearable include, but not limited to, Alper, Damla, Ekin, Eralp, Kaçkın, Mete, Onur, Özge and Zahid. I hope these people will always be close to me.

Last but not least, I like to express my deepest gratitude to my dearest family. I am thankful to my parents for raising me such that I became who I am now. Also my little brother, Oğuz, has become an indispensable part of my life since I was six.

This work is supported by Boğaziçi University Research Fund under Grant 6987.

### ABSTRACT

# FABRICATION AND CHARACTERIZATION OF A PLANAR WATER GATED TRANSISTOR UTILIZING ULTRA THIN SINGLE CRYSTALLINE SILICON FILM

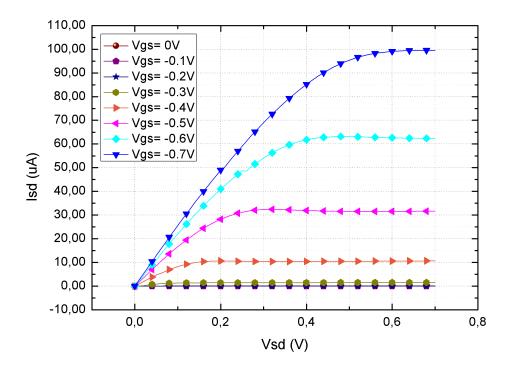

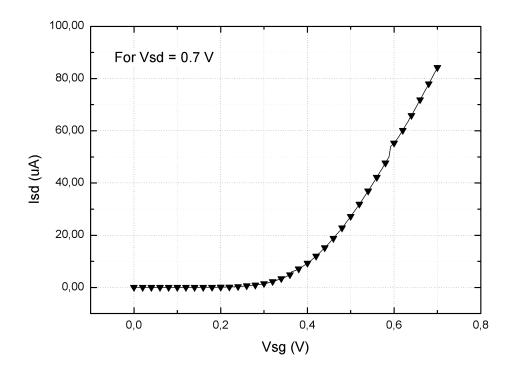

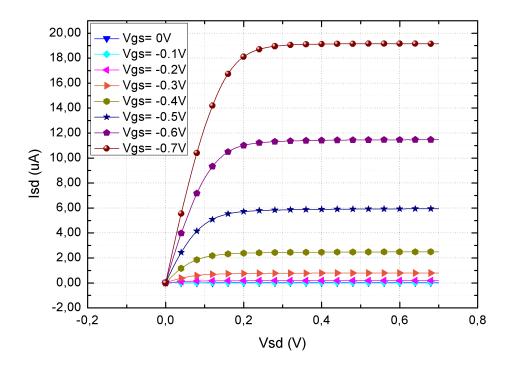

In this thesis, the fabrication and characterization of a planar water-gated thin film transistor are explained and analyzed. Silicon-on-insulator (SOI) wafer is used to build the device. Two different gate structures are used and tested. Firstly, the measurements are realized with the usual probe gate immersed into the water droplet as a reference. Then the novel planar gate structure is used. In the fabrication process, first the 16-nm thick silicon on top of the SOI wafer is patterned to build the channel area of the transistor. After that aluminum is evaporated on top of it to make the drain, source and planar gate contacts at one step. Finally, photoresist is spin coated on the drain and source electrodes to insulate them from the water droplet. After forming the transistor structure, a water droplet is dripped onto the channel area. It has contact to the gate electrode and channel, but not to the drain and source electrodes. Thanks to the this liquid-solid interface, an electrical double layer is formed on the channel, which serves as a perfect gate insulator since it is uniform, pin-hole free, very thin and has a high dielectric constant. Fabricated transistors are tested and characterized. Since the silicon used is p-type, negative voltages are applied. The transistor works between 0 V and -0.7 V. Using the probe gate structure, a maximum drain current of  $99.49 \,\mu\text{A}$  is established with an on-off ratio of 232000 and threshold voltage of 0.27 V. In the planar gate structure this values are  $19.15 \,\mu\text{A}$ , 2150 and  $0.31 \,\text{V}$  respectively. However the transistor parameters of the planar gate structure can be improved by the future developments.

### ÖZET

# ÇOK İNCE TEK KRİSTALLİ SİLİSYUM FİLM KULLANAN YATAY SIVI KAPILI TRANSİSTÖRÜN ÜRETİMİ VE BELİRLENMESİ

Bu tezde, yatay sıvı kapılı bir ince film transistörün üretimi ve belirlenmesi açıklanıp analiz edilmiştir. Cihazı üretmek için yalıtkan üstü silikon (SOI) pul kullanılmıştır. İki farklı kapı yapısı kullanılmış ve test edilmiştir. İlk olarak referans olması amacıyla, su damlasının içine batırılan klasik ince tel kapıyla ölçümler gerçekleştirilmiştir. Daha sonra özgün yatay kapı yapısı kullanılmıştır. Üretim aşamasında öncelikle transistörün kanal bölgesini oluşturmak için SOI pulun üzerindeki 16 nm kalınlığında silisyum şekillendirilmiştir. Daha sonra üzerine tek seferde kaynak, savak ve yatay kapi kontaklarını yapmak için alüminyum buharlaştırılmıştır. Son olarak kaynak ve savak elektrotlarının üzerine, bunları su damlasından izole etmek için, döndürmeli fotorezist kaplanmıştır. Transistör yapısını oluşturduktan sonra, kanal bölgesi üzerine bir su damlası damlatılmıştır. Su damlası kapı elektroduna ve kanala temas etmekte, fakat kaynak ve savak elektrotlarına temas etmemektedir. Bu katısıvı arayüzü sayesinde kanal üzerinde mükemmel bir kapı yalıtkanı olarak hizmet eden bir elektrik çift katman oluşmaktadır, çünkü bu katman düzgün, deliksiz, çok incedir ve yüksek dielektrik sabitine sahiptir. Üretilen transistörler test edilip karakterize edilmiştir. Kullanılan silisyum p tipi olduğu için negatif gerilimler uygulanmıştır. Transistör 0V ile -0.7V arasında çalışmaktadır. Ince tel kapı yapısını kullanarak  $99.49 \,\mu\text{A}$  maksimum savak akımı, 232000 açık-kapalı akım oranı ve  $0.27 \,\text{V}$  eşik gerilimi elde edilmiştir. Yatay kapı yapısında bu değerler sırasıyla  $19.15 \,\mu \text{A}, 2150 \text{ ve } 0.31 \text{ V}$ olarak ölçülmüştür. Ancak yatay kapı yapısının transistör parametreleri gelecekteki geliştirmelerle iyileştirilebilir.

# TABLE OF CONTENTS

| AC  | CKNC | OWLED   | OGEMENTS                                     | iii  |

|-----|------|---------|----------------------------------------------|------|

| AE  | BSTR | ACT     |                                              | iv   |

| ÖZ  | ZЕТ  |         |                                              | v    |

| LIS | ST O | F FIGU  | JRES                                         | viii |

| LIS | ST O | F TAB   | LES                                          | xi   |

| LIS | ST O | F SYM   | BOLS                                         | xii  |

| LIS | ST O | F ACR   | ONYMS/ABBREVIATIONS                          | xiv  |

| 1.  | INT  | RODU    | CTION                                        | 1    |

|     | 1.1. | Silicon | -on-Insulator Wafer                          | 2    |

|     | 1.2. | Motiva  | ation and Novelty                            | 4    |

|     | 1.3. | Outlin  | e of the Thesis                              | 6    |

| 2.  | THE  | ORY     |                                              | 7    |

|     | 2.1. | Water-  | -Gated Field Effect Transistors              | 7    |

|     |      | 2.1.1.  | Principle of Operation                       | 8    |

|     |      | 2.1.2.  | Electrical Characteristics                   | 9    |

|     |      | 2.1.3.  | Electrical Double Layer                      | 12   |

|     |      | 2.1.4.  | Planar WG-FET                                | 16   |

|     | 2.2. | Band I  | Diagrams of Metal-Semiconductor Junctions    | 17   |

|     |      | 2.2.1.  | Establishment of Ohmic Contact               | 17   |

| 3.  | STR  | UCTUI   | RE OF THE FABRICATED DEVICE                  | 20   |

|     | 3.1. | Fabric  | ation                                        | 21   |

|     |      | 3.1.1.  | Photolithography and Wet Etching of Silicon  | 21   |

|     |      | 3.1.2.  | Aluminum Evaporation                         | 22   |

|     |      | 3.1.3.  | Photolithography and Wet Etching of Aluminum | 22   |

|     |      | 3.1.4.  | Thermal Annealing                            | 24   |

|     |      | 3.1.5.  | Photoresist as Insulator Layer               | 25   |

| 4.  | MEA  | ASURE   | MENTS AND CHARACTERIZATION OF THE DEVICE     | 27   |

|     | 4.1. | Measu   | rement Equipment                             | 27   |

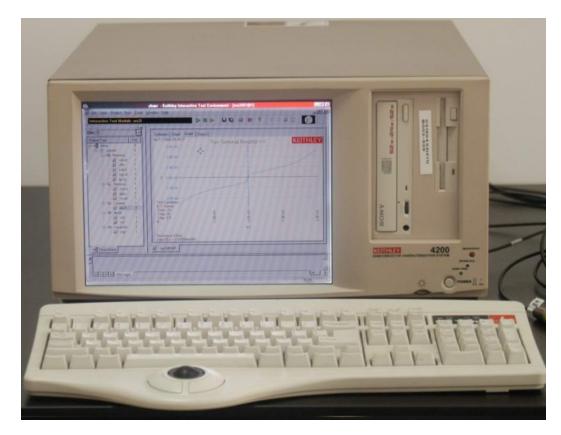

| 4.1.1. Keithley Characterization System               | 27 |

|-------------------------------------------------------|----|

| 4.1.2. Probes                                         | 28 |

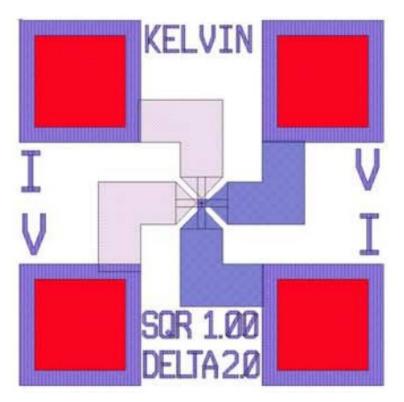

| 4.2. Kelvin Contact Measurement                       | 29 |

| 4.3. Measurements of the Probe and Planar Gate Design | 30 |

| 4.4. Transistor Parameters                            | 34 |

| 4.4.1. On-off Ratio                                   | 34 |

| 4.4.2. Threshold Voltage                              | 34 |

| 4.4.3. Comparison of the Gate Structures              | 36 |

| 5. CONCLUSIONS AND FUTURE WORK                        | 38 |

| APPENDIX A: LAYOUT IMAGES OF THE WG-FET               | 40 |

| REFERENCES                                            | 43 |

## LIST OF FIGURES

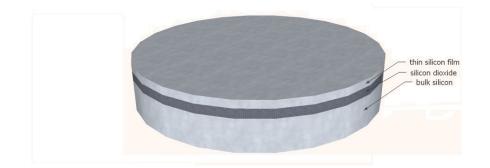

| Figure 1.1. | A silicon-on-insulator wafer.                                    | 2  |

|-------------|------------------------------------------------------------------|----|

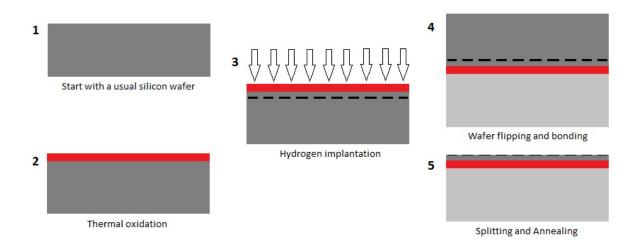

| Figure 1.2. | Production of SOI wafer by Smart Cut method                      | 3  |

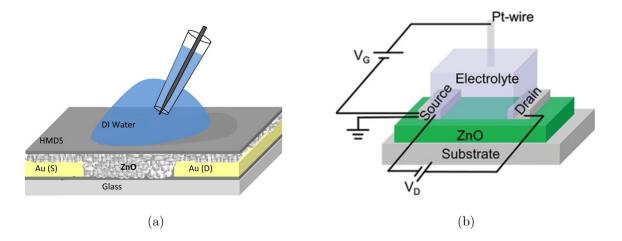

| Figure 2.1. | Water-gated field effect transistors.                            | 7  |

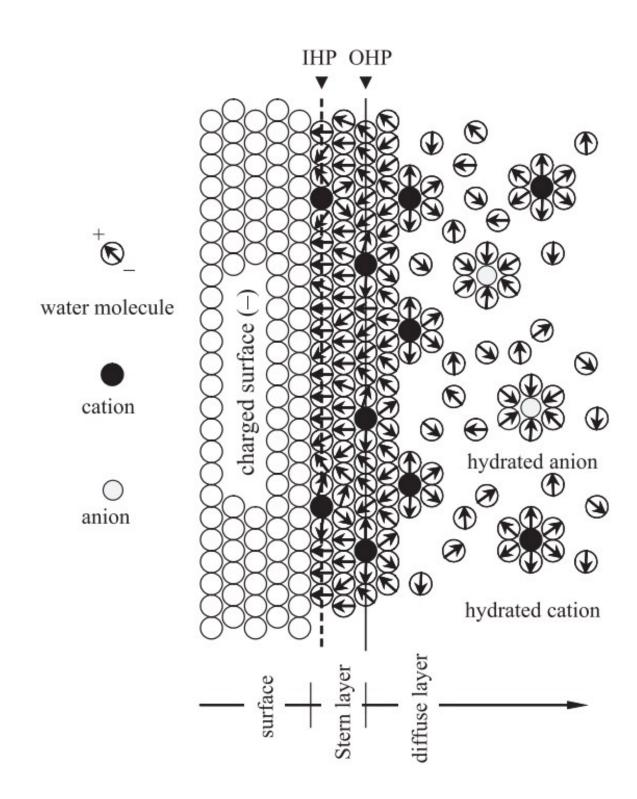

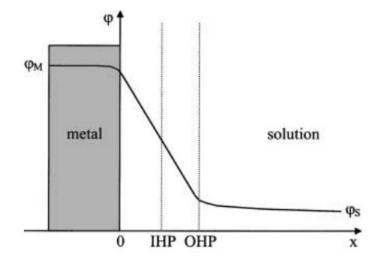

| Figure 2.2. | Schematic model of the EDL                                       | 13 |

| Figure 2.3. | Potential profile in the double layer                            | 15 |

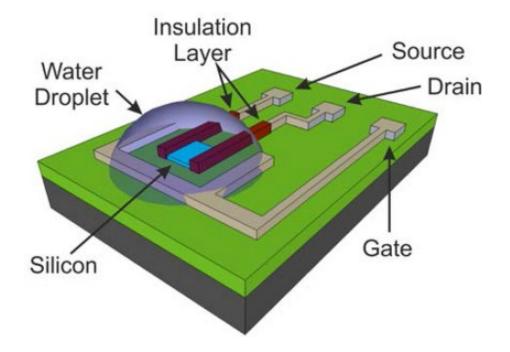

| Figure 2.4. | Planar water-gated field effect transistor                       | 16 |

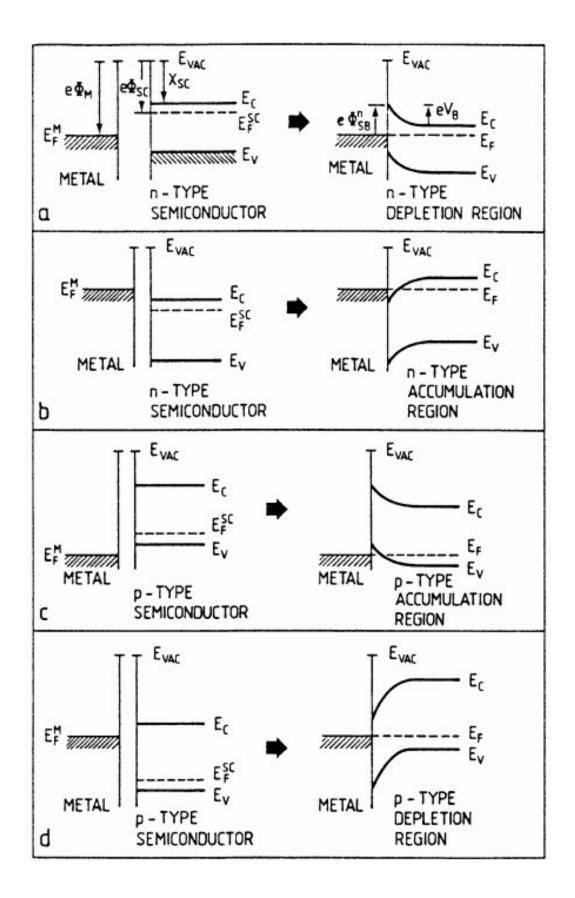

| Figure 2.5. | Band bending before and after metal-semiconductor contact        | 18 |

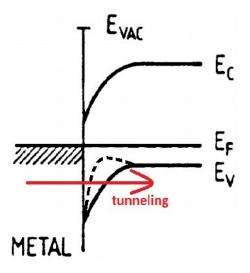

| Figure 2.6. | The band diagram after annealing that enables tunneling          | 19 |

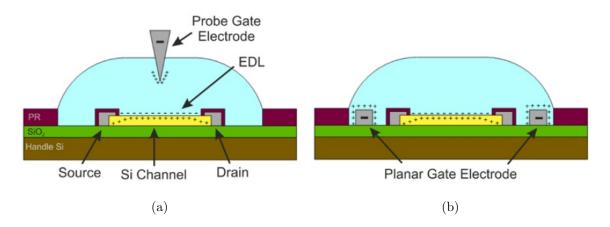

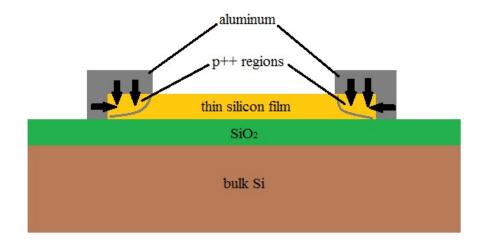

| Figure 3.1. | Structure of the transistor using the probe gate and planar gate | 20 |

| Figure 3.2. | SOI wafer before and after the wet etching of silicon. $\hdots$  | 21 |

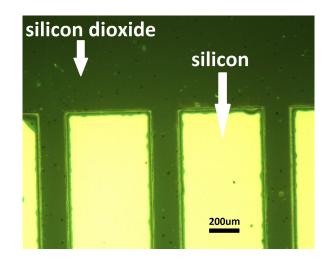

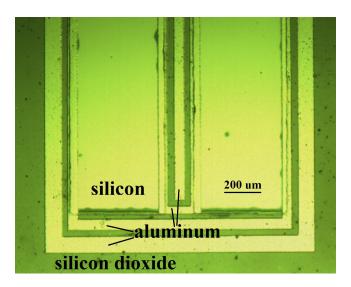

| Figure 3.3. | The micrograph of the sample after silicon etching               | 22 |

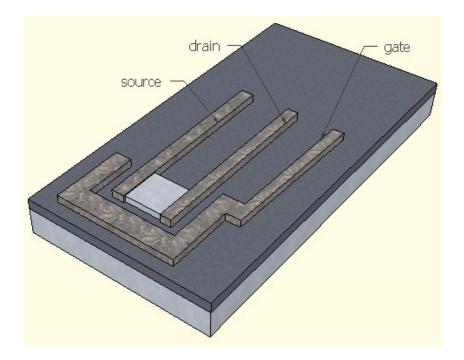

| Figure 3.4. | The sample after the wet etching of aluminum                     | 23 |

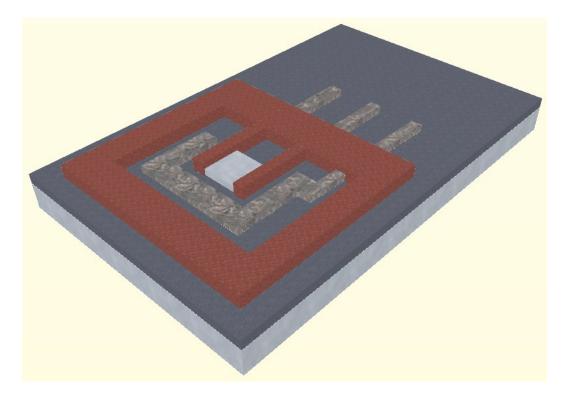

| Figure 3.5. | The micrograph of the sample after the wet etching of aluminum.  | 23 |

| Figure 3.6. | Diffusion of Al atoms into Si during annealing                   | 24 |

| Figure 3.7.  | The sample after the photolithography of the photoresist                             | 25 |

|--------------|--------------------------------------------------------------------------------------|----|

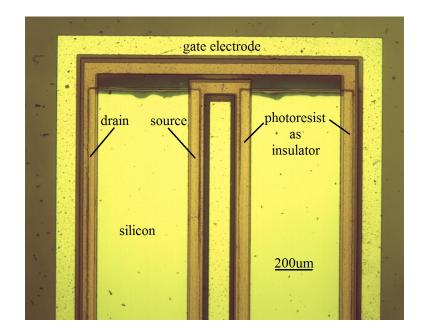

| Figure 3.8.  | The micrograph of the final device.                                                  | 26 |

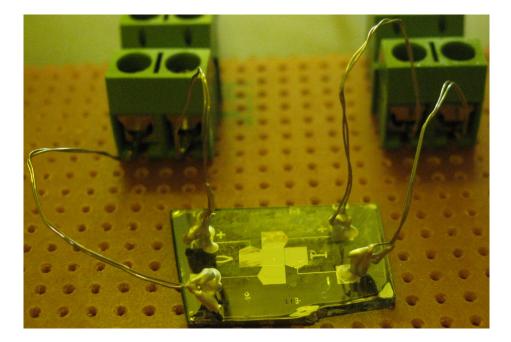

| Figure 3.9.  | Final form of the transistor with silver-epoxy contacts. $\ . \ . \ .$ .             | 26 |

| Figure 4.1.  | Keithley 4200SCS semiconductor characterization system                               | 27 |

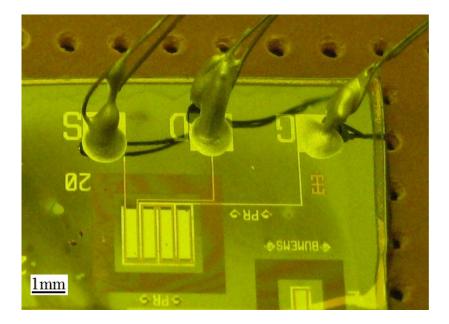

| Figure 4.2.  | Gate structure and contacts of the WG-FET's                                          | 28 |

| Figure 4.3.  | Kelvin contact measurement layout                                                    | 29 |

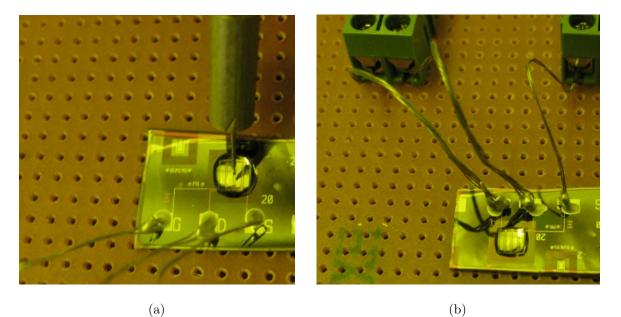

| Figure 4.4.  | Kelvin contact measurement setup.                                                    | 30 |

| Figure 4.5.  | $I_{\rm sd} - V_{\rm sd}$ curve of the probe gate design                             | 31 |

| Figure 4.6.  | $I_{\rm sd} - V_{\rm sg}$ curve of the probe gate design for $V_{\rm sd} = -0.07V$   | 31 |

| Figure 4.7.  | $I_{\rm sd} - V_{\rm sg}$ curve of the probe gate design for $V_{\rm sd} = -0.7V.$   | 32 |

| Figure 4.8.  | $I_{\rm sd} - V_{\rm sd}$ curve of the planar gate design                            | 32 |

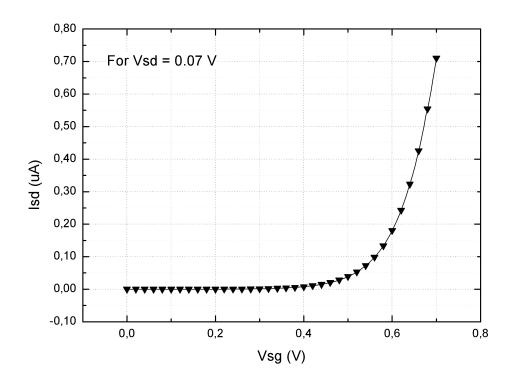

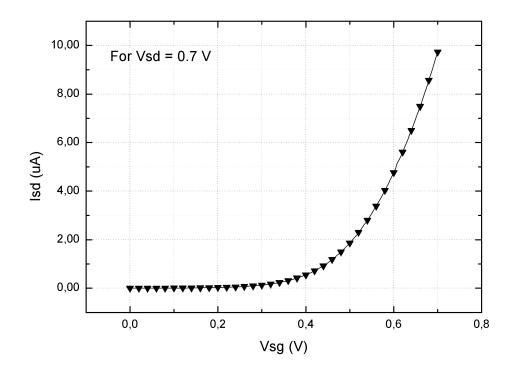

| Figure 4.9.  | $I_{\rm sd} - V_{\rm sg}$ curve of the planar gate design for $V_{\rm sd} = -0.07V.$ | 33 |

| Figure 4.10. | $I_{\rm sd} - V_{\rm sg}$ curve of the planar gate design for $V_{\rm sd} = -0.7V.$  | 33 |

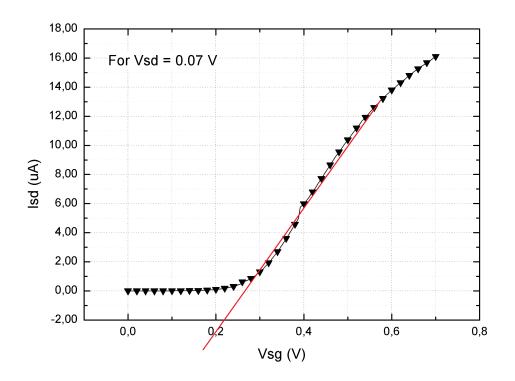

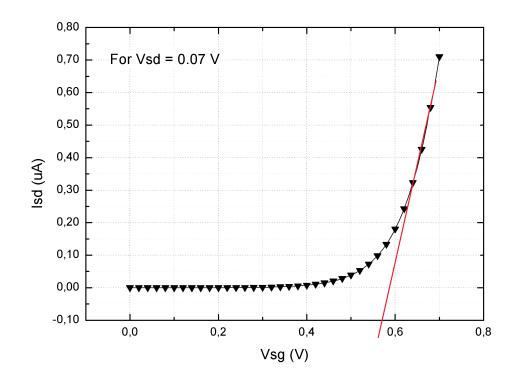

| Figure 4.11. | Extrapolation of the $I_{\rm sd}-V_{\rm sg}$ curve in probe gated design             | 35 |

| Figure 4.12. | Extrapolation of the $I_{\rm sd}-V_{\rm sg}$ curve in planar gated design            | 35 |

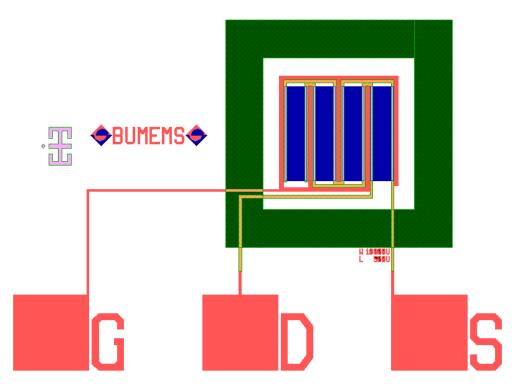

| Figure A.1.  | Layout design of WG-FET                                                              | 40 |

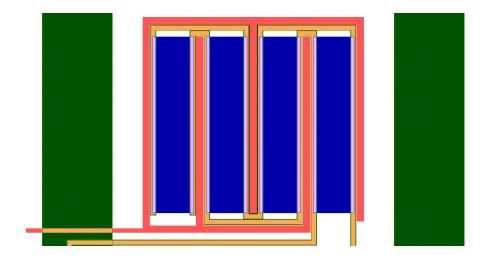

| Figure A.2. | Closer view of the layout design of WG-FET | 40 |

|-------------|--------------------------------------------|----|

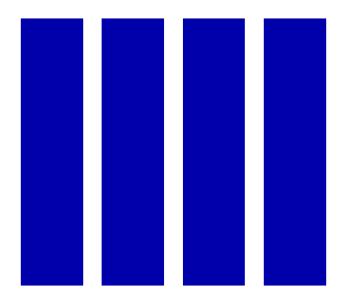

| Figure A.3. | Layout design of silicon mask.             | 41 |

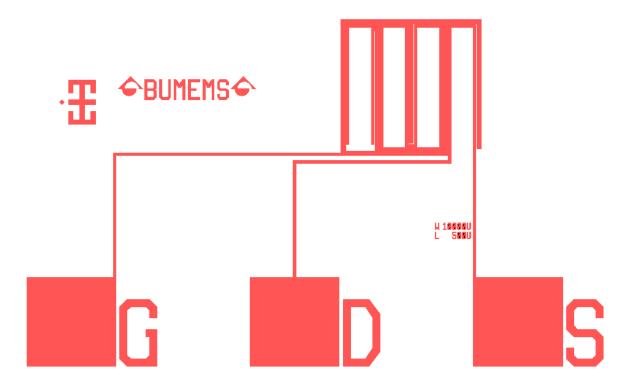

| Figure A.4. | Layout design of aluminum mask             | 41 |

| Figure A.5. | Closer view of the layout of aluminum mask | 42 |

| Figure A.6. | Layout design of photoresist mask          | 42 |

## LIST OF TABLES

| Table 4.1. | Comparison | of probe and | l planar gated WG-FET's | . 36 |

|------------|------------|--------------|-------------------------|------|

|            |            |              |                         |      |

## LIST OF SYMBOLS

| Al                  | Aluminum                                   |

|---------------------|--------------------------------------------|

| $C_{ m d}$          | Diffuse layer capacitance                  |

| $C_{ m dl}$         | Double layer capacitance                   |

| $C_{ m i}$          | Gate insulator capacitance per area        |

| $C_{ m s}$          | Stern layer capacitance                    |

| d                   | Distance between two plates of a capacitor |

| $g_{ m m}$          | Transconductance                           |

| $H_2O$              | Water                                      |

| $HNO_3$             | Nitric acid                                |

| $I_{ m d}$          | Drain current                              |

| $I_{ m d,V_{gmax}}$ | Drain current at maximum gate voltage      |

| $I_{ m d,Vg_{min}}$ | Drain current at minimum gate voltage      |

| $I_{ m d_{lin}}$    | Drain current at linear region             |

| $I_{ m d_{sat}}$    | Drain current at saturation region         |

| $I_{ m sd}$         | Source-to-drain current                    |

| L                   | Length of the semiconductor channel        |

| n                   | n-type doping concentration                |

| $NH_4F$             | Ammonium fluoride                          |

| p                   | p-type doping concentration                |

| $p^{++}$            | p-type high concentration doping           |

| q                   | Elementary charge                          |

| Si                  | Silicon                                    |

| $SiO_2$             | Silicon dioxide                            |

| $SnS_2$             | Tin(IV) sulfide                            |

| $V_{ m dd}$         | IC power-supply pin                        |

| $V_{ m sd}$         | Source-to-drain voltage                    |

| $V_{ m sg}$         | Source-to-gate voltage                     |

| $V_{ m th}$         | Threshold voltage                          |

| W                 | Width of the semiconductor channel |

|-------------------|------------------------------------|

| ZnO               | Zinc oxide                         |

|                   |                                    |

| $\epsilon_0$      | Permittivity of vacuum             |

| $\epsilon_{ m r}$ | Relative permittivity              |

| $\mu_n$           | Electron mobility                  |

| $\mu_p$           | Hole mobility                      |

| Ω                 | Ohm                                |

| $\Psi_1$          | Electrical potential at the OHP    |

| $\Psi_2$          | Electrical potential at the IHP    |

| ρ                 | Resistivity                        |

|                   |                                    |

# LIST OF ACRONYMS/ABBREVIATIONS

| DI             | Deionized (water)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EDL            | Electrical double layer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| FET            | Field effect transistor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| HMDS           | Hexamethyldisilazane                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| IBM            | International Business Machines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| IHP            | Inner Helmholtz plane                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| ISFET          | Ion-sensitive field effect transistor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| MEMS           | Micro-electro-mechanical systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| MOSFET         | Metal-oxide-semiconductor field effect transistor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| OFET           | Organic field effect transistor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| OHP            | Outer Helmholtz plane                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| P3HT           | Poly(3-hexylthiophene-2,5-diyl)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| PBTTT          | Poly (2, 5-bis (3-hexadecylthiophen-2-yl) thieno [3, 2-bis (3-hexadecylthiophen-2-yl) thieno [3, 2-bis (3-hexadecylthiophen-2-yl) thieno [3, 2-bis (3-hexadecylthiophen-2-yl) thieno [3, 2-bis (3-hexadecylthiophen-2-yl) thieno [3, 2-bis (3-hexadecylthiophen-2-yl) thieno [3, 2-bis (3-hexadecylthiophen-2-yl) thieno [3, 2-bis (3-hexadecylthiophen-2-yl] thieno [3, 2-bis (3-hexadecylthiophen-2-yl] thieno [3, 2-bis (3-hexadecylthiophen-2-yl] thieno [3, 2-bis (3-hexadecylthiophen-2-yl] thieno [3, 2-bis (3-hexadecylthiophen-2-yl] thieno [3, 2-bis (3-hexadecylthiophen-2-yl] thieno [3, 2-bis (3-hexadecylthiophen-2-yl] thieno [3, 2-bis (3-hexadecylthiophen-2-yl] thieno [3, 2-bis (3-hexadecylthiophen-2-yl] thieno [3, 2-bis (3-hexadecylthiophen-2-yl] thieno [3, 2-bis (3-hexadecylthiophen-2-yl] thieno [3, 2-bis (3-hexadecylthiophen-2-yl] thieno [3, 2-bis (3-hexadecylthiophen-2-yl] thieno [3, 2-bis (3-hexadecylthiophen-2-yl] thieno [3, 2-bis (3-hexadecylthiophen-2-yl] thieno [3, 2-bis (3-hexadecylthiophen-2-yl] thieno [3, 2-bis (3-hexadecylthiophen-2-yl] thieno [3, 2-bis (3-hexadecylthiophen-2-yl] thieno [3, 2-bis (3-hexadecylthiophen-2-yl] thieno [3, 2-bis (3-hexadecylthiophen-2-yl] thieno [3, 2-bis (3-hexadecylthiophen-2-yl] thieno [3, 2-bis (3-hexadecylthiophen-2-yl] thieno [3, 2-bis (3-hexadecylthiophen-2-yl] thieno [3, 2-bis (3-hexadecylthiophen-2-yl] thieno [3, 2-bis (3-hexadecylthiophen-2-yl] thieno [3, 2-bis (3-hexadecylthiophen-2-yl] thieno [3, 2-bis (3-hexadecylthiophen-2-yl] thieno [3, 2-bis (3-hexadecylthiophen-2-yl] thieno [3, 2-bis (3-hexadecylthiophen-2-yl] thieno [3, 2-bis (3-hexadecylthiophen-2-yl] thieno [3, 2-bis (3-hexadecylthiophen-2-yl] thieno [3, 2-bis (3-hexadecylthiophen-2-yl] thieno [3, 2-bis (3-hexadecylthiophen-2-yl] thieno [3, 2-bis (3-hexadecylthiophen-2-yl] thieno [3, 2-bis (3-hexadecylthiophen-2-yl] thieno [3, 2-bis (3-hexadecylthiophen-2-yl] thieno [3, 2-bis (3-hexadecylthiophen-2-yl] thieno [3, 2-bis (3-hexadecylthiophen-2-yl] thieno [3, 2-bis (3-hexadecylthiophen-2-yl] thieno [3, 2-bis (3-he |

|                | b]thiophene)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| PR             | Photoresist                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| SC             | Semiconductor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| SIMOX          | Separation by implantation of oxygen                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| SOI            | Silicon-on-insulator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| SOITEC         | Silicon-on-insulator Technology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| $\mathrm{TFT}$ | Thin film transistor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| UV             | Ultraviolet                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| VLSI           | Very-large-scale integration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| WG-FET         | Water-gated field effect transistor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

### 1. INTRODUCTION

At Bell Telephone Laboratories, J. Bardeen and W. H. Brattain were working on finding a smaller, more efficient, more reliable, more durable and cheaper replacement for the vacuum tubes [1]. In 1948 when they built the first transistor, they didn't only invent a better amplifier than the vacuum tube, but also a digital circuit element that will find itself a place in almost every electronic device in the future [2]. The device they created has evolved and evolved through the years, as a result there are numerous sub-types of the transistor now. Even a paper about the transistor consisting of one single atom has been published in year 2012 [3].

For instance, there are transistors containing an organic semiconductor as their channel material instead of the usual inorganic ones like silicon or germanium. Different types of semiconductor polymers like PBTTT [4] and P3HT [5] are used to build such transistors. Other than that, there are also ion-sensitive field effect transistors (ISFET) which are mostly used for sensing purposes. They have a solution on top of their channel area, which is practically used as the gate electrode. A nanoscale pH sensor sensing the change of pH in this solution [6] is an example to this type of transistor. Another special kind of the field effect transistor is the thin-film transistor (TFT), which usually contains a thin deposited layer of semiconductor as the channel region. The semiconductor used can be inorganic or organic as well. It is shown that some basic digital circuits can be designed using organic thin-film transistors [7]. Using thin-films may enable compatibility with optoelectronics, too. A thin-film field effect transistor using a single-crystalline thin-film transparent oxide semiconductor is fabricated [8] and this transparency provides promising combination with optoelectronic devices.

Thanks to the variety of the available transistors, specific devices for specific application areas can be produced. The fabricated transistor, which is described and analyzed in the following chapters of this thesis, is a novel combination of an inorganic thin-film transistor and an ISFET. The thin-film semiconductor of the transistor is not produced through deposition though. The thin silicon film on a silicon-on-insulator (SOI) wafer is used, which is single-crystalline and thus advantageous in terms of mobility and stability. Through dripping a water droplet on top of this silicon, the gate insulator is created. This design looks similar to an ISFET. However the fabricated device is not primarily designed as a sensor, but as a field effect transistor (FET) and it performs well as a transistor. Additionally, this similarity to an ISFET makes the transistor a prospective candidate for possible sensor compatibility.

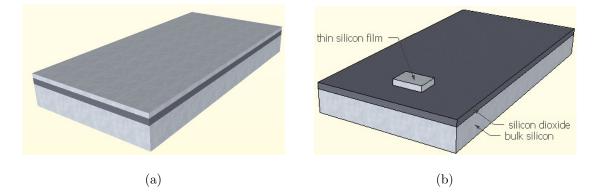

#### 1.1. Silicon-on-Insulator Wafer

A silicon-on-insulator wafer is a modified version of the usual single crystalline silicon wafers. Unlike a usual silicon wafer, it contains a thin single crystalline silicon film on top of a thin insulator layer, which is usually silicon dioxide. These thin layers of silicon and insulator are located on a thick bulk silicon [9].

Figure 1.1. A silicon-on-insulator wafer (not to scale).

SOI wafers may simplify the fabrication and improve the performance for specific designs of MEMS and VLSI. Having an insulator layer between the channel region silicon and bulk silicon enhances the characteristics of the fabricated device by reducing parasitic effects [10]. Thanks to these advantages SOI wafers find themselves a place in the industry, too. Some technology companies are using SOI wafers to build their transistors. In 2011, a multicore server processor was built from SOI transistors by IBM [11]. It was an eight-core processor fabricated in 45-nm SOI technology with 11 levels of metal and contained more than one billion SOI transistors.

Figure 1.2. Production of SOI wafer by Smart Cut method.

There are several ways to produce silicon-on-insulator wafers. One method is growing the topmost silicon directly on the insulator layer, which is called as the seed method. The epitaxial growth of silicon is enabled by the vias through the insulator from the bulk silicon. Another production method is called separation by implantation of oxygen (SIMOX) and it uses an oxygen ion beam implantation process to implant the oxygen molecules under the surface. Then the wafer is annealed at high temperature to create the buried  $SiO_2$  layer [12]. Finally, the last method that will be mentioned here is achieved through wafer bonding. As shown in Figure 1.2, in this method a silicon wafer is thermally oxidized and then hydrogen atoms are implanted under the silicon dioxide layer. Then it is bonded to another silicon wafer and the bulk under the hydrogen implanted layer is cut away [13]. The hydrogen implantation enables the splitting of the wafer to be precise and smooth. After that a heat treatment is applied to give the SOI wafer its final form. This method is referred as the Smart Cut method.

The SOI wafers used in this project are purchased from the company SOITEC and they use the Smart Cut method to produce them. They have several types of SOI wafers for specific application areas. The ones that are used in this work to build the water-gated transistor have 16 nm p-type single crystalline silicon film on top of 145 nm SiO<sub>2</sub> layer. The resistivity of the top silicon layer is  $10 \Omega \cdot cm$  and from this resistivity value, the doping concentration can be found using the Equation 1.1, where  $\rho$  is the resistivity, q is the elementary electric charge,  $\mu_n$  and  $\mu_p$  are the mobility of an electron and a hole respectively and n and p are the n-type and p-type doping concentrations.

$$\rho = \frac{1}{q(\mu_n n + \mu_p p)} \tag{1.1}$$

Since the silicon is p-type, the acceptor atom concentration is dominant over the donor atom concentration, so the  $\mu_n n$  part of the equation can be neglected, which leads to

$$\rho = \frac{1}{q\mu_p p} \,. \tag{1.2}$$

When the  $\rho$ , q and  $\mu_p$  values are inserted into the Equation 1.2, the acceptor atom concentration is found as  $p = 1.4 \times 10^{15} \text{ cm}^{-3}$ , which means that the single crystalline silicon used to build the transistor is lightly doped.

#### 1.2. Motivation and Novelty

In today's world, almost every electronic device contains millions, if not billions, of MOSFET's inside and the production of these classical MOSFET's requires very expensive facilities. Also as the device sizes get smaller and smaller, building a uniform, pin-hole free gate insulator becomes more difficult. However some application areas don't require such small devices or fast performance. Bigger or slower transistors, which satisfy the needs of these application fields, can be produced at a much lower price.

A water-gated transistor can be an alternative to the MOSFET where high performance is not a necessity. When the water droplet is placed directly on the semiconductor, then this liquid-solid interface brings several advantages. First of all, the very thin electrical double layer, which is formed at this interface, behaves as a perfect gate insulator. The liquid covers the top of the semiconductor uniformly and the resulting gate insulator becomes pin-hole free. This double layer has relatively high dielectric constant ( $\epsilon_r = 80.1$ ) compared to the frequently used silicon dioxide ( $\epsilon_r = 3.9$ ) as well. Its small thickness combined with its high dielectric constant presents a better gate insulator capacitance and thanks to this improvement the introduced transistor can function below 0.7 V, which may make it suitable for low power applications. This voltage level is desirable for another aspect, too. Since the device has water in design, the possibility of hydrolysis is dangerous for the proper functioning of the device. However the water gets hydrolyzed at 1.23 V [14] and working below 0.7 V eliminates this possibility. On top of these advantages, water-gated transistors can easily be compatible with biosensors, since these sensors require fluidic interfaces.

Previously, a water gated organic FET device was introduced as a cheap and simple alternative [15]. It uses a semiconductor polymer thin film in the channel region. A water droplet is used as the gate insulator and a probe is immersed into the water as the gate electrode. However organic materials have a certain life time and stability problems due to polymer degradation. Also the mobility and performance of the polymer devices are very low compared to the inorganic semiconductor devices.

The water-gated transistor, which is fabricated and characterized throughout this thesis, uses an inorganic semiconductor, single crystalline silicon, to overcome the problems associated with organic materials. Silicon has higher mobility, is stable throughout the time and less sensitive to environmental conditions.

In addition to the mentioned desirable properties of the fabricated water-gated transistor, a planar gate electrode structure is integrated as well. This structure was used with success in an organic transistor previously [16]. This planar gate design simplifies the integration of several devices on the same die. Otherwise for every transistor a probe top gate should have been used separately. Also the gate electrode is fabricated at the same time when drain and source electrodes are being built, which makes the fabrication of the transistor more practical.

#### 1.3. Outline of the Thesis

Up to this point in Chapter 1, various transistor types that are associated with the fabricated transistor of this work are briefly presented, along with some familiarizing examples. Following this, silicon-on-insulator wafer is introduced and the SOI wafer used in this work is presented. Finally the motivation behind this project and its novelty are told.

In Chapter 2, different types and applications of water-gated FET's are described. Then the theory behind the field effect transistors and especially the water-gated FET's is explained along with their principal of operation and electrical characteristics. The electrical double layer, which is the key concept of the water-gated devices, is presented. After that, a short introduction to the band structures is made to clarify why an annealing step is needed to establish an ohmic contact between the metal and the semiconductor.

In Chapter 3, both structures of the fabricated transistor, planar gated and probe gated, are described and the fabrication process is explained step by step.

In Chapter 4, the measurements of the planar gated and probe gated transistors are presented after introducing the measurement equipment. Then, using these measurement results, the transistors are characterized and compared in terms of their performance.

In Chapter 5, the document is concluded with a brief summary of the measurement and characterization results, which is followed by an introduction of the possible future works of the project.

### 2. THEORY

#### 2.1. Water-Gated Field Effect Transistors

A water-gated field effect transistor (WG-FET) is a special type FET, which contains water on its gate insulator or uses the water directly as the gate insulator. The gate electrode is mostly a needle probe immersed into the water from top. Dripping the water droplet onto the gate insulator isolates the water from the channel and in most of the designs from the drain and source electrodes as well. This isolation enables the transistor to be more stable, since the possibility of hydrolysis and current leakage through the water are avoided. However the voltage that is needed to modulate the channel becomes very high in that case because of the insulator layer. In the other type, where the water is placed directly on the channel, the electrical double layer in the liquid-solid interface behaves as the gate insulator, which is very thin and consequently needs lower gate voltage. The drawback of this design is the possibility of hydrolysis above 1 V and current leakage.

Figure 2.1. WG-FET's with (a) water placed on the insulator layer [17] and (b) water placed on the channel [18].

Both types of WG-FET's can be used according to the needs of the desired application. Two transistors using ZnO as the inorganic semiconductor material can

be seen in Figure 2.1. In the first one, the water droplet is placed on the nonconductive HMDS layer [17]. However in the second one, the liquid is dripped directly on the ZnO layer [18]. Both of them use a top probe gate electrode to modulate the drain current.