## PERFORMANCE AND COST EFFICIENT RELIABILITY FRAMEWORK FOR MULTICORE ARCHITECTURES

by

Sanem Arslan Yılmaz B.S., Computer Engineering, Marmara University, 2009 M.S., Computer Engineering, Boğaziçi University, 2011

Submitted to the Institute for Graduate Studies in Science and Engineering in partial fulfillment of the requirements for the degree of Doctor of Philosophy

Graduate Program in Computer Engineering Boğaziçi University 2017

## PERFORMANCE AND COST EFFICIENT RELIABILITY FRAMEWORK FOR MULTICORE ARCHITECTURES

### APPROVED BY:

| Prof. Can Özturan                 |  |

|-----------------------------------|--|

| (Thesis Supervisor)               |  |

|                                   |  |

| Prof. Haluk Rahmi Topcuoğlu       |  |

| (Thesis Co-supervisor)            |  |

|                                   |  |

| Prof. Arda Yurdakul               |  |

|                                   |  |

| Assoc. Prof. Alper Şen            |  |

|                                   |  |

| Assoc. Prof. Deniz Turgay Altılar |  |

|                                   |  |

| Assoc. Prof. Gürhan Küçük         |  |

|                                   |  |

DATE OF APPROVAL: 15.05.2017

### ACKNOWLEDGEMENTS

I would like to express my gratitude to my thesis advisors Prof. Oğuz Tosun and Prof. Haluk Topcuoğlu for their support, encouragement, and guidance throughout my graduate study and completion of this thesis. I would like to thank my last-year advisor, Prof. Can Özturan for his help and suggestions. I also want to thank Prof. Mahmut Kandemir (from Pennsylvania State University) for his valuable feedback and guidance during my dissertation. I would also thank to Prof. Arda Yurdakul, Assoc. Prof. Alper Şen, Assoc. Prof. Deniz Turgay Altılar, and Assoc. Prof. Gürhan Küçük for their participation in my thesis jury, their useful comments, and feedback.

I gratefully acknowledge the financial support of The Scientific and Technological Research Council of Turkey (TUBITAK) BIDEB 2211. This work was also supported by TUBITAK through a research grant (Project Number:113E530).

I would like to thank my colleagues from the Department of Computer Engineering at Marmara University for their support and friendship. In particular, I would like to thank Betül Boz and Işıl Öz for their invaluable support and friendship throughout the years.

I would like to offer my thanks to my father Hüseyin Arslan and my sister Azime Evrim Arslan for their endless love and great support during my dissertation. I am eternally grateful to my mother Mukaddes Arslan (now deceased, greatly missed) who always believed in my ability to be successful in the academic arena. The biggest credit goes to my dear husband, Tanju Yılmaz. I am grateful for his love, patience, sacrifices, and understanding. This thesis (along with everything else I have in life) was made possible thanks to your support.

### ABSTRACT

# PERFORMANCE AND COST EFFICIENT RELIABILITY FRAMEWORK FOR MULTICORE ARCHITECTURES

Modern architectures become more vulnerable to soft errors with technology scaling. Enabling fault tolerance capabilities on all cache structures in a system is inefficient in terms of performance and power consumption. In this study, we propose an enhanced protection mechanism for code segments, which are critical in terms of reliability, by utilizing asymmetrically reliable cores under performance and power constraints. Our proposed system contains at least one high-reliability core, which has an ECC-protected L1 cache, and several low-reliability cores, which have no protection mechanisms. Our framework protects only reliability-based critical code regions of each application, which are determined based on critical data usage, user annotations, or static analysis. In our first attempt, the framework dynamically assigns the software threads executing critical code fragments to the protected core(s) by using the First Come First Served (FCFS) algorithm. Our experimental evaluation shows that the proposed approach takes advantage of protecting only critical code regions and presents comparable performance and reliability results with fully protected systems having lower power consumption and cost values for a set of applications. However, the FCFS-based scheduling algorithm may degrade the system performance and unfairly slow down applications for some workloads. Therefore, a set of scheduling algorithms is proposed to improve both the system performance and fairness perspectives. Various static priority techniques that require preliminary information about the applications and dynamic priority techniques that target to equalize the total time spent of applications on the protected core(s) are presented as part of this thesis. Extensive evaluations using multi-application workloads validate significant improvements of proposed scheduling techniques on system performance and fairness over the FCFS algorithm.

### ÖZET

# ÇOK ÇEKİRDEKLİ MİMARİLERE YÖNELİK PERFORMANS VE MALİYET ETKİN GÜVENİLİRLİK SİSTEMİ

Modern mimariler gelişen teknoloji ile geçici hatalara karşı daha savunmasız hale gelmiştir. Bir sistemdeki tüm önbellek yapılarını seçici olmaksızın korumak, performans ve enerji tüketimi açısından önemli bir ek yük getirir. Bu tez kapsamında performans ve güç tüketimi kısıtları altında asimetrik olarak güvenilir önbelleklere sahip çok çekirdekli bir sistem kullanılarak, yalnızca güvenilirlik açısından kritik olan kod parçalarını koruyan bir mekanizma önerilmiştir. Önerilen sistemimiz L1 önbellek yapılarında ECC korumasına sahip en az bir yüksek güvenilirlikli çekirdek ve önbellek yapılarında koruma bulunmayan birden fazla düşük güvenilirlikli çekirdeklerden oluşmaktadır. Bu tez kapsamında, güvenilirlik temelli kritik kod bölümleri, kritik veri kullanımı, kullanıcı ek açıklamaları ve statik analiz temel alınarak farklı yöntemlerle belirlenmiştir. İlk yaklaşımımızda, kritik kod bölümlerini çalıştıran uygulama iş parçacıkları First Come First Served (FCFS) tabanlı bir çizelgeleme algoritması ile dinamik olarak korunan çekirdeğe eşlenmiştir. Yapılan deneysel çalışma sonucunda, önerilen yaklaşımımız bir dizi uygulama için tamamen güvenilir sisteme yakın güvenilirlik ve performans sonuçları ile daha düşük güç tüketimi ve maliyet değerleri sunmuştur. Bununla birlikte FCFS tabanlı çizelgeleme algoritması bazı iş yükleri için düşük sistem performansı ve eşitlik sonuçlarına sahiptir. Bu tez kapsamında, sistem performansı ve eşitlik perspektiflerini iyileştirmek için, uygulamalar hakkında ön bilgi gerektiren önceliğe dayalı çizelgeleme teknikleri ve korunan çekirdek(ler) üzerindeki harcanan toplam süreyi eşitlemeyi hedefleyen dinamik çizelgeleme teknikleri sunulmuştur. Yapılan deneysel değerlendirme sonucunda, önerilen çizelgeleme tekniklerinin FCFS algoritmasına kıyasla sistem performansını ve eşitlik sonuçlarını önemli ölçüde iyileştirdiği gözlemlenmiştir.

## TABLE OF CONTENTS

| AC  | KNC  | WLED    | GEMENTS i                                       | iii            |

|-----|------|---------|-------------------------------------------------|----------------|

| AE  | BSTR | ACT .   | i                                               | iv             |

| ÖZ  | ΈT   |         |                                                 | v              |

| LIS | ST O | F FIGU  | IRES i                                          | ix             |

| LIS | ST O | F TABI  | LES                                             | iv             |

|     |      |         | BOLS                                            |                |

| LIS | ST O | F ACR   | ONYMS/ABBREVIATIONS                             | ii             |

| 1.  | INT  | RODUC   | CTION                                           | 1              |

|     | 1.1. | Thesis  | Contributions                                   | 3              |

|     | 1.2. |         |                                                 | 5              |

| 2.  | LITI | ERATU   | RE SURVEY                                       | 7              |

|     | 2.1. | Literat | ure Survey on Reliability                       | 7              |

|     | 2.2. | Literat | sure Survey on Scheduling Techniques            | 0              |

| 3.  | OUF  | R RELIA | ABILITY FRAMEWORK FOR MULTICORE ARCHITECTURES 1 | .4             |

| 4.  | ASY  | MMET    | RICALLY RELIABLE CACHES FOR CRITICAL DATA 1     | 17             |

|     | 4.1. | System  | with Single Type of Protected Core              | $\overline{7}$ |

|     |      | 4.1.1.  | Reliability-based Critical Data                 | $\overline{7}$ |

|     |      | 4.1.2.  | Architecture Model                              | 9              |

|     |      | 4.1.3.  | Execution Model                                 | 9              |

|     |      | 4.1.4.  | Cache Protection Scheme                         | 20             |

|     |      | 4.1.5.  | Experimental Study                              | 22             |

|     |      |         | 4.1.5.1. Simulation Platform                    | 22             |

|     |      |         | 4.1.5.2. Applications                           | 27             |

|     |      |         | 4.1.5.3. Fault Injection Model                  | 29             |

|     |      |         | 4.1.5.4. Performance and Energy Consumption     | 80             |

|     |      |         | 4.1.5.5. Experimental Results                   | 32             |

|     | 4.2. | System  | with Two Types of Protected Cores               | 87             |

|     |      | 4.2.1.  | Architecture and Execution Model                | 88             |

|     |      | 4.2.2.  | Applications                                    | 10             |

| 4.2.3. Experimental Study                                                                            | 40 |

|------------------------------------------------------------------------------------------------------|----|

| 4.2.3.1. Experimental Results Using Single Type of Protected                                         |    |

| Cores                                                                                                | 41 |

| 4.2.3.2. Experimental Results Using Different Types of Pro-                                          |    |

| tected Cores                                                                                         | 45 |

| 4.2.3.3. Analysis of Fault Injection Experiments                                                     | 49 |

| 4.3. Summary                                                                                         | 52 |

| 5. ASYMMETRICALLY RELIABLE CACHES FOR CRITICAL REGIONS .                                             | 54 |

| 5.1. Code Criticality Based on Annotations                                                           | 54 |

| 5.1.1. Architecture Model                                                                            | 55 |

| 5.1.2. Execution Model                                                                               | 55 |

| 5.1.3. Experimental Study                                                                            | 57 |

| 5.1.3.1. Experimental Setup                                                                          | 57 |

| 5.1.3.2. Applications                                                                                | 58 |

| 5.1.3.3. Experimental Results                                                                        | 60 |

| 5.2. Code Criticality Based on Static Analysis                                                       | 66 |

| 5.2.1. Determining Function Priorities                                                               | 67 |

| 5.2.2. Experimental Study                                                                            | 70 |

| 5.2.2.1. Applications                                                                                | 70 |

| 5.2.2.2. Experimental Results                                                                        | 73 |

| 5.3. Summary                                                                                         | 85 |

| 6. SCHEDULING OPPORTUNITIES FOR OUR FRAMEWORK                                                        | 87 |

| 6.1. Shortcomings of FCFS Scheduling                                                                 | 87 |

| 6.2. Determining Function Priorities                                                                 | 88 |

| 6.3. Different Scheduling Techniques                                                                 | 89 |

| 6.3.1. Priority-based Scheduling                                                                     | 90 |

| $6.3.1.1. Priority-ldf \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 91 |

| 6.3.1.2. Priority-missRate                                                                           | 91 |

| 6.3.1.3. Priority-min-reqs                                                                           | 91 |

| 6.3.1.4. Priority-max-reqs                                                                           | 92 |

| 6.3.1.5. Priority-min-burst                                                                          | 92 |

|       |           | 6.3.1.6. | Priority-max-burst                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------|-----------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | 6.3.2.    | Equal-ti | me Scheduling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|       | 6.3.3.    | Equal-p  | cogress Scheduling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|       | 6.3.4.    | Thresho  | ld-based Priority Scheduling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 6.4   | 4. Metho  | odology  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|       | 6.4.1.    | Applicat | $for s \dots for s \dots for s \dots for s \dots for s \dots for s \dots for s \dots for s \dots for s \dots for s \dots for s \dots for s \dots for s \dots for s \dots for s \dots for s \dots for s \dots for s \dots for s \dots for s \dots for s \dots for s \dots for s \dots for s \dots for s \dots for s \dots for s \dots for s \dots for s \dots for s \dots for s \dots for s \dots for s \dots for s \dots for s \dots for s \dots for s \dots for s \dots for s \dots for s \dots for s \dots for s \dots for s \dots for s \dots for s \dots for s \dots for s \dots for s \dots for s \dots for s \dots for s \dots for s \dots for s \dots for s \dots for s \dots for s \dots for s \dots for s \dots for s \dots for s \dots for s \dots for s \dots for s \dots for s \dots for s \dots for s \dots for s \dots for s \dots for s \dots for s \dots for s \dots for s \dots for s \dots for s \dots for s \dots for s \dots for s \dots for s \dots for s \dots for s \dots for s \dots for s \dots for s \dots for s \dots for s \dots for s \dots for s \dots for s \dots for s \dots for s \dots for s \dots for s \dots for s \dots for s \dots for s \dots for s \dots for s \dots for s \dots for s \dots for s \dots for s \dots for s \dots for s \dots for s \dots for s \dots for s \dots for s \dots for s n n n n n n n n n n n n n n n n n n $ |

|       | 6.4.2.    | Multi-th | readed Workloads                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|       | 6.4.3.    | Evaluati | on Metrics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 6.5   | 5. Evalua | ation    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|       | 6.5.1.    | Experim  | ental Setup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|       | 6.5.2.    | Experim  | ental Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

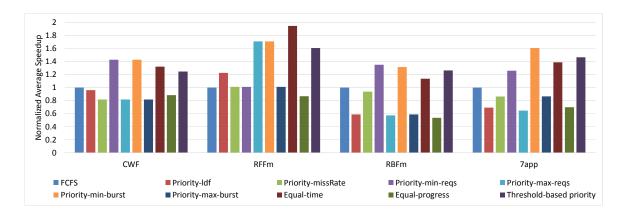

|       |           | 6.5.2.1. | Comparison of Average Speedup Metric 103                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

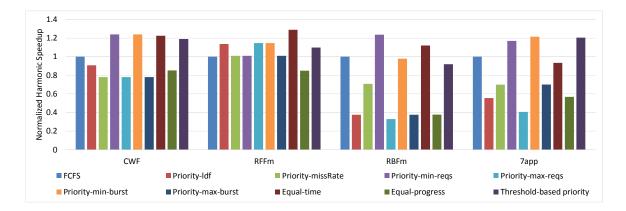

|       |           | 6.5.2.2. | Comparison of Harmonic Speedup Metric 106                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|       |           | 6.5.2.3. | Comparison of Fairness Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|       |           | 6.5.2.4. | Experiments with Different Numbers of Protected Cores 110                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|       |           | 6.5.2.5. | Detailed Analysis Based on 7-application Workload 113                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|       |           | 6.5.2.6. | Discussions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 6.0   | 6. Summ   | ary      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 7. CO | ONCLUS    | IONS AN  | D FUTURE WORK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| REFE  | ERENCES   | 5        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

## LIST OF FIGURES

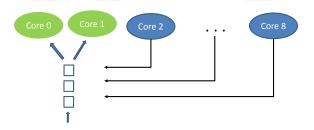

| Figure 3.1.  | Proposed framework.                                                                                                 | 15 |

|--------------|---------------------------------------------------------------------------------------------------------------------|----|

| Figure 4.1.  | An output of a fault injection experiment.                                                                          | 18 |

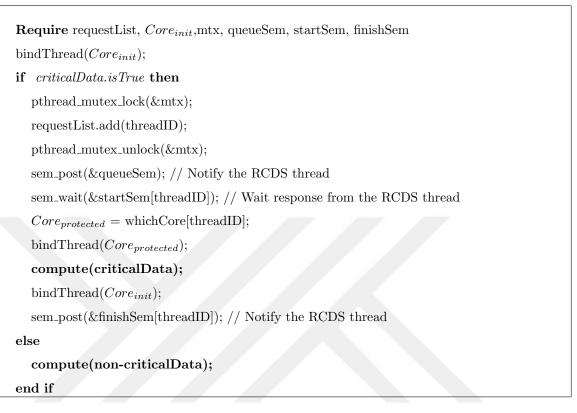

| Figure 4.2.  | Application thread.                                                                                                 | 21 |

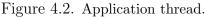

| Figure 4.3.  | RCDS on a high reliability core.                                                                                    | 21 |

| Figure 4.4.  | Coding phase of the SECDED [70]                                                                                     | 23 |

| Figure 4.5.  | Decoding phase of the SECDED [70]                                                                                   | 24 |

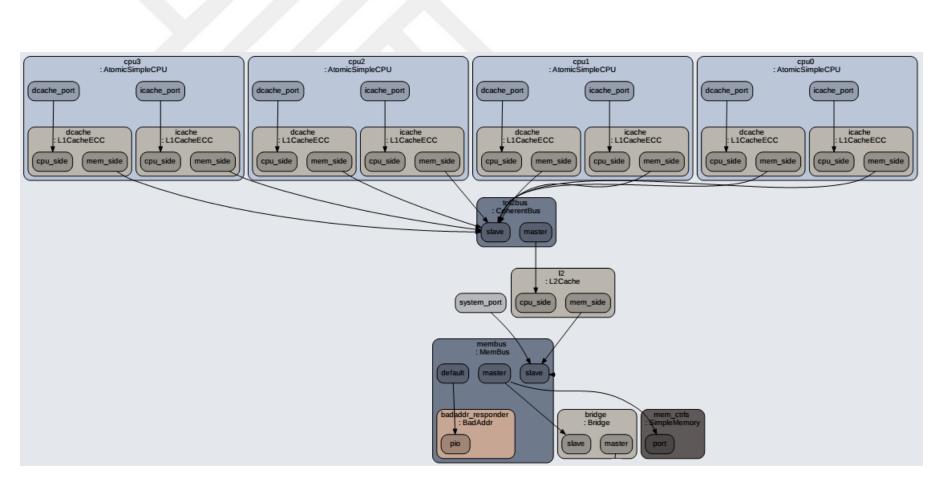

| Figure 4.6.  | The visualization of the simulated system [72]                                                                      | 26 |

| Figure 4.7.  | Blocked Dense LU Factorization [75]                                                                                 | 28 |

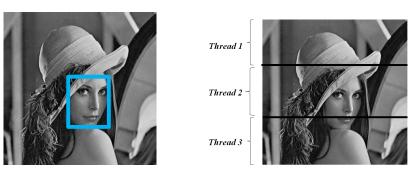

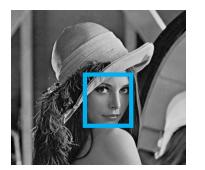

| Figure 4.8.  | Susan application with Lena image                                                                                   | 29 |

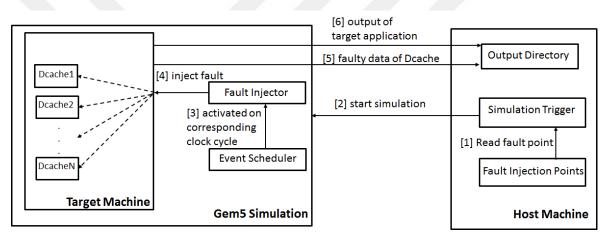

| Figure 4.9.  | Fault injection model in our framework where numbers on the arrows represent order of operations for an experiment. | 30 |

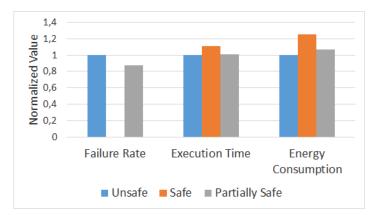

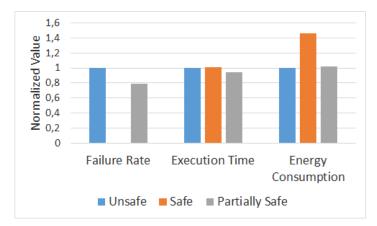

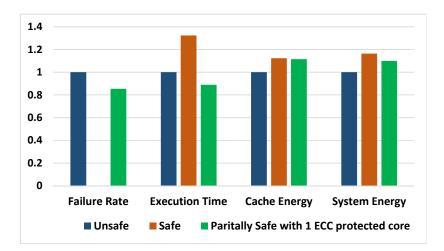

| Figure 4.10. | Normalized values of failure rate, execution time and energy con-<br>sumption for the LU application.               | 34 |

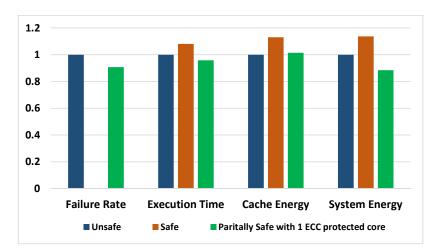

| Figure 4.11. | Normalized values of failure rate, execution time and energy con-<br>sumption for the Susan smoothing application.  | 36 |

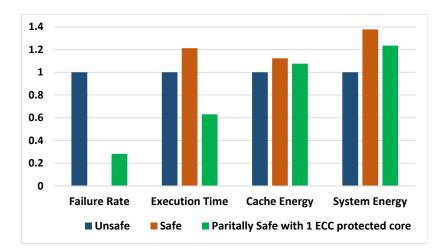

| Figure 4.12. | Normalized values of failure rate, execution time and energy con-<br>sumption for the Susan corners application                        | 37 |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------|----|

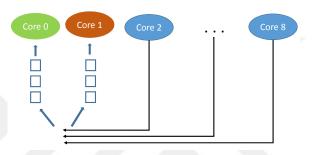

| Figure 4.13. | Different types of partially safe configuration                                                                                        | 39 |

| Figure 4.14. | Critical data on the Lena image                                                                                                        | 41 |

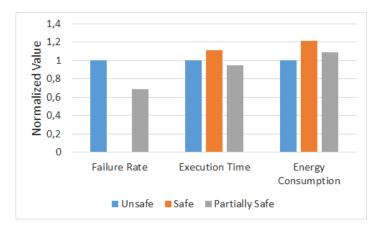

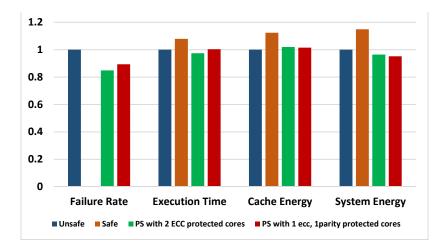

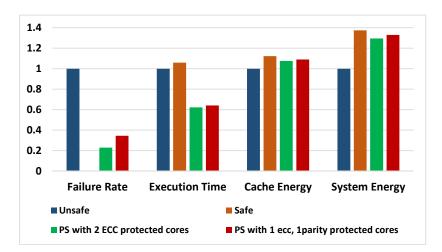

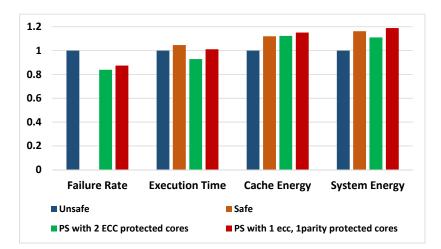

| Figure 4.15. | Normalized values of failure rate, execution time and energy con-<br>sumptions for the LU application in an 8-core system.             | 43 |

| Figure 4.16. | Normalized values of failure rate, execution time and energy con-<br>sumption for the Susan smoothing application in an 8-core system. | 44 |

| Figure 4.17. | Normalized values of failure rate, execution time and energy con-<br>sumption for the Susan corners application in an 8-core system.   | 45 |

| Figure 4.18. | Normalized values of failure rate, execution time and energy con-<br>sumptions for the LU application in a 9-core system               | 46 |

| Figure 4.19. | Normalized values of failure rate, execution time and energy con-<br>sumptions for the Susan smoothing application in a 9-core system. | 47 |

| Figure 4.20. | Normalized values of failure rate, execution time and energy con-<br>sumptions for the Susan corners application in a 9-core system    | 49 |

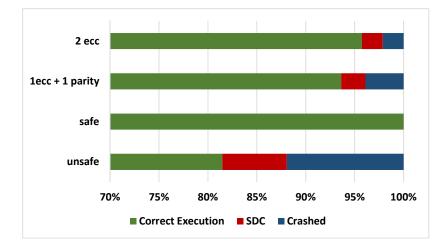

| Figure 4.21. | Results of fault injection experiments for the Susan smoothing application.                                                            | 51 |

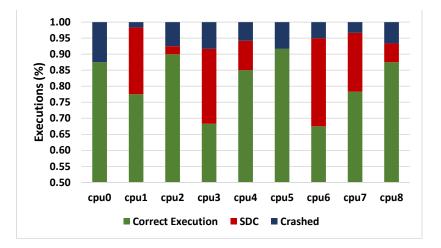

| Figure 4.22. | Application behavior when injecting faults to different cores for the Susan smoothing application in the unsafe configuration.         | 52 |

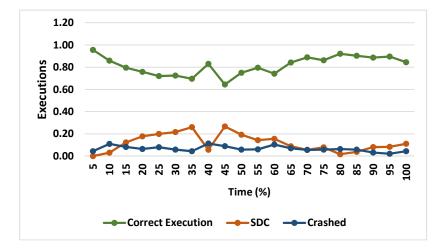

| Figure 4.23. | Correlation of fault injection timing with the Susan smoothing application execution.                                                                   | 53 |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|----|

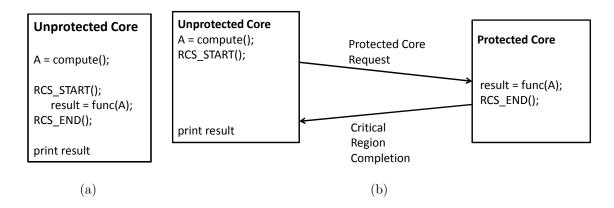

| Figure 5.1.  | Source code and its execution.                                                                                                                          | 55 |

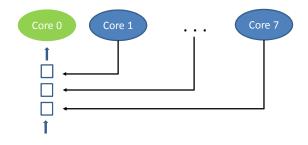

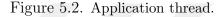

| Figure 5.2.  | Application thread.                                                                                                                                     | 56 |

| Figure 5.3.  | Queue thread on a protected core.                                                                                                                       | 56 |

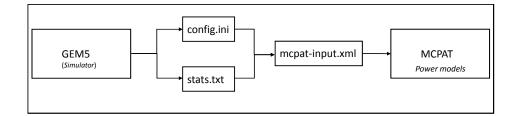

| Figure 5.4.  | Execution flow of the simulation                                                                                                                        | 58 |

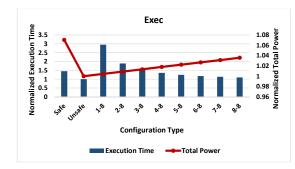

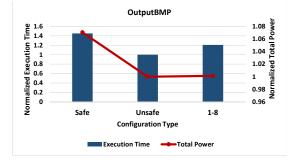

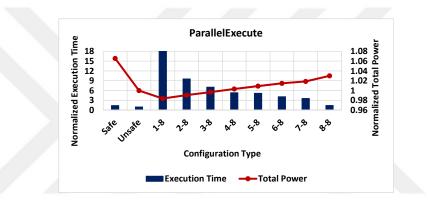

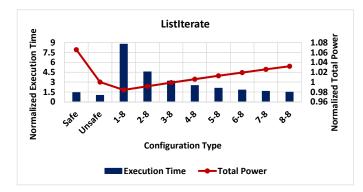

| Figure 5.5.  | Normalized values of execution time and power consumption for<br>the Bodytrack application. (x-8) configuration: x protected and 8<br>unprotected cores | 63 |

| Figure 5.6.  | Fault injection experiment results of the Bodytrack application                                                                                         | 64 |

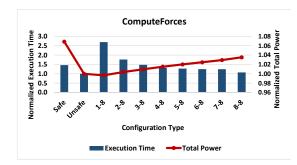

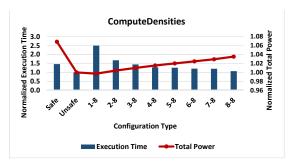

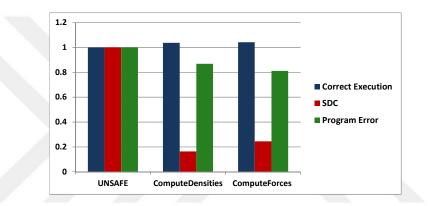

| Figure 5.7.  | Normalized values of execution time, power and reliability results<br>for the Fluidanimate application.                                                 | 65 |

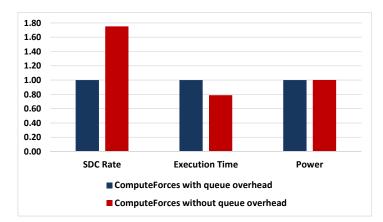

| Figure 5.8.  | Effect of queue waiting with ComputeForces function                                                                                                     | 66 |

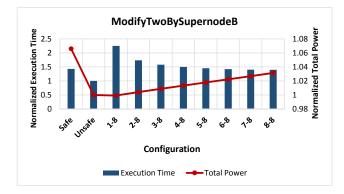

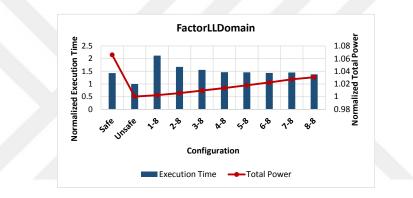

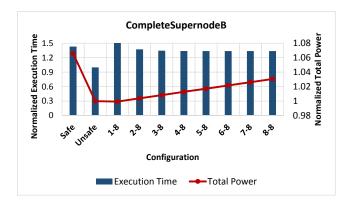

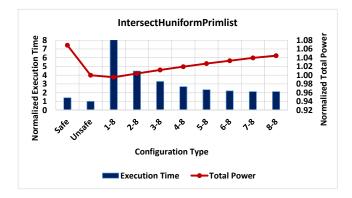

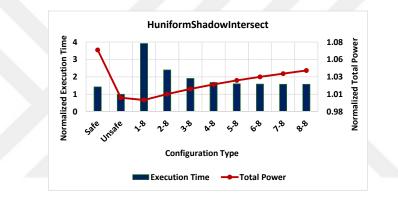

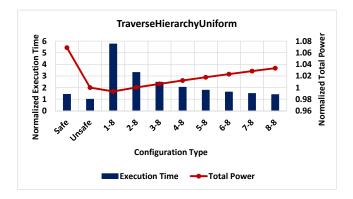

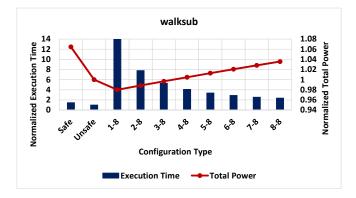

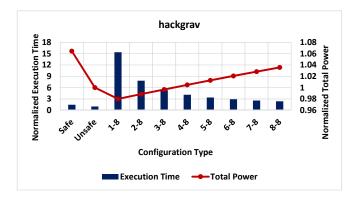

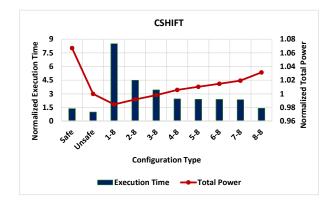

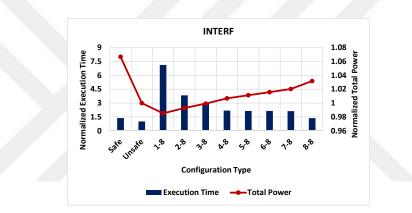

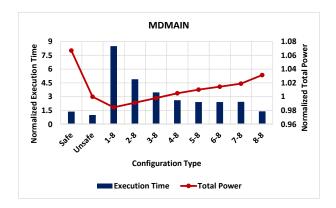

| Figure 5.9.  | Normalized values of execution time and power consumption for<br>the Cholesky application. (x-8) configuration: x protected and 8<br>unprotected cores  | 74 |

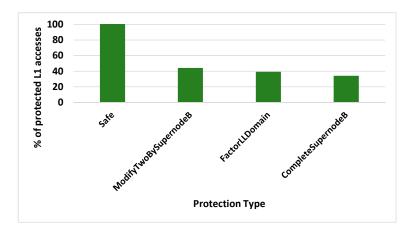

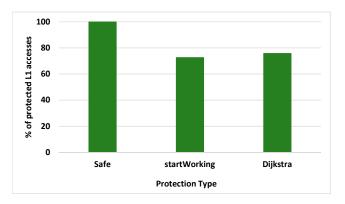

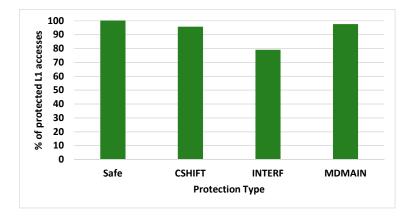

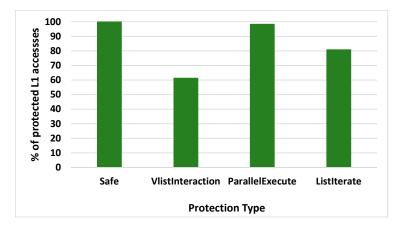

| Figure 5.10. | Percentage of protected L1 accesses for the Cholesky application                                                                                        | 75 |

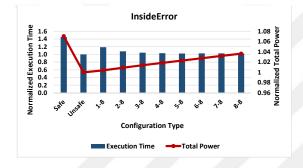

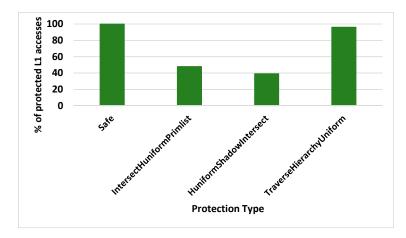

| Figure 5.11. | Normalized values of execution time and power consumption for<br>the Raytrace application                                                               | 76 |

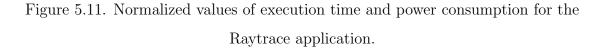

| Figure 5.12. | Percentage of protected L1 accesses for the Ray<br>trace application                             | 77 |

|--------------|--------------------------------------------------------------------------------------------------|----|

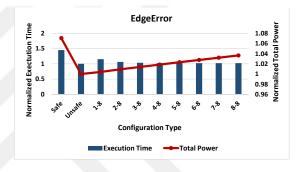

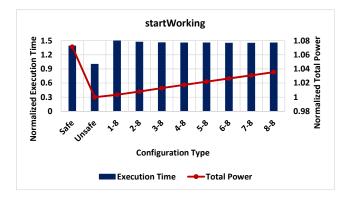

| Figure 5.13. | Normalized values of execution time and power consumption for<br>the Dijkstra application.       | 78 |

| Figure 5.14. | Normalized values of execution time and power consumption for<br>the Barnes application.         | 79 |

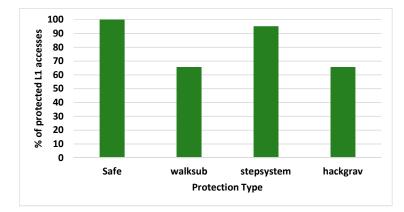

| Figure 5.15. | Percentage of protected L1 accesses for the Barnes application                                   | 81 |

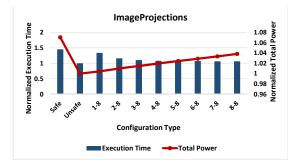

| Figure 5.16. | Normalized values of execution time and power consumption for<br>the Water-nsquared application. | 82 |

| Figure 5.17. | Percentage of protected L1 accesses for the Water-nsquared appli-<br>cation.                     | 83 |

| Figure 5.18. | Normalized values of execution time and power consumption for<br>the fmm application.            | 84 |

| Figure 5.19. | Percentage of protected L1 accesses for the fmm application                                      | 85 |

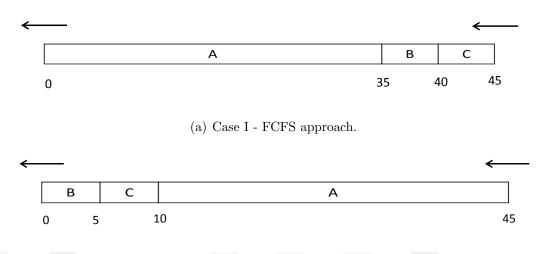

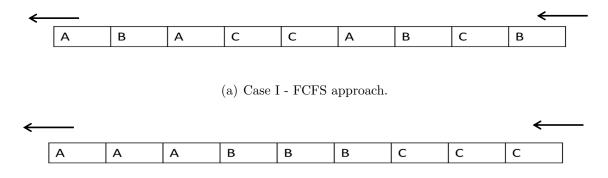

| Figure 6.1.  | Order of applications at the queue with the FCFS and SJF based scheduling techniques             | 88 |

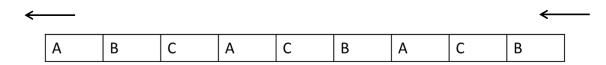

| Figure 6.2.  | Snapshot of the queue with the FCFS and priority-based scheduling techniques.                    | 91 |

| Figure 6.3.  | Snapshot of the queue with the equal-time scheduling                                             | 94 |

| Figure 6.4.  | Snapshot of the queue with the threshold-based priority scheduling.                              | 97 |

| Figure 6.5.  | Average speedup results                                                                                                                                      | 105 |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

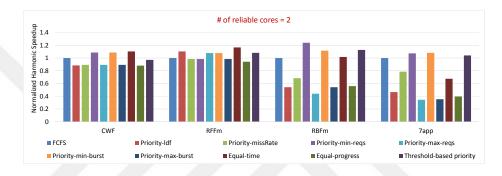

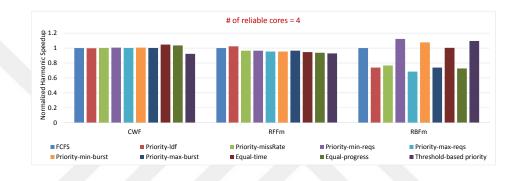

| Figure 6.6.  | Harmonic speedup results                                                                                                                                     | 107 |

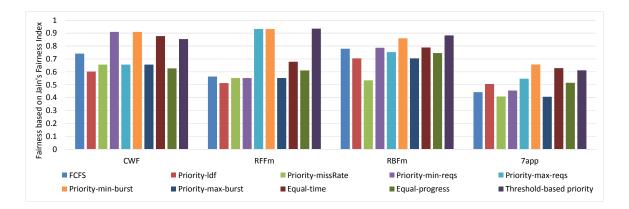

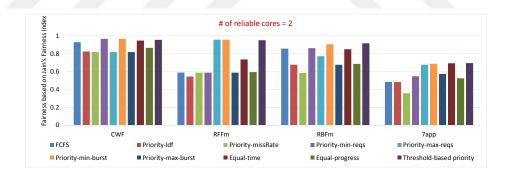

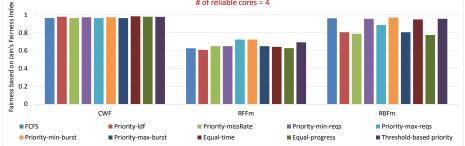

| Figure 6.7.  | Fairness results based on Jain's fairness index                                                                                                              | 108 |

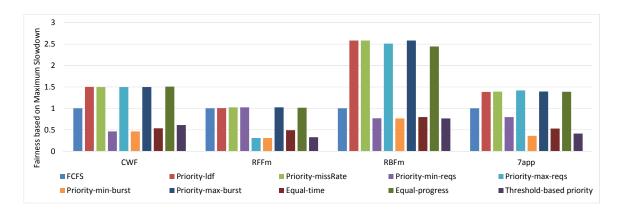

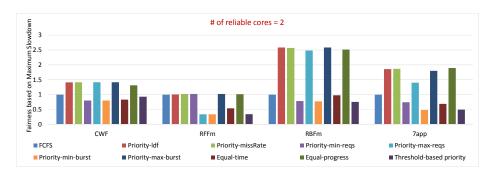

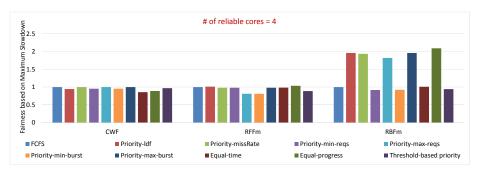

| Figure 6.8.  | Fairness results based on maximum slowdown                                                                                                                   | 109 |

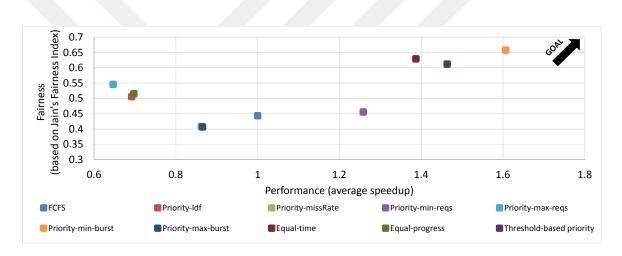

| Figure 6.9.  | Pareto plot of performance and fairness for the 7-application work-<br>load                                                                                  | 109 |

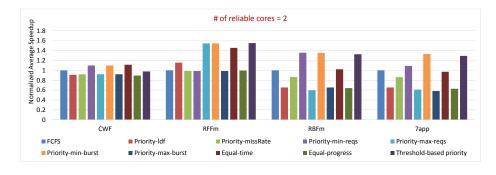

| Figure 6.10. | Results of different workloads for the system with two protected cores                                                                                       | 111 |

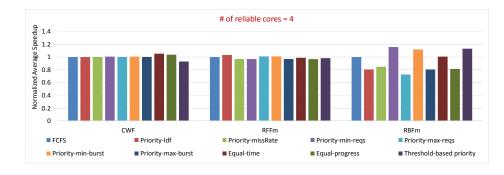

| Figure 6.11. | Results of different workloads for the system with four protected cores                                                                                      | 112 |

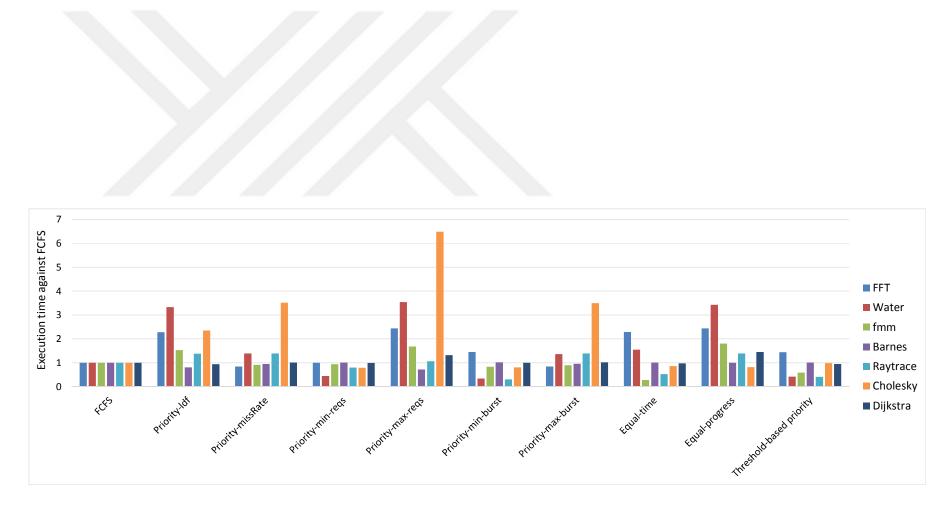

| Figure 6.12. | Execution time differences of applications against FCFS                                                                                                      | 114 |

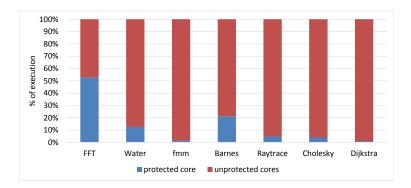

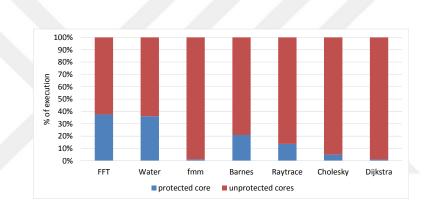

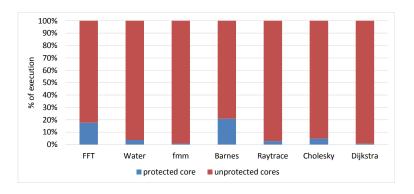

| Figure 6.13. | Execution time distributions of the applications in 7-application<br>workload on the protected and unprotected cores with different<br>scheduling techniques | 116 |

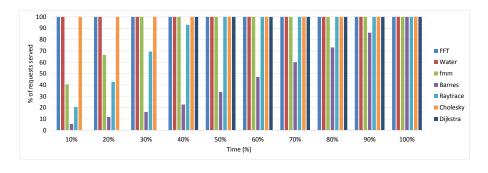

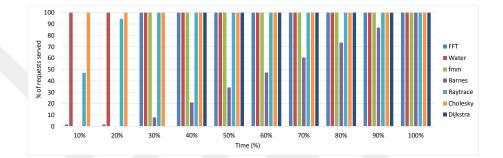

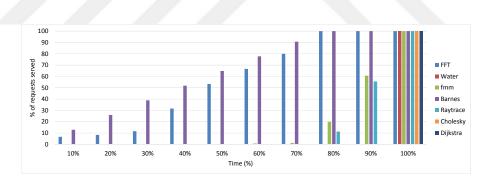

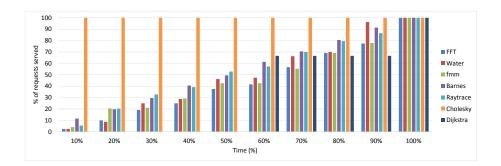

| Figure 6.14. | Percentage of application requests served over time for the 7-applicati<br>workload under different scheduling techniques                                    |     |

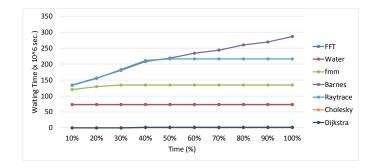

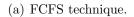

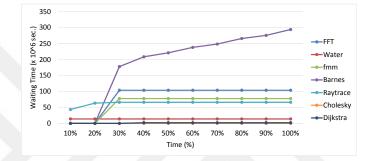

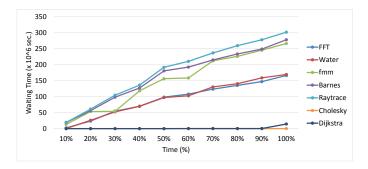

| Figure 6.15. | Waiting time of the applications for the 7-application workload in<br>the queue with different scheduling techniques                                         | 119 |

## LIST OF TABLES

| Table 4.1. | Gem5 simulator parameters.                                                                                                                                  | 25 |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Table 4.2. | Instruction counts and cache accesses of each data cache for the LU application.                                                                            | 33 |

| Table 4.3. | Average reliability, performance and energy consumption values for<br>different cache configurations of 800 fault injection tests for the LU<br>application | 33 |

| Table 4.4. | Average reliability, performance and energy values for different cache configurations of 800 fault injection tests for the Susan smoothing application.     | 35 |

| Table 4.5. | Average reliability, performance and energy values for different cache<br>configurations of 800 fault injection tests for the Susan corners application.    | 36 |

| Table 4.6. | Instruction counts and cache accesses of each data cache for the LU application in an 8-core system.                                                        | 42 |

| Table 4.7. | Total number of instruction counts and cache accesses for the Susan smoothing application in a 9-core system.                                               | 48 |

| Table 4.8. | Total number of instruction counts and cache accesses for the Susan corners application in a 9-core system.                                                 | 50 |

| Table 5.1. | Gem5 simulator parameters.                                                                                                                                  | 57 |

| Table 5.2. | Applications that could not be selected                                                                                                                     | 59 |

| Table 5.3. | Application functions, percentage of execution time, and total num- |     |

|------------|---------------------------------------------------------------------|-----|

|            | ber of calls for each function                                      | 60  |

| Table 5.4. | Profiling results of six applications                               | 72  |

| Table 6.1. | Profiling results of seven applications.                            | 99  |

| Table 6.2. | Number of requests of each application for the protected core(s).   | 101 |

## LIST OF SYMBOLS

| AS                | Average speedup                                                  |

|-------------------|------------------------------------------------------------------|

| $criticality_i$   | Criticality value of function $i$                                |

| $E_{bus}$         | Energy value for off-chip bus                                    |

| $E_{cod}$         | ECC encoder energy                                               |

| $E_{dec}$         | ECC decoder energy                                               |

| $E_{mem}$         | Memory access energy                                             |

| $E_{proc}$        | Processor energy                                                 |

| Eread             | Energy value of read access                                      |

| $E_{readECCoff}$  | Energy values of the read accesses for the unprotected cache     |

| $E_{readECCon}$   | Energy values of the read accesses for the protected cache       |

| $ET_i$            | Execution time of function $i$                                   |

| Ewrite            | Energy value of write access                                     |

| $fixity_i$        | Fixity value of function $i$                                     |

| HS                | Harmonic speedup                                                 |

| $M_i$             | Number of misses for cache $i$                                   |

| $M_{protected}$   | Number of misses for the protected cache                         |

| $N_{protected}$   | Number of cache accesses for the protected cache                 |

| $Nread_i$         | Number of read accesses for cache $i$                            |

| $N_{unprotected}$ | Number of cache accesses for the unprotected cache               |

| $Nwrite_i$        | Number of write accesses for cache $i$                           |

| $OutDegree_i$     | Number of callee functions in function $i$                       |

| $priority_i$      | Priority value of function $i$                                   |

| $R_{protected}$   | Number of replacements for the protected cache                   |

| $slack_i$         | Slack value of function $i$                                      |

| $T_i(alone)$      | Execution time of the application $i$ with no scheduler          |

| $T_i(approach)$   | Execution time of the application $i$ with the proposed schedul- |

|                   | ing technique                                                    |

| $T_i(baseline)$   | Execution time of the application $i$ with the FCFS technique    |

| $vulnerability_i$ | Vulnerability value of function $i$                              |

$W_{protected}$  Number of write accesses for the protected cache

$\alpha$

Weight of the vulnerability metric on the criticality metric

# LIST OF ACRONYMS/ABBREVIATIONS

| AFCFS  | Adapted First Come First Served                    |

|--------|----------------------------------------------------|

| CFS    | Completely Fair Scheduler                          |

| DFT    | Discrete Fourier Transform                         |

| DVFS   | Dynamic Voltage and Frequency Scaling              |

| ECC    | Error Correcting Codes                             |

| EDC    | Error Detection Codes                              |

| EPET   | Earliest Possible Execution Time                   |

| EST    | Earliest Start Time                                |

| FCFS   | First Come First Served                            |

| FFM    | Fast Multipole Method                              |

| FFT    | Fast Fourier Transform                             |

| IPC    | Instruction per Cycle                              |

| LGFS   | Largest Gang First Served                          |

| LST    | Latest Start Time                                  |

| LTF    | Largest Task First                                 |

| RCS    | Reliability-based Critical Section                 |

| RCSS   | Reliability-based Critical Section Scheduler       |

| SDR    | Silent Data Corruption                             |

| SECDED | Single Error Correction and Double Error Detection |

| TMR    | Triple Modular Redundancy                          |

| TVF    | Thread Vulnerability Factor                        |

|        |                                                    |

### 1. INTRODUCTION

Modern architectures are progressively vulnerable to transient and permanent errors because of persistent decrease on transistor sizes, high transistor density per chip, and high operating frequencies [1,2]. The impact of such errors can be quite varied and dramatic depending on the target application domain. For instance, in a safety-critical application (e.g., a program that controls a nuclear plant or a missile), results of even a single transient error can be catastrophic. On the other hand, in a molecular dynamics application with self-correcting capability (e.g., one that uses iterative solvers), an error can notably increase the running time of the program, in spite of the fact that the program may still finish successfully. Based on above observations, reliability (fault tolerance) should be considered as a fundamental and first-class metric in hardware and software designs.

Previous studies explore the fault tolerance strategies in different layers of hardware and software. A certain level of success is accomplished by those efforts in predicting and mitigating hardware faults. Hardware-only approaches for reliability improvement lacks of application-level information. As a result, all memory accesses must be protected as they have the same criticality level (which is clearly not the case in reality). Because of this conservative situation, the provided reliability has overheads of cost, performance and power consumption. On the other hand, software-only approaches are not aware of the runtime information to enable making ideal protection decisions, dynamically.

A temporary condition in a semiconductor device may alter the stored data in memory, which results in a soft error [3]. This sort of error randomly occurs and may modify the data or terminate the execution of a target program. Alpha particles, low energy particles from the packaging material, and high energy particles from the cosmic rays are the main causes of this type of error [2]. Having large area of the logic relative to other parts of the chip [1,4] and high transistor density [5] makes cache structures more vulnerable to soft errors. Utilizing Error Correction Codes (ECC) is a general method to ensure protected cache memories. However, applying ECC protection in all cache structures may result in significant overheads in terms of area, power, and cost [2].

The multicore architectures with the unprecedented levels of transistors will require more appropriate measures to be taken for the reliability problem. In the light of the observations specified, we propose a performance and cost efficient reliability framework aiming to maximize the reliability with using minimum reliability hardware under the performance, power and cost constraints. In our proposed framework, instead of protecting all data uniformly at the same level of reliability, we can determine the Reliability-based Critical Sections (RCS) which specifies the portions of the program that should be protected. Then, these portions are preserved more conservatively than the remaining parts.

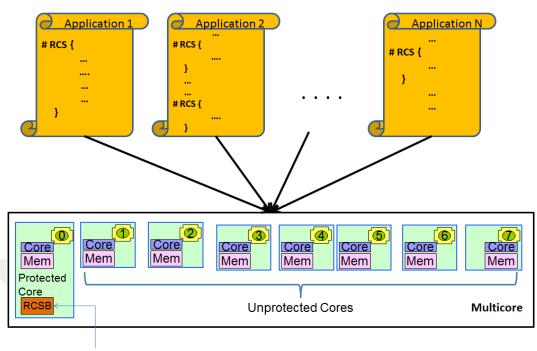

We consider an asymmetric chip multiprocessor (or heterogeneous chip multiprocessor) consisting of at least one reliability-aware core and a set of less reliable cores. While the protected core(s) use most of the chip area by containing larger amount of fault-tolerant logic and components, the unprotected cores do not provide any protection mechanisms. An efficient way to achieve higher hardware reliability is to utilize protected core(s) for the Reliability-based Critical Sections and to map the less-critical parts of the program on the remaining unprotected cores. By using asymmetrically reliable cores we can provide maximum reliability enhancement using minimum reliability hardware. In our framework, the protected core is not reserved for a particular application or thread, and the application threads can visit the high reliability cores at runtime according to their critical sections of code. Therefore, an efficient scheduling method is required to dynamically map application threads to the protected cores. We started with a primitive scheduling technique based on First Come First Served (FCFS) policy. Then, alternative scheduling techniques with different characteristics are implemented and evaluated in terms of system performance and fairness.

### 1.1. Thesis Contributions

This thesis proposes an enhanced protection mechanism for the Reliability-based Critical Sections of the given program by utilizing an asymmetric chip multiprocessors containing cores with different protection levels. The contributions of the thesis can be listed in three categories:

Proposing Asymmetrically Reliable Caches for Critical Data [6,7]:

- We propose two different heterogeneous chip multiprocessors in this part. In the first approach, a chip multiprocessor which has one high reliability and a set of low reliability cores is proposed. While ECC protection is applied on individual L1 cache structure of the high reliability core, there is no cache protection mechanism for the less reliable cores. An application input is analyzed statically a priori, and a portion of the input is determined as critical data specifically for the given application. The code fragments that access critical data are determined as the critical code fragments that need to be protected.

- In the second approach, we propose a chip multiprocessor which has one high reliability, one middle-level reliability and a set of low reliability cores. While ECC protection is applied on individual L1 cache structure of the high reliability core, parity check is utilized for the middle-level reliability core. An application input data is analyzed statically and classified as critical, semi-critical and non-critical. The applications can utilize high, medium-level or low reliability cores based on critical, semi-critical, and non-critical data.

- We present a framework which dynamically allocates application threads to asymmetrically reliable cores based on critical data usage for both cases. We present an FCFS-based scheduling method for the queue structure of the high reliability core.

- A simulation-based fault injection framework is implemented to perform a detailed experimental study on both proposed asymmetrically reliable caches and traditional caches.

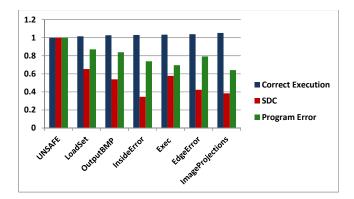

Experimental studies performed on applications with various characteristics validate the proposed framework for asymmetrically reliable caches. The partially safe cache configuration performs significantly better than the unsafe configuration with respect to reliability, and the safe configuration with respect to performance and energy consumption.

Proposing Asymmetrically Reliable Caches for Critical Code Regions [8,9]:

- We propose two different approaches to determine the reliability-based critical code regions of the applications. As a first approach, a programmer can annotate the reliability-based critical code regions of the application. Selected applications are profiled and the functions that cover 90% of total execution time (that might be three or four functions) are assumed as critical regions for each application. Then, each of these functions are protected using asymmetrically reliable caches.

- As a second approach, the critical code fragments are extracted by using static analysis. Each application is profiled, and the execution time percentages and the call graph of the functions are generated. Then, high-priority functions to be protected are determined with vulnerability and criticality analysis on the profiling results.

- For both cases, a comparative study is performed using different numbers of protected cores to show the efficiency of our framework by using a diverse set of applications from benchmarks. Our experimental evaluation shows that the proposed approach takes advantage of protecting only functions with higher priority and presents comparable performance and reliability results with fully protected systems, while providing lower power consumption and cost values for a set of functions.

Proposing Different Scheduling Techniques for Our Framework [10]:

• We propose different scheduling techniques with various characteristics to map application threads on the protected cores.

Six priority-based scheduling techniques are presented in which the applications are prioritized based on their execution order, cache miss rates, number of requests sent to the protected core(s), or total burst time spent on the protected core(s). These static priority techniques require executing the applications in advance to determine the priority-level of the applications.

- We propose two dynamic priority techniques: equal-time and equal-progress. The former one targets to equalize the amount of time for each application on the protected core(s) at every scheduling point whereas the latter one targets to equalize the progress of requests for each application on the protected core(s). Additionally, the priority-levels of the applications are updated dynamically at runtime in these techniques.

- We propose the threshold-based priority technique, which uses a static priority technique by considering last scheduled application.

- Evaluations with different workloads show that our priority-min-burst method that prioritizes the applications with low total burst time on the protected core(s) presents an average of 51.4% (up to 70.8%) better performance with respect to average speedup metric and an average of 36.7% (up to 65.4%) better fairness with respect to Jain's fairness index on a 16-core system with one protected core. On the other hand, our equal-time scheduling technique shows an average of 44.7% better performance with an average of 20.5% better fairness results relative to the FCFS algorithm. Overall, these results validate the usage of scheduling algorithms presented in this part for providing high performance and fairness values, in place of the FCFS algorithm.

#### 1.2. Outline of the Thesis

The remainder of this thesis is organized as follows. Chapter 2 presents a variety of studies proposed in the literature. We describe our framework in general in Chapter 3. Chapter 4 demonstrates the implementation and evaluation of the main mechanics of our proposed approach with critical data. In Chapter 5, we present our framework with asymmetrically reliable caches for critical code regions. Chapter 6 demonstrates the scheduling opportunities of our framework by providing nine different methods. We conclude the document by providing summary and directions for future work in Chapter 7.

### 2. LITERATURE SURVEY

We present a summary of related work in two subsections. Hardware-based, software-based and hybrid approaches for the reliability problem are summarized in the first subsection. It also includes a review on data and code criticality approaches. In the second part, various scheduling methods that are frequently used in the literature are explained.

### 2.1. Literature Survey on Reliability

Hardware-based and software-based reliability approaches have been extensively studied in the literature. Physical duplication of hardware units is a common method in hardware-based techniques [11]. Triple Modular Redundancy (TMR) is a well-known method of three identical pieces of hardware components are used [12]. With the evaluation of majority voting system, the majority of these results are considered as accurate and the system is continued to the operation with this outcome. In such a case, errors may occur in a part of the system without affecting the correct functioning of it. While such techniques use fault masking methods, there are studies dealing with error detection and error correction techniques. Error Correcting Codes (ECC) based techniques are widely deployed technology in the industry that are designed in different ways to protect on-chip memory and cache structures as well as communication links of NoC. Variable Strength Error Correcting Codes (VS-ECC) change ECC strength on different cache lines with online testing [13]. In another study, Hi-ECC provides protection at a coarse granularity by reducing the cost of strong ECC [14]. Virtualized ECC [15] provides adaptable memory protection by mapping ECC to areas that are noticed by software in memory. Memory mapped ECC [16] stores the error protection codes in main memory to decrease area overhead in last level caches.

Software-based techniques provide software-level solutions by putting additional instructions to the original program. Information, data, and time redundancy methods are widely used techniques in this level. Adaptive redundancy is provided to increase data reliability in shared caches [17]. In addition to full redundancy, partially protected cache is proposed, which ensures a few sections of the cache against soft errors [18]. Applying only data-intensive multimedia applications or considering of single-processor architectures are the fundamental limitations of those studies mentioned above. In various studies, operating system data structures are protected by software-based fault tolerance [19] and checkpoint recovery [20].

Cross-layer approaches that provide solutions at the architecture and application level for the reliability problem are also presented in the literature [21]. The Relax framework provides software level protection for hardware faults [22]. They extract vulnerable code regions as the functions that can be ignored within a program. If a hardware fault occurs while executing these regions, they are either re-executed or the results produced by these regions are ignored. A programming model, EnerJ, is presented by classifying application data as critical or approximate [23]. In this study, approximate data calculations are performed in low-energy, low reliable mode, while critical data calculations are performed in high-energy, high reliable mode.

A programming model, Rely, is presented in which the user can figure out reliability requirements in application level [24]. In this method, probabilistic hardware models are developed to meet the reliability requirements. The authors also proposed a system, Chisel, in which reliable data and operations can be determined automatically [25]. Additionally, a flexible architecture is presented using reliable processors to control algorithmic flow and unreliable processors to run slave tasks [26]. While this work requires rewriting the application source code, the overhead of using reliable processor can be decreased by using many parallel threads. Rehman *et al.* [27] propose a system using heterogeneous error recovery cores to select a task among various task alternatives, where vulnerable tasks are bound to the reliable cores while robust tasks are bound to the unreliable cores. They also provide a compiler-based solution that reduces the vulnerability of critical instructions on unreliable hardware [28]. Yetim *et al.* [29] propose a system that can convert the fatal errors in the inter-thread communication into application-level data errors. A model-driven method is also proposed for fault-tolerant embedded systems [30]. In this model, design space exploration methods are studied using application-level reliability requirements and hardware platform information.

Researchers have also examined asymmetric multicore architectures in the literature. An asymmetric architecture is proposed in which a high-performance core (called large core) is used to execute critical sections and low-performance cores (small cores) are used to execute other instructions [31]. Thus, the execution of the critical sections, which have to be executed in serial, is accelerated using a high-performance core and the thread waiting times are decreased by this approach.

Asymmetric multicore architectures are also studied in terms of reliability in the literature. A multicore system is proposed where different fault tolerant cores are used for different applications [32]. In this work, critical applications are executed on highreliability cores, while non-critical applications are executed on low-reliability cores. Application criticality is determined from the scratch and critical applications run on high-reliability cores until the end of the execution. Heterogeneous-reliable memory implementations are also proposed in the literature [33]. In this study, application data are classified in two groups referred to as less vulnerable and more vulnerable data. While more vulnerable data are stored in protected memory, less vulnerable data are stored in unprotected memory. This study has been proposed to reduce the memory cost of the servers.

There are various studies in the literature regarding the determination of critical code regions in applications. Burtscher *et al.* [34] assume that the code regions that have higher execution time percentages are more critical than the other parts. Subotic *et al.* [35] claim that the code regions that could be improved with performance optimizations and those that have maximum speed up in the case of optimizations are selected as the most significant regions. Carbin *et al.* [36] extract critical and non-critical code regions by utilizing flexible input fuzzing methods in which different inputs are given to the program and critical regions are determined depending on the program path. Duque *et al.* [37] propose a system that can perform an application-specific criticality measurement using static task graphs.

There are significant differences between the studies presented in this section and the system we have proposed. In our proposed system, a high reliability core is not reserved for a particular application or thread. Various threads can use high reliability core(s) at runtime. Therefore, dynamic allocation of application threads and a scheduling technique are required in our work. On the other hand, protection techniques are applied to the individual cache structures of the cores, rather than the external storage as in the studies above. Furthermore, critical code regions are determined in several ways using real applications, rather than using ready task graphs.

#### 2.2. Literature Survey on Scheduling Techniques

Scheduling is a very popular research area in the literature where a large number of policies have been implemented based on various perspectives. Scheduling techniques are studied as part of the reliability-based research in the literature [37–42]. Duque et al. [37] propose a reliability-aware task scheduling that uses several metrics such as core reliability, task vulnerability, and task criticality. In this study, time-correlated fault behavior of the applications are modeled and different priorities are given to different tasks. The task vulnerability metric is defined as affecting the task outcome of a possible error. A task criticality metric is defined as the effect of a possible error on the execution time of the application. The task vulnerability and task criticality metrics are calculated based on the task graph information. Using these metrics, the runtime scheduler assigns more vulnerable and critical tasks to the more reliable cores, dynamically. In this study, ready task graphs are used rather than real applications. The authors propose a static reliability-aware scheduling technique in another study [38]. The aim of this work is again to assign more critical and vulnerable tasks to more reliable cores. In the event of a possible error, it is assumed that the faulty task will be re-executed. Then, the level of reliability is defined as the expected increase in execution time in case of a possible error. In this study, List scheduling, which consists of a task prioritization and a core assignment stages are used.