## ISTANBUL TECHNICAL UNIVERSITY ★ GRADUATE SCHOOL OF SCIENCE ENGINEERING AND TECHNOLOGY

### A 14-BIT 100-kHZ CONTINUOUS-TIME DELTA-SIGMA ANALOG-TO-DIGITAL CONVERTER FOR HALL EFFECT BASED CURRENT SENSOR APPLICATION

M.Sc. THESIS Alper GİRGİN

**Department of Electronics and Communication Engineering**

**Electronics Engineering Programme**

December 2017

## ISTANBUL TECHNICAL UNIVERSITY ★ GRADUATE SCHOOL OF SCIENCE ENGINEERING AND TECHNOLOGY

### A 14-BIT 100-kHZ CONTINUOUS-TIME DELTA-SIGMA ANALOG-TO-DIGITAL CONVERTER FOR HALL EFFECT BASED CURRENT SENSOR APPLICATION

**M.Sc. THESIS**

Alper GIRGIN (504141202)

**Department of Electronics and Communication Engineering**

**Electronics Engineering Programme**

Thesis Advisor: Assist. Prof. Dr. Tufan Coşkun KARALAR

December 2017

# <u>ISTANBUL TEKNİK ÜNİVERSİTESİ ★ FEN BİLİMLERİ ENSTİTÜSÜ</u>

## HALL ETKİSİ BAZLI AKIM SENSÖRÜ UYGULAMASI İÇİN 14-BİT 100-kHz SÜREKLİ ZAMANLI DELTA-SİGMA ANALOG DİJİTAL ÇEVİRİCİ

YÜKSEK LİSANS TEZİ

Alper GİRGİN (504141202)

Elektronik ve Haberleşme Anabilim Dalı

Elektronik Mühendisliği Programı

Tez Danışmanı: Yard. Doç. Dr. Tufan Coşkun KARALAR

Aralık 2017

Alper Girgin, a M.Sc student of ITU Graduate School of Science Engineering and Technology student ID 504141202, successfully defended the thesis entitled "A 14-Bit 100-kHZ Continuous-Time Delta-Sigma Analog-to-Digital Converter for Hall Effect Based Current Sensor Application", which he prepared after fulfilling the requirements specified in the associated legislations, before the jury whose signatures are below.

| Thesis Advisor : | Assist.Prof. Dr. Tufan Coşkun KARALAR<br>ISTANBUL Technical University  |  |

|------------------|-------------------------------------------------------------------------|--|

| Jury Members :   | Assist. Prof. Dr. Mustafa Berke YELTEN<br>ISTANBUL Technical University |  |

|                  | Assist. Prof. Dr. Hakan DOĞAN<br>Medipol University                     |  |

Date of Submission: 17 November 2017Date of Defense: 12 December 2017

### FOREWORD

I would like to thank my advisor Assist. Prof. Dr. Tufan Coşkun KARALAR for the oppurtunity of working in this project so that I can have such kind of thesis which include all aspects of integrated circuit design such as schematic design, layout and lab measurements etc.

I also would like to thank to the guys in ITU VLSI LABs for making a nice and friendly working environment during my graduate education there.

Last but not least I would like to thank my family for their continuous and unconditional support in any endeavor I may undertake.

December 2017

Alper GİRGİN

## TABLE OF CONTENTS

| Page |

|------|

|------|

| FOREWORD                                                            | ix  |

|---------------------------------------------------------------------|-----|

| TABLE OF CONTENTS                                                   | xi  |

| ABBREVIATIONS                                                       |     |

| LIST OF TABLES                                                      | xv  |

| LIST OF FIGURES                                                     |     |

| SUMMARY                                                             | xix |

| ÖZET                                                                | xxi |

| 1. INTRODUCTION                                                     | 1   |

| 1.1 Motivation                                                      | 1   |

| 1.2 Design Summary                                                  | 2   |

| 1.3 Thesis Organization                                             |     |

| 2. CONTINUOUS TIME DELTA SIGMA ADC BASICS                           | 5   |

| 2.1 Oversampling and Noise Shaping                                  | 6   |

| 2.2 Performance Metrics                                             |     |

| 2.3 Increasing the Performnace                                      |     |

| 2.4 Delta Sigma Modulator Structures                                |     |

| 2.4.1 Feedback                                                      | 9   |

| 2.4.2 Feed-forward                                                  | 9   |

| 2.4.3 Cascaded (MASH)                                               | 9   |

| 2.5 Implementation Considerations                                   |     |

| 2.5.1 Noise                                                         | 10  |

| 2.5.2 Nonlinearity                                                  | 11  |

| 2.5.3 Excess loop delay                                             | 11  |

| 2.5.4 Metastability                                                 | 12  |

| 2.5.5 Finite amplifier gain and gain bandwidth product              | 12  |

| 3. MODEL                                                            | 15  |

| 3.1 Noise Transfer Function Synthesis in DT Domain                  | 15  |

| 3.2 DT to CT Conversion by Using Impulse Invariant Transform        | 17  |

| 3.3 Simulink Model                                                  | 18  |

| 3.3.1 Model with ideal quantizer                                    | 18  |

| 3.3.2 Model with flash ADC, dynamic element matchin and feedback DA | C20 |

| 3.3.3 Model with integrator non-idealities                          | 23  |

| 3.4 Calculation of Resistor and Capacitor Values of Loop Filter     | 24  |

| 3.5 Ideal Circuit Model                                             | 27  |

| 3.5.1 Loop filter                                                   | 28  |

| 3.5.2 Quantizer                                                     | 29  |

| 3.5.3 Feedback DAC                                                  | 30  |

| 3.5.4 Simulation results                                            | 30  |

| 4. SCHEMATIC                                                        | 33  |

| 4.1 Loop Filter                                                     | 34  |

| 4.1.1 Operational amplifier                                         |     |

| 4.1.2 Noise analysis                                                | 37  |

| 4.2 Quantizer                          | 39 |

|----------------------------------------|----|

| 4.2.1 Comparator                       | 40 |

| 4.2.2 Output latch                     | 42 |

| 4.3 Dynamic Element Matching           |    |

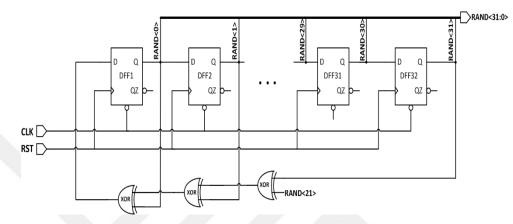

| 4.3.1 Pseudo random bit generator      |    |

| 4.3.2 Swapper                          | 45 |

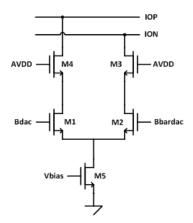

| 4.4 Feedback DAC                       | 46 |

| 4.4.1 Input latch                      | 48 |

| 4.4.1 DAC cell                         | 49 |

| 4.5 Decimation Filter                  | 50 |

| 4.6 Corner And Monte Carlo Simulations | 52 |

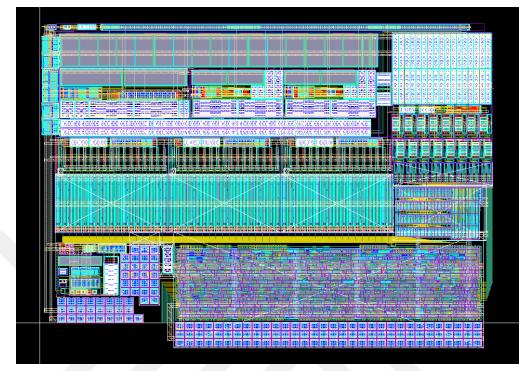

| 5. LAYOUT AND MEASUREMENTS             | 53 |

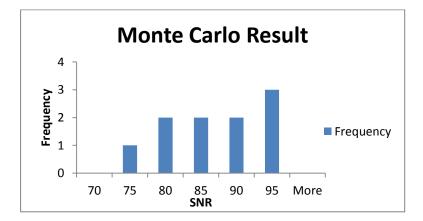

| 5.1 Floorplan                          | 53 |

| 5.2 Loop Filter                        | 54 |

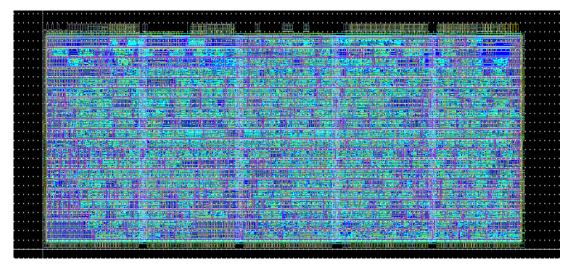

| 5.3 Quantizer                          |    |

| 5.4 Dynamic Element Matching           | 57 |

| 5.5 Feedback DAC                       | 58 |

| 5.6 Decimation Filter                  | 59 |

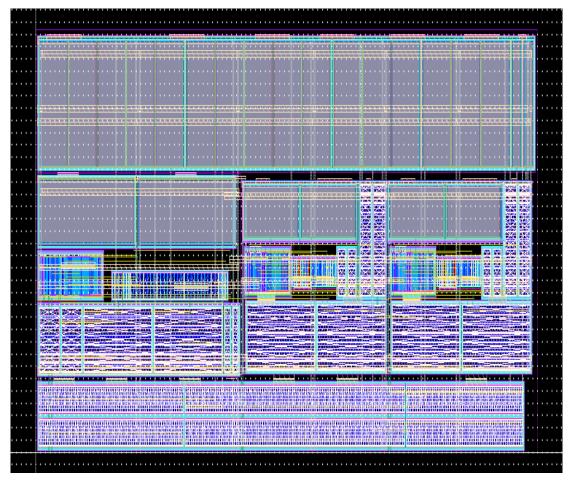

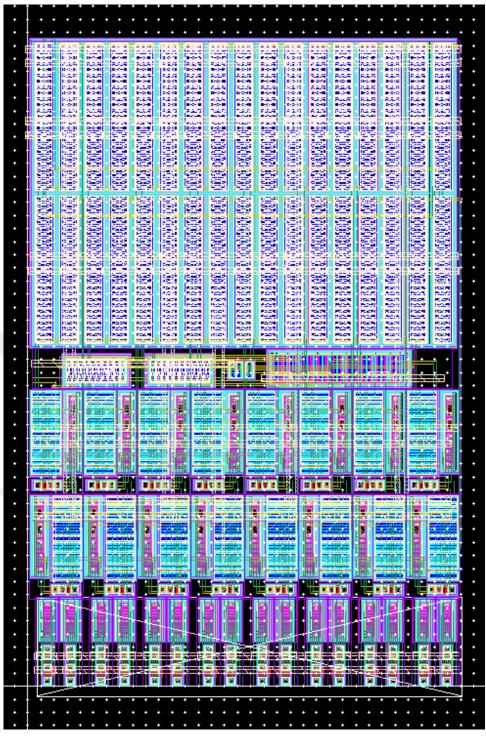

| 5.7 Full Delta Sigma ADC Layout        | 60 |

| 5.8 Post Layout Simulation Result      | 62 |

| 5.9 Measurement Results                | 62 |

| 6. CONCLUSIONS                         | 69 |

| REFERENCES                             |    |

| APPENDICES                             |    |

| APPENDIX A                             | 73 |

| APPENDIX B                             |    |

| APPENDIX C                             | 79 |

| APPENDIX D                             | 81 |

| APPENDIX E                             | 85 |

| APPENDIX F                             | 89 |

## **ABBREVIATIONS**

| ADC  | : Analog to Digital Converter                |

|------|----------------------------------------------|

| CMRR | : Common Mode Rejection Ratio                |

| CMFB | : Common Mode Feedback                       |

| DAC  | : Digital to Analog Converter                |

| ENOB | : Efficient Number of Bits                   |

| FPGA | : Field Programmable Gate Array              |

| РСВ  | : Printed Circuit Board                      |

| PSD  | : Power Spectral Density                     |

| SNDR | : Signal to Noise and Distortion Ratio       |

| SNR  | : Signal to Noise Ratio                      |

| SoC  | : System on Chip                             |

| SPI  | : Serial Peripheral Interface                |

| SQNR | : Signal to Quantization Noise Ratio         |

| STF  | : Signal Transfer Function                   |

| NTF  | : Noise Transfer Function                    |

| TSMC | : Taiwan Semiconductor Manufacturing Company |

| VCVS | : Voltage Controlled Voltage Source          |

|      |                                              |

# LIST OF TABLES

## Page

| Table 1.1 : Specifications of Delta Sigma ADC | 3  |

|-----------------------------------------------|----|

| Table 3.1 : Discrete Time Coefficients.       | 4  |

| Table 3.2 : Continuous Time Coefficients      | 6  |

| Table 3.3 : Resistor and Capacitor Values     | 26 |

| Table 4.1 : Corner Analysis Results           | 52 |

| Table 6.1 : Comparison with Other Works       |    |

## LIST OF FIGURES

## Page

| Figure 1.1 : System Level Block Diagram of Hall Effect Sensor         | 1  |

|-----------------------------------------------------------------------|----|

| Figure 1.2 : ADC Survey                                               |    |

| Figure 2.1 : System Model of Delta Sigma ADC                          |    |

| Figure 2.2 : Frequency Plots of NTF and STF in 3rd Order DSM.         |    |

| Figure 2.3 : Oversampling                                             |    |

| Figure 2.4 : Noise Shaping                                            |    |

| Figure 2.5 : Feedback DSM Topology                                    |    |

| Figure 2.6 : Nth Order Feed-forward DSM.                              | 9  |

| Figure 2.7 : Cascaded DSM Architecture.                               |    |

| Figure 2.8 : Noise Elements in DSM.                                   |    |

| Figure 2.9 : ELD Compansation.                                        | 12 |

| Figure 3.1 : Root Locus of NTF                                        | 15 |

| Figure 3.2 : SNR vs. Input Amplitude Plot                             |    |

| Figure 3.3 : Frequency Response of NTF and STF.                       | 17 |

| Figure 3.4 : Simulink Model with Ideal Quantizer Block                | 19 |

| Figure 3.4 : PSD of First Model                                       | 20 |

| Figure 3.6 : Model with Flash ADC, DEM and Feedback DACs.             | 20 |

| Figure 3.7 : 4-bit Flash ADC Simulink Model                           |    |

| Figure 3.8 : Feedback DAC Simulink Model                              | 22 |

| Figure 3.9 : Dynamic Element Matching Block                           |    |

| Figure 3.10 : Power Spectrum Density of Second Model                  | 23 |

| Figure 3.11 : Integrator with Non-idealities                          |    |

| Figure 3.12 : Power Spectrum Density of Third Model                   | 24 |

| Figure 3.13 : Ideal Schematic of Loop Filter.                         | 25 |

| Figure 3.14 : Loop Filter Structure                                   | 26 |

| Figure 3.15 : AC Response of the Loop Filter                          | 27 |

| Figure 3.16 : Ideal Schematic Model                                   |    |

| Figure 3.17 : Schematic of Loop Filter                                | 29 |

| Figure 3.18 : Bode Plot and Schematic of Ideal Opamp                  |    |

| Figure 3.19 : Ideal Schematic of Flash ADC                            |    |

| Figure 3.20 : Power Spectrum Density of the Ideal Schematic Model     |    |

| Figure 4.1 : Top Level Schematic of Delta Sigma ADC                   |    |

| Figure 4.2 : Power Spectrum Density of ADC Output                     |    |

| Figure 4.3 : Schematic of Loop Filter                                 |    |

| Figure 4.4 : AC Simulation Result of Loop Filter                      |    |

| Figure 4.5 : Transient Simulation Result of Loop Filter               | 35 |

| Figure 4.6 : Folded Cascode Fully Differential Opamp with Common Mode |    |

| Feedback                                                              |    |

| Figure 4.7 : Simulation Test Bench.                                   |    |

| Figure 4.8 : AC Simulation Result                                     |    |

| Figure 4.9 : Transient Simulation Result                              |    |

| Figure 4.10 : Input Noise Equivalent Plot                             | 38 |

|                                                               | 20   |

|---------------------------------------------------------------|------|

| Figure 4.11 : Noise Analysis Summary                          |      |

| Figure 4.12 : Schematic of Flash ADC                          | 40   |

| Figure 4.13 : Simulation Result of Flash ADC.                 |      |

| Figure 4.14 : Schematic of Fully Differential Comparator      |      |

| Figure 4.15 : Simulation Result of Comparator                 |      |

| Figure 4.16 : Output Latch of Flash ADC                       |      |

| Figure 4.17 : Dynamic Element Matching                        |      |

| Figure 4.18 : Pseudo Random Bit Generator                     |      |

| Figure 4.19 : Swapper                                         |      |

| Figure 4.20 : Feedback DAC Schematic View                     |      |

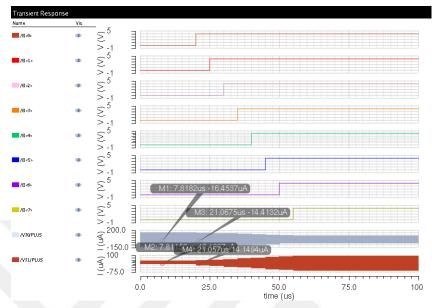

| Figure 4.21 : Simulation Result of Current DAC                | . 47 |

| Figure 4.22 : Glitches of Output Current                      | 47   |

| Figure 4.23 : Schematic of Input Latch                        | 48   |

| Figure 4.24 : Simulation Result of Input Latch                | 48   |

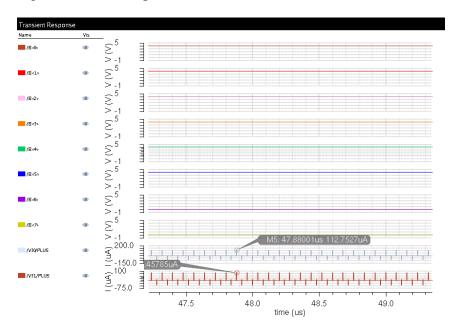

| Figure 4.25 : Output Transition of Input Latch                | 49   |

| Figure 4.26 : Schematic of a DAC Cell                         | 50   |

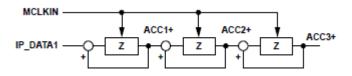

| Figure 4.27 : Accumulator                                     | 50   |

| Figure 4.28 : Differentiator                                  | 51   |

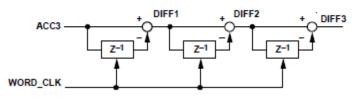

| Figure 4.29 : Monte Carlo Result                              | 52   |

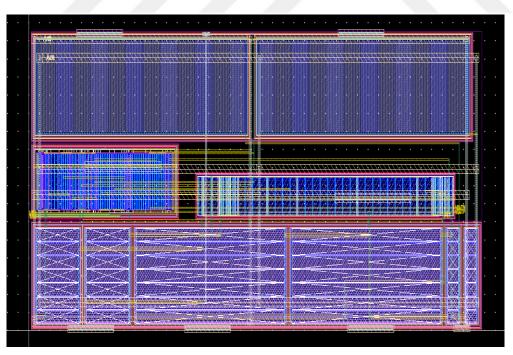

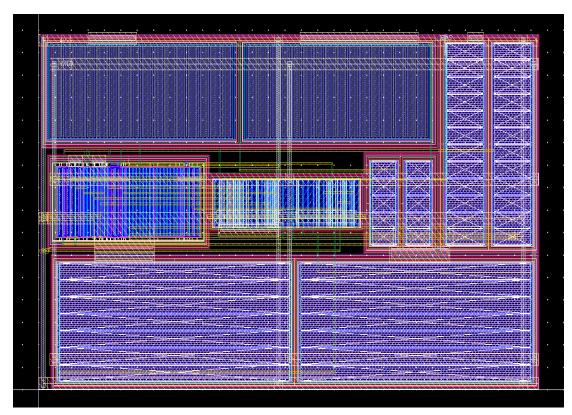

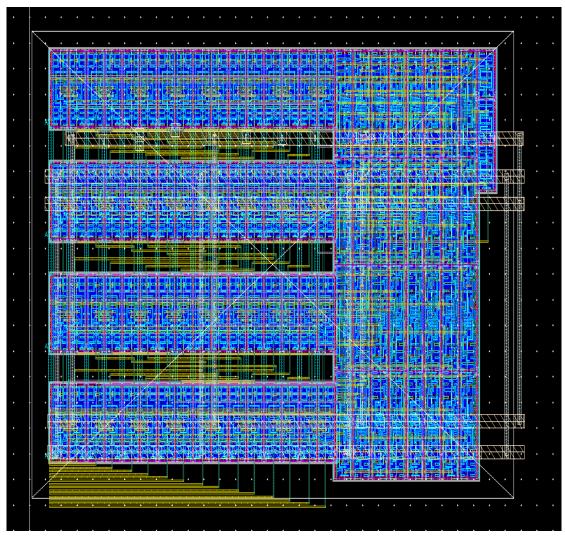

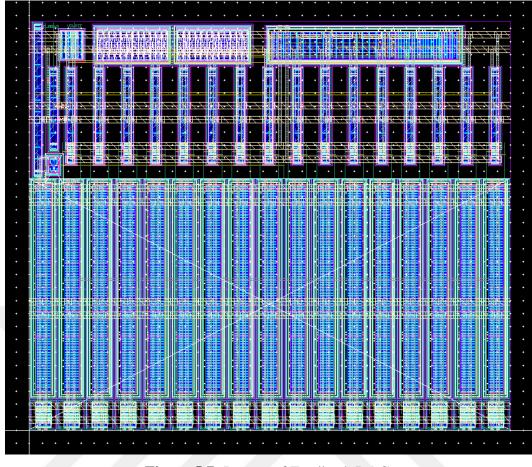

| Figure 5.1 : Floorplan of the Design                          |      |

| Figure 5.2 : Layout of First Operational Amplifier            |      |

| Figure 5.3 : Layout of Second and Third Operational Amplifier |      |

| Figure 5.4 : Layout of Loop Filter                            |      |

| Figure 5.5 : Layout of Flash ADC                              | 57   |

| Figure 5.6 : Layout of Dynamic Element Matching               |      |

| Figure 5.7 : Layout of Feedback DAC                           |      |

| Figure 5.8 : Layout of Decimation Filter                      | . 60 |

| Figure 5.9 : Layout of Delta Sigma ADC                        | . 61 |

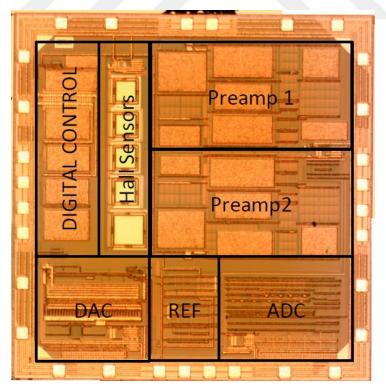

| <b>Figure 5.10 :</b> Micrograph of Sensor Chip                |      |

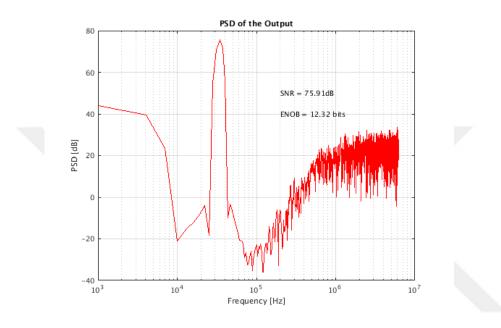

| Figure 5.11 : Post-Layout PSD of Output                       |      |

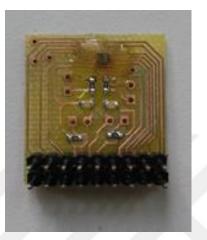

| Figure 5.12 : Test Board                                      |      |

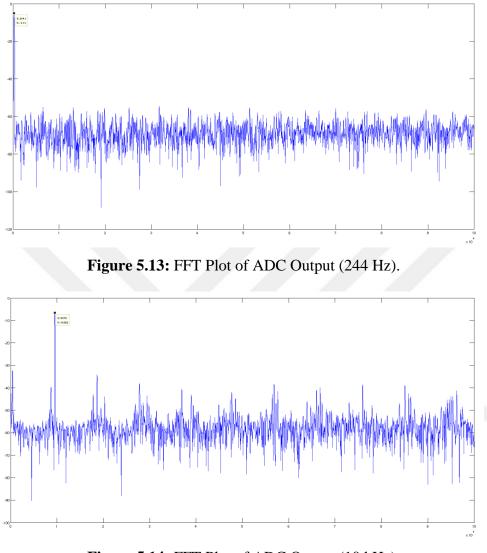

| Figure 5.13 : FFT Plot of ADC Output (244 Hz)                 |      |

| Figure 5.14 : FFT Plot of ADC Output (10 kHz)                 |      |

| <b>Figure 5.15 :</b> FFT Plot of ADC Output (47 kHz)          |      |

| Figure 5.16 : FFT Plot of ADC Output (88 kHz)                 |      |

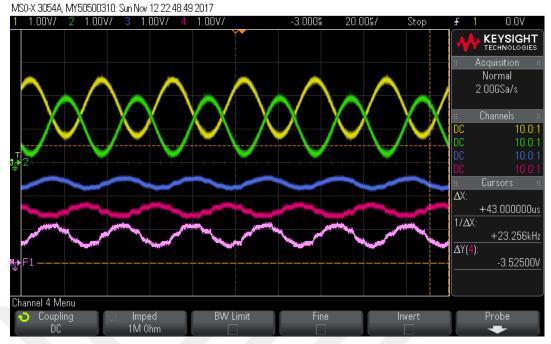

| Figure 5.17 : Time Domain Plot of DAC Output (5 kHz).         |      |

| Figure 5.17 : This Domain Flot of DAC Output (5 kHz)          |      |

| Figure 5.19 : Time Domain Plot of DAC Output (30 kHz).        |      |

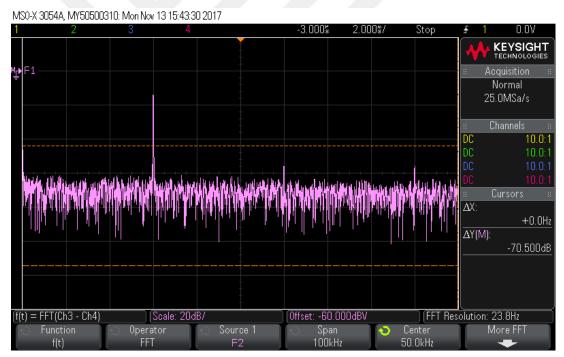

| Figure 5.20 : FFT Plot of DAC Output (30 kHz)                 |      |

|                                                               |      |

### A 14-BIT 100-kHZ CONTINUOUS-TIME DELTA-SIGMA ANALOG-TO-DIGITAL CONVERTER FOR HALL EFFECT BASED CURRENT SENSOR APPLICATION

#### SUMMARY

Systems on chip can integrate a number of different functions in a single die and replace a PCB with many discrete components with a single integrated circuit. Therefore their popularity increased over years. Sensor systems are good examples of system-on-chip designs.

This work is also a part of a sensor system on a chip. The sensor system consists of sensor cores, preamplifiers, analog-to-digital converter, digital calibration and digital-to-analog converter. System needs an analog-to-digital converter because calibration of the sensor is in digital domain. Delta sigma ADC is preferred due to the sensor system requirements of high-resolution and low speed.

Integrated circuit design steps are modelling, schematic level design, physical design and lab measurements after production. In this work, first, Simulink and Verilog-A model of full ADC system is prepared and requirements of sensor system are satisfied. SNQR of the ADC is about 100 dB using ideal models. Next, ideal blocks are replaced with their schematic level realizations using transistors, resistors and capacitors that are provided by the foundry. TSMC 0.18um process is used in this work. In this step, non-idealities affect the system performance and SQNR of the ADC is reduces to 87 dB. Following schematic level design, physical design step starts. During physical design, Placement of each component on the chip and their interconnections are realized. There are some verification steps that ensure the physical design is ready for production (DRC, LVS, ERC, etc.). After these verifications are completed, post layout simulations are executed. Post-layout simulation adds parasitics effects to the simulation to have more realistic results. SONR of the ADC including post-layout parasitics is around 77 dB, which meet our specification. After manufacturing the chip is charaterized in our test labs Since the chip is not only an ADC chip, but a sensor system on chip and the ADC is a subblock of this sensor system some problems arose during measurements of the ADC. However, the ADC works mostly as expected in the system chip.

As a conclusion, a delta sigma ADC for a sensor system on chip application is designed and realized in this work with using a common integrated circuit design flow. After manufacturing the chip is characterized and the ADC is found to be functional.

### HALL ETKİSİ BAZLI AKIM SENSÖRÜ UYGULAMASI İÇİN 14-BİT 100-KHZ SÜREKLİ ZAMANLI DELTA SİGMA ANALOG DİJİTAL ÇEVİRİCİ

## ÖZET

Günümüzde tümdevre teknolojisinin giderek gelişmesiyle birlikte ayrık elemanlarla gerçekleştirilen elektronik sistemler hem alan hem de güç tasarrufundan dolayı system-on-chip denilen bütün bir sistemi oluşturan blokların aynı kırmık üzerinde bulunduğu sistemler olarak gerçekleştirilmektedir. Bir çok alt bloktan oluşan sensör uygulamaları ise bunun iyi bir örneğidir. Genel olarak sensor sistemleri sensor çekirdeği, kuvvetlendirici, analog sayısal dönüştürücü, sayısal işaret işleme ve sayısal analog (S/A) dönüştürücü bloklarından oluşmaktadır. Kalibrasyon gibi işlemler sayısal ortamda yapıldığı takdirde analog sayısal (A/S) dönüştürücü bloğunun olması şarttır.

Bu çalışmada da bir sensor uygulaması için analog sayısal dönüştürücü tasarlanmıştır. Sensör çekirdeği Hall etkisini kullanarak üzerine düşen manyetik alandan Hall gerilimini oluşturmaktadır. Bu gerilim küçük genlikli olduğundan kuvvetlendirici bloğu gerekmektedir. Daha sonra gerek sensor çekirdeğinden gerekse diğer elektronik işaret işleme bloklarından kaynaklı nonlineerlikleri düzeltmek için sayısal kalibrasyon gerekmektedir. Kalibre edilen işaret sayısal analog çevirici kullanılarak dışarıya analog olarak verilmektedir.

Analog sayısal dönüştürücü ise sürekli zamanlı delta sigma analog sayısal dönüştürücü olarak seçilmiştir. Bunun sebebi sensor sistemi için gerekli olan hassasiyet ve hız seviyesidir. 14-bit çözünürlük ve 100 kHz bant genişliğine sahip olması istenen analog sayısal dönüştürücü için en optimum seçenek delta sigma analog sayısal dönüştürücülerdir. Düşük hızlı ve yüksek çözünürlüklü uygulamalar için delta sigma dönüştürücüler tercih edilmektedir.

Delta sigma A/S dönüştürücüler genel olarak üç alt bloktan oluşur. Bunlar, gürültü şekillendirmenin yapıldığı filtre bloğu, yüksek hızlı örnekleme ve kuantalamanın yapıldığı kuantalayıcı bloğu ve geri besleme katsayılarının oluşturulduğu bloklardır. Bu tasarımda geri besleme katsayıları akım modlu S/A dönüştürücüler ile elde edilmiştir. Filtre ise aktif-RC integratörler kullanılarak oluşturulmuştur. Kuantalayıcı ise basit bir flash tipinde A/S dönüştürücüdür.

Tümdevre tasarımında genel olarak önce sistemin ideal modeli oluşturularak sistemin fonksiyonel bir hatası olup olmadığı kontrol edilir. Daha sonra da şematik seviyesinde tasarıma geçilerek gerçek modele sahip elemanlarla tasarıma devam edilir. Sonrasında ise fiziksel tasarım olarak devrenin serimi yapılır ve üretime hazır olduğundan emin olunduktan sonra üretime gönderilir. Üretimden geldikten sonra da çipin ölçümüne başlanır. Tümdevre tasarımının temel adımları bunlardır. Bu çalışmada da benzer tasarım adımları uygulanmıştır.

Öncelikle A/S dönüştürücü sisteminin Simulink ve Verilog-A kullanılarak devrenin ideal modelleri yapılmış ve benzetimler yapılarak sistemin herhangi bir yapısal hatası

var mı diye kontrol edilmiş, olan hatalar da düzeltilmiştir. Benzetim sonuçlarında 100 dB civarı SQNR görüldükten sonra da şematik seviyesi tasarıma geçilmiştir.

Şematik seviye tasarım ise modeldeki ideal elemanlar üreticiden gelen gerçek modele sahip elemanlarla değiştirilerek yapılmıştır. Örneğin, ideal bir anahtar elemanı yerine transistörler kullanılarak yapılan bir anahtar koyulduğunda doğal olarak o anahtarın direnci, gecikmesi, yük etkileri devreye girecektir. Bu da performansta bir düşüşe sebep olacaktır.

Gürültü ve işaret transfer fonksiyonlarını sağlayan filtre aktif-RC integratörler kullanılarak oluşturulmuştur. Bu tipteki integratörler direnç, geri besleme kapasitesi ve operasyonel kuvvetlendirici kullanılarak yapılır. Bu tasarımda da kuvvetlendirici olarak katlı kaskot yapısında giriş katı ve ortak kaynak bağlı bir çıkış katı birlikte kullanılarak iki katlı bir yapı tasarlanmıştır. Filtre üçüncü dereceden olduğu için üç tane integratör kullanılmıştır. İşaretle ilk karşılaşan blok ilk integratör olduğu için o integratör özellikle gürültü performansı daha iyi olacak şekilde tasarlanmıştır.

Kuantalayıcı katı olarak 5-bitlik basit bir flash A/S dönüştürücü kullanılmıştır. Bu tür A/S dönüştürücüler referans aralığı ve bu referansları giriş işaretiyle karşılaştıran karşılaştırıcı devrelerinden oluşmaktadır. Bu tasarımda ise direnç dizisiyle oluşturulan referanslar ve bu referansları girişle karşılaştıran 16 adet karşılaştırıcı devresi kullanılmıştır. 16 seviyelik bir flash A/S dönüştürücü olduğu için 5-bit olarak kabul edilmiştir.

Geri besleme katsayılar ise akım modlu S/A kullanılarak filtreye verilmiştir. Burada S/A dönüştürücü kullanılmasının sebebi, kuantalayıcının termometrik kodlu 16 bitlik dijital bir işaret oluşturması ve filtreye girecek geri besleme katsayılarının ise analog olması gerekliliğidir. Akım modlu S/A dönüştürücü 16 adet hücreden oluşmaktadır ve her bir bit bir hücredeki anahtarla o hücreden akım geçmesini ya da geçmemesini sağlar. Bu şekilde 16 hücrenin akımı toplanarak filtreye geri besleme olarak girer.

Burada önemli olan diğer bir blok ise dinamik eleman eşleme bloğudur. Genel olarak D/A dönüştürücülerin girişine koyulan bu tip bloklar S/A dönüştürücü hücreleri arasındaki uyuşmazlık etkilerinden kaynaklı lineerlik bozulmalarını düzeltmeye yararlar. Bu tasarımda da dinamik eleman eşleme metoduyla S/A dönüştürücünün performansı arttırılmıştır.

Dinamik eleman eşleme metodu ise şu şekilde çalışmaktadır: Kuantalayıcı çıkışından gelen termometrik kodlu bitler S/A dönüştürücü düşük bitlerin denk geldiği hücrelerin sürekli aktif olmasına sebep olur. Bu da bu hücreler arasındaki uyuşmazlık etkilerinin performansı daha çok etkilemesine sebep olur. Bu neden termometrik kodlu bitler dinamik eleman eşleme metoduyla rastgele olacak şekilde dağıtılır ve hep aynı hücrelerin aktif olması engellenir. Böylece de aktif olan S/A dönüştürücü hücrelerinin çeşitlenmesiyle uyuşmazlıkların ortalaması düşer. Bu da S/A dönüştürücünün lineerliğini arttırır.

A/S dönüştürücü çıkışı yüksek hızlı örnekleyen saat işaretiyle çalıştığı için çıkış verisini Nyquist bandına indirmek için delta sigma A/S dönüştürücülerinde seyreltme filtresi kullanılır. Sistem üçüncü dereceden olduğu için seyreltme filtresi de sinc3 fonksiyonu olacak şekilde seçilmiştir. Bu fonksiyonu gerçeklemek için ise Hogenauer filtre yapısı kullanılmıştır. Bu yapının kullanılma sebebi ise gerçekleme kolaylığıdır.

Seyreltme filtresi tamamen dijital olduğu için de Verilog koduyla tasarlanıp Cadence tasarım ortamının dijital tasarım araçları kullanılarak sentezlenip diğer bloklara eklenmiştir.

Şematik seviye tasarımda alt bloklar bu şekilde tasarlandıktan sonra tüm sistemin benzetimleri yapılmıştır. Burada da 86 dB civarında bir SNDR elde edilmiştir. Ek olarak, işaretin girdiği ilk blok olan delta sigma modulatörün termal gürültü performansına da bakılmış ve gürültü performansın -87 dB civarında olduğu görülmüştür. Bu da kuantalama gürültüsü, harmonik distorsiyon ve termal gürültü toplamının 80 dB'den yüksek olduğu anlamına gelmektedir. Bu da zaten istenilen SNDR 80 dB civarında olduğu için iyi bir değer denebilir.

Şematik tasarım bittikten sonra da devrenin fiziksel tasarımına yani serimine başlanmıştır. Serimde önce istenilen alana sığacak şekilde yer planı yapılıp sonra da alt bloklardan başlanarak hepsi için tek tek belirlenen alanlara uyacak şekilde serimleri yapılmıştır. Buradaki diğer önemli konu ise işaretin izlediği yola uygun olarak yer planının yapılmasıdır. Alt blok serimlerinde mümkün olduğunca düşük seviyeli metaller kullanılmaya çalışılmıştır.

Serimler bittikten sonra DRC, LVS ve ERC kontrolleri yapılmıştır. Sonrasında ise serim sonrası benzetimleri yapılmıştır ve bu sonuçlarda da 77 dB civarı bir SNDR elde edilmiştir. Bu değer hedeflenen değerden düşük olmasına rağmen yine de kabul edilebilir bir değerdir. Devre tamamlandıktan sonra sensör sistemindeki diğer bloklara eklenip üretime gönderilmiştir.

Çip üretilip geldikten sonra ölçümlere başlanmıştır. Çip sadece delta sigma A/S dönüştürücüyü değil de bir sürü bloğun bulunduğu sensör sistemini içerdiği için tek başına A/S dönüştürücünün performansı düzgün ölçülememiştir.

En başta seyreltilmiş delta sigma A/S dönüştürücü çıkışını çipin SPI haberleşme arayüzünü kullanarak dışarı almak planlanmıştır ancak SPI hızı özellikle 1 kHz'den yüksek hızlı A/S giriş işaretleri için yeterli gelmemeye başlamıştır.

Buna çözüm olarak A/S dönüştürücü diğer bloklarla birlikte çalıştırılmış ve tüm sistemin çıkışı olan S/A dönüştürücü çıkışının frekans spektrumu incelenmiştir. Burada daha iyi bir lineerlik performansı görülse de sebebinin yüksek ihtimalle sistemin en son bloğu olan S/A dönüştürücüden kaynaklandığı düşünülmektedir. Yine de bütün sensör sistemi incelendiğine delta sigma A/S dönüştürücünün performansına tam olarak bakılamasa da çalıştığı gözlenmiştir.

A/S dönüştürücünün benzetim performansı FoM (Figure of Merit) hesaplanarak literatürdeki diğer benzer çalışmalarla karşılaştırılmıştır. Burada da akım optimizasyonu yapılmadığı için S/A dönüştürücünün güç tüketiminin diğer çalışmalardan fazla olduğu görülmüştür.

İleri çalışma olarak ise A/S dönüştürücünün akım optimizasyonu yapılıp daha iyi bir FoM değerine sahip olması sağlanabilir. Buna ek olarak seyreltilmemiş A/S dönüştürücü çıkışı çipe yeni terminaller eklenerek direkt olarak dışarıya verilebilir. Bu sayede ölçümde karşılaşılan zorluklar çözülmüş olur ve A/S dönüştürücünün performansına net bir şekilde bakılabilir.

Sonuç olarak bu çalışmada sensör uygulaması için sürekli zamanlı delta sigma A/S dönüştürücü genel tümdevre tasarım aşamalarına uyularak tasarlanmış ve ölçümler sonucunda başarılı olduğu görülmüştür.

#### **1. INTRODUCTION**

System on chip (SoC) is a term that defines the chips that include all the blocks that are included in an electronic system such as, sensors, amplifiers, data converters, RF blocks or microcontrollers. Improvements in integrated circuit design and production technologies, popularized System on chips. Electronic systems realized as SoCs consume less area and power than system on board level designs which is their main advantage. However, harder design and verification processes and less error correction ability are some of the disadvantages of SoCs.

### **1.1 Motivation**

The work presented in this thesis is a part of Hall Effect Based Current Sensor project which is funded by The Scientific and Technological Research Council of Turkey (TÜBİTAK) research grant 115C053.

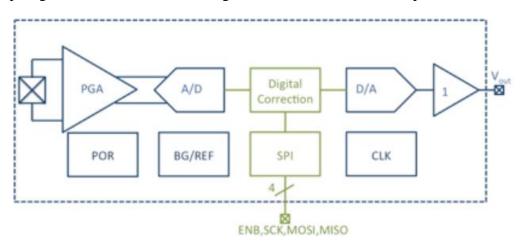

Sensor chip consists of Hall Effect sensors, a preamplifier, an analog-to-digital converter, a digital calibration block and a digital-to-analog converter. In addition to these blocks, a serial peripheral interface (SPI) block to communicate with outside, temperature sensor block to be used in calibration and other necessary blocks like bandgap references, an oscillator, a power-on-reset and a test bus switch are in the chip. Figure 1.1 shows the block diagram of the overall sensor chip.

Figure 1.1: System Level Block Diagram of Hall Effect Sensor Application.

Sensors produce analog voltage output, the preamplifier amplifies this voltage and since there is a digital calibration block, an ADC is needed to convert this amplified sensor voltage to digital bits.

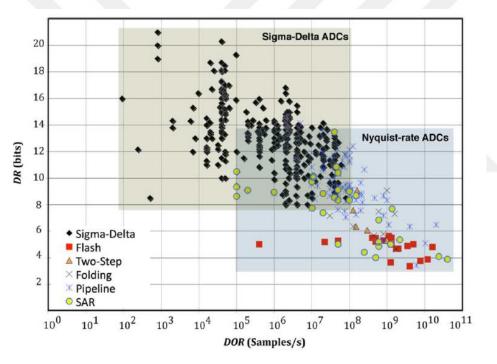

The reason that delta sigma ADC chosen is the low signal bandwidth (100 kHz) and mid-resolution (14-bit) requirements. Meeting these specifications with a continuous time delta sigma ADC is easier. Figure 1.2 shows the ADC survey results of the literature. It is obvious that high speed and low resolution ADCs are dominated by Nyquist rate ADCs while low speed and high resolution ADCs are dominated by delta sigma ADCs. It also can be seen that the ADCs that have similar specifications to this work are delta sigma ADCs.

Figure 1.2: ADC Survey [1].

#### **1.2 Design Summary**

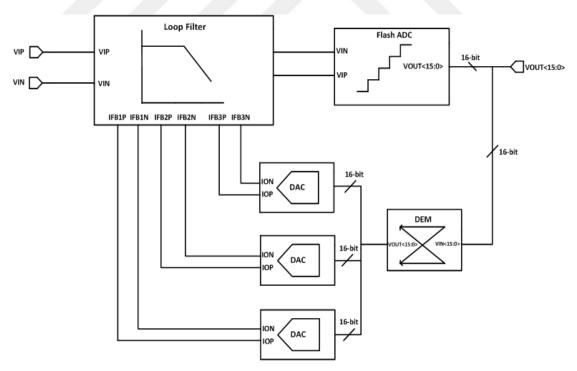

Delta sigma modulators mostly consist of three fundamental sub-blocks. In this design, first block is loop filter which basically does the noise shaping, second one is the flash ADC which samples and quantizes the signal and last block is feedback DAC which produces the feedback coefficients as currents from the output voltage to the loop filter. Additional to these, there is dynamic element matching block that reduces the mismatch based errors of feedback DAC.

Because of several advantages delta sigma ADC is planned to design in continuous mode and multi bit at output (decided as 4 bits). Different type of delta sigma ADCs are investigated and compared in next chapter which explains delta sigma ADC basics.

Since the ADC has a 100 kHz bandwidth a faster sampling clock with enough oversampling is necessary. There is a 50 MHz internal clock in the system and the sampling clock can be produced by using it, just simply dividing by 4. This makes the sampling frequency 12.5 MHz and OSR is calculated as 62.5. SNDR of ADC is expected around 82 dBc. In terms of ENOB fashion, this makes typically 13 bits (max 14, min 12). Table 1.1 shows the basic specifications of the delta sigma ADC in this work. SNDR, ENOB and current consumption values are design targets that may differ from results.

| Parameter        | Value    |

|------------------|----------|

| Power Supply     | 4 V      |

| Current Consump. | 5 mA     |

| Common Mode V.   | 2 V      |

| Full Scale V.    | 4 V      |

| ENOB             | 13 Bits  |

| SNDR             | 82 dBc   |

| Bandwidth        | 100 kHz  |

| Sampling Freq.   | 12.5 MHz |

| OSR              | 62.5     |

| Output Bits      | 4 Bits   |

**Table 1.1:** Specifications of Delta Sigma ADC.

Manufacturing technology is TSMC 0.18u CMOS process with high voltage (5V) transistors. Design environment is Cadence Design Environment tools: Virtuoso Schematic and Layout XL editors, Spectre simulator and Assura layout verification. NCLaunch, RTL Compiler and Encounter tools of Cadence Design Environment are used to simulate, synthesize and implement digital blocks that are designed by using Verilog hardware description language. MATLAB and Simulink are also used for modelling and SNR calculations.

### **1.3 Thesis Organization**

The design flow of continuous time delta sigma analog to digital converter in this thesis is given below.

- Synthesizing NTF and STF (z-domain) in MATLAB by using Delta-Sigma Toolbox

- Transforming filter coefficients from z-domain to s-domain by using Impulse Invariant Transform

- Modelling delta sigma ADC in Simulink with s-domain elements (some nonidealities also can be added)

- Calculating resistor and capacitor values of loop filter

- Modelling delta sigma ADC in Cadence with ideal blocks (important to investigate excess loop delay)

- Implementing delta sigma ADC with real elements

- Layout and measurements results

Thesis organization is planned respect to this design flow with additional theoretical sections. In this first chapter, general information about SoCs, sensor chip which includes this work's delta sigma ADC and the specifications of delta sigma ADC are given.

In second chapter, fundamentals of continuous time delta-sigma converters are explained with basic background, performance aspects and some non-idealities.

In third chapter, system level design starts by synthesizing a proper noise transfer function(NTF) and modelling this function in Simulink with other blocks of delta sigma ADC. Then, ideal model in Cadence environment is presented.

In fourth chapter, schematic level design with real components is explained and simulation results of the sub-blocks and delta sigma ADC are given.

In fifth chapter, layout of the design is explained with layout considerations and some important notes about the layout. In addition to this, measurement test setup is explained and the results are given.

#### 2. CONTINUOUS TIME DELTA SIGMA ADC BASICS

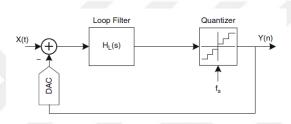

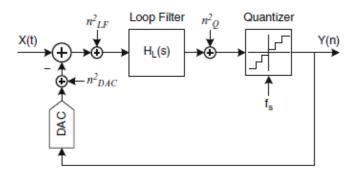

An ideal delta sigma ADC consists of three main sub-blocks: Loop filter, quantizer and feedback DAC. Figure 2.1 shows the delta sigma ADC modulator. First, input signal are filtered by loop filter and then sampled and quantized by the quantizer block. After that the feedback DAC converts digital output to analog and feeds the input. This system is nonlinear in reality however the approximate linear equations of the system are given in (2.1) and (2.2) to understand it better.

Figure 2.1: System Model of Delta Sigma ADC [2].

Here, X is the input signal, H is the transfer function of loop filter and  $E_Q$  is the quantization error. STF and NTF stands for signal transfer function and noise transfer function. Figure 2.2 shows the frequency domain plots of NTF and STF.

$$Y(s) = X(s) \cdot \frac{H_L(s)}{1 + H_L(s)} + E_Q(s) \cdot \frac{1}{1 + H_L(s)}$$

(2.1)

$$STF(s) = \frac{H_L(s)}{1 + H_L(s)}, NTF = \frac{1}{1 + H_L(s)}$$

(2.2)

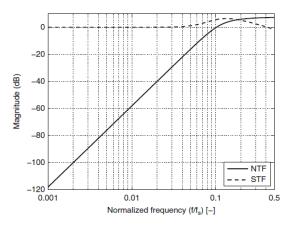

Figure 2.2: Frequency Plots of NTF and STF in 3rd Order DSM [2]

As it can be seen from Figure 2.2, noise transfer function shapes the noise, which decreases the noise in base band and increases the resolution of the ADC. This noise shaping is one of the major features of a delta sigma ADC with oversampling.

### 2.1 Oversampling and Noise Shaping

There might be some application specific differences between delta sigma ADCs but two basic principles are the same for all of delta sigma ADCs: oversampling and noise shaping.

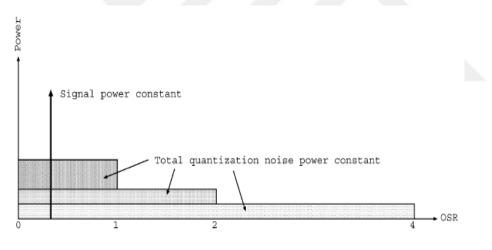

Sampling with a higher frequency than required Nyquiest frequency is called oversampling. Oversampling does not change the total quantization noise power because quantization noise is not related to the sampling frequency. However, total quantization noise power spread over a wider band due to oversampling and it decreases the quantization noise power over the band of interest. Figure 2.3 shows the effect of oversampling by 2x and 4x on quantization noise power.

Figure 2.3: Oversampling [3].

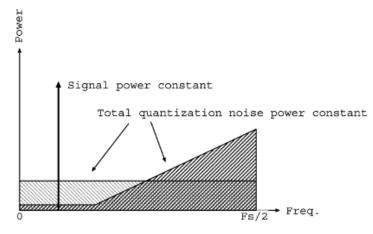

Noise shaping is another way to decrease quantization noise power over the band of interest by pushing the quantization noise through the higher frequencies as shown in Figure 2.4. This process also does not change the total quantization noise power. Quantization error feeds the filter input and the noise transfer function of loop filter shapes the noise. Signal is not affected from this process because the input signal is only related to signal transfer function. Equation (2.1) and (2.2) shows the theory behind noise shaping.

Figure 2.4: Noise Shaping [3].

These two methods are used together in delta sigma ADCs and they are the main elements that decide the performance of delta sigma ADC.

### **2.2 Performance Metrics**

Some important performance parameters used in delta sigma ADCs are explained in this section.

**Signal-to-Noise Ratio (SNR):** SNR is the ratio between signal power and the total in-band noise power. For a first order delta sigma modulator, the SNR can be derived as given in (2.3) where A is input amplitude, OSR is oversampling ratio and q is quantization level.

$$SNR = 10\log \frac{18A^2 OSR^3}{\pi^2 q^2}$$

(2.3)

This equation only covers the quantization noise. Normally, ADCs suffer from many other noise sources that decrease the SNR of delta sigma ADC. The parameter that covers all the noise and non-linearity in the design is signal to noise distortion ratio (SNDR).

**Effective Number of Bits (ENOB):** Efficient number of bits is another way to express the linearity of the delta sigma ADC in terms of resolution.

$$ENOB = \frac{SNR_{peak} - 1.76dB}{6.02dB}$$

(2.4)

**Dynamic Range (DR):** Dynamic range is about the input signal. It is the ratio of minimum detectable input signal by the modulator and maximum input signal which makes modulator stable.

**Figure of Merit (FOM):** FOM is the parameter that is a function of a few specifications of the circuit which make easier to compare the design with other designs. For delta sigma ADCs, power consumption, signal bandwidth and SNDR are taken to consideration.

$$FOM = \frac{Power}{2f_B \ge 2^{ENOB}}$$

(2.5)

### 2.3 Increasing the Performance

It is possible to increase the linearity of delta sigma ADC by increasing OSR, loop filter order and number of quantizer bits. These are explained below with considering their tradeoffs or drawbacks.

As explained in Section 2.1, oversampling is applied in delta sigma ADCs to spread the quantization noise power over the out of the band frequencies. The higher the OSR is the less will be the quantization noise power in interested band. On the other hand, higher clock frequencies are needed to satisfy higher OSR. Therefore, clock frequency limits the OSR especially in high frequency applications. This also causes extra power consumption.

The order of loop filter helps to realize sharper noise filters which increase the noise shaping effect. Therefore, SNR of the delta sigma ADC can increase with higher order. However, stability becomes important when implementing third or more order loop filters which limits the order of the loop most of time.

Another method to achieve higher SNR is to change the single bit quantizer to multi bit quantizer. For this end a 3 or 4 bit flash ADC is used instead of a comparator as quantizer. Here there are more quantization levels which decrease the quantization noise power in multi bit quantizers. However, multi bit quantizers require more complex feedback DACs and Dynamic Element Matching (DEM) as well as extra circuitry to improve its linearity. These overhead become important in the multi bit quantizer case.

#### 2.4 Delta Sigma Modulator Structures

There are three main different types of delta sigma modulators. These are feedforward, feedback and cascaded (MASH). All of them realize the same noise transfer function and signal transfer function in different ways and each offer some advantages and disadvantages.

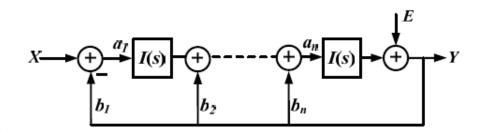

#### 2.4.1 Feedback delta sigma modulator

Figure 2.5 shows the nth order structure of feedback delta sigma modulator. I(s) blocks represent 1/s continuous time integrator blocks and E is the quantization error. In the figure "a<sub>i</sub>" coefficients are gains of integrators.

Figure 2.5: Feedback DSM Topology [4].

In feedback DSM topology, every integrator outputs are fed, which leads to large input swing. Thus, there may be some linearity problems especially for low voltage applications.

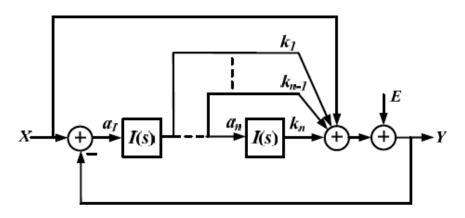

#### 2.4.2 Feed-forward delta sigma modulator

Feed-forward system solves the problem in feedback systems by feeding the quantizer input from integrator inputs so that one feedback DAC would suffice, only to the first integrator's input. This is the main advantage of the feed-forward system. Thus, internal voltage swing requirements are decreased by this architecture. Figure 2.6 shows the nth order structure of feed-forward delta sigma modulator.

Figure 2.6: Nth Order Feed-forward DSM [4].

#### 2.4.3 Cascaded delta sigma modulator (MASH)

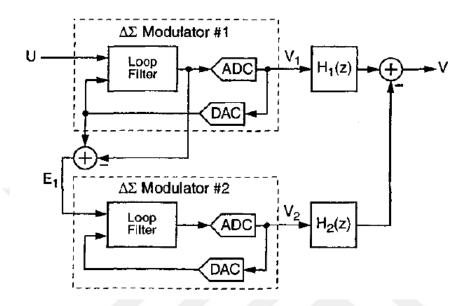

Basic structure of cascaded delta sigma modulators, also called multi stage noise shaping (MASH), can be seen in Figure 2.7. It is basically two different modulators connected together with digital filters in their outputs.

Figure 2.7: Cascaded DSM Architecture [4].

Normally in delta sigma modulators, stability becomes a big problem in high order transfer functions. On the other hand in cascaded topologies, stability is less problematic than high orders. This is the main advantages of the cascaded delta sigma modulators. The main disadvantage of MASH, it requires digital filters at the output and this increases the complexity and power consumption. Also the matching between the cascaded stages can be an issue.

#### 2.5 Implementation Considerations

System level simulations in Simulink considers only quantization errors and shows the maximum achievable SQNR. During implementation, there are some other effects that need to be considered. SNR of the delta sigma modulator suffers from the non-ideal effects in addition to quantization error such as noise, nonlinearity, metastability, excess loop delay(ELD) and finite gain, finite GBW. This effect can be modeled in system level but normally they affect the circuit in transistor level. Therefore, noise budget must be prepared and SNDR of the modulator in system level (ideal model) must satisfy the sum of needed SNR, non-ideality caused distortions and other noise sources.

#### 2.5.1 Noise

Thermal noise affects the delta sigma converter circuits such as all other electronic devices and it decreases SNR of system. Figure 2.8 shows the noise sources in a delta sigma ADC system.

Figure 2.8: Noise Elements in DSM [5].

Another effect that can be count as noise and that reduces the SNR is clock jitter. Clock jitter is the non-idealities in the clock signal such as delays, time shifts etc. It becomes more important in high frequency designs.

As an implementation problem, it is obvious that noise effects will reduce the SNR of the circuit. Therefore margin must be buit into the SNR values in ideal system simulations. Moreover to maintain some noise margin over targeted SNR value is always good.

#### 2.5.2 Nonlinearity

As explained before, quantizer is the only nonlinear block in delta sigma modulators. Quantization noise of the system has very important effect over SNR.

Another nonlinearity source is mismatches in circuit. To avoid these nonlinearities, quantizer output can be designed to have multi bits which increase the linearity and SNR. Although DAC mismatch can limit the multi bit system's SNR, calibration ways such as dynamic element matching (DEM) mitigate this limitation.

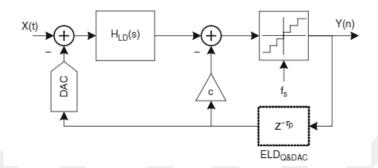

#### 2.5.3 Excess loop delay

Excess loop delay (ELD) is defined as the delay between quantizer clock edge and output change of DAC. Main reason of that is the limited speed of transistors in the quantizer and DAC. ELD causes a phase shift in the signal and this can make the system unstable.

In system level, ELD can be modelled by putting a delay between quantizer and DAC. To solve the unstability caused by ELD, a zero must be added the system to bybass the loop filter at  $F_s/2$ .

Figure 2.9 shows the additional ELD model block and c coefficient to add extra zero to compensate ELD effect. There are other compensation techniques to avoid ELD but the main idea is similar.

Figure 2.9: ELD Compansation [5].

### 2.5.4 Metastability

Quantizer output is digital and this digital output is decided by comparators or simple ADCs which also have comparators. In the high speed applications, this digital output can be resolved incorrectly by the latches of comparator due to metastability and this incorrect digital bits reduce the SQNR of the system, and increase nonlinearity.

Metastability can be modeled by adding some noise at output of the quantizer. To avoid metastability, pipeline ADCs can be used in quantizer but this also increases the latency. This delay increases the ELD and may cause unstability. Therefore, metastability must be considered in the noise budget of the system.

#### 2.5.5 Finite amplifier gain and gain-bandwidth effect

Integrators in continuous time delta sigma modulators are mostly active-RC integrators or gm-C integrators. Active-RC integrators are based on operational amplifiers and gm-C integrators are based on transconductance amplifiers. In reality both amplifiers suffer from finite gain and gain bandwidth product(GBW). Ideally pole of the integrator is in DC but in reality it is pushed away from DC through high frequencies. Non-ideal integrators are also called lossy integrators.

Since finite gain and GBW changes the integrator's transfer function, NTF and STF of the delta sigma modulator is also affected. Non-ideal effects change the shaping of filters and this reduces the SNR of the delta sigma modulator.

Decreasing these non-ideal effects is possible by using feed-forward delta sigma modulator structure.

## 3. MODEL

### 3.1 Noise Transfer Function In Discrete Time Domain

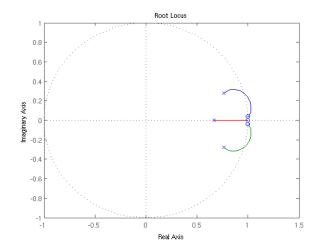

One of the most important features of delta sigma ADC is its noise shaping behavior. Quantization noise in the in-band frequencies are suppressed through the high frequencies by the noise transfer function. Therefore, first step of the delta sigma ADC design flow is to synthesize a noise transfer function. In this design, Delta-Sigma Toolbox of Richard Schreier [5] is used to synthesize a proper NTF.

Delta Sigma Toolbox is a bunch of MATLAB codes and commands that synthesizes a NTF for given specifications, simulates the synthesized NTF, calculates its SNR and calculates the implementation coefficients for the given structure and scales those coefficients.

First, synthesizeNTF command is used with proper input parameters to get a NTF (z-domain) that has above 100 dB SNR. simulateSNR command plots the SNR vs. input amplitude graph. Therefore, it can be seen checking the max. SNR whether NTF is proper or not. H(z) is the synthesized noise transfer function. Figure 3.1 shows the root locus of NTF.

$$H(z) = \frac{(z-1)(z^2-1.988z+1)}{(z-0.6992)(z^2-1.52z+0.6636)}$$

(3.1)

Figure 3.1: Root Locus of NTF.

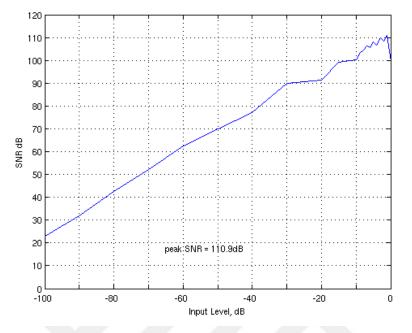

Figure 3.2 shows the SNR vs. Input Amplitude Plot. Zero optimization option of Delta Sigma Toolbox optimizes the zeros to get maximum SNR from the transfer function.

Figure 3.2: SNR vs. Input Amplitude Plot.

Last command is realizeNTF, which computes the coefficients for the CIFB structure that stands for "Cascade of Integrator, FeedBack form". z-domain coefficients of the resulting loop filter are given in Table 3.1.

| Coefficient | Value  |

|-------------|--------|

| a1          | 0.0441 |

| a2          | 0.2871 |

| a3          | 0.8005 |

| b1          | 0.0441 |

| b2=b3       | 0      |

| c1=c2=c3    | 1      |

| g1          | 0.0015 |

Table 3.1: Discrete Time Coefficients.

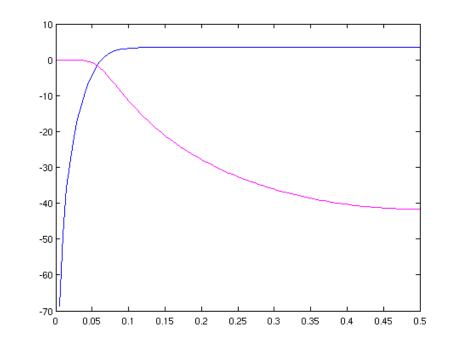

Frequency responses of the resulting NTF and STF are given in Figure 3.3. MATLAB codes of this process can be seen Appendix-A.

Figure 3.3: Frequency Response of NTF and STF.

## 3.2 DT to CT Conversation by Using Impulse Invariant Transform

After obtaining the coefficients in discrete time domain, next step is to convert them into continuous time domain. When impulse invariant transform is applied to transfer function in terms of coefficients, discrete time coefficients change by the equations given below [7].

$$\mathbf{k}_1 = \frac{\mathbf{a}_1 \mathbf{a}_2 \mathbf{a}_3}{\beta - \alpha} \tag{3.2}$$

$$k_2 = \frac{a_1 a_2 a_3}{2} \frac{\frac{2}{a_1} + \alpha + \beta - 3}{\beta - \alpha}$$

(3.3)

$$k_{3} = \frac{a_{1}a_{2}a_{3}}{12} \frac{\alpha(\alpha-9) + \beta(\beta-9) + 4\alpha\beta + \frac{6}{a_{1}}(\beta+\alpha) + \frac{12}{a_{1}}(\frac{1}{a_{2}} + a_{1} - 1)}{\beta-\alpha}$$

(3.4)

$a_1$ ,  $a_2$ ,  $a_3$  are discrete time feedback coefficients and  $k_1$ ,  $k_2$ ,  $k_3$  are continuous time versions of coefficients.  $\beta$  and  $\alpha$  are DAC pulse coefficients and they are selected as  $\beta = 1$  and  $\alpha = 0$  to satisfy the non-return to zero DAC pulse behavior. As a result the equation is simplified as seen below.

$$\mathbf{k}_1 = \mathbf{a}_1 \mathbf{a}_2 \mathbf{a}_3 \tag{3.5}$$

$$k_2 = a_1 a_2 a_3 + a_2 a_3 \tag{3.6}$$

$$k_3 = \frac{a_1 a_2 a_3}{3} + \frac{a_2 a_3}{2} + a_3 \tag{3.7}$$

Continuous time coefficients are calculated regarding to these equations and given in Table 3.2.  $b_1$  coefficient sets the gain of the loop filter. To have a gain of 1, it must be equal to the  $a_1$  coefficient. Other b and c coefficients are not changed and  $g_1$  coefficient is ignored since it needs high resistor values to be implemented.

| Coefficient | Value           0.0101 |  |

|-------------|------------------------|--|

| k1          |                        |  |

| k2          | 0.2400                 |  |

| k3          | 0.9188                 |  |

| b1          | 0.0101                 |  |

| b2=b3       | 0                      |  |

| c1=c2=c3    | 1                      |  |

Table 3.2: Continuous Time Coefficients.

In the next step, Simulink model of the delta sigma ADC is prepared by using these continuous time coefficients.

### 3.3 Simulink Model

Studying on a Simulink model before circuit implementation is always better way to design systems. Therefore, there is a Simulink model step in the design flow. Three different models of the delta sigma ADC is prepared. First model is the loop filter with ideal quantizer elements, second one is loop filter with flash ADC instead of ideal quantizer, dynamic element matching and feedback DAC, and third model is just the similar to the second one except non-ideal integrators are used in the loop filter instead of ideal integrators.

### 3.3.1 Model with ideal quantizer

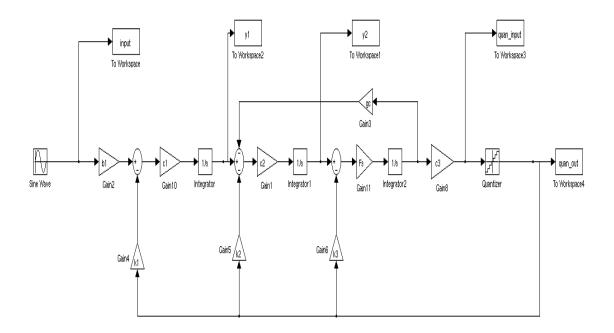

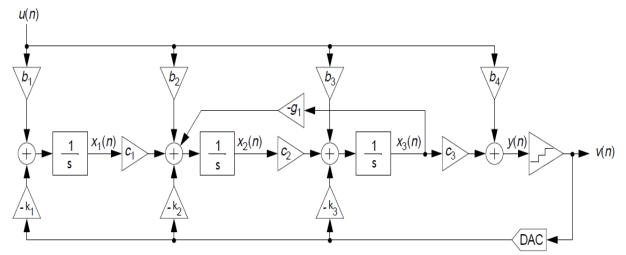

Simulink model of the delta sigma ADC is based on the CIFB structure in the Delta Sigma Toolbox of Schreier. Model consists of continuous time integrators, gain blocks and an ideal

quantizer. Integrators with gain blocks as coefficients are used to model the loop filter. Quantizer at the output sets the sampling frequency and quantization level which is 16 in this design, since the design is 5-bit output (multi bit).

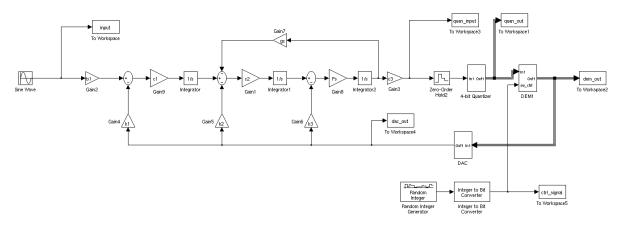

Figure 3.4 shows the Simulink model of the design. This model is simulated by a MATLAB code which is given in Appendix-B. Values of the coefficients are given at Table 3.2 above. Additional to these coefficients, blocks just in front of the integrators has the value of  $F_S$  which is sampling frequency. Since the model is not in the normalized frequency, integrators are needed to multiply by sampling frequency.

Figure 3.4: Simulink Model with Ideal Quantizer Block.

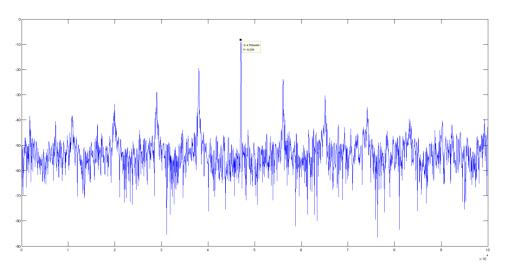

$3.6 V_{PP}$  amplitude sine wave at 33.5 kHz with 4096 samples is applied as input and signal to quantization noise ratio (SQNR) of the system is calculated by the code that is given in Appendix-B. Power spectrum density plot of the simulation result is given in Figure 3.5. It shows that SQNR is calculated as 96.2 dB and efficient number of bits (ENOB) is around 16 bits.

These results show that coefficients of the loop filter are good enough and the noise shaping is working well. In the next model, flash ADC model and feedback DACs are used instead of ideal quantizer model.

Figure 3.5: Power Spectrum Density of the First Model.

# 3.3.2 Model with flash ADC, dynamic element matching and feedback DAC

In this model, ideal quantizer is changed to have a more realistic approach. Figure 3.6 shows the new model with other elements that are zero-order hold for sampling in  $F_s$ , 4-bit quantizer for quantization in amplitude and digitalizing, dynamic element matching (DEM) for cancelling mismatch errors in real implementation and DAC to have analog signal for feedback of loop filter.

Figure 3.6: Model with Flash ADC, DEM and Feedback DACs.

In the 16-level quantizer block which is actually simple flash ADC, sampled analog signal compared by the intervals that are calculated by  $\Delta = \frac{V_{FS}}{2^{n}-1}$  where V<sub>FS</sub> is full scale voltage and n

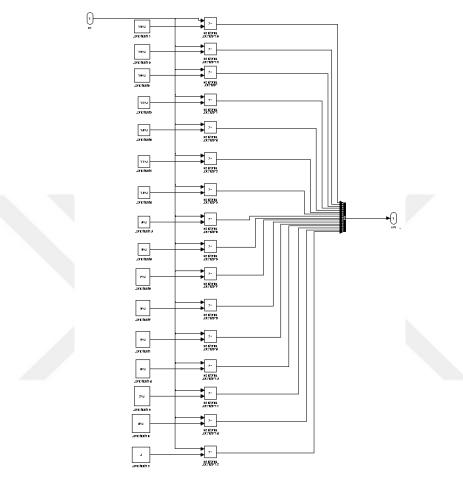

is the number of bits and produces a 16-bit thermometer coded digital output. Figure 3.7 shows the flash ADC model that is used as 4-bit quantizer. There are 16 levels in quantizer that can be considered as 5-bit. The additional bit is needed for DEM block which only works with 2n numbered bits.

Figure 3.7: 4-bit Flash ADC Simulink Model.

Signal is converted to digital by the quantizer but the loop filter is still in analog domain and feedback signals of the loop filter depends on digital output. Therefore, there has to be feedback DAC that to produce the feedback gains properly. Since the digital output is 16-bit thermometer coded, unity weighted element DAC can do the conversion. Figure 3.8 shows the simple model of the unity weighted DAC. Digital input of DAC multiplies by unity weight which is  $\Delta$  calculated above.

When implementation issues considered, mismatch in DAC elements degrades the performance of the system. To cancel the mismatch effects, dynamic element matching concept is developed. Figure 3.9 shows the model of dynamic element matching block. It

takes the thermometer coded input and changes the places of 1s and 0s. For example, 0000000011111111 is a thermometer coded signal and it may get shuffled into 00111010010011010. More detailed explanation of DEM is given in Chapter 4.

Figure 3.8: Feedback DAC Simulink Model.

Figure 3.9: Dynamic Element Matching Block.

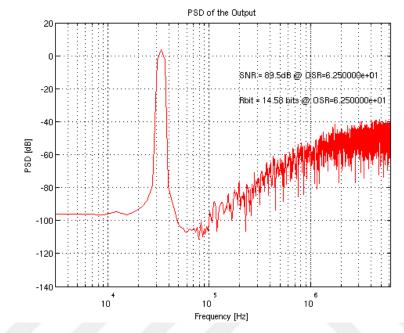

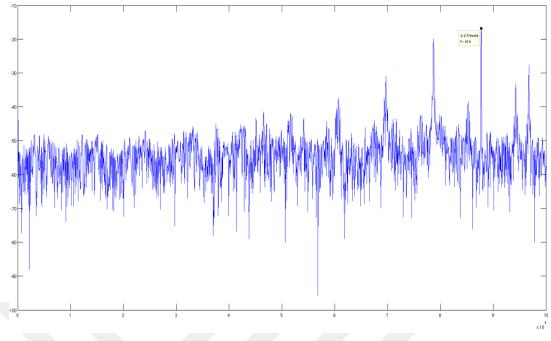

$3.6 V_{PP}$  amplitude sine wave at 33.5 kHz with 4096 samples is applied as input and signal to quantization noise ratio (SQNR) of the system is calculated as 89.5 dB and ENOB is calculated as 14.58 bits. Figure 3.10 shows the PSD of the output signal. In the first model, there was no DC at input but in this model, there is a DC value at input because of the structure of Flash ADC model. Still this model shows the noise shaping is working quite well.

Figure 3.10: Power Spectrum Density of Second Model.

### 3.3.3 Model with integrator non-idealities

In the previous models integrators were ideal integrators that their gain and bandwidth were infinite. However in real circuits, integrators have finite gain, bandwidth and slew rate. These effects also must be modelled to have an accurate model. Figure 3.11 shows the integrator model with non-ideal effects. This model is taken from the Data Converter book by Franco Maloberti [8].

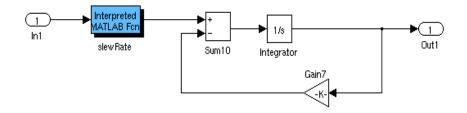

Figure 3.11: Integrator with Non-idealities.

Interepreted MATLAB Function whose code is given in Appendix-B, models the gain bandwidth product and slew rate of the integrator and the feedback part models the gain. Other blocks of the model is the same as the second model. Figure 3.12 shows the power spectral density of the modulator output with non-ideal integrator.

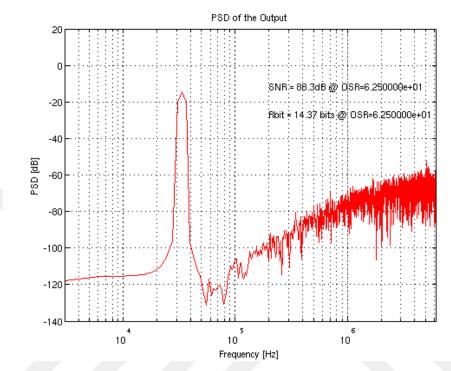

Figure 3.12: Power Spectrum Density of Third Model.

Parameters of the non-ideal integrator are selected as a gain of 1000, a GBW of 30 MHz and a slew rate of 2 V/us. These values are the expected performance specifications of the operational amplifiers in the integrators. Input amplitude is 3.6  $V_{PP}$ . Simulation results for these parameter set are given in Figure 3.12. There is 1 dB loss in SNR and if gain and GBW values are selected lower, this loss would increase.

## 3.4 Calculation of Resistor and Capacitor Values of Loop Filter

In the previous sections, NTF and STF of delta sigma ADC is designed and modeled in Simulink with additional blocks. Simulation results show that the performance of the ADC satisfies the system requirements. Next step is implementation of the system. Since it affects the performance directly by noise shaping, the most important block is the loop filter as far as implementation is concerned. Similar to the Simulink model, loop filter in schematic level is based on the integrators and feedbacks. There are many ways to realize an integrator such as active-RC, gm-C, etc. In this design, active-RC integrators are used because they are proper for resistive feedback as well as current mode feedback.

As mentioned in the first chapter, feedbacks of the loop filter are produced by current mode DACs. However, it is easy to maintain stability and other issues of the loop filter with resistive feedbacks. Therefore, first a resistive feedback structure is designed and then they are replaced with DACs that satisfy these resistor values in current mode, as shown in next section.

First of all, transfer function of third order loop filter with active-RC based integrators and feedback resistors is expressed as (3.8). Then, transfer function of Simulink model with ideal integrators and coefficients as gain blocks is determined as (3.9). After that, an equation set (3.10), (3.11) and (3.12) is found out which shows the relation between coefficients in Simulink model and resistor and capacitor values in schematic model. Lastly, resistor and capacitor values are scaled for values that suit integrated circuits better (for example, capacitors are less than 5 pF) by using this equation set.

Transfer function of the Figure 3.13 is shown in (3.8). In Figure 3.13, phases of the feedback loops are set regarding to satisfy the polarity of the equations (3.8) and (3.9). There's need to have some negativities in the equation (3.8) to get proper R and C values. This is the reason for the change in feedback polarities.

Figure 3.13: Ideal Schematic of Loop Filter.

$$\frac{V_o}{V_i} = \frac{1}{\frac{R_1}{R_{f1}} + \frac{sC_1R_1R_2}{R_{f2}} + \frac{s^2C_1C_2R_2R_3}{R_{f3}} + s^3C_1C_2C_3R_1R_2R_3}}$$

(3.8)

Transfer function of Figure 3.14 is shown in (3.9).

Figure 3.14: Loop Filter Structure.

$$\frac{V_o}{V_i} = \frac{\frac{b_1}{k_1}}{1 + \frac{s}{F_S}\frac{k_2}{k_1} + \frac{s^2}{F_S^2}\frac{k_3}{k_1} + \frac{s^3}{F_S^3}\frac{1}{k_1}}$$

(3.9)

After getting transfer functions, an equation set in (3) is obtained by equating the coefficients of the transfer functions together.

$$R_{f3}C_3 = \frac{1}{k_3 F_s} \tag{3.10}$$

$$\frac{R_{f_3}}{R_{f_2}}C_2R_2 = \frac{k_3}{k_1F_s} \tag{3.11}$$

$$\frac{R_{f_2}}{R_{f_1}}C_1R_3 = \frac{k_2}{k_1F_2} \tag{3.12}$$

Table 3.3 shows resistor and capacitor values that are calculated using the equation set above.

| Element               | Value  |

|-----------------------|--------|

| <b>R</b> <sub>1</sub> | 125 kΩ |

| R <sub>2</sub>        | 190 kΩ |

| R <sub>3</sub>        | 100 kΩ |

| R <sub>f1</sub>       | 125 kΩ |

| R <sub>f2</sub>       | 250 kΩ |

| R <sub>f3</sub>       | 250 kΩ |

| C <sub>1</sub>        | 5 pF   |

| C <sub>2</sub>        | 3 pF   |

| C <sub>3</sub>        | 300 fF |

**Table 3.3:** Resistor and Capacitor Values.

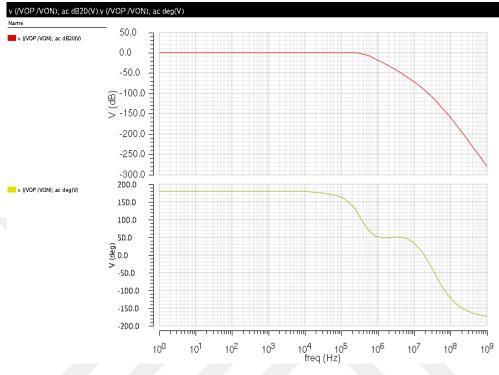

After calculating the resistor and capacitor values, AC simulation of the filter with resistive feedback loops is performed. Figure 3.15 shows the bode plot of the filter and it can be seen that the system is stable and DC gain of the system is 1.

Figure 3.15: AC Response of the Loop Filter.

Transient response of the loop filter is important to see output swing of the loop filter. However, since ideal operational amplifier model does not model the output swing limitations, transient simulation of ideal model of loop filter is not performed.

# **3.5 Ideal Circuit Model**

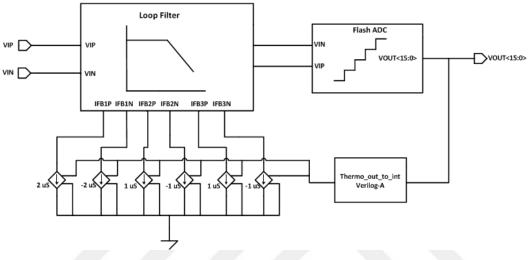

In previous section, resistor and capacitor values of the loop filter is calculated to realize the gain coefficients in Simulink model. In the real circuit, there will be current DACs instead of feedback resistors. Therefore, ideal schematic model of the whole system is necessary to implement these current DACs as feedbacks of the loop filter.

Feedback resistors are removed and a 4-bit flash ADC is added as quantizer to the output of the loop filter. Then, these thermometer coded bits are converted to analog currents by a Verilog-A code with voltage controlled current sources. These currents feed the loop filter instead of the calculated resistors. Of course, transconductance values of the dependent

current sources are calculated by dividing the voltage difference between full scale voltage and common mode voltage to the resistor values, in the equations given below in (3.14) and (3.15).

$$g_{m1} = \frac{V_{FS} - V_{CM}}{R_1} = \frac{4V - 2V}{125k\Omega} = 2 \ uS \tag{3.14}$$

$$g_{m2,3} = \frac{V_{FS} - V_{CM}}{R_{2,3}} = \frac{4V - 2V}{250k\Omega} = 1 \ uS \tag{3.15}$$

Figure 3.16 shows the ideal schematic model of delta sigma ADC.

Figure 3.16: Ideal Schematic Model.

Next, structure of sub-blocks, loop filter, flash ADC and feedback DAC, are explained.

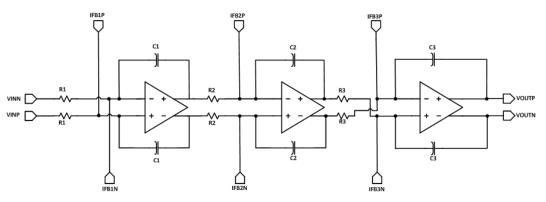

### 3.5.1 Loop filter

Schematic of loop filter similar to feedbacks resistor one explained in the previous section. The only difference is that feedbacks come from outside as currents. Figure 3.17 shows the schematic of the loop filter.

Figure 3.17: Schematic of Loop Filter.

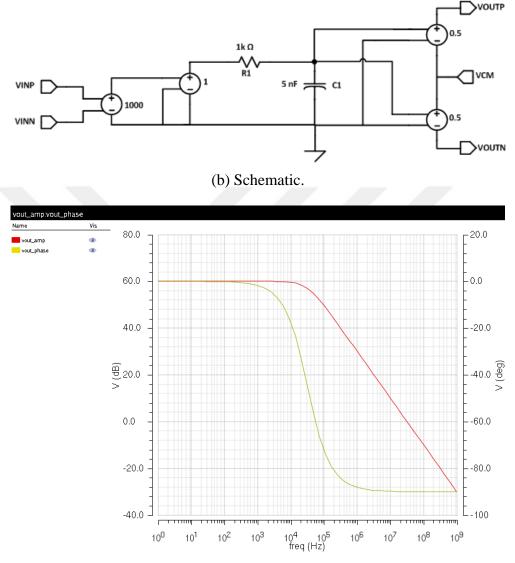

Operational amplifiers that used in loop filter are simple ideal ones that only model gain, gain-bandwidth product and differential output. Gain and bandwidth of this amplifier is set 60 dB and 30 MHz respectively, to become close to the planned specifications of real one. Figure 3.18 shows the schematic of the ideal operational amplifier model (b) and its bode plot (a).

Figure 3.18: (a) Bode Plot.

# 3.5.2 Quantizer

A simple flash ADC consists of resistor string that produce reference voltages and comparators that generate digital output bits. In the ideal schematic model of flash ADC, ideal resistors are used as voltage dividers to produce reference voltages, just like the same way with real flash ADC, and voltage controlled voltage sources are used as comparators. Input

signal is connected to plus input terminal of voltage controlled voltage source (VCVS) and reference voltages are connected to minus input terminal of VCVS the difference between input terminals are multiplied by 1000 and the output terminals of VCVS is limited by 4V and 0V. Lastly, clocked output latches sample the outputs at the  $f_s$  rate. Figure 3.19 shows the schematic of model.

Figure 3.19: Ideal Schematic of Flash ADC.

# 3.5.3 Feedback DAC

Feedback currents are produced by a Verilog-A code and voltage controlled current sources. Verilog-A code basically converts the thermometer coded digital bits into an integer and that integer is multiplied by transconcutance values of the voltage controlled current sources that determine the feedback currents. This Verilog-A code is given in Appendix-C. Transconcutance values of current sources are the same as those calculated in previous section.

# **3.5.4 Simulation results**

After full delta sigma ADC is prepared from these sub-blocks, transient simulation is run for 4096 samples, 33 kHz input sine wave that satisfies the coherent sampling with 11 period and

3.2 us for system settling time added to simulation time which is 330.88 us in total. After simulation is completed, thermometer coded output bits are summed and written into a text file. Then, this file read by MATLAB and SNR calculation is done by the MATLAB code which also used executed the Simulink model. This script is presented in Appendix-B. PSD of the simulation result is given below in Figure 3.20. More than 100 dB SQNR and 16-bit ENOB are achieved in this model. If total SNR loss due to implementation is assumed around 20 dB, it shows that this design would still satisfy the specifications.

Figure 3.20: Power Spectrum Density of Ideal Schematic Model.

# 4. SCHEMATIC

What mentioned in this report until here are only ideal blocks and their simulations. Ideal models are important to understand the system principles and avoiding fundamental problems before they affect the next steps. In this section transistor level implementation issues are investigated and circuit level design considerations are explained.

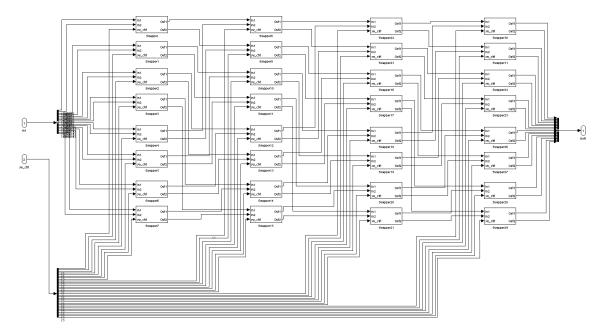

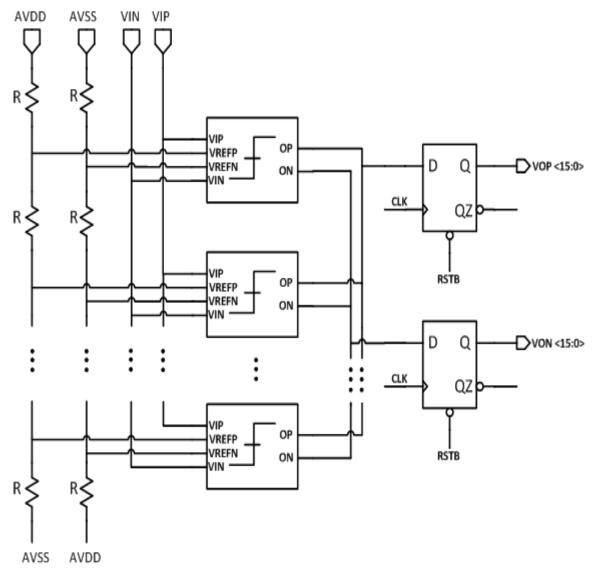

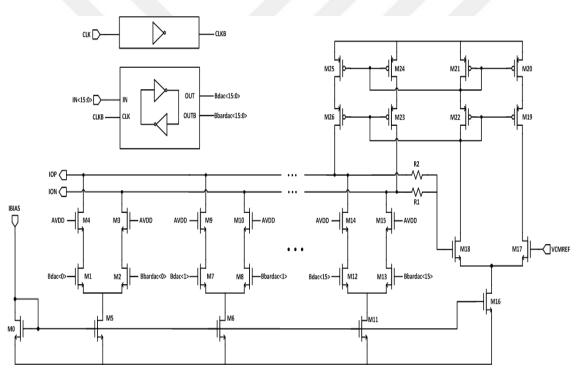

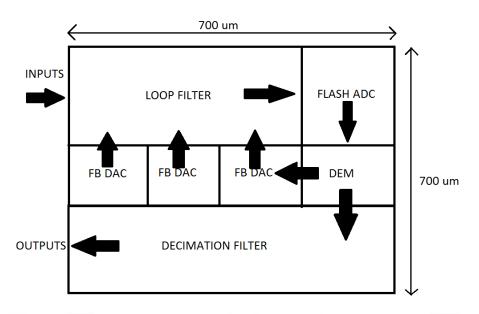

Figure 4.1 shows the top level schematic of delta sigma ADC circuit. Loop filter and flash ADC are similar to ideal circuits, the only difference is that using real circuit elements provided by the foundry instead of ideal circuit elements. Feedback DAC is also implemented with real elements in the form of current DACs. There is also dynamic element matching block just before feedback DAC to reduce the mismatch based errors of DAC. These sub-blocks are explained briefly in next sections.

Figure 4.1: Top Level Schematic of Delta Sigma ADC.

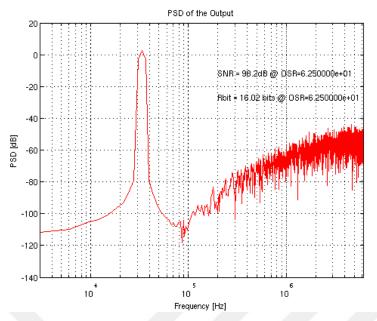

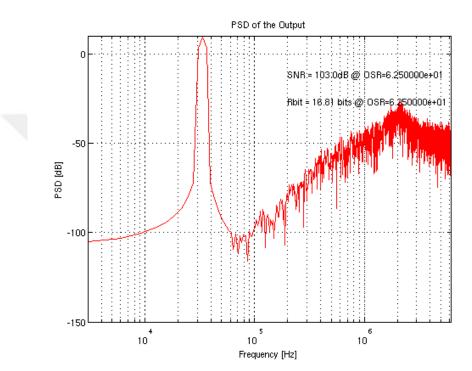

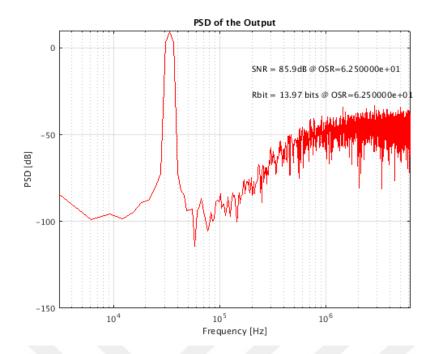

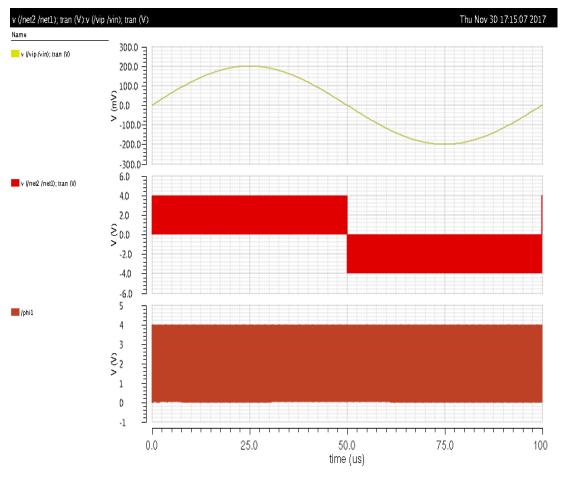

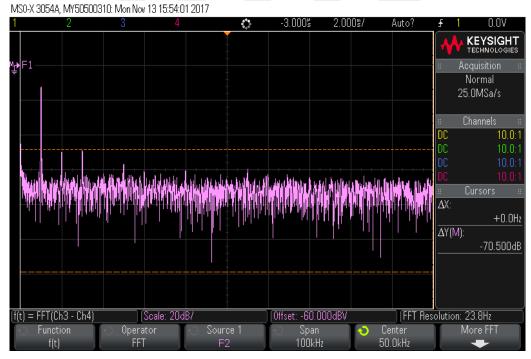

For a 3.6  $V_{PP}$  sine wave at 33 kHz frequency, power spectrum density of the output is given below in Figure 4.2. SNQR is calculated as 85.9 dB and 13.97 bits ENOB.

Figure 4.2: Power Spectrum Density of ADC Output.

# 4.1 Loop Filter

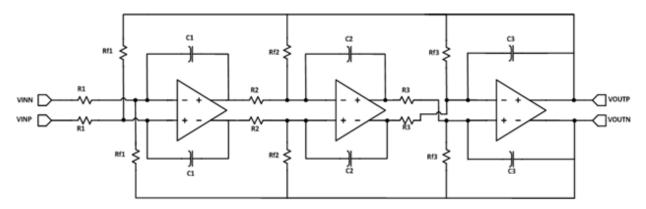

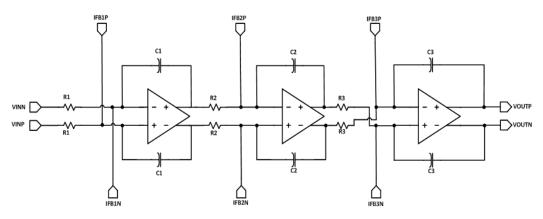

Resistor and capacitor values and calculations are given in previous chapter. These values are used in ideal block of loop filter and simulated. Here same capacitor and resistor values are used in real blocks with real resistor and capacitors and non-ideal operational amplifier. These capacitors, resistors and transistors are not ideal. Figure 4.3 shows the schematic of loop filter in current feedback configuration.

Figure 4.3: Schematic of Loop Filter.

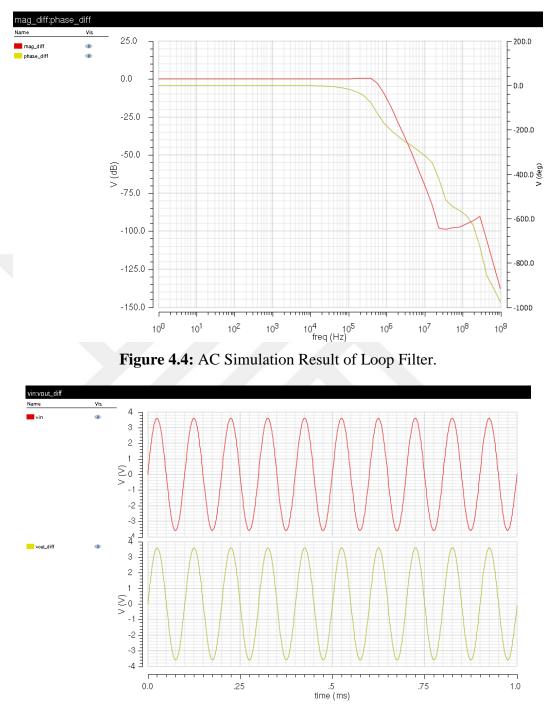

Simulation of this block has been done in resistive feedback configuration. One reason of this is that easy test setup and the other one is that both configurations are quite similar as far as stability is concerned. AC and transient simulation results of the loop filter is given in Figure 4.4 and Figure 4.5, respectively.

This Bode plot in Figure 4.4 shows that the loop is stable and DC gain is 1 as expected. The bandwidth is also more than 100 kHz which is our design bandwidth.

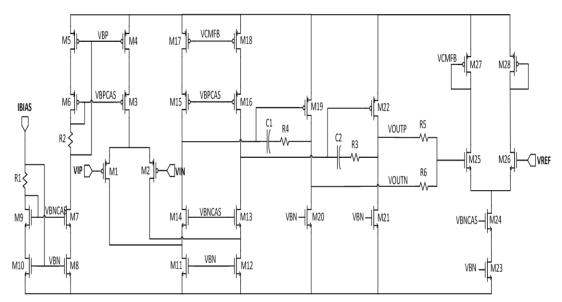

Figure 4.5: Transient Simulation Result of Loop Filter.

For transient simulation, 3.6  $V_{PP}$  and 10 kHz frequency sine wave is applied to input differentially which doubles the amplitude. The main reason of transient simulation is to see the swing at the output. There is no clipping as it can be seen. The ratio of feedback and feed-through resistor values are important to avoid clipping at the

output. Proper values are selected to satisfy both design equations and full swing at the output.

# 4.1.1 Operational amplifier

Integrators of the loop filter are implemented as active-RC integrators. Active-RC integrators are based on operational amplifiers with a feedback capacitor and a resistor at the input. To satisfy more ideal integrator behavior, DC gain and bandwidth of amplifier must be as high as possible. For delta sigma ADC applications, bandwidth must be at least twice the sampling frequency. Hence for our design a target GBW of 25-30 MHz is good enough. Amplifier gain of 80-90 dB is also proper for the integrator.

Folded cascode structure in fully differential mode with common mode feedback is preferred to satisfy previously mentioned specifications. Self-biased, high swing and high output impedance biasing circiut is used to bias the necessary nodes in amplifier and also in common mode feedback.

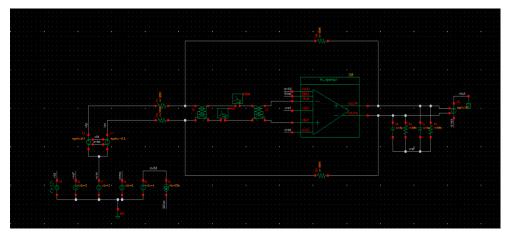

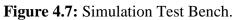

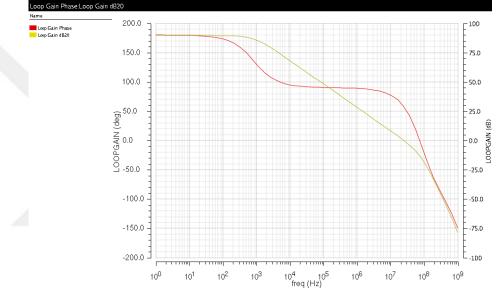

Figure 4.6 shows schematic of folded cascode operational amplifier and Figure 4.7 shows the simulation test bench. Ideal baluns and current probes are used to break feedback loop and run stability analysis. Stability and transient simulation results are given below in Figure 4.8 and Figure 4.9, respectively.

Figure 4.6: Folded Cascode Fully Differential Opamp with Common Mode Feedback.

Figure 4.8: Stability Simulation Result.

Figure 4.9: Transient Simulation Result.

#### 4.1.2 Noise analysis

In delta sigma ADCs quantization noise is the most important element that determines the performance of the ADCs. In addition, thermal and flicker noise are also important so that they may limit the total performance of the ADC.

Since loop filter is the first block that takes the analog input signal, noise performance of this block is very important. It is mentioned before that loop filter consists of three active-RC integrators and first of these integrators are designed differently from others due to its noise performance which has to be greater than second and third integrators.

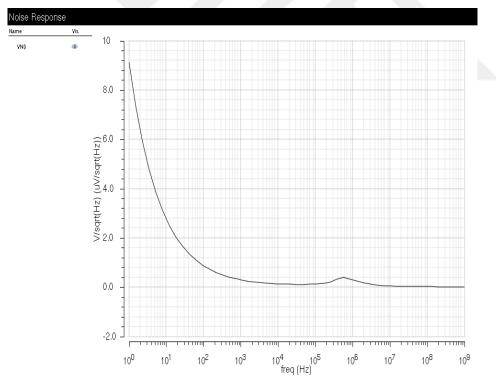

Figure 4.10 shows the input equivalent noise plot of loop filter in terms of V/sqrt(Hz). Input equivalent noise shows the noise performance of the circuit as it can be considered that there is a additional noise signal over the input signal. Simulator calculates the total output noise and divides it to transfer function of the circuit, basically.

Figure 4.10: Input Noise Equivalent Plot.

The integration of this plot over the band of interest gives the total input noise power in those interval. Noise performance of loop filter in 1 Hz - 100 kHz band is given in Figure 4.11. It shows the top sixteen noise contributors in the loop filter. They are transistors in first operational amplifier and resistors in loop filter.

| Device     | Param | Noise Contribution | % Of Total |

|------------|-------|--------------------|------------|

|            |       |                    |            |

| /I0/I0/M7  | fn    | 1.74729e-05        | 14.95      |

| /I0/I0/M6  | fn    | 1.74729e-05        | 14.95      |

| /R1        | rn    | 1.44567e-05        | 10.23      |

| /R0        | rn    | 1.44567e-05        | 10.23      |

| /I0/I0/M3  | fn    | 1.13946e-05        | 6.36       |

| /I0/I0/M2  | fn    | 1.13946e-05        | 6.36       |

| /I0/I1/M7  | fn    | 8.01195e-06        | 3.14       |

| /I0/I1/M6  | fn    | 8.01195e-06        | 3.14       |

| /I0/I0/M13 | fn    | 6.44649e-06        | 2.03       |

| /I0/I0/M11 | fn    | 6.44649e-06        | 2.03       |

| /R3        | rn    | 3.53593e-06        | 0.61       |

| /R2        | rn    | 3.53593e-06        | 0.61       |

| /I0/I0/M7  | id    | 3.17513e-06        | 0.49       |

| /I0/I0/M6  | id    | 3.17513e-06        | 0.49       |

| /I0/I0/M2  | id    | 2.80936e-06        | 0.39       |

| /I0/I0/M3  | id    | 2.80936e-06        | 0.39       |

|            |       |                    |            |

Integrated Noise Summary (in V) Sorted By Noise Contributors Total Summarized Noise = 4.51966e-05 Total Input Referred Noise = 4.51051e-05 The above noise summary info is for noise data

### Figure 4.11: Noise Analysis Summary.

Total input referred noise is  $4.51051 \times 10^{-5}$  V/sqrt(Hz) from Figure 4.11. It is converted to dB by the Equation 4.1.

$$20 \times \log(4.51051 \times 10^{-5}) = -86.9 \, dB \tag{4.1}$$

This can give some idea about the noise floor of the design. Since the main goal of the design is to have total noise (quantization, thermal and flicker) and distortion level is about 80 dB, this value of thermal and flicker noise can be acceptable.

### 4.2 Quantizer

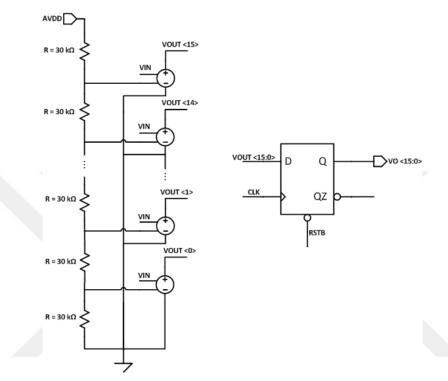

In a single-bit delta sigma ADCs, one comparator is enough at the output since there only need for two logic levels basically 1 and 0. However in multi-bit delta sigma ADCs, additional bits at the output increase the SQNR. Therefore if it is proper for the system, multi-bit designs are chosen. This design is also a multi-bit delta sigma ADC whose output has 16 logic level. To achieve this in an easy way, a simple flash ADC is used.

Flash ADCs produce thermometer coded bits and normally those bits are converted to binary coded bits. However, for this delta sigma ADC, there is no need to convert thermometer bits to binary coded bits, since thermometer coded bits are going to be used in feedback DACs.

Figure 4.12 shows the schematic view of the flash ADC. It is simple flash ADC with resistor string for references, comparators for digitizing and output latches to have logic values. The only difference of this flash ADC is its fully differential architecture. Fully differential architecture doubles  $V_{FS}$  and increases SNR by 3 dB, to yield better CMRR and noise immunity. However it also needs fully differential comparators and more resistors as drawback.

Figure 4.12: Schematic of Flash ADC.

Since the flash is fully differential there are two resistor strings for negative and positive references, resistor values are the same but the only differences is that positive string biased AVDD at the top and AVSS at the bottom and the negative one is vice versa.

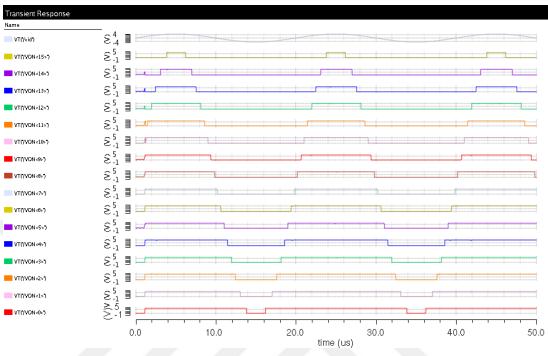

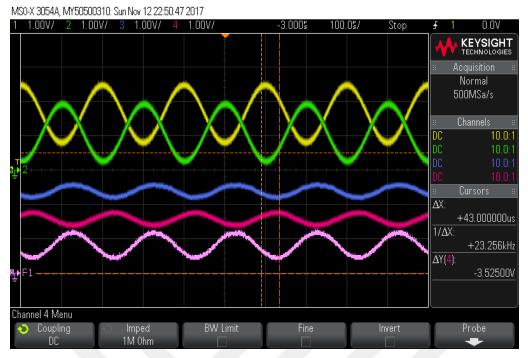

For 3.8 VPP amplitude and 50 kHz frequency differential sine wave signal applied to input and flash ADC is simulated. Output bits of flash ADC is shown in Figure 4.13 as differential. Simulation results shows that the flash ADC works very well.

Figure 4.13: Simulation Result of Flash ADC.

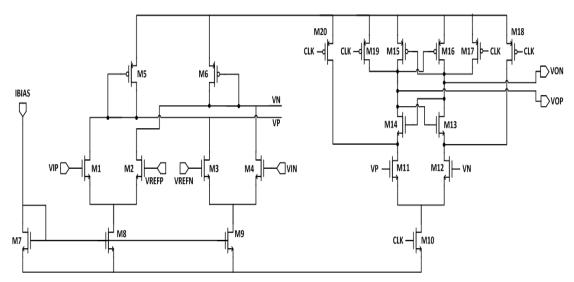

# 4.2.1 Fully differential comparator

As mentioned previously, fully differential comparators are needed for fully differential flash ADC architectures. Schematic of fully differential comparator is given below in Figure 4.14. It is a pre-amplifier and latch based comparator with double balanced fully differential input stage.

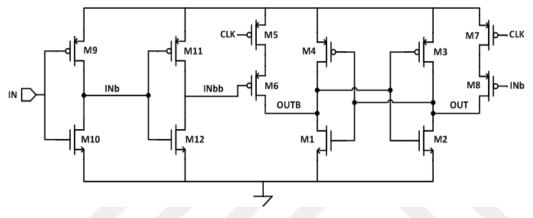

Figure 4.14: Schematic of Fully Differential Comparator.

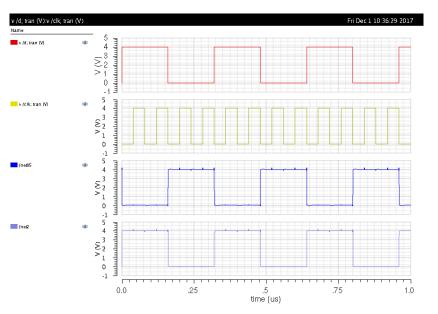

Razavi's modified storgARM latch is used in this comparator to produce the logic values at the output. The main advantage of this latch is that it does not consume any static power. M11 and M12 switches stop the input propagation during the regeneration phase. Latch also works well with active pull up switch.

Simulations are repeated for various reference voltages which are similar to the flash ADC working principle. However, references set to 2V and 100 mV as a differential input signal at 10 kHz frequency is applied for the simulation results given above in Figure 4.15. Output signal of the comparator is also differential as it changes between 4V to -4V as it can be seen from the figure.

Figure 4.15: Simulation Result of Comparator.

Simulations are repeated for various reference voltages which are similar to the flash ADC working principle. However, references set to 2V and 100 mV as a differential input signal at 10 kHz frequency is applied for the simulation results given above in Figure 4.15. Output signal of the comparator is also differential as it changes between 4V to -4V as it can be seen from the figure.

The problem with this comparator is that its latch at the output does not hold the signal its value while in regeneration phase. In other words, the output signal goes to common mode voltage during regeneration phase because of the switch in the latch. Therefore another latch with opposite clock phase is needed to hold the logic bit values during regeneration phase.

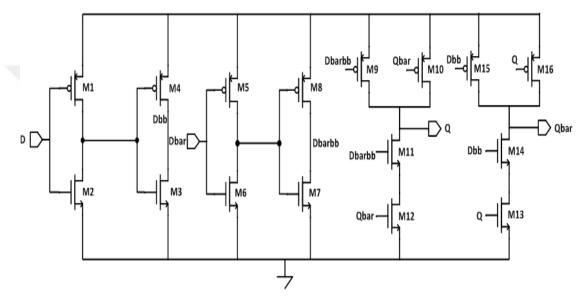

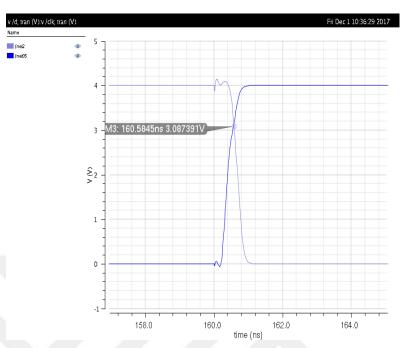

### 4.2.2 Output latch

A simple output latch is used to solve the problem mentioned in the previous section. It is actually a NAND based D latch and its schematic is shown in Figure 4.16.

Figure 4.16: Output Latch of Flash ADC.

Output latch works with the inverted clock of the comparator. Therefore, latch in the comparator and this output latch can be considered as an edge sensitive flip flop together.

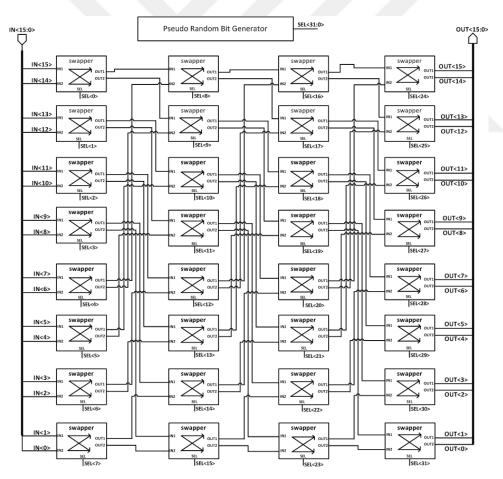

#### **4.3 Dynamic Element Matching**

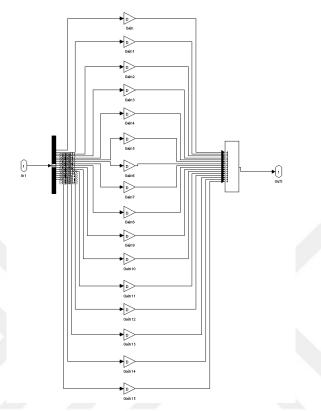

In unit weighted DACs, mismatches between DAC cells decrease the linearity of the converter. There are some techinques developed to reduce or to cancel these mismatch based effects. If same DAC cells are active most of the time, their mismatch become more dominant. However, if some techniques are applied to spread the active DAC cells over time, then some mismatches can cancel each other and the average mismatch of the DAC cells reduce. These techniques are called dynamic element matching in a general way.

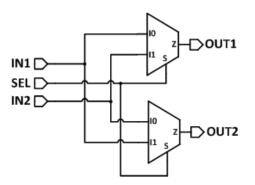

In delta sigma ADCs, multi-bit output designs suffers from DAC mismatch because they need unit element feedback DAC. Since this is a 4-bit design and there is a 16bit thermometer coded flash ADC output that is fed back to DACs, there's needs for a dynamic element matching block to spread the active bits over the 16 bit signal.

Figure 4.17 shows the scrambling type of dynamic element matching systems. Butterfly connected swappers whose select signal is coming from a randomizer is used. Random bit generator produces 32-bit random bits for 32 swappers' select signals which decide that data will flow wheter one way or the other. For example, if the 16-bit thermometer coded data at the input is 0000000111111111, data at the output can be 1101011011000101 or some other randomly shuffled version of the ADC thermal encoded output. The difference between words doesn't matter for unity weighted DACs as long as the total number of 1s and 0s are equal to each other.

Figure 4.17: Dynamic Element Matching.