T.C.

## ISTANBUL AYDIN UNIVERSITY

## INSTITUTE OF NATURAL AND APPLIED SCIENCES

## NEW CONTROL METHOD FOR DUAL VOLTAGE RECTIFIER

M.Sc. THESIS

Engr. Rai Muhammad Omar

**Department of Electrical and Electronics Engineering**

**Electrical and Electronics Engineering Program**

September 2019

T.C.

# ISTANBUL AYDIN UNIVERSITY

# INSTITUTE OF NATURAL AND APPLIED SCIENCES

## NEW CONTROL METHOD FOR DUAL VOLTAGE RECTIFIER

**M.Sc. THESIS**

Engr. Rai Muhammad Omar

(Y1713.300009)

**Department of Electrical and Electronics Engineering**

**Electrical and Electronics Engineering Program**

Advisor: Professor Dr. MURTAZA FARSADİ

September 2019

#### T.C. İSTANBUL AYDIN ÜNİVERSİTESİ FEN BİLİMLER ENSTİTÜSÜ MÜDÜRLÜĞÜ

# Yüksek Lisans Tez Onay Belgesi

Enstitümüz Elektrik- Elektronik Mühendisliği Ana Bilim Dalı Elektrik- Elektronik Mühendisliği (İngilizce) Tezli Yüksek Lisans Programı Y1713.300009 numaralı öğrencisi Raı Muhammad OMAR'ın "NEW CONTROL METHOD FOR DUAL VOLTAGE RECTIFIER" adlı tez çalışması Enstitümüz Yönetim Kurulunun 11.09.2019 tarih ve 2019/18 sayılı kararıyla oluşturulan jüri tarafından (Y. Li Elektronik Lisans tezi olarak

#### Öğretim Üyesi Adı Soyadı

İmzası

Tez Savunma Tarihi : 27/09/2019

1)Tez Danışmanı: Prof. Dr. Murtaza FARSADI

2) Jüri Üyesi : Prof. Dr. Ayşen DEMİRÖREN

3) Jüri Üyesi : Dr. Öğr. Üyesi Eylem Gülce ÇOKER

Not: Öğrencinin Tez savunmasında **Başarılı** olması halinde bu form imzalanacaktır. Aksi halde geçersizdir.

## DECLARATION

I hereby declare that all information in this thesis document has been obtained and presented in accordance with academic rules and ethical conduct. I also declare that, as required by these rules and conduct, I have fully cited and referenced all material and results, which are not original to this thesis.

### Engr. Rai Muhammad Omar

## FOREWORD

After thanks to Allah our creator, I would like to thank my mother and my father who raised me to become a good person. They were patient during my mistakes and my bad times and helped me in all times and everything I have accomplished is because of their effort. I hope I can make them happy and return even some of what they gave me during their whole lives.

I would like to thank my thesis advisor Prof Dr. MURATZA FARSADİ for his guidance, support, and help during my work in the thesis. I thank him for everything I learned from him.

I thank all my teachers starting from my school time until today as they had great influence on me and made me love education and I hope I can become one day a good teacher as they were

September 2019

Engr. Rai Muhammad Omar

(Electrical and Electronics Engineering)

# TABLE OF CONTENT

| DODDWODD                                                                                                                  | Page<br> |

|---------------------------------------------------------------------------------------------------------------------------|----------|

| FOREWORD                                                                                                                  |          |

| TABLE OF CONTENT.                                                                                                         |          |

| ABBREVIATIONS                                                                                                             |          |

| LIST OF FIGURES                                                                                                           |          |

| LIST OF TABLES                                                                                                            |          |

| ABSTRACT                                                                                                                  |          |

| ÖZET                                                                                                                      |          |

| 1 INTRODUCTION                                                                                                            |          |

| 1.1 Problem Definition                                                                                                    |          |

| 1.2 Non-Isolated Converter                                                                                                |          |

| 1.3 Isolated Converter                                                                                                    | 4        |

| 1.4 AC to DC Converters                                                                                                   |          |

| 1.5 DC-DC Converters                                                                                                      | 5        |

| 1.5.1 Buck Converter                                                                                                      | 5        |

| 1.5.2 Boost Converter                                                                                                     | 7        |

| 1.5.3 Buck-Boost Converter:                                                                                               | 9        |

| 2 MAIN CIRCUIT AND PROPOSED DESIGN                                                                                        | 13       |

| 2.1 Voltage Conversion of a Conventional Two-Stage AC to DC Conver                                                        | ter 13   |

| 2.2 Voltage Conversion of Proposed Circuit                                                                                | 14       |

| 2.3 Topologies of Dual Voltage Rectifier & DC-DC transformer                                                              | 16       |

| 2.4 LLC Resonant Converter                                                                                                | 17       |

| 2.5 Analysis of the Proposed AC to DC Converter                                                                           | 17       |

| 2.6 Operational Modes of Dual Voltage Rectifier                                                                           | 18       |

| 2.7 VHi Single-Output Mode                                                                                                | 18       |

| 2.8 VLow Single Output Mode                                                                                               | 18       |

| 2.9 VLow and VHi Dual Output Mode                                                                                         | 19       |

| 2.10Operation Mode Consideration                                                                                          | 20       |

| 2.11Relationship Between the Power Ratio and Phase Angle <b>0L</b>                                                        | 22       |

| 3 CONTROL SCHEME                                                                                                          | 29       |

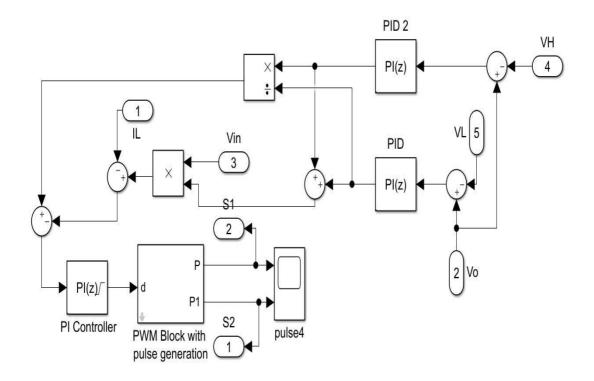

| 3.1 PWM Control Strategy                                                                                                  |          |

| 3.2 Pulse Width Modulation (PWM) Technique & Smooth Mode Transit<br>Based on Voltage-Second Balance Principle of Inductor | tion     |

|        | 3.3 Comparative Analysis                       | 35 |

|--------|------------------------------------------------|----|

|        | 3.4 Fuzzy Logic Controller                     | 39 |

|        | 3.5 Fuzzy Logic Controller for Boost Converter | 41 |

|        | 3.6 Analytical Expressions                     | 41 |

|        | 3.7 Fuzzy Logic Membership Function            | 41 |

|        | 3.8 Fuzzy Logic Table Rules                    | 43 |

| 4      | EXPERIMENTAL RESULTS                           | 45 |

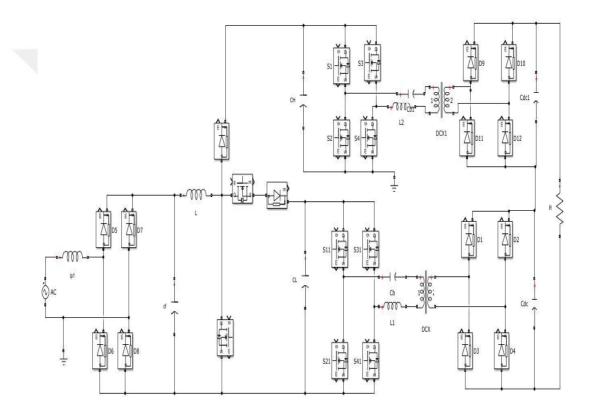

|        | 4.1 Main Circuit                               | 45 |

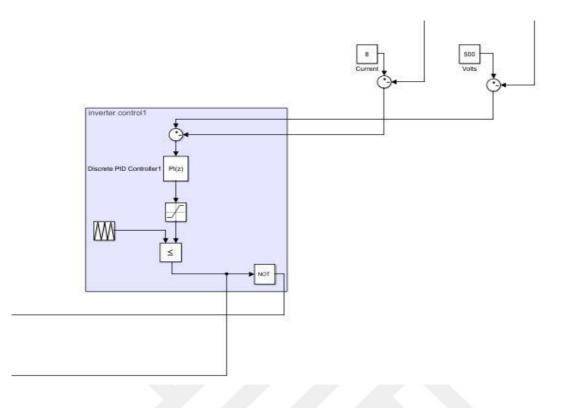

|        | 4.2 LLC Resonant Circuit & Control Circuit     | 46 |

|        | 4.3 PWM Controller                             | 46 |

|        | 4.3.1 Graphs                                   | 47 |

|        | 4.4 Fuzzy Logic Controller for DV-Rectifier    | 50 |

|        | 4.5 Fuzzy Logic Control Scheme                 |    |

|        | 4.5.1 Graphs                                   | 51 |

| 5      | CONCLUSION AND FUTURE WORK                     | 55 |

|        | 5.1 Discussion and Conclusion                  | 55 |

|        | 5.2 Future Work                                | 57 |

| RE     | FERENCES                                       | 59 |

| RESUME |                                                |    |

|        |                                                |    |

# ABBREVIATIONS

| BJT<br>ce<br>D1<br>D2<br>DV<br>e | <ul> <li>Bipolar Junction Transistor</li> <li>Change of Error</li> <li>Diode 1</li> <li>Diode 2</li> <li>Dual Voltage</li> <li>error</li> </ul> |

|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| FLC                              | : Fuzzy Logic Controller                                                                                                                        |

| L                                | : Inductor                                                                                                                                      |

| LLC                              | : Inductor Inductor Capacitor                                                                                                                   |

| NB                               | : Negative Big                                                                                                                                  |

| NS                               | : Negative Small                                                                                                                                |

| PB                               | : Positive Big                                                                                                                                  |

| PFC                              | : Power Factor Correction                                                                                                                       |

| PID                              | : Proportional Integral Derivative                                                                                                              |

| PWM                              | : Pulse Width Modulation                                                                                                                        |

| <b>S</b> <sub>1</sub>            | : Switch 1                                                                                                                                      |

| S <sub>2</sub>                   | : Switch 2                                                                                                                                      |

| SM                               | : Single Output Mode                                                                                                                            |

| SPTT                             | : Single Pole Triple Throw                                                                                                                      |

| V <sub>AB</sub>                  | : Voltage between point A and B                                                                                                                 |

| v <sub>c1</sub>                  | : Voltage across Capacitor 1                                                                                                                    |

| v <sub>c2</sub>                  | : Voltage across Capacitor 2                                                                                                                    |

| w.r.t                            | : With Respect To                                                                                                                               |

# LIST OF FIGURES

| Figure 1.1 Block Diagram of AC to DC Converter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4                                                                                         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|

| Figure 1.2 Simple Buck-Converter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 6                                                                                         |

| Figure 1.3 Buck Regulator Characteristics.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 6                                                                                         |

| Figure 1.4 Simple Boost Converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 8                                                                                         |

| Figure 1.5 Boost Converter Characteristics.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 8                                                                                         |

| Figure 1.6 Simple Buck-Boost Design.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 9                                                                                         |

| Figure 1.7 Buck-Boost Characteristics.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 10                                                                                        |

| Figure 2.1 Conventional Two Stage AC to DC Converter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 14                                                                                        |

| Figure 2.2 Proposed DV Rectifier Block Diagram.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                           |

| Figure 2.3 Different Types of Boost Topologies.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 16                                                                                        |

| Figure 2.4 LLC Resonant Converter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 17                                                                                        |

| Figure 2.5 Block Diagram of Proposed AC to DC Converter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                           |

| Figure 2.6 VHi Single Output Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 18                                                                                        |

| Figure 2.7 VLo Single Output Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 19                                                                                        |

| Figure 2.8 VLo and VHi Dual Output Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 20                                                                                        |

| Figure 2.9 Operation Region of VLo-SM and DOM.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                           |

| Figure 2.10 Optimized Scheme of Mode Selection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 22                                                                                        |

| <b>Figure 2.11</b> Curves of <i>kpow</i> with respect to (a) $\theta$ L and (b) sin( $\theta$ L)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                           |

| <b>Figure 2.12</b> Curves of $\theta L_solu$ and $\sin(\theta L_solu)$ with respect VL, (a) curves of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | f                                                                                         |

| $\theta L$ solu and (b) curves of $\sin(\theta L$ solu)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 26                                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                           |

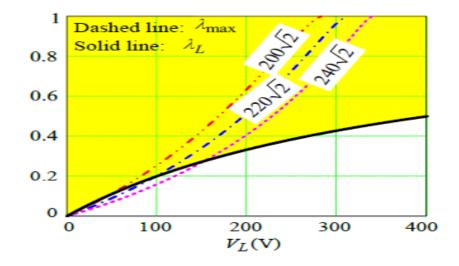

| <b>Figure 2.13</b> Curve of the Maximum Power Ratio $\lambda max$ and $\lambda L$ Versus the Volt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | tage                                                                                      |

| <b>Figure 2.13</b> Curve of the Maximum Power Ratio $\lambda max$ and $\lambda L$ Versus the Volt <i>VLo</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | U                                                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 27                                                                                        |

| VLo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 27<br>30                                                                                  |

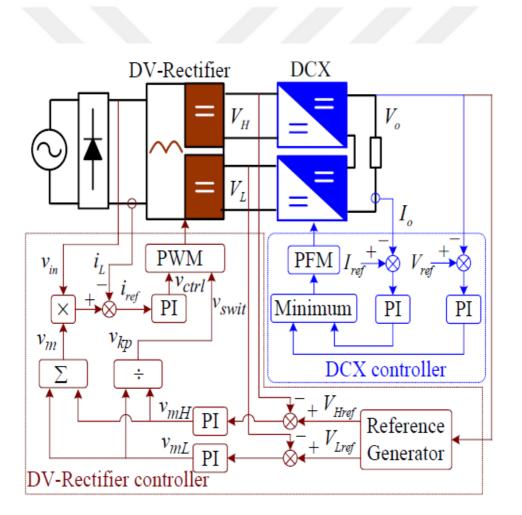

| <i>VLo</i><br>Figure 3.1 Control Block Diagram of Proposed DV-Converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 27<br>30<br>tween                                                                         |

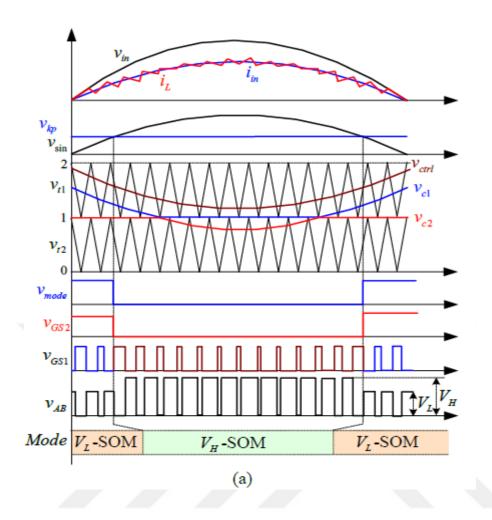

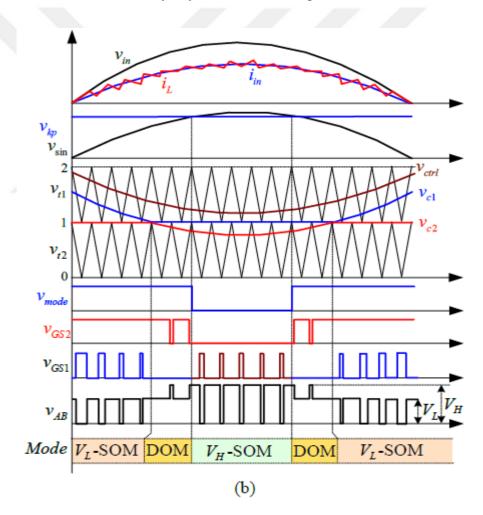

| <ul> <li><i>VLo</i></li> <li>Figure 3.1 Control Block Diagram of Proposed DV-Converter</li> <li>Figure 3.2 Key Waveforms of the PWM Strategy with (a) Mode Switching Be</li> <li><i>VL</i>-SOM and <i>VH</i>-SOM</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 27<br>30<br>tween<br>32                                                                   |

| <ul><li><i>VLo</i></li><li>Figure 3.1 Control Block Diagram of Proposed DV-Converter</li><li>Figure 3.2 Key Waveforms of the PWM Strategy with (a) Mode Switching Be</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 27<br>30<br>tween<br>32<br>33                                                             |

| <ul> <li>VLo</li> <li>Figure 3.1 Control Block Diagram of Proposed DV-Converter</li> <li>Figure 3.2 Key Waveforms of the PWM Strategy with (a) Mode Switching Be</li> <li>VL-SOM and VH-SOM</li> <li>Figure 3.3(b) Mode Switching Between DOM and VH-SOM</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 27<br>30<br>tween<br>32<br>33<br>34                                                       |

| <ul> <li>VLo</li> <li>Figure 3.1 Control Block Diagram of Proposed DV-Converter.</li> <li>Figure 3.2 Key Waveforms of the PWM Strategy with (a) Mode Switching Be</li> <li>VL-SOM and VH-SOM.</li> <li>Figure 3.3(b) Mode Switching Between DOM and VH-SOM.</li> <li>Figure 3.4 Equivalent Circuit of the DV-Rectifier in One Switching Cycle.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                      | 27<br>30<br>tween<br>32<br>33<br>34<br>40                                                 |

| <ul> <li>VLo</li> <li>Figure 3.1 Control Block Diagram of Proposed DV-Converter</li> <li>Figure 3.2 Key Waveforms of the PWM Strategy with (a) Mode Switching Be</li> <li>VL-SOM and VH-SOM</li> <li>Figure 3.3(b) Mode Switching Between DOM and VH-SOM.</li> <li>Figure 3.4 Equivalent Circuit of the DV-Rectifier in One Switching Cycle</li> <li>Figure 3.5 FLC Strategy</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                        | 27<br>30<br>tween<br>32<br>33<br>34<br>40<br>42                                           |

| <ul> <li>VLo</li> <li>Figure 3.1 Control Block Diagram of Proposed DV-Converter.</li> <li>Figure 3.2 Key Waveforms of the PWM Strategy with (a) Mode Switching Be</li> <li>VL-SOM and VH-SOM.</li> <li>Figure 3.3(b) Mode Switching Between DOM and VH-SOM.</li> <li>Figure 3.4 Equivalent Circuit of the DV-Rectifier in One Switching Cycle.</li> <li>Figure 3.5 FLC Strategy.</li> <li>Figure 3.6 The Membership Functions Plot of Error.</li> </ul>                                                                                                                                                                                                                                                                                                                        | 27<br>30<br>tween<br>32<br>33<br>34<br>40<br>42<br>42                                     |

| <ul> <li>VLo</li> <li>Figure 3.1 Control Block Diagram of Proposed DV-Converter.</li> <li>Figure 3.2 Key Waveforms of the PWM Strategy with (a) Mode Switching Be</li> <li>VL-SOM and VH-SOM.</li> <li>Figure 3.3(b) Mode Switching Between DOM and VH-SOM.</li> <li>Figure 3.4 Equivalent Circuit of the DV-Rectifier in One Switching Cycle.</li> <li>Figure 3.5 FLC Strategy.</li> <li>Figure 3.6 The Membership Functions Plot of Error.</li> <li>Figure 3.7 The Membership Function Plots of Change Error.</li> </ul>                                                                                                                                                                                                                                                     | 27<br>30<br>tween<br>32<br>33<br>34<br>40<br>42<br>42<br>43                               |

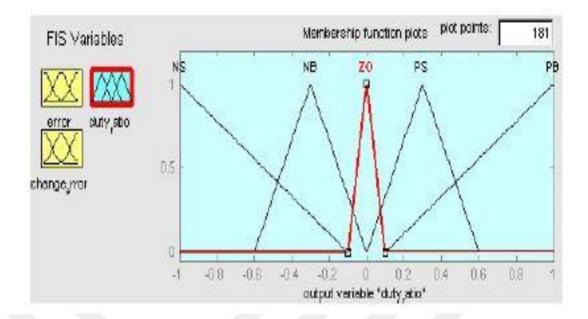

| <ul> <li>VLo</li> <li>Figure 3.1 Control Block Diagram of Proposed DV-Converter</li> <li>Figure 3.2 Key Waveforms of the PWM Strategy with (a) Mode Switching Be</li> <li>VL-SOM and VH-SOM</li> <li>Figure 3.3(b) Mode Switching Between DOM and VH-SOM</li> <li>Figure 3.4 Equivalent Circuit of the DV-Rectifier in One Switching Cycle</li> <li>Figure 3.5 FLC Strategy</li> <li>Figure 3.6 The Membership Functions Plot of Error</li> <li>Figure 3.7 The Membership Function Plots of Change Error</li> <li>Figure 3.8 The Membership Function Plots of Duty Ratio</li> </ul>                                                                                                                                                                                            | 27<br>30<br>tween<br>32<br>33<br>34<br>40<br>42<br>42<br>43<br>45                         |

| <ul> <li>VLo</li> <li>Figure 3.1 Control Block Diagram of Proposed DV-Converter.</li> <li>Figure 3.2 Key Waveforms of the PWM Strategy with (a) Mode Switching Be</li> <li>VL-SOM and VH-SOM.</li> <li>Figure 3.3(b) Mode Switching Between DOM and VH-SOM.</li> <li>Figure 3.4 Equivalent Circuit of the DV-Rectifier in One Switching Cycle.</li> <li>Figure 3.5 FLC Strategy.</li> <li>Figure 3.6 The Membership Functions Plot of Error.</li> <li>Figure 3.7 The Membership Function Plots of Change Error.</li> <li>Figure 3.8 The Membership Function Plots of Duty Ratio.</li> <li>Figure 4.1 Complete Circuit Diagram Of DV-Rectifier</li> </ul>                                                                                                                       | 27<br>30<br>tween<br>32<br>33<br>34<br>40<br>42<br>43<br>45<br>46                         |

| <ul> <li>VLo.</li> <li>Figure 3.1 Control Block Diagram of Proposed DV-Converter.</li> <li>Figure 3.2 Key Waveforms of the PWM Strategy with (a) Mode Switching Be</li> <li>VL-SOM and VH-SOM.</li> <li>Figure 3.3(b) Mode Switching Between DOM and VH-SOM.</li> <li>Figure 3.4 Equivalent Circuit of the DV-Rectifier in One Switching Cycle.</li> <li>Figure 3.5 FLC Strategy.</li> <li>Figure 3.6 The Membership Functions Plot of Error.</li> <li>Figure 3.7 The Membership Function Plots of Change Error.</li> <li>Figure 3.8 The Membership Function Plots of Duty Ratio.</li> <li>Figure 4.1 Complete Circuit Diagram Of DV-Rectifier</li> <li>Figure 4.2 LLC Resonant Converter Control Strategy .</li> </ul>                                                        | 27<br>30<br>tween<br>32<br>33<br>34<br>40<br>42<br>42<br>43<br>45<br>46                   |

| <ul> <li>VLo</li> <li>Figure 3.1 Control Block Diagram of Proposed DV-Converter.</li> <li>Figure 3.2 Key Waveforms of the PWM Strategy with (a) Mode Switching Be</li> <li>VL-SOM and VH-SOM.</li> <li>Figure 3.3(b) Mode Switching Between DOM and VH-SOM.</li> <li>Figure 3.4 Equivalent Circuit of the DV-Rectifier in One Switching Cycle.</li> <li>Figure 3.5 FLC Strategy.</li> <li>Figure 3.6 The Membership Functions Plot of Error.</li> <li>Figure 3.7 The Membership Function Plots of Change Error.</li> <li>Figure 3.8 The Membership Function Plots of Duty Ratio.</li> <li>Figure 4.1 Complete Circuit Diagram Of DV-Rectifier</li> <li>Figure 4.2 LLC Resonant Converter Control Strategy</li> <li>Figure 4.3 PWM Control Circuit for DV-Rectifier.</li> </ul> | 27<br>30<br>tween<br>32<br>33<br>34<br>40<br>42<br>42<br>43<br>45<br>46<br>46<br>47       |

| <ul> <li>VLo</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 27<br>30<br>tween<br>32<br>33<br>34<br>40<br>42<br>42<br>42<br>43<br>45<br>46<br>46<br>47 |

| Figure 4.8 Output Current and Voltage Graph when Vin is 230V and 60Hz        |     |

|------------------------------------------------------------------------------|-----|

| Frequency                                                                    | 49  |

| Figure 4.9 Output Current and Voltage Graph when Vin is 230V and 50Hz        |     |

| Frequency                                                                    | 49  |

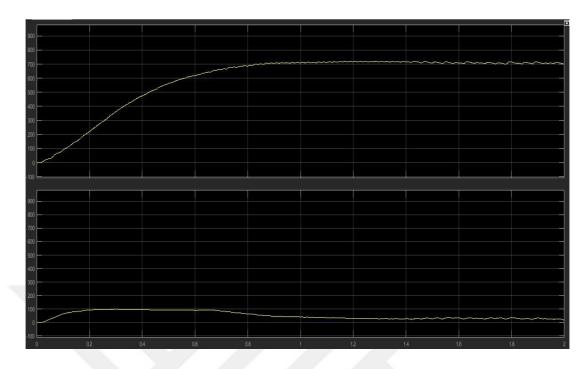

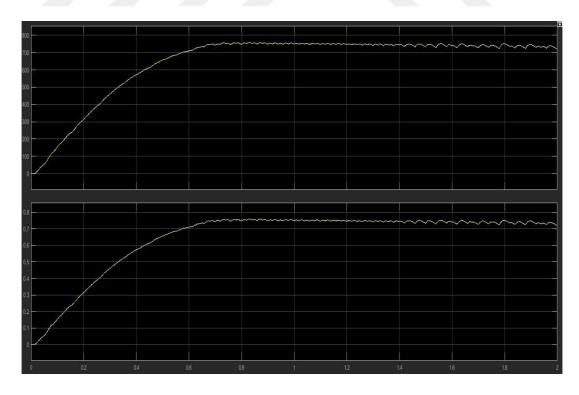

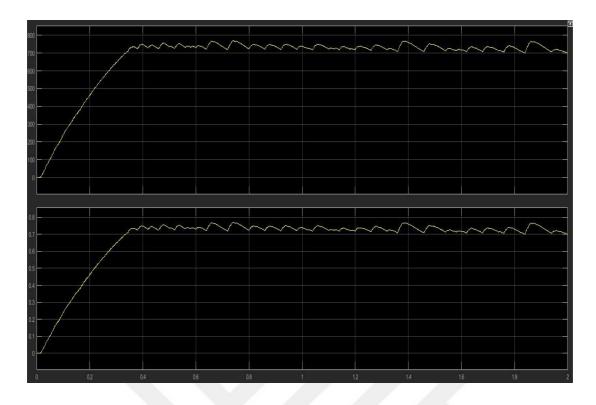

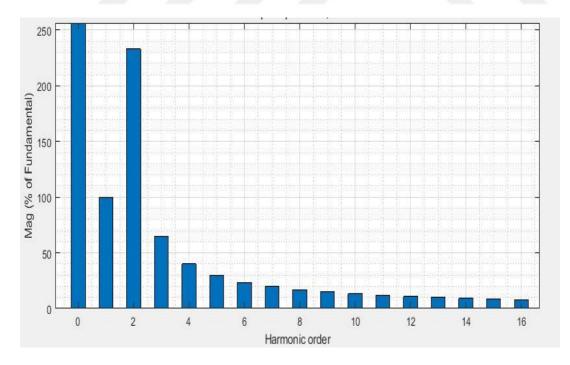

| Figure 4.10 Total Harmonic Distortion Graph                                  | 50  |

| Figure 4.11 Control Circuit Diagram of Fuzzy Logic Controller                | 50  |

| Figure 4.12 Fuzzy Logic Control Scheme                                       | 51  |

| Figure 4.13 Fuzzy Logic Controlled DV-Rectifier Input Current and Voltage Gr | aph |

|                                                                              | 51  |

| Figure 4.14 Inductor Current                                                 |     |

| Figure 4.15 Voltage Across Points A & B                                      | 52  |

| Figure 4.16 Voltage at Port VHi & VLo                                        | 53  |

| Figure 4.17 Output Current and Voltage Graph When Vin is 230V and 60Hz       |     |

| Frequency                                                                    | 53  |

| Figure 4.18 Output Current and Voltage Graph When Vin is 230V and 50Hz       |     |

| Frequency                                                                    | 54  |

| Figure 4.19 Total Harmonic Distortion                                        | 54  |

# LIST OF TABLES

| Table 3.1 |  |

|-----------|--|

| Table 3.2 |  |

### A NEW CONTROL METHOD FOR DUAL VOLTAGE RECTIFIER

#### ABSTRACT

In this thesis, novel single-phase AC-DC converter dependent on double voltagerectifier (DV-rectifier) and voltage-sigma design will be proposed. Double DC-Buses, i.e.; a consistent DC voltage BUS and a customizable DC voltage BUS, will be given by the DV-rectifier. Voltages of the two DC-Buses will be stacked together on the Output port through down-stream DC-DC transformers (DCXs). The DC Output voltage is controlled by directing the voltage of the DC-BUS of the DV-rectifier. Consequently, voltage controlling won't be required for the DC-DC transformers, which will dependably work at their upgraded task point to guarantee high effectiveness. Since the voltage of the customizable DC-BUS is lower than the steady DC-BUS, multi voltage-level qualities can be achieved with the DV-rectifier, which will profit for decrease of exchanging misfortunes and improvement of conversion proficiency. To accomplish Current control of AC input port and voltage Regulation of the two DC-Buses at the same time, multi-mode task and smooth mode transition methodologies will be proposed for the DV-rectifier. Task standards, control techniques and characteristics of the DV-rectifier and DC-DC transformer-based AC-DC converter will be examined in detail.

Keywords: AC-DC converter, dual-voltage-rectifier, dual-dc-bus, sigma structure

## ÇİFT VOLTAJ DÜZELTICI İÇİN YENİ BİR KONTROL YÖNTEMİ

## ÖZET

Bu tezde çift gerilim doğrultucuya (DV-doğrultucu) ve voltaj-sigma tasarımına bağlı yeni tek fazlı AC-DC dönüştürücü önerilmektedir. Çift DC-Otobüsler, yani; tutarlı bir DC voltaj BUS ve özelleştirilebilir DC voltaj BUS, DV-doğrultucu tarafından verilecektir. İki DC-Butos'un gerilimleri, dc-DC transformatörleri (DCXs) aracılığıyla Cıkış portu üzerinde bir araya getirilecektir. DC Cıkış gerilimi, DV-doğrultucunun DC-BUS geriliminin yönlendirilmesiyle kontrol edilir. Sonuç olarak, yüksek etkinliği garanti etmek için yükseltilmiş görev noktalarında güvenilir bir şekilde çalışacak olan DC-DC transformatörleri icin voltaj kontrolü gerekli olmayacaktır. Özellestirilebilir DC-BUS'un gerilimi sabit DC-BUS'tan daha düşük olduğundan, dv-doğrultucu ile çok voltaj seviyesinde nitelikler elde edilebilir, bu da alışveriş talihsizliklerinin azalması ve dönüşüm yeterliliğinin iyileştirilmesinden fayda sağlayacaktır. Aynı anda iki DC-Butos'un AC giriş portu ve voltaj Regülasyonunun güncel kontrolünü gerçekleştirmek için DV-doğrultucu için çok modlu görev ve düz mod geçiş metodolojileri önerilecektir. DV-doğrultucu ve DC-DC transformatör tabanlı AC-DC dönüştürücünün görev standartları, kontrol teknikleri ve özellikleri ayrıntılı olarak incelenecektir.

Anahtar Kelimeler: AC-DC dönüştürücü, çift voltaj-doğrultucu, çift dc-bus, sigma

yapısı

### **1** INTRODUCTION

AC to DC converters are the important interface of the primary AC grid and different DC loads. They have been broadly utilized in electric vehicle charging, battery charging, smart grids and power supplies for different types of data centers and telecom industries, and so forth. With the fast advancement of EV and battery storages, AC to DC converters with wide DC output voltage ranges are important to meet the necessities of batteries and DC loads. The most effective method to accomplish high productivity and adaptable voltage control on both the AC input side and DC output side has been a developing examination theme in different AC to DC power systems[1]–[3]. Accordingly, new topological and control varieties and advancements have been consistently developing.

Meet the necessities of AC current guideline, DC o/p voltage guideline and electric disengagement, non-segregated boost-type PFC is normally utilized as a front-end rectifier and in charge of AC side regulation and another isolated DC to DC converter is utilized for voltage, charge and power control of DC output [4]. Typically, double stage AC to DC converter, and a constant DC BUS is given by the front-end rectifier and utilized as the contribution for down-stream DC-DC converter [5]. For this situation, the weight of DC o/p volt regulation in a wide range is altogether brought by the down-stream DC to DC converter. Therefore, the general conversion efficiency of the AC to DC converter is damaged by both the two-stage power handling stages and wide DC o/p voltage range [6]. Numerous endeavors have been tried to improve the change proficiency of the front-end rectifier and the downstream DC to DC converter, and consequently improve the general effectiveness of whole AC to DC converter [7], [8]. Soft-switching or multilevel techniques are viable for lessening the exchanging losses of active switches at the PFC stage [9], [10], on the other hand, bridgeless technique can be utilized to diminish conduction losses [11]–[13]. Soft switched DC to DC converters are utilized for down-stream DC to DC converter in a dual stage AC to DC converter. Among different soft switching DC to DC converters, LLC resonant converters are favored because of its amazing soft switching execution for both

primary side and secondary side gadgets, low volt stresses of switching components and simple reconciliation of magnetic parts [14], [15]. It is as yet difficult to accomplish high proficiency with an LLC resonant converter when the o/p voltage is should have been regulated in a variable range. There are many advanced parameter plan techniques, advanced topologies, altered adjustment systems suggested for LLC resonant converters, the productivity is as yet unavoidable to be harmed by the volt regulation range [16]–[18]. It's been approved that the best environment of a resonant converter is working it at series resonant frequency  $(f_R)$  of the resonant tank. When converters are utilized as unregulated DC transformer (DC-DC transformer) and dependably works at its streamlined conditions, high proficiency can be accomplished for the DC to DC stage [19]. However, for the DC to DC power stage in a dual stage AC to DC converter planned with wide output voltage applications, DC-DC transformer isn't acknowledged, particularly when the voltage of DC bus or the contribution of the DC to DC arrange is consistent. To conquer this disadvantage, variable volt DC bus is proposed for front-end rectifier [20], [21]. With wide range DC bus volt, the standardized voltage gains scope of the down-stream DC-DC stage can be decreased fundamentally, and subsequently better for the efficiency of the DC-DC stage. Tragically, the voltage of the DC bus. Since a Boost converter is utilized, DC bus voltage should be high than the peak amplitude of the AC input volt to guarantee well regulation of AC current. Proficiency of a rectifier drops if the DC bus voltage increments. In this manner, variable DC bus volt is better for the DC to DC arrange, however not suitable for front-end rectifier. Subsequently, it is extremely hard to consider the effectiveness and voltage Regulation scope of the rectifier and DC-DC stage at the same time.

In [7], AC to DC converter with sigma engineering and three-port rectifier was proposed. Dual DC o/ps are given by three-port rectifier, and two DC o/ps are proportionate parallel associated at load port through downstream DC-DC converter. So, it is a current-sigma engineering and the complete load Current is proportional to sum of two DC Outputs of the front-end rectifier. The Current-sigma engineering is a decent answer for Non-isolated AC to DC power converter, particularly consistent DC Output application. For Isolated AC to DC power transformation with variable DC Output, a DC-DC converter with wide voltage gain range is yet required for the current-sigma model. In this thesis, novel AC to DC converters with double DC-Buses

and voltage-sigma design will be proposed. Unique in relation to the Current-sigma design proposed in [7], the volts of the two DC buses will be added at the output port. Consequently, the o/p volt can be completely regulated by front-end rectifier, and DC-DC transformer can be utilized in the down-stream DC to DC level. The voltage sigma design is considerably much more appropriate for isolated AC to DC power converter with wide DC o/p. More vitally, the operation standards, attributes, modulation and controlling of AC to DC converters proposed in this thesis will be changed as in [7].

The real commitment of this thesis will be to propose a novel double voltage-rectifier (DV-rectifier)- based AC to DC converter, with which a consistent voltage DC bus and a variable voltage DC bus will be accommodated the down-stream DC to DC stage. The DC Output voltage will be legitimately Regulated by the front-end DV-rectifier and there is no voltage regulation necessity for the down-stream DC to DC arrange. In this way, unregulated DC-DC transformer can be utilized to improve proficiency of DC to DC arrange. Furthermore, multi-voltage-level can be created by the dual voltage rectifier to decrease conversion losses.

#### **1.1 Problem Definition**

The function of any AC/DC or DC/DC converter module is to meet one or more of the following requirements:

i: to match the secondary load to the primary power supply

ii: to provide Isolation between primary and secondary circuits iii: to provide protection against the effects of faults, short circuit or over heating

iv: to simplify compliance with safety, performance or EMC legislation [22].

The term topology refers to the different forms of switching and energy storage element combinations that are possible for the transmission, control and regulation of an output voltage or current from an input voltage source [22]. Different types of topologies for control switching are mainly divided into two main categories

#### **1.2 Non-Isolated Converter**

Non-isolated converters, in which the input source and the output load share a common Current path during operation.

#### **1.3 Isolated Converter**

Isolated converters, in which the energy is transferred via mutually coupled magnetic components (transformers), wherein the coupling between the supply and the load are achieved solely via an electromagnetic field, thereby permitting galvanic Isolation between input and output [22].

There are two basic types of electrical converters.

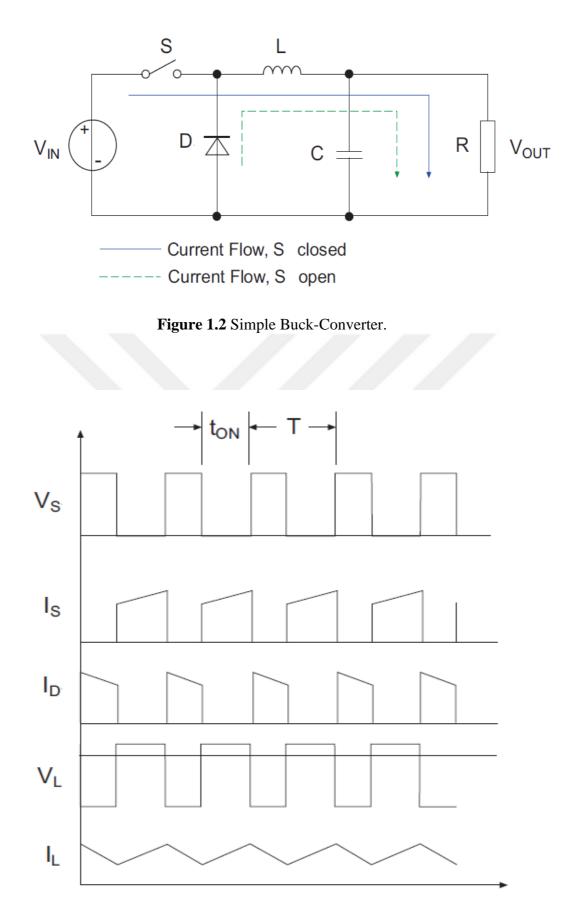

# 1.4 AC to DC Converters

These types of converters are used when we need our output in DC form. They are of two main types which are commonly used in electrical circuits. It may consist of transformer in it which steps up or steps down the input voltage according to our requirement. Basic circuit diagram of these type of converter is shown in figure 1.1.

Figure 1.1 Block Diagram of AC to DC Converter.

Above mentioned AC to DC power supply circuit is not commonly used because of their losses due to transformer. Because there are different types of power losses occur like hysteresis lose and eddy Current lose. Second type of AC to DC converter uses bridge diode for rectification of voltage. {A diode bridge in a bridge circuit configuration that provides the same polarity of Output for either polarity of input. When used in its most common application, for conversion of an alternating-

Current (AC) input into a direct-Current (DC) Output, it is known as a bridge rectifier. A bridge rectifier provides full-wave rectification from a two-wire AC input, resulting in lower cost and weight as compared to a rectifier with a 3-wire input from a transformer with a center-tapped secondary winding. The essential feature of a diode bridge is that the polarity of the Output is the same regardless of the polarity at the input. The diode bridge circuit was first used by Polish electro technician Karol Pollak [23].

### **1.5 DC-DC Converters**

For Non-isolated DC/DC converters there are five basic transformer-less topologies:

- a) Buck or step-down converter

- b) Boost or step-up converter

- c) Buck-boost or step-up-down converter

- d) Two-stage Inverting Buck-boost (Ćuk converter)

- e) Two stage non-inverting Buck-boost (Sepic converter, ZETA converter)

Our scope in this thesis is to only discuss Buck and Boost Converters and we shall stick to these two types of DC-DC converters. There are several controlling techniques available for controlling Outputs of these circuits in which PWM is widely used.

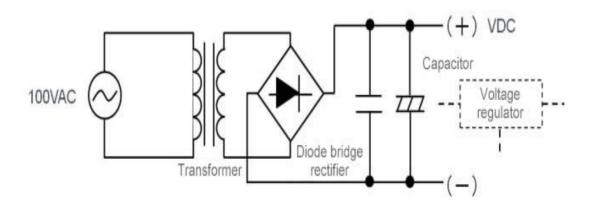

## **1.5.1 Buck Converter**

In the circuit diagrams the P-FET or N-FETs are shown only as simple switches.

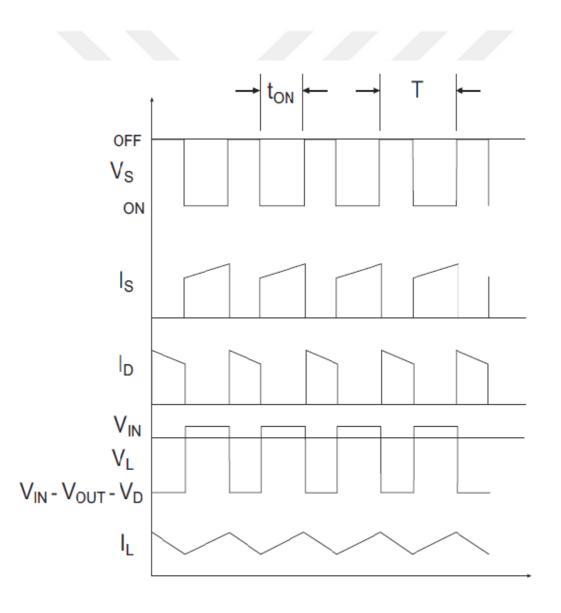

As the name suggests, the buck-converter or sometimes called the step-down converter, converts a high input voltage to a stabilized low Output voltage. A simple buck-converter is shown in figure 1.2 and the voltage-Current waveforms of circuit elements are shown in figure 1.3

Figure 1.3 Buck Regulator Characteristics.

$$V_{OUT} = V_{IN} \frac{t_{ON}}{T} = \delta V_{IN}$$

, valid when  $V_{IN} > V_{OUT}$  1.1

The transfer function of the buck-converter can be derived as:

For ON state: Input Power =

$$(V_{IN} - V_{OUT})t_{ON}$$

1.2

For OFF state: Output Power =

$$V_{OUT} t_{OFF}$$

, 1.3

Where,

$$t_{OFF} = T - t_{ON}$$

and

$$\delta = \frac{t_{ON}}{T}$$

Substituting gives:

$$(V_{IN} - V_{OUT})t_{ON} = V_{OUT}(T - t_{ON})$$

$$V_{IN}t_{ON} = V_{OUT}T$$

$$V_{OUT} = V_{IN}(\frac{t_{ON}}{T})$$

$$\frac{V_{OUT}}{V_{IN}} = \delta$$

1.5

Equation 1.5 is the transfer function of Buck-Converter

## **1.5.2 Boost Converter**

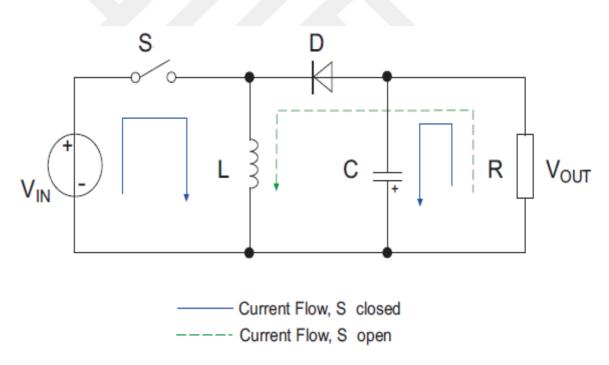

Boost converter is also called as step-up converter. As it is clear by its name it converts low voltage input to a higher Output voltage. A simplified form of boost converter is shown in figure 1.4 and its voltage-Current graphs in figure 1.5

Figure 1.4 Simple Boost Converter.

Figure 1.5 Boost Converter Characteristics.

For ON state: Input Power =  $V_{IN}t_{ON}$

For ON state: Output Power =  $(V_{OUT} - V_{IN})t_{OFF}$

$$\frac{V_{OUT}}{V_{IN}} = \frac{1}{1-\delta}$$

1.6

Eq 1.6 is the transfer function for boost-converter

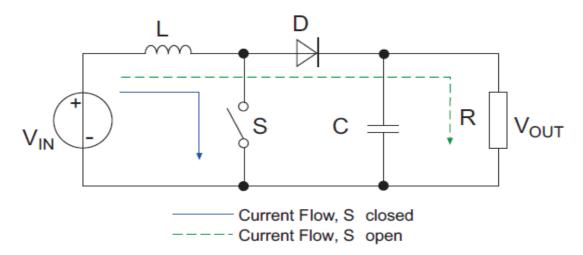

## **1.5.3 Buck-Boost Converter:**

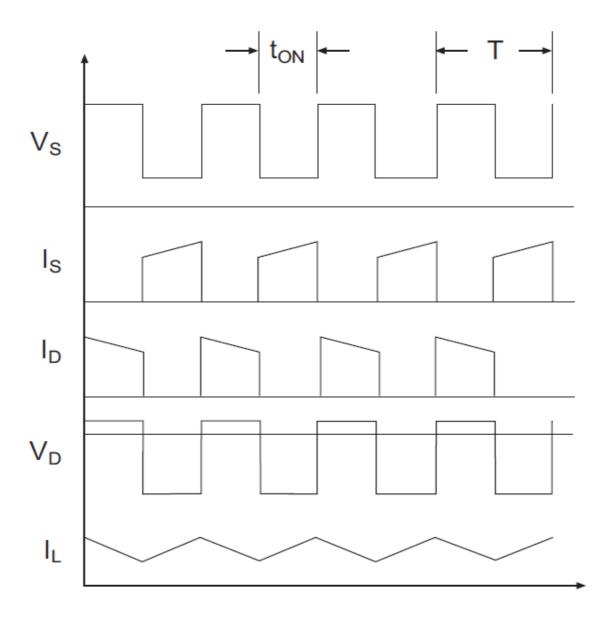

It is also known as fly back converter. This converter converts an input voltage to an Output voltage which can be higher or lower in magnitude as compared to input voltage. A simple fig. of a buck-boost converter is shown in 1.6 and their associated graphs in figure 1.7

Figure 1.6 Simple Buck-Boost Design.

Figure 1.7 Buck-Boost Characteristics.

In this circuit when switch S is in ON state, a Current IL, which increases as  $\frac{V_{IN}}{I_L}$ , flows through inductor L. Diode D blocks any Current to flow into the $R_L$ . In this state, the Output Current is supplied by Output capacitor C. When switch S is in OFF state, the energy stored in capacitor L causes the end of switch of the inductor to become negative. The Current now flows to the load. The inductor Current now decreases in proportion to  $\frac{V_{OUT}}{L}$ . This type of topology is best suitable for producing -ve voltages only.

$$V_{OUT} = V_{IN} \frac{-\delta}{1-\delta} \quad V_{IN} > V_{OUT} \ OR \ V_{IN} < V_{OUT}$$

1.7

The derivation of buck-boost transfer function is same as that of discussed in the previous section, only the main equations are:

For ON state: Input Power =  $V_{IN}t_{ON}$

For OFF state: Output Power =  $-V_{OUT}t_{OFF}$

$$\frac{V_{OUT}}{V_{IN}} = \frac{-\delta}{1-\delta}$$

1.8

Equation 1.8 is the transfer function of buck-boost converter.

#### 2 MAIN CIRCUIT AND PROPOSED DESIGN

#### 2.1 Voltage Conversion of a Conventional Two-Stage AC to DC Converter

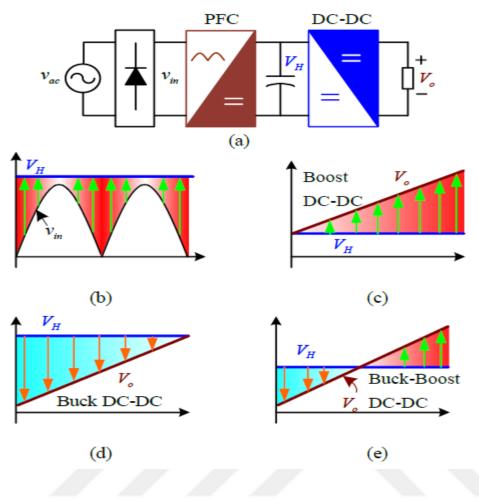

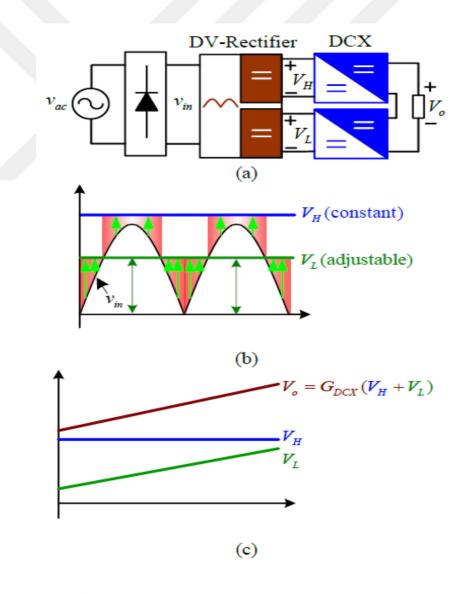

The block diagram of a regular Boost-PFC-based two-stage AC to DC converter is shown in Fig. 2.1(a), the voltage connection between input voltage  $v_{in}$  and Output voltage  $V_{Hi}$  of the PFC stage is delineated in Fig. 2.1(b), while the conceivable relations among  $V_{Hi}$  and the Output voltage  $V_o$  of the DC-DC stages are shown in Fig. 2.1(c)-(e). The pulsed input voltage  $v_{in}$  is ventured up to a steady DC-BUS voltage  $V_{Hi}$  and utilized as the input of the DC-DC stage, at that point  $V_{Hi}$  is changed over to movable DC Output voltage with a Boost-type, Buck-type, or a Buck-Boost type DC-DC converter, as delineated in Fig.2.1(c), (d) and (e), separately.

With a consistent voltage  $V_{Hi}$ , improved operation points for a Boost-type and Bucktype DC to DC stage is the most reduced and highest Output voltage, individually, while the best effectiveness point can be set at a specific load voltage when a Buck-Boost DC to DC is utilized. Nonetheless, regardless of which type DC to DC stage is utilized, it is hard to acknowledge high effectiveness inside the whole Output voltage run.

Figure 2.1 Conventional Two Stage AC to DC Converter.

### 2.2 Voltage Conversion of Proposed Circuit

The block drawing of proposed circuit converter is appeared in Fig. 2.2(a), while the relation between input and output volts of front-end rectifier and downstream DC to DC stage are represented in Fig.2.2(b), individually. To keep away from proficiency, decrease of the DC to DC stage because of wide volt regulation range, the fundamental thought of the proposed AC to DC converter depends on dual DC bus strategy. Two DC buses, that are, a consistent voltage DC bus  $V_{Hi}$  and customizable DC bus  $V_{Low}$ , are provided by the DV-rectifier.

The volts of  $V_{Hi}$  is consistent and will be higher than the maximum amplitude of  $V_{in}$  to guarantee well controlling of AC current and high power factor correction, and the voltage of  $V_{Low}$  can be controlled between 0 to  $V_{Hi}$  as per the necessity of  $V_o$ . The two voltages,  $V_{Hi}$  and  $V_{Low}$ , are added on the output point through the DC to DC converter. Since o/p volt  $V_o$  can be straightforwardly controlled by changing the voltage  $V_{Low}$

appropriately, there will be no volt regulation prerequisite for the DC to DC converter. In this manner, Unregulated DC-transformer (DC-DC transformer) with streamlined task criteria can be utilized as the DC to DC stage. As appeared in Fig. 2.1 (c), the connection between  $V_o$ ,  $V_{Hi}$  and  $V_{Low}$  is communicated as:

$$V_O = G_{DC-DC}(V_L + V_{Hi})$$

2.1

where  $G_{DC-DC}$  is volt gain of the DC to DC transformer. DC to DC converters with volt regulation capacity is just required only once the variation range of  $V_{Low}$  can't fulfill the prerequisite of  $V_o$ , however, the volt regulation range of the DC to DC stage can in any case be limited altogether, which is an advantage of the design, execution and conversion effectiveness of the DC to DC stage.

Figure 2.2 Proposed DV Rectifier Block Diagram.

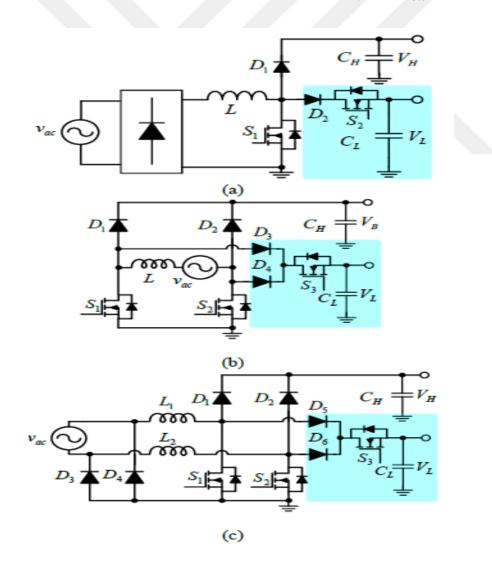

#### 2.3 Topologies of Dual Voltage Rectifier & DC-DC transformer

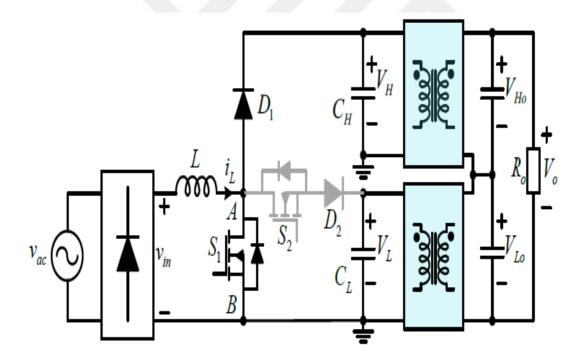

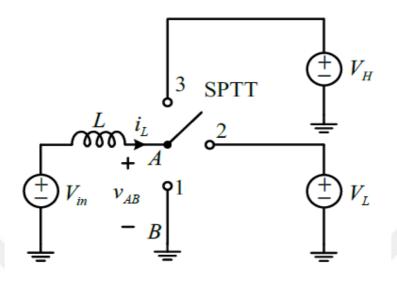

The dual voltage rectifier is the key to the proposed AC to DC converter. A dual voltage rectifier can be determined by bringing another DC o/p into an ordinary boost power factor corrector or bridgeless boost power factor corrector. Keeping in mind the standard of dual o/p boost converter, a group of dual voltage rectifier topologies are outlined in fig. 2.3 The topologies have appeared in Fig. 2.3 (a) and (b) and are taken from a regular Boost PFC [5]–[7], on the other hand the topologies in Fig. is derived from a bridgeless Boost PFC [11]. Two DC o/p, for example  $V_{Hi}$  and  $V_{Low}$ , are provided by DV-rectifiers. New branch presented for the movable DC Output  $V_{Low}$  has been featured in Fig. Clearly the voltage  $V_{Hi}$  is constantly more noteworthy than  $V_{Low}$ . Thusly, a functioning switch, for example  $S_2$  in Fig. 2.3(a) and S3 in Fig. 2.3(b) and, is utilized to appropriate the AC input control among  $V_{Hi}$  and  $V_{Low}$ .

Figure 2.3 Different Types of Boost Topologies.

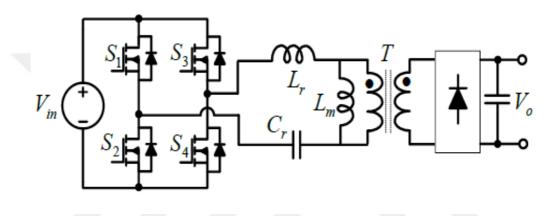

#### 2.4 LLC Resonant Converter

The DC to DC transformer in the proposed AC to DC converter is utilized to coordinate the load voltage with the two DC Buses with a legitimate transformer turns proportion. Practically all isolated DC to DC converters could be utilized as DC to DC transformer, a soft switching full converter, for example, the LLC resonant converter, is favored because of its high productivity and high-power ratio. In this thesis, the LLC full converter appeared in Fig. 2.4 is utilized as the downstream DC to DC transformer to demonstrate the task of the proposed DC to DC transformer.

Figure 2.4 LLC Resonant Converter.

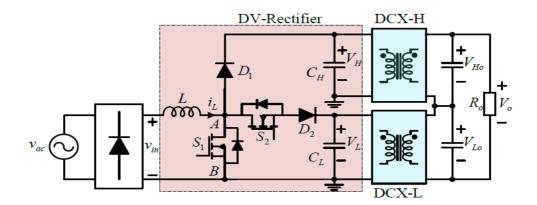

#### 2.5 Analysis of the Proposed AC to DC Converter

The proposed AC to DC converter appeared in Fig. 2.5, where the dual voltage rectifier in Fig. 2.3(a) is utilized as the main PFC converter, is utilized to investigate the activity standards, control and qualities of the proposed arrangements.

Figure 2.5 Block Diagram of Proposed AC to DC Converter.

#### 2.6 Operational Modes of Dual Voltage Rectifier

To decrease switching losses, there is just one ON dynamic switch,  $S_1$  or  $S_2$ , will be switched at high recurrence, the other switch will be kept ON or OFF. As per the switching conditions of  $S_1$  and  $S_2$ , the converter has triple activity modes.

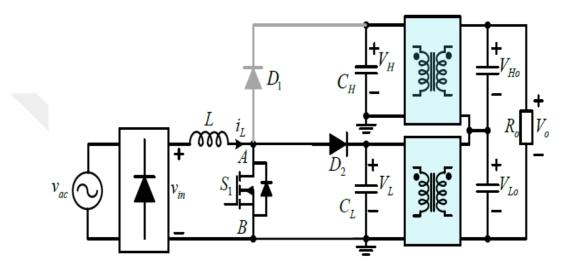

#### 2.7 V<sub>Hi</sub> Single-Output Mode

At the point when the switch  $S_2$  is kept OFF and  $S_1$  works at high switching frequency, the rectifier works in the  $V_{Hi}$  single o/p mode ( $V_{Hi}$ -SM). Fig. 2.6 demonstrates the comparable circuit of the  $V_{Hi}$  single o/p mode. Clearly, the equal cct of the front-end rectifier is equivalent to the customary boost power factor corrector (PFC), the single o/p boost converter is worked by inductor L, the switch  $S_1$ , and the diode  $D_1$ . At this instance, all the power is provided to the  $V_{Hi}$  port, and the post voltage  $V_{AB}$  will change between volt 0 and  $V_{Hi}$  with  $S_1$  On & Off, respectively.

Figure 2.6  $V_{Hi}$  Single Output Mode.

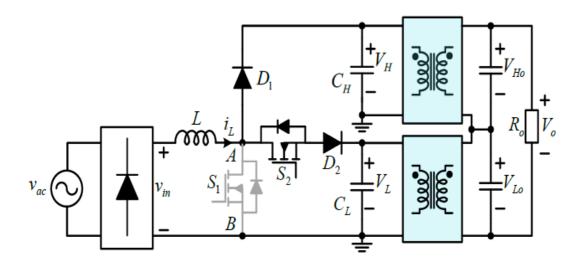

#### 2.8 V<sub>Low</sub> Single Output Mode

The rectifier will work in the  $V_{Low}$  single-Output mode ( $V_{Low}$ -SM) if the switch  $S_2$  is dependably ON and  $S_1$  works at max frequency. The equal circuit of the  $V_{Low}$  single o/p mode is appeared in Fig. 2.7. Since  $V_{Hi}$  is more prominent than  $V_{Low}$ , the diode  $D_1$  will be reversed biased and hence no power transferred to  $V_{Hi}$  port. Another Boost PFC converter is developed by the inductor L, the switch  $S_1$  and the diode  $D_1$ . Though  $S_1$  is switching ON and OFF state, the voltage  $v_{AB}$  switches among 0 and  $V_{Low}$ . It ought to be noticed, since the proportionate cct of the rectifier is a Boost converter, the volt  $V_{Low}$  must be more noteworthy than the information volts  $v_{in}$  to ensure the converter works properly. Thusly, the rectifier can possibly work in the  $V_{Low}$  single o/p mode when  $v_{in} < V_{Low}$ .

Figure 2.7 V<sub>Lo</sub> Single Output Mode.

#### 2.9 $V_{Low}$ and $V_{Hi}$ Dual Output Mode

If switch  $S_1$  is kept OFF and just the switch  $S_2$  is a high-frequency switch, the DVrectifier will work in the  $V_{Low}$  and  $V_{Hi}$  double Output mode. The comparable circuit of this mode is appeared in Fig. 2.8, where an equivalent Boost PFC is formed by the inductor L, the switch  $S_2$ , the diode D1 and D2. Not the same as the  $V_{Low}$ -SM and the  $V_{Hi}$ -SM, the input power is provided to the  $V_{Low}$  and  $V_{Hi}$  port on the other hand as  $S_2$  is turned ON and OFF. Henceforth, the voltage vAB changes among  $V_{Low}$  and  $V_{Hi}$ . Clearly, to influence the equivalent Boost converter to work typically, the inductor L must be charged when  $S_2$  is ON with the goal that the inductor L can be discharged when  $S_2$  is OFF. In this manner, the DV-rectifier can possibly work in the DM when

$$V_{Hi} > v_{in} > V_{Low}$$

Figure 2.8  $V_{Lo}$  and  $V_{Hi}$  Dual Output Mode.

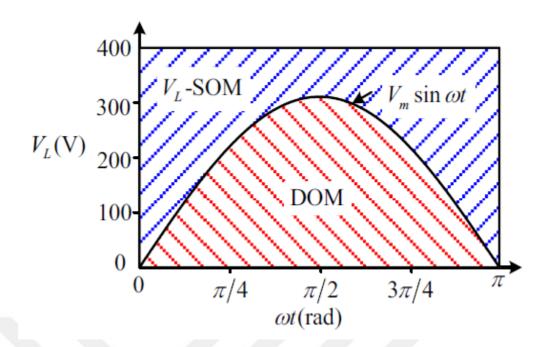

#### 2.10 Operation Mode Consideration

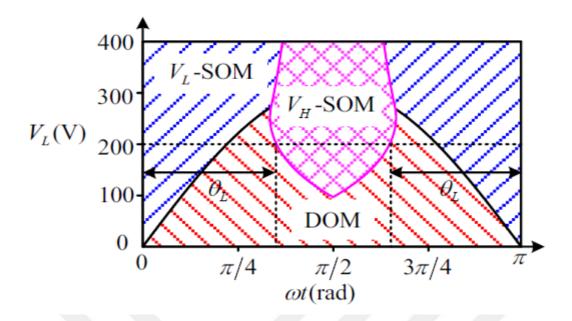

As appeared in Fig. 2.2(b) and Fig. 2.2(c), the voltage  $V_{Hi}$  is consistent and higher than the maximum amplitude of  $v_{in}$ , for example  $V_M$ , while voltage of  $V_{Low}$  can be Regulated between 0 to  $V_{Hi}$  to coordinate the Output voltage  $V_o$ . In light of the working standard of Boost converter, operation area of various modes can be inferred. Fig. 2.9 demonstrates the conceivable activity areas of the  $V_{Low}$  -SM and DM in half time of the grid voltage w.r.t voltage  $V_{Low}$ . Since the voltage  $V_{Hi}$  is steady and constantly higher than  $V_M$ , the DV-rectifier can work in the  $V_{Hi}$  single-Output mode inside whole input voltage range. In this manner, the stage point scope of  $V_{Low}$  -SM, DM and  $V_{Hi}$  -SM fulfill:

$$V_{LOW} - SM$$

: 2.2

$$0 \le \omega t \le \arcsin \frac{V_{LOW}}{V_M} \text{ and } \pi - \arcsin \frac{V_{LOW}}{V_M} \le \omega t \le \pi$$

$$DM: \quad \arcsin \frac{V_{LOW}}{V_M} \le \omega t \le \pi - \arcsin \frac{V_{LOW}}{V_M}$$

2.3

$$V_{HIGH} - SM: \quad 0 \le \omega t \le 0$$

2.4

Figure 2.9 Operation Region of  $V_{Lo}$ -SM and DOM.

As per the Output power of  $V_{Lo}$  and  $V_{Hi}$  ports, there might be numerous sorts of power dissemination strategies to decide the activity modes fifty-fifty time of the grid voltage. Considering  $V_{Lo} \leq V_{Hi}$ , so as to decreases switching losses, the  $V_{Lo}$ -SM is favored when the stage point fulfills  $0 \leq \omega t \leq \arcsin V_{Lo} / V_M$  and  $\pi - \arcsin V_{Lo} / V_M \leq \omega t \leq \pi$ , while the DM is favored when the stage edge fulfill  $\arcsin V_{Lo} / V_M \leq \omega t \leq \pi - \arcsin V_{Lo} / V_M$ . The  $V_{Hi}$  -SM is the last decision to fulfill the Output power necessity of the  $V_{Hi}$  port. The optimized mode determination plot is represented in Fig. 2.10, where  $\theta_L$  speaks to the phase angle in which the DV-rectifier works in the  $V_{Lo}$ -SM and DM to fulfill the Output power necessity of the  $V_{Lo}$  port.

Figure 2.10 Optimized Scheme of Mode Selection.

### 2.11 Relationship Between the Power Ratio and Phase Angle $\theta_L$

According to condition shown in Fig. 2.10, the input power will be delivered to the  $V_{Lo}$  port only in the range of  $0 \le \omega t \le \theta_L$ . Hence, the value of  $\theta_L$  defines the power transferred to the  $V_{Lo}$  port or power ratio between the  $V_{Lo}$  and  $V_{Hi}$  port. The input ac voltage and Current will be expressed as:

$$v_{ac} = V_M sin\omega t \qquad 2.5$$

$$i_{ac} = I_M sin\omega t$$

2.6

where  $V_M$  and Im are the maximum (peak) amplitude of the input voltage and Current, respectively. The input power is calculated as:

$$p_{ac} = v_{ac}i_{ac} = \frac{V_M I_M}{2}(1 - \cos 2\omega t) = P_{OUT}(1 - \cos 2\omega t)$$

2.7

The average input power *P*<sub>average</sub> is:

$$P_{average} = P_{OUT} = \frac{V_M I_M}{2}$$

2.8

The input power can be provided to the  $V_{Lo}$  port only when the DV-rectifier works in the  $V_{Lo}$ -SM and DM. As appeared in Fig. 2.7, all the input power is provided to the

$V_{Lo}$  port when the DV-rectifier works in the  $V_{Lo}$ -SM. In this way, the prompt power pL\_ $V_{Lo}$ -SM:

$$p_{LOW-V_{LO-SM}} = p_{ac} = \frac{V_M I_M}{2} (1 - \cos 2\omega t)$$

2.9

Nevertheless, when the DV-rectifier works in the DM, input power is sustained to the  $V_{Low}$  port just when  $S_2$  is ON. In this manner, the instantaneous power provided to the  $V_{Low}$  port is determined as:

$$p_{LO-DM} = I_M sin\omega t \cdot d_2 \cdot V_{Lo} = I_M sin\omega t \cdot \frac{V_{HIGH} - v_{in}}{V_{HIGH} V_{Lo}} \cdot V_{Lo}$$

2.10

The rectifier will work in the DM only when the phase angle will be  $\theta_L$ >arcsin $V_{Low}$ / $V_M$ . Therefore, the average power delivered to the  $V_{Low}$  port is calculated as:

$$P_{Lo} = 2.11$$

$$\left\{\frac{2}{\pi}\int_{0}^{arcsin\frac{V_L}{V_M}} p_{LOW_{VLOW}-SM}d\omega t + \frac{2}{\pi}\int_{arcsin\frac{V_{LOW}}{V_M}}^{\theta_{LOW}} p_{LOW_{mode2}}d\omega t \quad \theta_{LOW} \ge arcsin\frac{V_{LOW}}{V_M}}{\frac{2}{\pi}\int_{0}^{\theta_{LOW}} p_{LOW_{-}SM}d\omega t \quad \theta_{LOW} < \arcsin\frac{V_L}{V_{ML}}}\right\}$$

Hence, the power ratio between the  $V_{Lo}$  and  $V_{Hi}$  port can be extracted as:

$$k_{pow} = \frac{P_L}{P_H} = \begin{cases} \frac{V_L V_m \sin 2\theta_L - 2V_L V_m \theta_L - 4V_H V_L \cos \theta_L + 2V_H V_L \sqrt{1 - \frac{V_L^2}{V_m^2}} + 2V_H V_m \arcsin \frac{V_L}{V_m}}{\pi V_m (V_H - V_L) - V_L V_m \sin 2\theta_L - 2V_L V_m \theta_L - 4V_H V_L \cos \theta_L + 2V_H V_L \sqrt{1 - \frac{V_L^2}{V_m^2}} + 2V_H V_m \arcsin \frac{V_L}{V_m}} & \theta_L \ge \arcsin \frac{V_L}{V_m} \\ \frac{2\theta_L - \sin 2\theta_L}{\pi - 2\theta_L + \sin 2\theta_L}} & \theta_L < \arcsin \frac{V_L}{V_m} \end{cases}$$

2.12

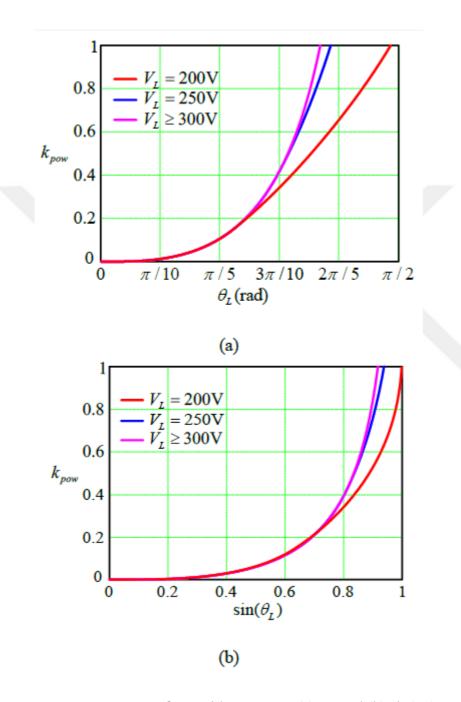

$k_{power}$  is an element of both the phase angle  $\theta_L$  and voltages  $V_{Lo}$ ,  $V_{Hi}$  and  $V_M$ . Fig. 2.11 demonstrates the bends of  $k_{power}$  when vac=220VAC and  $V_{Hi}$  =400V as for  $\theta_L$  and sin( $\theta_L$ ), separately. As appeared in Fig. 11(a),  $k_{power}$  increments monotonically with the expanding of stage point  $\theta_L$ . As appeared in Fig. 2.11(b),  $k_{power}$  and sin( $\theta_L$ ) pursues a similar relationship too. Both  $\theta_L$  and sin( $\theta_L$ ) can be utilized as a controlling

factor to Regulate the power proportion between the  $V_{Low}$  and  $V_{Hi}$  ports. Practically speaking, utilizing  $\sin(\theta_L)$  as a control variable will be a lot simpler in light of the fact that the data of  $\sin(\theta_L)$  has been incorporated into the input voltage vac.

**Figure 2.11** Curves of  $k_{pow}$  with respect to (a)  $\theta$ L and (b)  $\sin(\theta$ L).

Assuming the DC to DC transformers are unit gain, since the two Outputs of DC to DC transformers in the proposed converter are associated in arrangement, control

proportion  $k_{power}$  is likewise equivalent to the voltage proportion kvolt among  $V_{Lo}$ and  $V_{Hi}$

$$k_{power}(\theta_L) = k_{volt} = \frac{V_{Lo}}{V_{HIGH}}$$

2.13

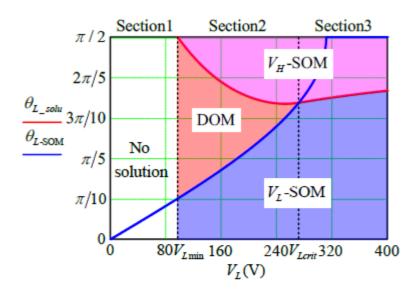

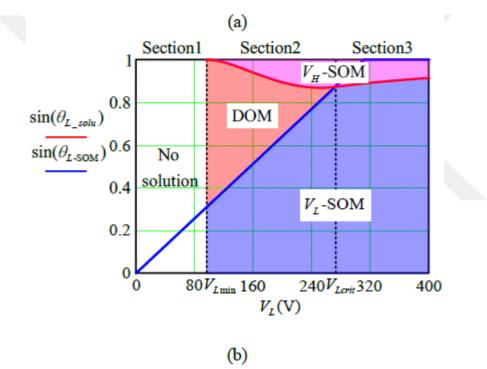

As indicated by 2.12 and 2.13, the arrangement of phase angle  $\theta_L$ \_solu comparing to certain  $V_{Low}$ ,  $V_{Hi}$  and  $V_M$  can be explained. Fig. 2.12 demonstrates the bends of  $\theta_L$ \_solu and  $\sin(\theta_L$ \_solu) as for various estimation of  $V_{Low}$  when vac=220VAC and  $V_{Hi}$  =400V, in which three task areas are incorporated. As appeared in Fig.2.12(a), when  $V_{Lo} < V_{Lo min}$ , there is no accessible arrangement of  $\theta_L$  for a given estimation of  $V_{Low}$  which implies the dual voltage rectifier can't work regularly in area 1. It is on the grounds that the power provided to  $V_{Lo}$  port can't fulfill the necessity of the DC to DC transformer. Whenever  $V_{Lo} \min < V_{Lo} < V_{Lo}$  criti, the DV-rectifier works in area 2, in which  $\theta_L$  solu is bigger than  $\theta_{Lo}$ \_SM.  $\theta_{Lo}$ \_SM is the limit phase angle among the  $V_{Low}$  -SM and DM and can be determined as:

$$\theta_{L-SM} = \begin{cases} arcsin \frac{V_{Lo}}{V_{Hi}} & V_{Lo} \le V_M \\ \frac{\pi}{2} & V_{Lo} > V_M \end{cases}$$

2.14

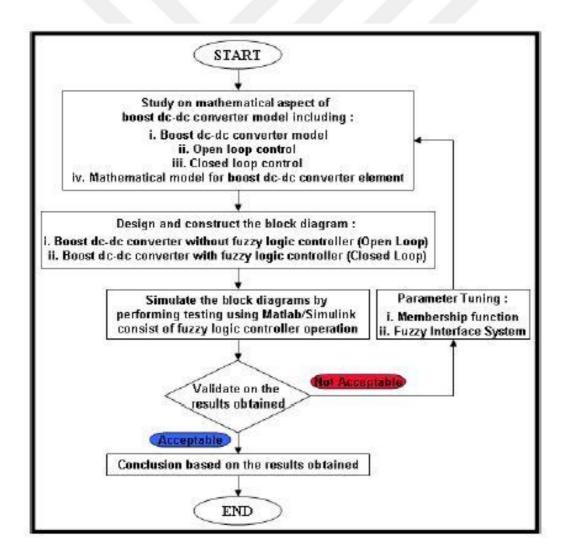

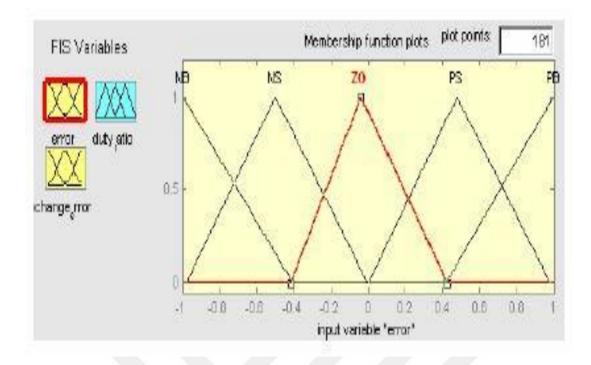

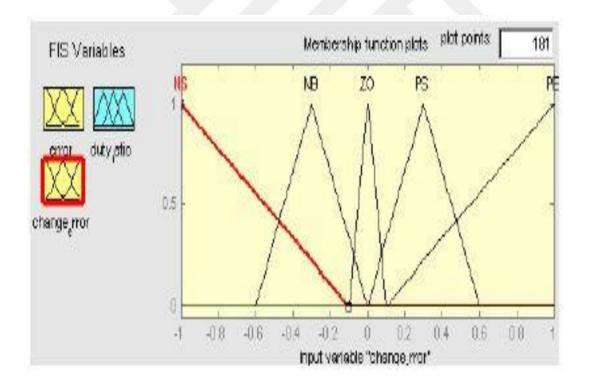

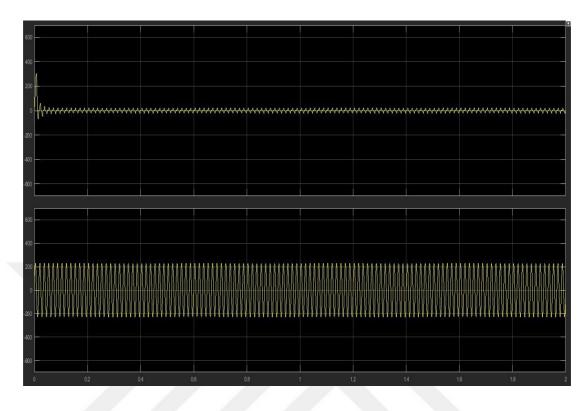

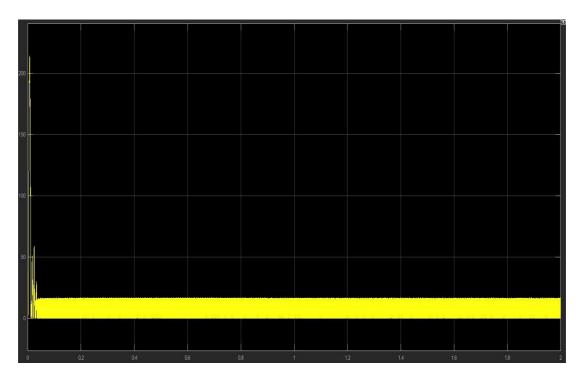

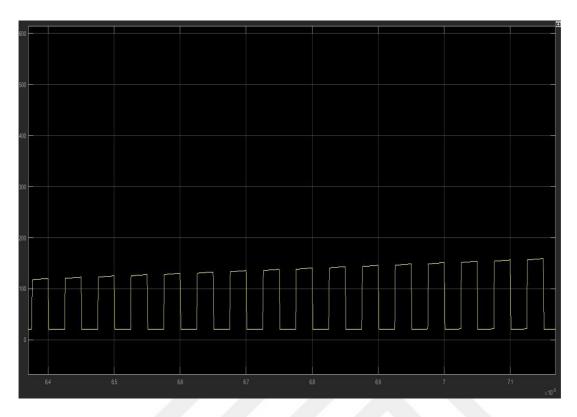

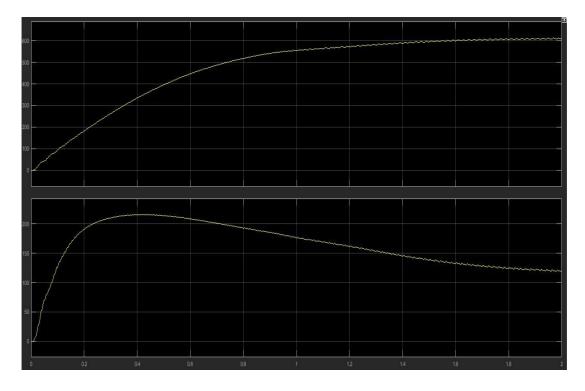

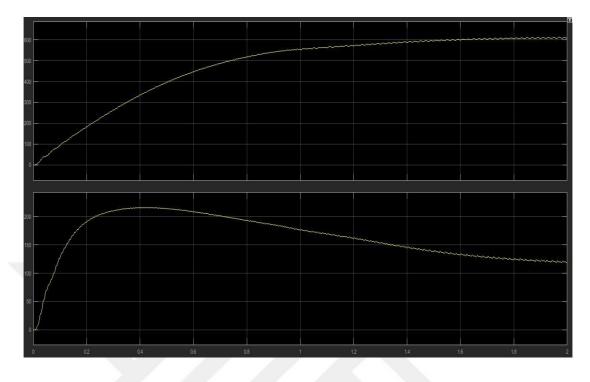

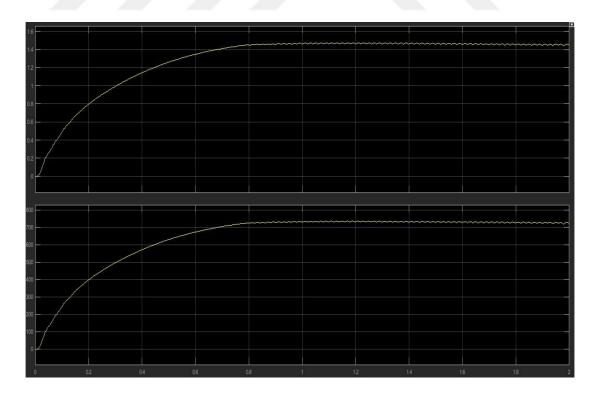

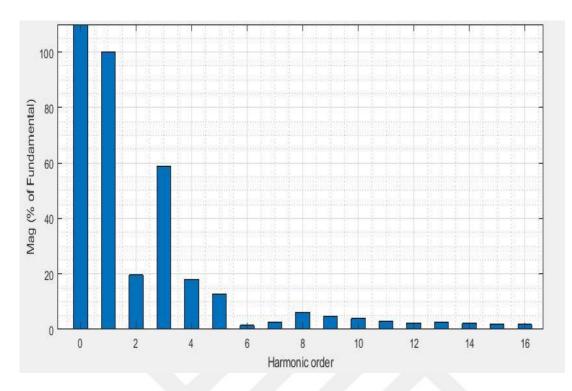

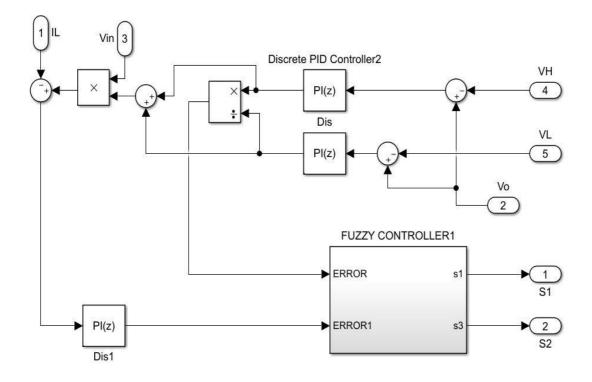

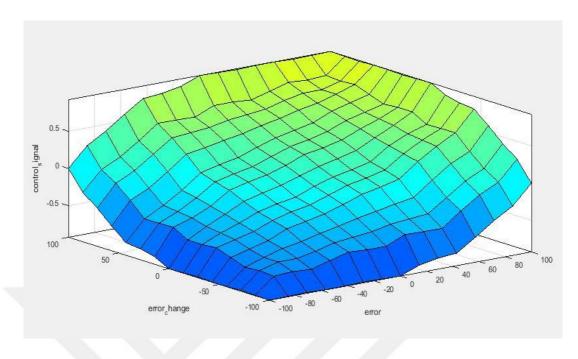

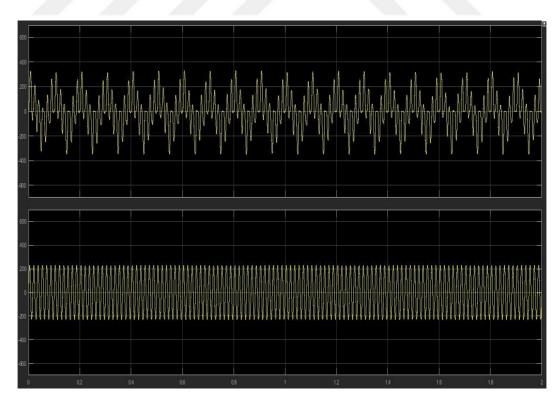

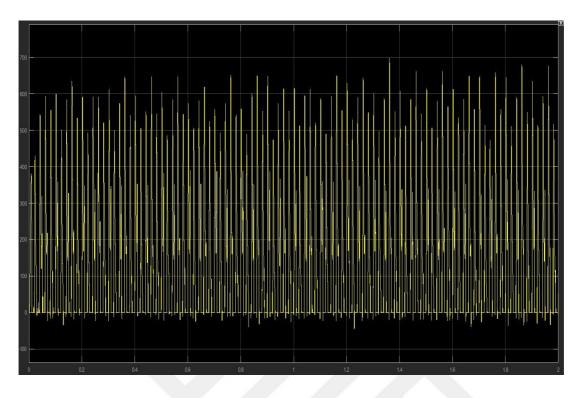

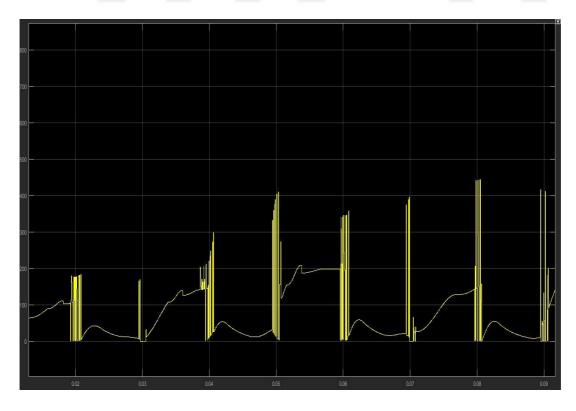

Since  $\theta_{L}$ \_solu> $\theta_{L}$ \_SM in area 2, both  $V_{Low}$  -SM and DM are utilized to fulfill the power necessity of the  $V_{Low}$  port. All the more explicitly, the activity phase angle scope of DM in the half period time of the line voltage is  $2(\theta_{L}$ \_solu- $\theta_{L}$ \_SM). in the end, when  $V_{Lo} \ge V_{Lo}$  criti, the dual voltage rectifier works in segment 3, in which  $\theta_{L}$ \_solu< $\theta_{L}$ \_SM. It implies the converter just works in  $V_{Lo}$ -SM to supply capacity to the  $V_{Lo}$  port. A similar end can be acquired from Fig. 2.12(b), where  $\sin(\theta_{L}$ \_SM) is determined as: