# DESIGN AND IMPLEMENTATION OF A GENERAL PURPOSE MEDIAN FILTER UNIT IN VLSI

#### A THESIS

SUBMITTED TO THE DEPARTMENT OF ELECTRICAL AND

ELECTRONICS ENGINEERING

AND THE INSTITUTE OF ENGINEERING AND SCIENCES

OF BILKENT UNIVERSITY

IN PARTIAL FULFILLMENT OF THE REQUIREMENTS

FOR THE DEGREE OF

MASTER OF SCIENCE

By Mustafa Karaman October 1988

T. C.

Yükseköğretim Kurulu

Dokümantasyon Merkezi

To my family

I certify that I have read this thesis and that in my opinion it is fully adequate, in scope and in quality, as a thesis for the degree of Master of Science.

Asst. Prof. Dr. Levent Onural(Principal Advisor)

I certify that I have read this thesis and that in my opinion it is fully adequate, in scope and in quality, as a thesis for the degree of Master of Science.

Assoc. Prof. Dr. Abdullah Atalar (Second supervisor)

I certify that I have read this thesis and that in my opinion it is fully adequate, in scope and in quality, as a thesis for the degree of Master of Science.

Asst. Prof. Dr. Mehmet Ali Tan

Approved for the Institute of Engineering and Sciences:

Prof. Dr. Mehmet Baray, Director of Institute of Engineering and Sciences

© Copyright 1988 by Mustafa Karaman

#### ABSTRACT

## DESIGN AND IMPLEMENTATION OF A GENERAL PURPOSE MEDIAN FILTER UNIT IN VLSI

Mustafa Karaman

M.S. in Electrical and Electronics Engineering

Supervisors: Asst. Prof. Dr. Levent Onural

and Assoc. Prof. Dr. Abdullah Atalar

October 1988

The median of a group, containing an odd number of elements, is defined as the middle element, when the elements of the group are sorted. A median filter finds the median of a number of elements at its inputs. Median filters are frequently used in many signal, and image processing applications for smoothing of the noisy signals and images while at the same time preserving the edge information.

The required window size, speed, and the word length of the median filters vary depending on the applications. In order to meet these changing demands a general purpose median filter unit configuration is proposed. The unit consists of two single-chip median filters. One of the chips is designed for unlimited word-length and extensibility to larger window sizes whereas the other one is for real-time video applications. The networks of the chips are based on the odd/even transposition sorting. The chips are implemented in  $3-\mu m$  M<sup>2</sup>CMOS by using full-custom VLSI design techniques. For physical testing of the chips, the test vectors and the corresponding outputs of the chips are generated by using software tools written for this purpose.

In this thesis, the algorithms, VLSI implementations, simulation results, testing, and applications of the chips are presented.

**Keywords**: Median filters, signal and image processing, signal processing hardware, VLSI implementation, VLSI testing.

## ÖZET

## GENEL AMAÇLI BİR ORTANCA SÜZGECİ BİRİMİNİN VLSI TASARIMI VE GERÇEKLEŞTİRİLMESİ

Mustafa Karaman Elektrik ve Elektronik Mühendisliği Yüksek Lisans Tez Yöneticileri: Yrd. Doç. Dr. Levent Onural ve Doç. Dr. Abdullah Atalar

Ekim 1988

Tek sayıdaki verilerin oluşturduğu bir kümenin ortancası (medyanı), verilerin büyüklüklerine göre sıralanması ile elde edilen dizinin tam ortasındaki veri olarak tanımlanır. Bir ortanca süzgeci, girişindeki verilerin ortancasını bulur. Ortanca süzgeçleri, bir çok işaret ve görüntü işleme uygulamalarında kullanılmaktadır. Kenar keskinliğinin korunması ve *impulsive* gürültülerin iyi ayıklanması bu süzgeçlerin en önemli özelliklerindendir.

Ortanca süzgeçlerinin gereken pencere büyüklüğü, hızı ve bit uzunluğu uygulamaya bağlı olarak değişmektedir. Bu değişen gereksinimleri karşılayabilmek için genel amaçlı bir ortanca süzgeci birimi önerilmiştir. Bu birim, iki tek yonga ortanca süzgecinden oluşmaktadır. Yongalardan biri, sınırsız bit uzunluğu ve daha büyük pencerelere genişletilebilecek şekilde diğeri ise on-line uygulamalarında kullanılabilecek hızlara erişebilecek şekilde tasarlanmıştır. Yongalarda kullanılan ağlar tek/çift değiştirimle sıralama yöntemine dayalıdır. Yongalar, full-custom VLSI tasarım teknikleri kullanılarak 3-µm M²CMOS'da gerçekleştirilmiştir. Yongaların üretiminden sonra yapılacak testlerinde kullanılacak olan giriş işaretleri ve bunlara ait çıkış işaretleri bu amaçlar için yazılmış bilgisayar programları yardımıyla elde edilmiştir.

Bu tezde, söz konusu yongaların algoritmaları, VLSI gerçekleştirimleri, simülasyon sonuçları, testleri ve uygulamaları sunulmaktadır.

Anahtar Kelimeler: Ortanca süzgeçleri, işaret ve görüntü işleme, işaret işleme donanımı, VLSI gerçekleştirim, VLSI test.

## ACKNOWLEDGEMENT

I would like to express my deep thanks to my thesis supervisors Asst. Prof. Dr. Levent Onural and Assoc. Prof. Dr. Abdullah Atalar for their supervisions, guidances, and encouragements during this research.

I am grateful to my friend İ. Enis Ungan for his efforts to modify the VLSI tools and to develop new tools, and to my friend Satılmış Topcu for his valuable ideas on VLSI testing of the chips.

## TABLE OF CONTENTS

| 1 | INT       | TRODUCTION                             | 1  |

|---|-----------|----------------------------------------|----|

|   | 1.1       | Median Filter                          | 1  |

|   | 1.2       | Motivation and Approach                | 2  |

|   | 1.3       | On the Performance of Algorithms       | 3  |

|   | 1.4       | Benefits                               | 4  |

|   | 1.5       | Organization of Thesis                 | 4  |

| 2 | A S       | URVEY OF MEDIAN FILTERING              | 5  |

|   | 2.1       | Median Filtering Techniques            | 5  |

|   |           | 2.1.1 Finding Root Signal              | 5  |

|   |           | 2.1.2 Recursive Median Filtering       | 6  |

|   |           | 2.1.3 Generalized Median Filtering     | 6  |

|   |           | 2.1.4 Separable Median Filtering       | 6  |

|   |           | 2.1.5 Weighted Median Filtering        | 7  |

|   | 2.2       | Median Filtering Algorithms            | 7  |

| 3 | <b>GE</b> | NERAL PURPOSE MEDIAN FILTER            | 10 |

|   | 3.1       | Odd/Even Transposition Sorting Network | 10 |

|   | 3.2       | Extensible Median Filter Network       | 12 |

|   | 3.3       | Real-Time Median Filter Network        | 16 |

|   | 3.4       | Feasibility of VLSI Implementation     | 18 |

| 4 | VL        | SI DESIGN METHODOLOGY                  | 21 |

|   | 4.1       | VLSI Design Approach                   | 21 |

|   | 4.2       | Circuit Technique                      | 25 |

|   | 4.3       | VLSI Tools                             | 27 |

| 5 | VLS | SI IMI | PLEMENTATION                                           | <b>29</b>  |

|---|-----|--------|--------------------------------------------------------|------------|

|   | 5.1 | Imple  | mentation of the Extensible Median Filter              | 29         |

|   |     | 5.1.1  | Compare-and-Swap Unit-1 (CSU1)                         | 31         |

|   |     | 5.1.2  | Delay Unit                                             | 34         |

|   |     | 5.1.3  | Clock Buffers                                          | 34         |

|   |     | 5.1.4  | Chip Overall Layout                                    | 38         |

|   |     | 5.1.5  | An Overview of the Extensible Median Filter Chip       | <b>3</b> 8 |

|   |     | 5.1.6  | Testing of the Extensible Median Filter Chip           | 44         |

|   | 5.2 | Imple  | mentation of the Real-Time Median Filter               | 46         |

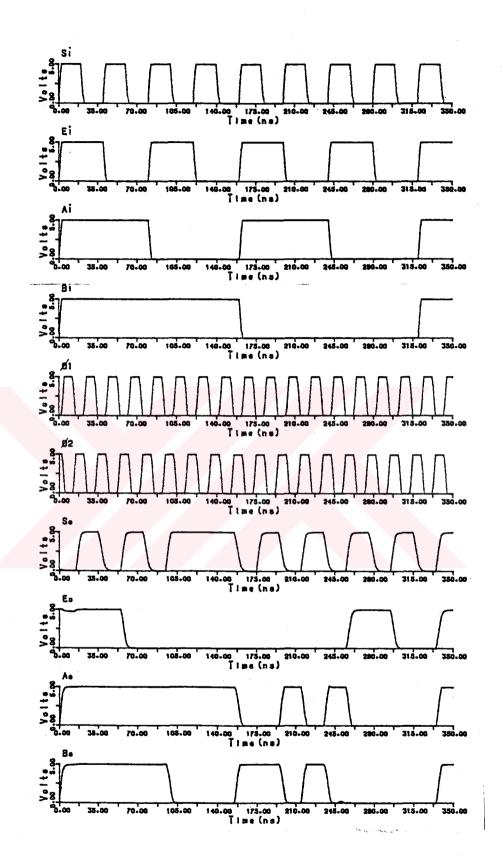

|   |     | 5.2.1  | Compare-and-Swap Unit-2 (CSU2)                         | 46         |

|   |     | 5.2.2  | Delay Unit                                             | <b>5</b> 1 |

|   |     | 5.2.3  | Clock Buffers                                          | <b>5</b> 1 |

|   |     | 5.2.4  | Chip Overall Layout                                    | 51         |

|   |     | 5.2.5  | An Overview of the Real-Time Median Filter Chip        | <b>5</b> 5 |

|   |     | 5.2.6  | Testing of the Real-Time Median Filter Chip            | 55         |

|   | 5.3 | Applie | cations of the Chips                                   | <b>5</b> 9 |

| 6 | RE  | SULTS  | S AND CONCLUSIONS                                      | 62         |

|   | AP  | PEND   | IX                                                     | 70         |

|   |     | Test I | Pattern Generator for the Real-Time Median Filter Chip | 70         |

## LIST OF FIGURES

| 3.1  | The ordinary odd/even transposition network $(w = 9)$               | 11 |

|------|---------------------------------------------------------------------|----|

| 3.2  | The extensible median filter network $(w = 9)$                      | 13 |

| 3.3  | The compare-and-swap unit-1 (CSU1): a) block diagram, b)            |    |

|      | state diagram, c) operations                                        | 14 |

| 3.4  | Interconnections of the extensible median filter networks for       |    |

|      | $w=9.\ldots\ldots$                                                  | 15 |

| 3.5  | The real-time median filter network                                 | 17 |

| 3.6  | The compare-and-swap unit-2 (CSU2)                                  | 18 |

| 4.1  | The VLSI design steps                                               | 23 |

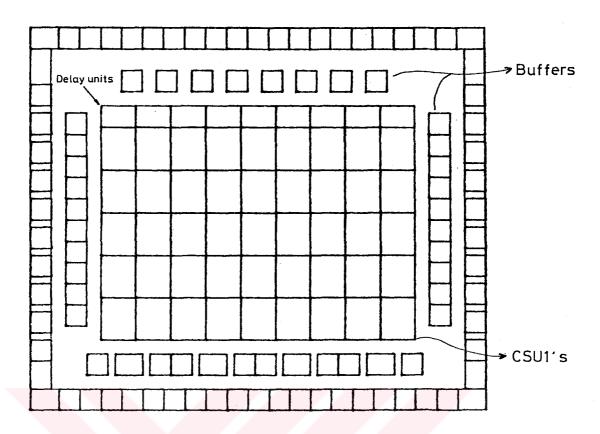

| 5.1  | The floor plan                                                      | 30 |

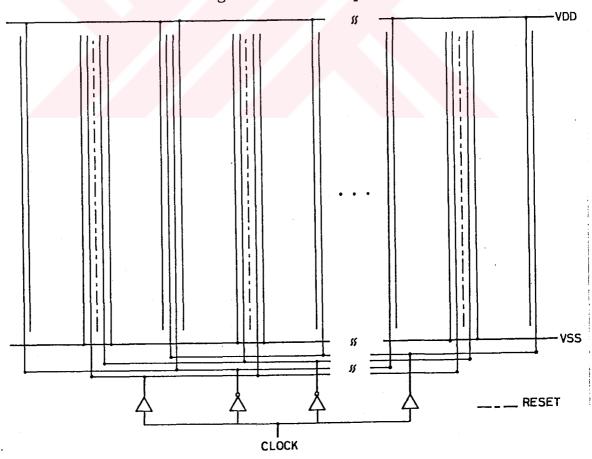

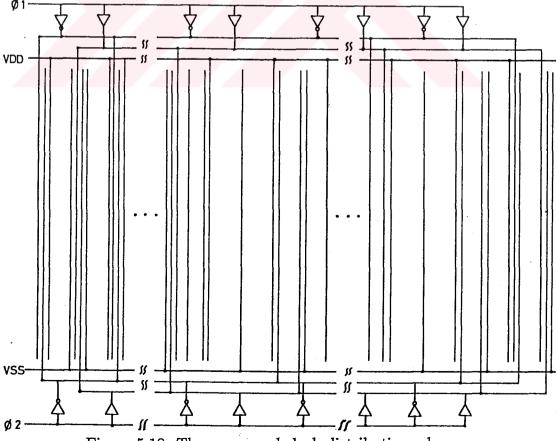

| 5.2  | The power and clock distribution scheme                             | 30 |

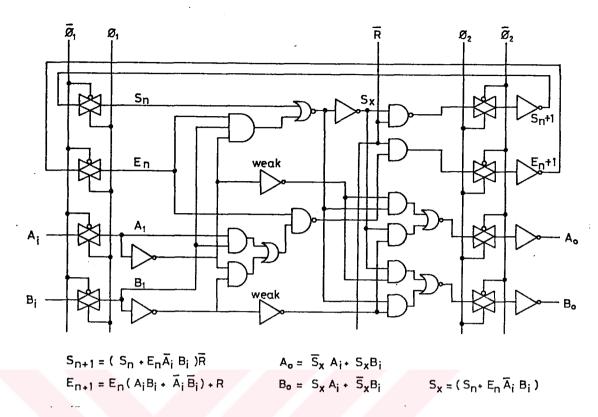

| 5.3  | Circuit diagram of the CSU1                                         | 32 |

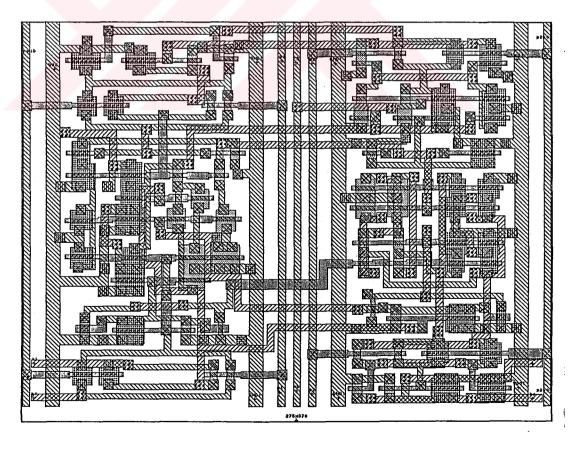

| 5.4  | Layout of the CSU1                                                  | 32 |

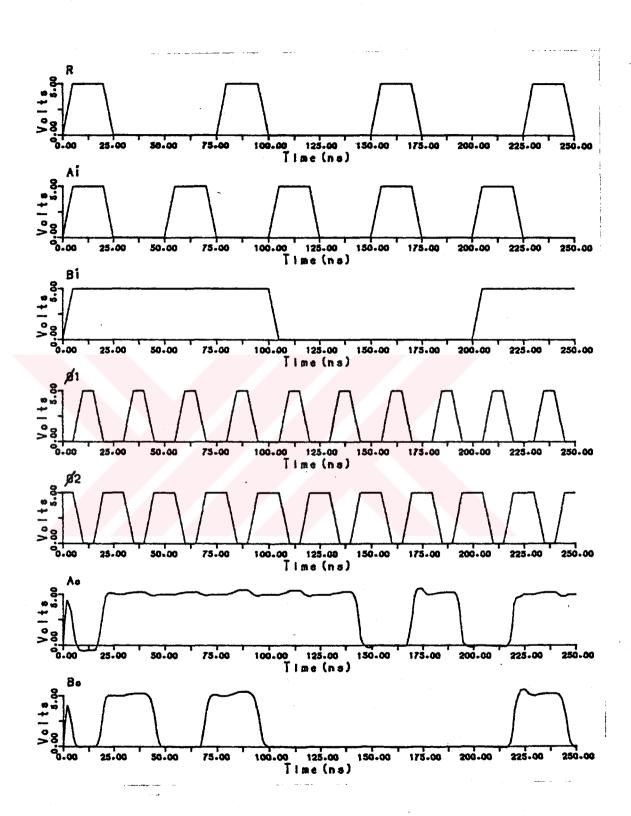

| 5.5  | Timing simulation results of the CSU1                               | 33 |

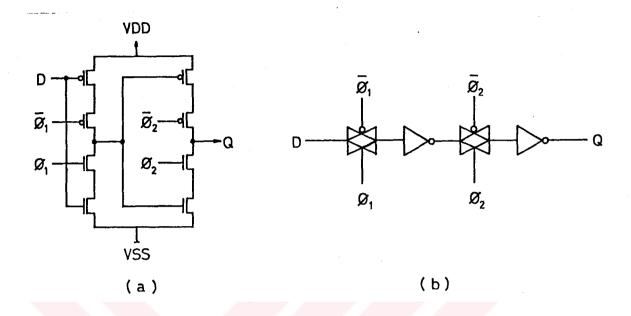

| 5.6  | Circuit diagram of the shift register cell                          | 35 |

| 5.7  | Layout of the shift register cell                                   | 35 |

| 5.8  | Timing simulation results of the shift register cell                | 36 |

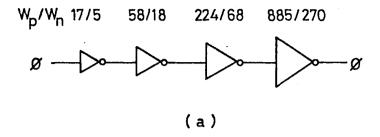

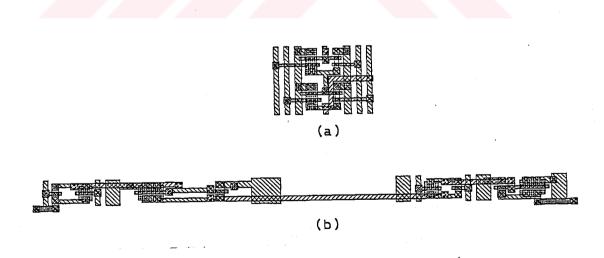

| 5.9  | Circuit diagrams of the clock buffers                               | 37 |

| 5.10 | Layouts of the clock buffers: a) noninverting, b) inverting         | 37 |

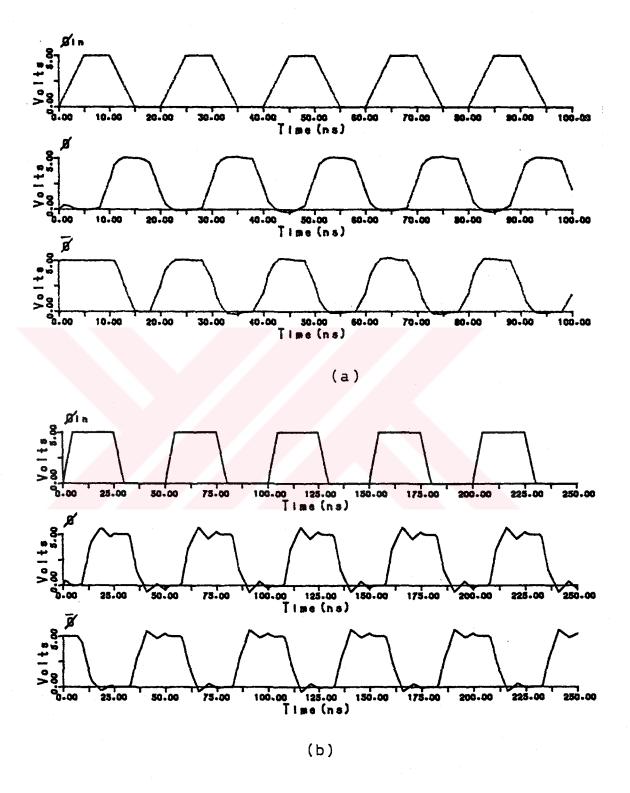

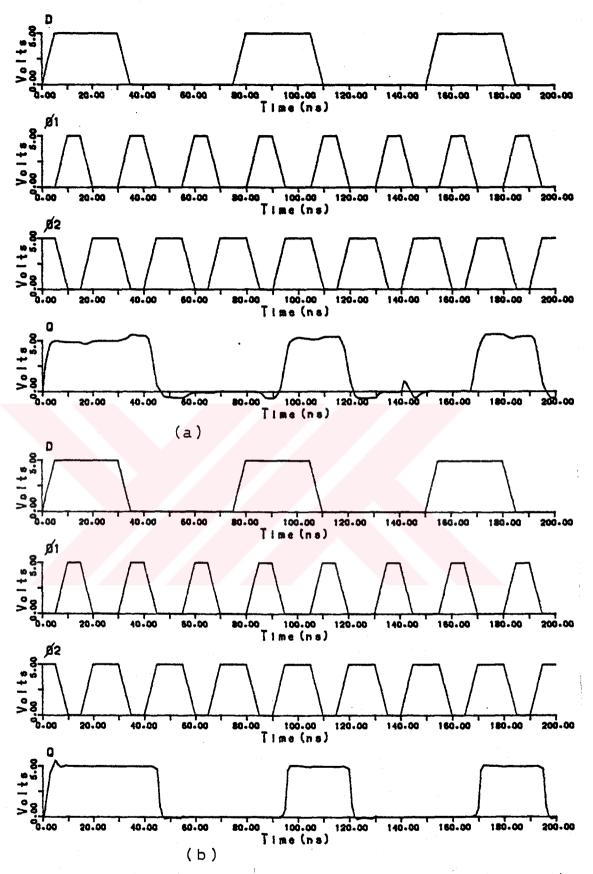

| 5.11 | Timing simulation results of the clock buffers: a) for 50 MHz,      |    |

|      | b) for 20 MHz                                                       | 39 |

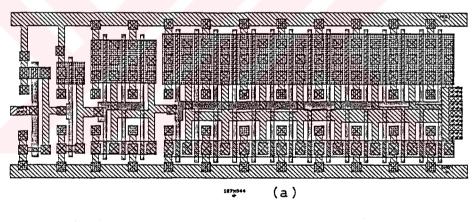

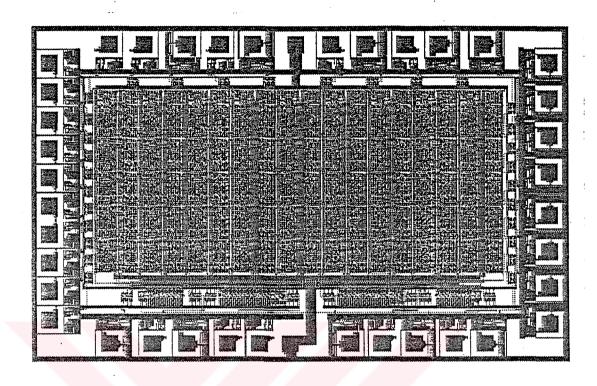

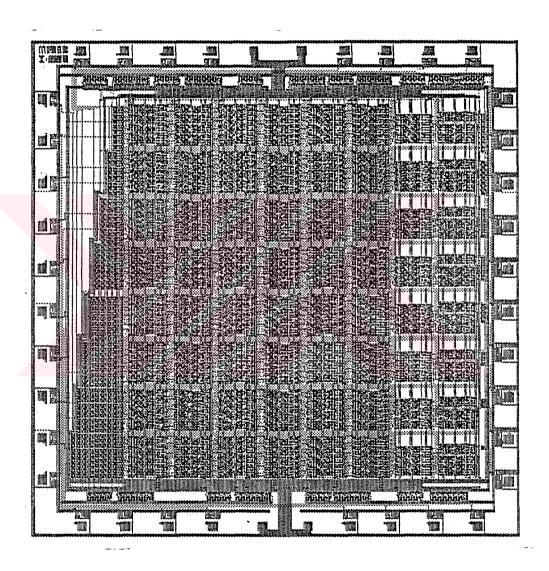

| 5.12 | Complete layout of the extensible median filter chip                | 40 |

| 5.13 | Logic simulation results of the extensible median filter chip       | 41 |

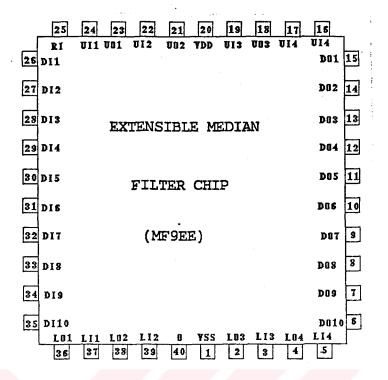

| 5.14 | Pin configuration of the extensible median filter chip              | 42 |

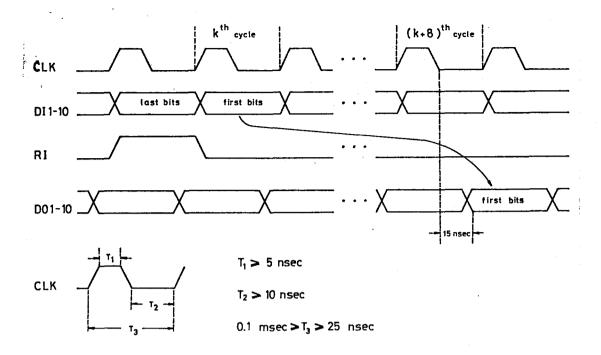

| 5.15 | Timing diagrams for data load and read operations of the ex-        |    |

|      | tensible median filter chip                                         | 43 |

| 5.16 | Interconnections of the extensible median filter chips for $w=25$ . | 44 |

|      |                                                                     |    |

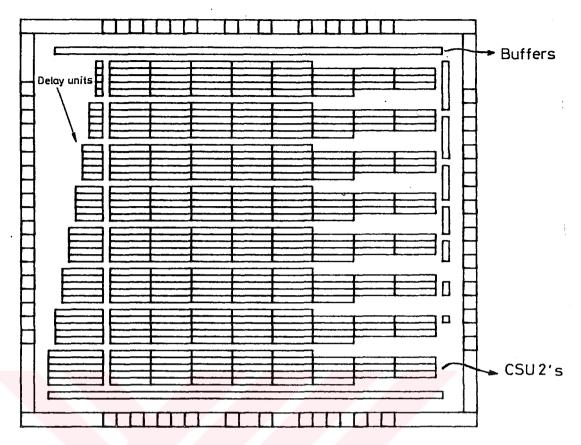

| 5.17 | The floor plan                                                 | 47 |

|------|----------------------------------------------------------------|----|

| 5.18 | The power and clock distribution scheme                        | 47 |

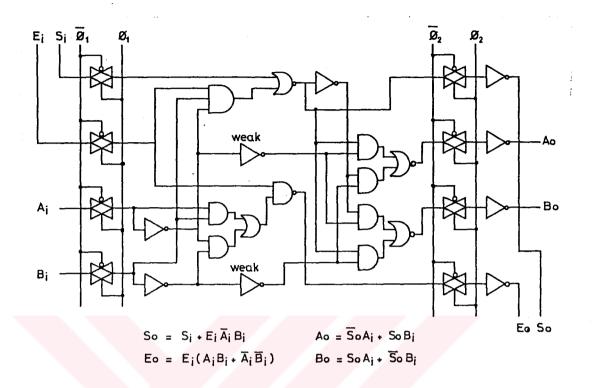

| 5.19 | Circuit diagram of the CSU2                                    | 49 |

| 5.20 | Layout of the CSU2                                             | 49 |

| 5.21 | Timing simulation results of the CSU2                          | 50 |

| 5.22 | Circuit diagrams of the delay units used at the: a) inputs, b) |    |

|      | internal stages of the the real-time median filter chip        | 52 |

| 5.23 | Layouts of the delay units used at the: a) inputs, b) internal |    |

|      | stages of the the real-time median filter chip                 | 52 |

| 5.24 | Timing simulations of the delay units used at the: a) inputs,  |    |

|      | b) internal stages of the the real-time median filter chip     | 53 |

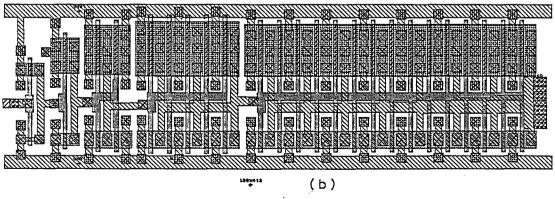

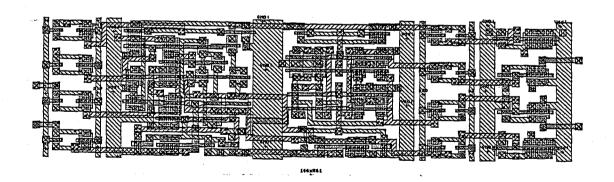

| 5.25 | Overall layout of the real-time median filter chip             | 54 |

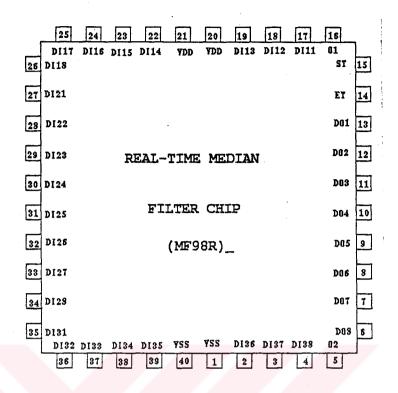

| 5.26 | Pin configuration of the the real-time median filter chip      | 57 |

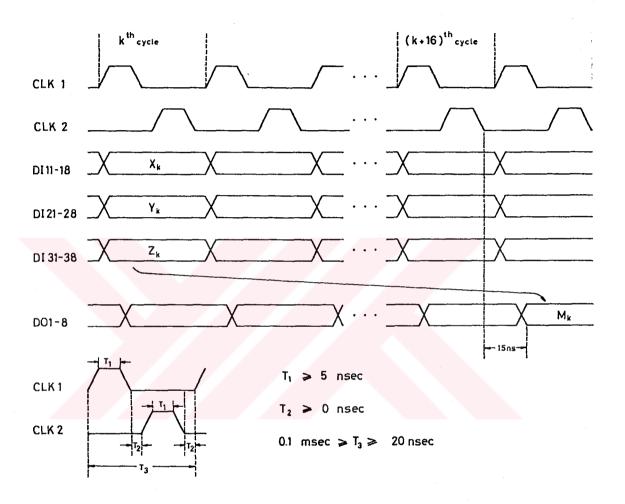

| 5.27 | Timing diagrams for the data load and read operations of the   |    |

|      | real-time median filter chip                                   | 58 |

## LIST OF TABLES

| 5.1 | Logic simulation results of the CSU1                         | 34 |

|-----|--------------------------------------------------------------|----|

| 5.2 | Pin labels of the extensible median filter chip              | 40 |

| 5.3 | Functions of the I/O's in the normal mode of the extensible  |    |

|     | median filter chip                                           | 43 |

| 5.4 | Logic simulation results of the CSU2                         | 48 |

| 5.5 | Logic simulation results of the real-time median filter chip | 56 |

| 5.6 | Pin labels of the the real-time median filter chip           | 57 |

| 5.7 | A sample of the test vectors and corresponding outputs. The  |    |

|     | IKJ/OKJ:J'th input/output of the K'th block of the real-time |    |

|     | median filter sorting network                                | 60 |

| 6.1 | Main features of the chips                                   | 63 |

|     |                                                              |    |

#### 1. INTRODUCTION

#### 1.1 Median Filter

The median of a group, containing an odd number of elements, is defined as the middle most element, when the elements of the group are sorted. For example, given five elements, 9, 0, 23, 145, 67, to find the median, the numbers are sorted as 0, 9, 23, 67, 145. Then, the median is 23 which is the middle most element of the sorted sequence. A median filter finds the median of a number of elements at its input.

In many signal and image processing applications, it is necessary to smooth the noisy signals while at the same time preserving the edge information. The most commonly used smoothing techniques are the linear filtering [1], the averaging filtering [2], and the median filtering [3,4]. The linear filters smooth the noisy signals but also the sharp edges. In addition, the impulsive noise components can not be suppressed sufficiently by the linear filtering and the digital implementation of the linear filters can be bulky and slow. On the other hand, the generalized mean filters have the disadvantages of allowing a small number of outlier points that distort the filtered output signal, and also deleting the edge information. The median filters have been better alternatives because of their some very interesting properties: they

- can smooth the transient changes in signal intensity (e.g., noise),

- are very effective for removing the impulsive noises from the signals,

- preserve the edge information in the filtered signal, and

- can be implemented by using very simple digital nonlinear operations.

Because of these properties of the median filters, they are frequently used in various signal and image processing applications, such as seismic signal

1

processing, speech processing, computerized tomography, medical imaging, robotic vision, pattern recognition, peak detection, coding, and communication.

In the applications for standard median filtering of the signals and images, a window of size w, where w is odd, is moved along the sampled values of signal or image, the median ((w+1)/2)nd largest one) of the samples within the window computed and written as the output pixel corresponding to the location of the center of the window. The median computed at this operation is called the running or the moving median. Since the size of the window is constant, the number of incoming elements is equal to the number of outgoing elements. The detailed discussion of the theoretical analysis of the median filters and their properties can be found in [5,6,7,8,9,10,11]. The applications of the median filters in speech processing and image processing were studied in [12,13,14].

#### 1.2 Motivation and Approach

The purpose of this study is to have an exercise in VLSI design by completing a part of a project which consists of the design and implementation of a flexible VLSI image processor. For this purpose, the VLSI design of a general purpose median filter unit is chosen since this unit can also be used in any signal or image processors.

Different two-dimensional applications require different window sizes and word-lengths for median filtering. The window size varies from  $3 \times 3$  to quite larger ones. Also, the required speed of the filtering operation varies depending on the application. A median filter which is intended as a component of a general purpose signal or image processor must meet these changing demands. For this reason, the median filter that we design should satisfy the following constraints:

- the word-length must be unlimited,

- the filter should be extensible to larger window sizes, and

- the filter should be able to operate at real-time rate which is about 30 mega medians per second for a 1024 × 1024 frame with 25-30 frames per second.

We propose a solution to this problem in the form of two single-chip median filter networks which form a general purpose median filter unit. The networks are implemented in 3-micron CMOS using the full-custom VLSI design techniques. One of the chips is designed for unlimited word length and extensibility for larger window sizes whereas the other one is for the real-time median filtering applications. The chips can be selectively used in a processor environment.

#### 1.3 On the Performance of Algorithms

The algorithms that are efficient for software implementation minimize the number of computations and hence the computation time. In VLSI, the cost is determined by the modularity and the internal communication between the modules. This is because the irregular structures and especially complex communication interconnections increase the chip area considerably. The computation is cheap in VLSI, because the recent developments offer designers very high potential for parallel operations. Hence, a good algorithm for VLSI implementation does not necessarily require the minimal computation but should possess the following properties: the algorithm

- can be implemented by using only a few different simple units,

- must have a simple and regular communication and control scheme,

and

- should employ the parallelism and pipelining.

A class of algorithms, called the *systolic algorithms*, have these properties. These algorithms for various computational problems have been discussed in [15,16,17,18,19,20]. The design cost of the special-purpose chips can be brought down by a systolic algorithm [21]. Application of the systolic data-flow concepts at the low level implementation of circuits such as comparison and addition will result in pipelined regular structures, small propagation delays and high throughput independent of the circuit size.

In design and implementation of a median filter in VLSI which is a specialpurpose design work, the selection of the algorithm determines the cost and performance. Hence, much effort to the choice of algorithm should be given. The optimizations at circuit or layout level will play rather minor role on the overall cost and performance.

#### 1.4 Benefits

In this study, we have followed all the steps of VLSI chip design starting from the problem definition to the test pattern generation of the chips. As a result, we have gained experience on VLSI design, and a median filter unit is obtained as a versatile component of a general purpose digital signal or image processor. Furthermore, the designed chips have significant importance since they are two of the first three custom chips designed and implemented in Turkey (the third one is a correlator chip designed at this university [22,23]).

#### 1.5 Organization of Thesis

In the next chapter, a review of the median filtering techniques and algorithms is given. Chapter 3 covers the algorithms of the extensible and the real-time median filters. The VLSI design approach, circuit technique, and the VLSI design tools are described in Chapter 4. In Chapter 5, the VLSI implementation of the chips, their simulations, testings and possible applications are presented. Finally, the results and conclusions of this study are discussed in Chapter 6.

#### 2. A SURVEY OF MEDIAN FILTERING

In this chapter, we will go over some of the median filtering techniques used in different practical applications and pass to the survey of median filtering algorithms for hardware implementation.

#### 2.1 Median Filtering Techniques

Median filters can be used to suppress the impulsive noises, and to preserve the edges on images. In some applications, suppression of the noise may be more important than preserving the edges, or vice verse. In addition, median filter can be used to enhance the edges. Furthermore, in some cases, the median filters may fail to provide sufficient smoothing of nonimpulsive noise components. In order to solve these problems, various median filtering techniques were developed to increase the performance of the median filter for a set of particular applications. Here, we summarize the most commonly used median filtering techniques.

### 2.1.1 Finding Root Signal

If a signal is not affected by passing through a median filter, this signal is termed a *root signal* of that filter. Any root of a median filter with a particular window size is also a root of any median filter with a smaller window size. In order to remove the nonimpulsive noise components quite well, it is sufficient to obtain the root signal [24].

One can use either an adaptive-length median filter [25] or pass the signal from a fixed sized median filter successive times for better nonimpulsive noise suppression. Any signal of length  $S_l$  samples is reduced to its root after at most  $(S_l - 2)/2$  successive passes by any median filter [5]. The cascaded median filters can be used for this purpose. Arce and Stevenson has reported that the cascade technique is better than a larger single median filter [26].

The median filtering of an arbitrary discrete levels signal to its root is equivalent to decomposing the signal into binary signals, filtering each binary signal to a root with a median filter, and then reversing the decomposition [27]. For application of the decomposition technique, a threshold test is performed for each sample value such that if the sample value is greater than the threshold value, then a 1 assigned to that sample as the new value, and otherwise the new value is 0. The selection of the threshold value and other details can be found in [27].

#### 2.1.2 Recursive Median Filtering

The operation of the recursive median filter is the same as that of the standard median filter except that, at each step, the leftmost (w-1)/2 sample values in the moving window are replaced with the previous (w-1)/2 output sample values [28,29]. The most interesting property of the recursive median filter is that any signal can be reduced to a root after the first pass. Due to this fact, the recursive median filters are much efficient in the applications that require the fast finding the root signals, such as peak detection and coding [12]. This class of median filters can also be used with other median filtering techniques such as the recursive median filtering with threshold decomposition [27] and the recursive separable median filtering [30].

#### 2.1.3 Generalized Median Filtering

An alternative technique to increase the efficiency of the nonimpulsive noise reduction or/and the edge preserving is the generalized median filtering. A generalization using linear combinations of order statistics is studied in [31]. Another generalization as a combination of a linear and median filters, in particular a combination of L and M filters, is analyzed in [32]. In the applications of the generalized median filtering, there is a tradeoff between noise suppression and the edge preservation; the generalized median filters are frequently used for edge detection [33,34,35,36]

#### 2.1.4 Separable Median Filtering

The median filtering in two-dimensions can be performed by using a two-dimensional median filter with a window of arbitrary shape. But the most common windows are the square and cross-shaped windows. An alternative

technique is the separable median filter which consists of two one-dimensional median filters that operate in the horizontal and vertical direction [30]. This technique is efficient for finding the root signal in two-dimensions quickly by using two separable recursive median filters instead of two standard median filters [37].

#### 2.1.5 Weighted Median Filtering

The weighted median of a group of the elements is defined as the middle element of the sequence obtained in such a way that, the elements of the group are first multiplied with proper weight coefficients and then sorted [38]. It is shown that the selection of the weight coefficients represents a trade-off between the noise reduction and the preservation of the edge information. The maximum noise reduction is achieved when all the weight coefficients are equal, that is the same as the case of standard median filtering, whereas when the weight coefficients decrease as we move away from the center of the window, the preservation of edges and small details improves at the expense of noise suppression.

Different applications require the selection of a proper median filtering technique. However, the standard median filtering technique is the fundamental one, since it is used as the basic component in the realizations of many median filtering techniques. Due to this fact, we have considered the design and implementation of a standard median filter rather than any other type of median filters. For this reason, starting from the next section, we will concentrate only on the standard median filter algorithms and implementations.

#### 2.2 Median Filtering Algorithms

The median filtering was first proposed by Tukey in 1974 [3,4]. From that time, there have been much efforts to develop fast off-line and on-line algorithms.

In 1979, the histogram method was presented [39], [40]. In this method, the median is found by sorting the grey level histogram of the window elements, and updating it as the window moves. The computation time of the method is  $O(\sqrt{w})$  for a square window. The histogram method is an off-line method and not practical for hardware implementation because of the

hardware complexity.

A real-time median filtering algorithm used for finding the running medians was proposed by Ataman et al. [41]. This algorithm is based on the binary representation of the sample values of the the window elements. For finding the running median, the number of 1's are counted in the most significant bits of the binary values of the elements, if that number is greater than (w+1)/2, then the most significant bit of the median is found as 1, else as 0. To find the second bit of the median, only the set of data whose first bits are equal to that of the median is considered and this operation is continued to find the other bits of the median. In order to determine the sets which include the median at each step, an array, called the  $\alpha$ -array, is computed and stored. The hardware implementation of this algorithm requires  $2^L$  words of memory (L is the word-length of an element), and an arithmetic-logic unit for arithmetic and logic operations. The parallel implementation of the algorithm needs L logic and L memory units. The main disadvantage of this algorithm is that its hardware implementation for a window size can not be used for finding the exact median for a larger window size.

A variation of Ataman's algorithm is given in [42]. In this algorithm, an m-array is computed instead of the  $\alpha$ -array of Ataman's algorithm. The k'th element of the array indicates the number of the samples in the window greater than or equal to (k-1). It is reported that the computation time of this algorithm is less than that of the Ataman's algorithm since updating the m-array is faster than that of  $\alpha$ -array.

The most commonly used median filtering algorithms are based on sorting. Many of the basic sorting algorithms, especially for software implementation, are collected and analyzed in [43]. The VLSI complexity of sorting is studied in [44].

A sorting network for VLSI implementation is proposed in [45]. The area and time evaluation shows a very high performance, but on the other hand the hardware complexity, especially in the internal communication structure, and also the extensibility to larger data groups are the remaining problems of this network.

Two well known networks for sorting and switching are the bitonic sorting and the shuffle exchange networks. An overview of two chips based on the bitonic and shuffle networks is presented in [46]: the bitonic sorting network consists of  $\frac{w}{2} \times \frac{1}{2}(log_2w)(log_2w+1)$  switch elements ( $\frac{w}{2}$  elements at each row),

whereas the shuffle network has  $\frac{w}{2} \times log_2 w$  switch elements. The chips are designed for sorting 64 elements with an unlimited word-length. Greater number of elements can be sorted by using more than one chips. The main disadvantages of this configuration are the low throughput (one output per L clocks) and the increase in the area and design time of the chips due to the internal communication. Also, since the structure is based on the binary trees, there is some waste of area in an implementation if the number of inputs is not an integer power of 2. For example, if w = 9, then a bitonic sorter of size 16 will be required. The configuration may be preferable for a large w.

A separable median filter was implemented in hardware as a component of an image processor using the odd/even transposition sorting networks [47]. The filter consists of two pair of cascaded sorters. One of the pairs operate in vertical direction while the other operating in the horizontal direction of the frame. The cascaded connection is preferred to increase the efficiency of the separable median filter. Each sorter has six 8-bit comparators to sort three pixels. This sorter can be implemented by using the bit level systolic approach to increase the performance.

A bit level pipelined systolic odd/even transposition sorting network with very high throughput was proposed by Oflazer [48] for median filtering. The network consists of L blocks of w(w-1)/2 bitwise compare-and-swap units. The network is a regular array of the compare-and-swap units, hence it has a very modular structure with a simple internal communication scheme. The network is implemented for w=5 and L=8 as a single-chip one-dimensional median filter. The throughput of the filter is one median per clock. The clock period is determined by the delay of a bitwise compare-and-swap unit; the clock rate of Oflazer's filter chip is 10 MHz. The chip is not extensible for larger window sizes and the word-length is fixed to 8. The odd/even transposition network is not preferable for large w because the area is proportional with  $w^2$ .

There are some other median filtering algorithms presented in the literature. These algorithms are for implementation in software using high level languages hence they are out of the focus in this study. For two of such algorithms, reader is addressed to [49] and [50].

#### 3. GENERAL PURPOSE MEDIAN FILTER

In this chapter, firstly, we will summarize the ordinary odd/even transposition sorting network. Then, the extensible and the real-time median filter networks which are based on the odd/even sorting are explained in detail. Finally, the feasibilities of the VLSI implementations of the networks are discussed.

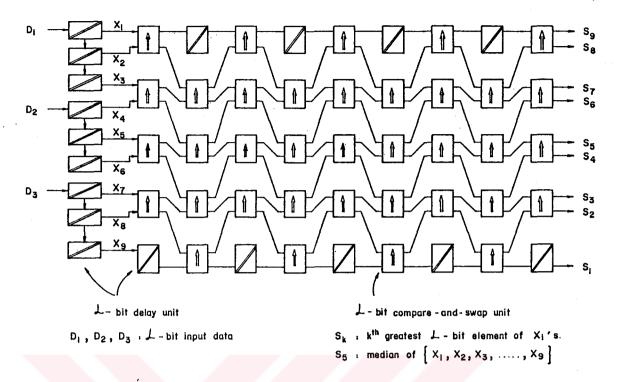

#### 3.1 Odd/Even Transposition Sorting Network

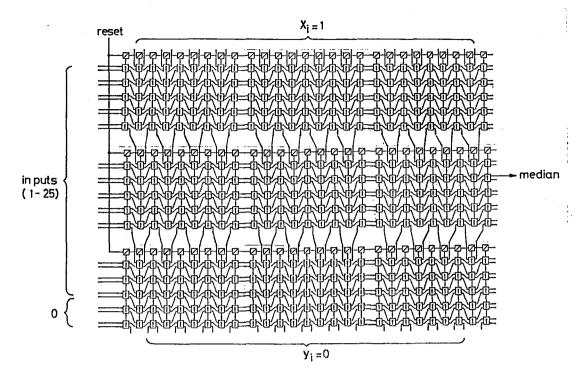

The odd/even transposition sorting network is a pipelined modular structure consisting of w compare-and-swap stages [43]. A compare-and-swap stage has (w-1)/2, w is odd, full-word (L-bit) parallel compare-and-swap units and an L-bit delay unit to delay the window element which is not compared at that stage. Each compare-and-swap unit operate on the odd and even pairs of the window elements alternately (Fig. 3.1). Odd pairs are in the form of  $(X_n, X_{n+1})$  where n is odd, whereas n is even for even pairs. Each L-bit compare-and-swap unit compares the two L-bit elements at its inputs and interchanges them if necessary so that the larger one of the elements will be at the "top" and the smaller one will be at the "bottom" output. At the output of the last stage, the input elements will be sorted such that the largest will be at the "top" and the median will be at the middle.

If the odd/even transposition network described above is implemented in hardware as a single chip median filter for a fixed window size,  $w_0$ , then one can not use that chip to find the exact medians of the window elements that is larger than  $w_0$ . On the other hand, there is no flexibility on the wordlength because the compare-and-swap unit can be implemented only for a fixed word-length in this configuration. Furthermore, the compare-and-swap unit can complete its job after an L-bit comparison resulting in a large propagation delay. Although, the throughput of the network is one L-bit median

Figure 3.1: The ordinary odd/even transposition network (w = 9).

per clock (assuming a sequential logic implementation), it is not possible to clock this network with a frequency required for the real-time operation rate since the clock period will be at least the time required for a full-word comparison. All these results show that the odd/even transposition network in the configuration described above can not satisfy any of the requirements for a general purpose median filter (extensibility in window size, unlimited word-length, and real-time application capability).

However, the odd/even transposition network can be modified so that resultant structure(s) can satisfy our needs. Starting from this approach, two median filter networks are obtained. Both of these networks are bit-level, systolic and pipelined odd/even transposition sorting networks that employ all the advantages of the systolic algorithms and satisfy the listed requirements for a general purpose median filter. The networks serve different purposes: one of them designed for unlimited word-length and extensibility to larger window sizes whereas the other one is for real-time applications.

#### 3.2 Extensible Median Filter Network

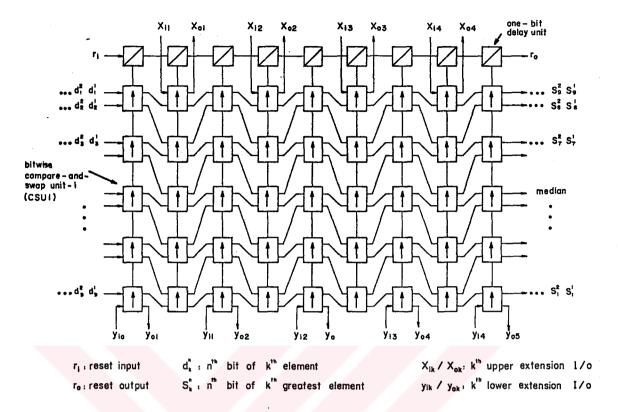

The odd/even transposition network shown in Fig. 3.1 is modified such that every operation is in the bit-serial form. We have used a bitwise compare-and-swap unit so that data flow is reduced to flowing of bit streams which eliminates the limit on the word-length and the large delay due to full-word comparison. In addition, the replacement of the delay units by the compare-and-swap units come up with extensibility in the window size. In the following paragraphs, the resultant extensible network is described in detail.

The extensible odd/even transposition sorting network is a pipelined systolic structure consisting of w = 9 compare-and-swap stages that operate on the consecutive pairs of window elements alternately. A compare-and-swap stage consists of (W+1)/2 bitwise compare-and-swap units. Each of these units compares the two one-bit numbers at its inputs and interchanges them if necessary so that the larger one is at the "top". At the output of the last stage, the data will be sorted such that the largest will be at the "top", and the median will be at the middle.

At each clock, one bit from each word (total of w bits) enters the network and one bit of the median is obtained at the output. The flow is from the most significant bits toward the least significant bits both at the input and the output. Due to serial bitwise data flow, this structure allows arbitrary word-length, L. The network is given in Fig. 3.2 for W = 9.

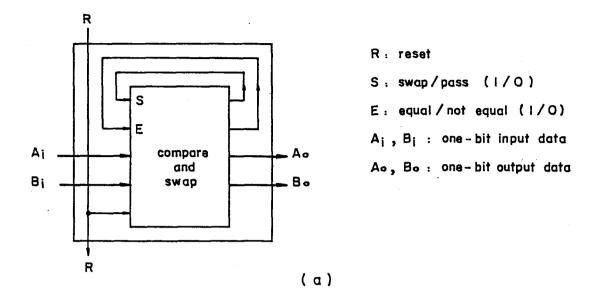

The bitwise compare-and-swap unit, CSU1, has two one-bit data inputs  $A_i$  and  $B_i$ , a reset input R, and two one-bit data outputs  $A_o$  and  $B_o$ . It also has two internal parameters S (1/0: swap/pass) and E (1/0: equal/not equal) which are updated and stored in the CSU1 (Fig. 3.3). Because of the feedbacks S and E, the best structure for the CSU1 is a finite state machine to have a reliable timing [46]. The CSU1 compares  $A_i$  and  $B_i$ , and either passes them unaltered, or swaps them. It has three legal operation states: equal state, pass state and swap state. The present state values of S and E shows the subresult of the bitwise comparison of the more significant bits while the next state values indicate the new subresult.

CSU1 is set to the equal state (S = 0, E = 1) by the reset signal R at the beginning of each computation cycle. This is the instant after the least significant bit of the previous cycle leaves and before the most significant bit of the next cycle enters the CSU1. Thus the reset signal also flows through

Figure 3.2: The extensible median filter network (w = 9).

the stages of the network. For this purpose, a chain of the bitwise delay units are used to reset the stages at appropriate time instants (see Fig. 3.2).

During the computation, the CSU1 stays in the equal state (S = 0, E = 1) and passes the input data unaltered  $(A_o = A_i \text{ and } B_o = B_i)$  as long as the two input bits are equal as they flow in. However, it locks itself into the pass state when it first finds that  $A_i > B_i$  and passes the inputs unaltered. On the other hand, it locks itself into the swap state when it first finds that  $A_i < B_i$  and swaps the inputs,  $A_o = B_i$  and  $B_o = A_i$ .

The extension I/O's  $(x_{i/o}$ 's and  $y_{i/o}$ 's, see Fig. 3.2) of the extensible median filter network are used to extend the filter to the window sizes larger than w = 9. If the upper and lower extension inputs  $(x_i$ 's and  $y_i$ 's) are connected to logic 1's and 0's, respectively, so the corresponding CSU1's operate as delay units. This is due to fact that the CSU1 will always pass the inputs unaltered if its inputs are 1X or X0  $(A_i = 1, B_i = X \text{ or } A_i = X, B_i = 0)$ , where X indicates don't care (i.e, X may be 1 or 0). On the other hand, if the network given in Fig. 3.2 is used as an array element to find the exact medians of window elements for w > 9 by connecting them as in Fig. 3.4.

Figure 3.3: The compare-and-swap unit-1 (CSU1): a) block diagram, b) state diagram, c) operations.

Figure 3.4: Interconnections of the extensible median filter networks for w = 9.

then these CSU1's operate as usual except those corresponding to the upper extension I/O's of the upper most network and corresponding to the lower extension I/O's of the lowest network. In this case, the CSU1's corresponding to the interconnected extension I/O's of the networks are not forced to lock in one state by means of extension signals, but they are free to enter any state depending on their inputs. As a result, the extensibility to indefinitely large windows is achieved: in the normal mode, it is possible to compute the exact median of a group of 9 elements using only one network, and for groups of w elements where w > 9, at most  $[w/9]^2$  ([.] indicates the smallest greater integer) networks are needed with appropriate interconnections of the extension and data I/O's similar to the connection scheme in Fig. 3.4.

The extensible network described above generates its outputs with a pipeline delay of w+L clocks and after the network is full, it finds one median per L clocks. The network can operate at a clock rate that is determined by the delay of one compare-and-swap unit which consists of, at least, the delay of a few cascaded bitwise comparisons and a  $2 \times 1$  multiplexing. Although, the resulting speed can be sufficient for the real-time median filtering of the  $512 \times 512$  frames with L < 5, it is less than the real-time operation rate for the  $1024 \times 1024$  frames with L > 1.

#### 3.3 Real-Time Median Filter Network

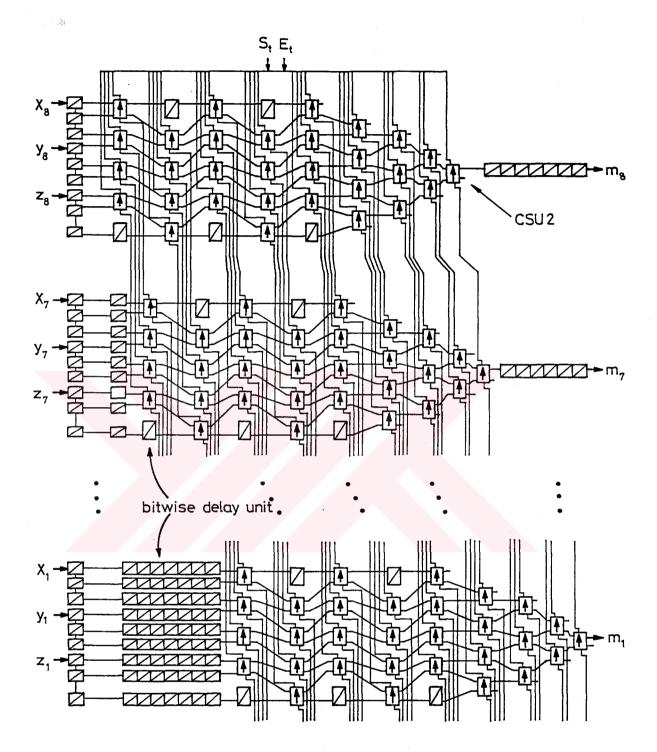

In order to achieve a real-time operating rate for the  $1024 \times 1024$  resolution frames, the only way is to find a structure that has a very high throughput capability. The only solution we have found is the odd/even transposition sorting network configuration proposed by Oflazer [48]. In the following section, we will describe the real-time median filter network designed for w=9 and L=8 which is a variation of Oflazer's network that was designed for w=5 and L=8.

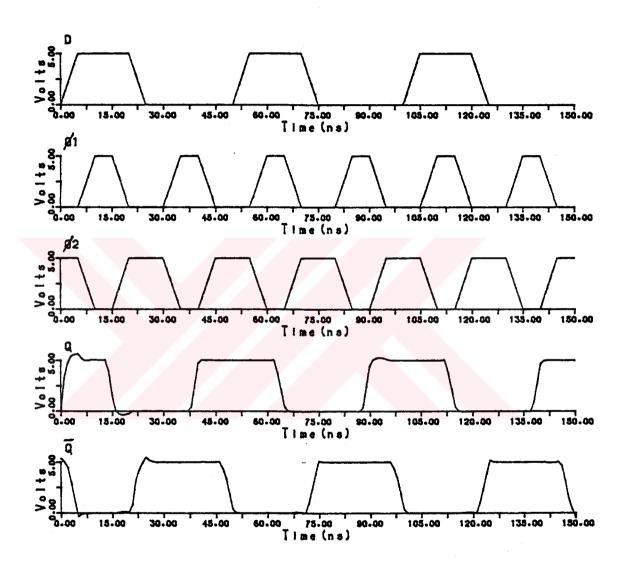

A median filter with very high throughput can be designed by interconnecting L number of the pipelined odd/even transposition sorter blocks in parallel and applying the systolic concepts at the bit-level. The block diagram of the overall network for w=9 and L=8 is shown in Fig. 3.5. In this network, the data enter in such a way that the most significant bits go to the first block, the second most significant bits to the second block and so on. There are nine 8-bit input data, and one 8-bit median is obtained per clock. At every clock, three new elements enter the network, corresponding to the new elements of a sliding  $3 \times 3$  window.

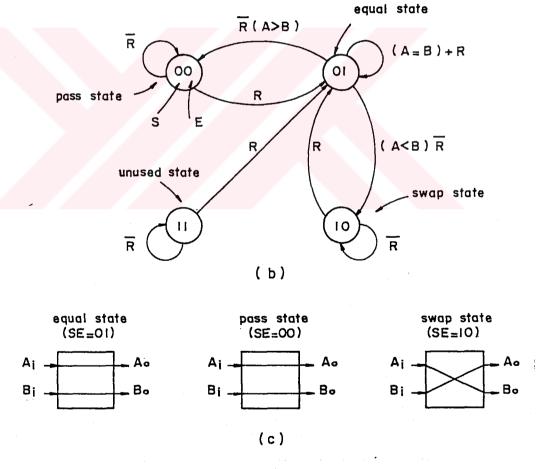

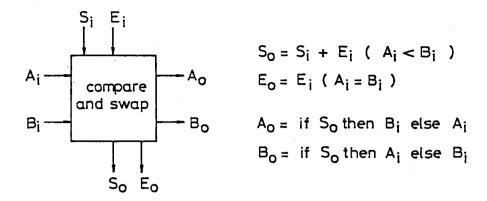

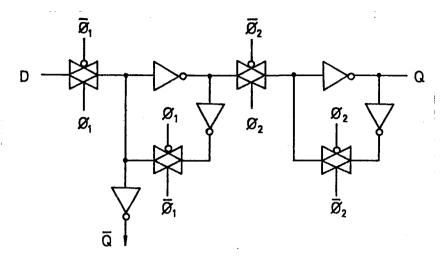

The bitwise compare-and-swap unit, CSU2, used in this network is slightly different from CSU1 in such a way that the S and E parameters of CSU1 are external parameters in CSU2. These parameters are taken as inputs  $S_i$  and  $E_i$  (the cumulative subresult of the bitwise comparison of the more significant bits) from the upper block, used, updated and sent out as  $S_o$  and  $E_o$  (the new cumulative subresult) to the lower block. Hence, CSU2 does not have any storage or the reset input signal. The functional description of CSU2 is given in Fig. 3.6.

During the computation, CSU2 compares the inputs  $A_i$  and  $B_i$  and passes or swaps them conditionally depending on  $S_i$  and  $E_i$ . If  $E_i = 1$  and  $S_i = 0$ , it passes or swaps the inputs so that larger one goes to  $A_o$  and the smaller to the  $B_o$ . On the other hand, if  $E_i = 0$  and  $S_i = 1$ , CSU2 passes/swaps the inputs independent to the result of the comparison of the inputs. It also updates  $S_i$  and  $E_i$  and sends out as  $S_o$  and  $E_o$  for the comparison of the less significant bits.

The computation at each stage of a lower block starts after the corresponding stage of the upper neighborhood block completes its operation so that the  $S_i$ 's and  $E_i$ 's are ready at input of that stage. As a result of this,

$x_i\,,y_i\,,z_i:i^{\,th}$  bits of the inputs corresponding the new elements in a  $3x\,3$  sliding window.

mi : i <sup>th</sup> bit of the median

$\mathsf{S}_{\mathsf{t}}.\mathsf{E}_{\mathsf{t}}$  : Test inputs for testing of the blocks individually.

Figure 3.5: The real-time median filter network.

$S_i$  and  $E_i$  indicate the cumulative subresult of the bitwise comparison of more significant bits while  $E_0$  and  $S_0$  indicate the new cumulative subresult.

Figure 3.6: The compare-and-swap unit-2 (CSU2).

each stage of a lower block must operate one clock later compared to the corresponding stage of the upper block. For the same reason, the outputs of a lower block are ready one clock later compared to the upper neighborhood block. In order to employ a proper timing, the pipeline delay units are used both at the input and the output of the network such that k'th block from top has (k-1) delay units at its inputs and (L-k) delay units at its output, where k=1,2,...L (see Fig. 3.5).

The throughput of the network is one full-word median per clock. The clock period is determined by the delay of one CSU2. Recent VLSI technology allows the implementation of CSU2 at a speed larger than the real-time rate for the  $1024 \times 1024$  frames with L=8.

#### 3.4 Feasibility of VLSI Implementation

Both of the extensible and real-time median filter networks are regular arrays of bitwise compare-and-swap and delay units. Also, their internal communication schemes are simple and regular. This makes the VLSI implementations to be easy and straightforward. Furthermore, the testing of the VLSI chip may be easily accomplished by the *functional test* techniques [51], since the operations of the cells may be selectively probed by issuing proper test vectors. The testing operation includes the running of the chip with test vectors as inputs and the comparison of the outputs with expected results. The testing can be performed on-line or off-line, in any case, the comparison time

is reasonably short. The generation of the expected results, which are the correct outputs, can be obtained by using a software sorter and a software median filter.

The extensible median filter chip can be tested by using a few hundreds test vectors. If we apply the same element to all of the inputs, then every CSU1 will act in equal state. On the other hand, the sorted inputs will cause all the CSU1's operating in swap state. Consequently, a set of inputs sorted in reverse order will make all the CSU1's operate in swap state. By this way the CSU1's will be tested in all the operation states.

The real-time median filter chip can be tested by using 12,288 ( $8 \times 3 \times 2^9$ ) test vectors. The  $S_i$ 's and  $E_i$ 's at the top of the network are connected to external test control inputs,  $S_t$  and  $E_t$  respectively (see Fig. 3.5). These test control signals are used to isolate the operation of each block from each others, thus the number of test vectors reduced to 12,288. If these test inputs are not used then the number of test vectors will be a few millions. The k'th block can be tested individually with applying logic 1 to all of the upper blocks' inputs so that it receives the external  $S_t$  and  $E_t$  without any change. As a result, each block can be tested by using 1,536 ( $3 \times 2^9$ ) test vectors: all combinations of one-bit 9 inputs times 3, where 3 comes from the legal values of the pair  $S_i E_i$  (01, 00, 10).

The extensible network can be implemented with about 5 K transistors and packaged in 28 pins with 2 × 1 I/O multiplexing whereas the real-time median filter will consist of about 20 K transistors and has 40 pins.

One may choose to implement either the extensible median filter network or the real-time network for a large w, but this not preferable since the area is proportional to  $w^2$ . We have chosen w = 9, because it is the minimum and the most commonly used window size in two-dimensional median filtering applications.

In an attempt to increase the efficiency of the silicon area use, one may consider to design a network which utilizes the same compare-and-swap units (CSU1 and CSU2) in both modes by altering the interconnections via the external select signal. Examination of this possibility did not give the desired result: the chip area turned out to be larger because of the decreased regularity and increased interconnections.

We have examined a network with real-time and unlimited word-length operation capability which is obtained by modifying the Oflazer's network such that all of the  $S_i$  and  $E_i$  inputs of the upper most sorting block and  $S_o$  and  $E_o$  outputs of the lowest block are used as extension I/O's. But VLSI implementation of this network needs an extremely large number of I/O's and unfortunately there is no way to multiplex such a fast network I/O's without decreasing the speed. Hence, it is not feasible and we have not attempted to implement it.

We have also examined the implementation of the two networks in the same chip. The I/O's of the two networks need to be multiplexed. On the other hand, due to very long wiring paths from I/O pads to the networks' I/O's, the strong buffers are needed to drive the large wiring capacitive loads. All these increase the area and decrease the throughput of the networks resulting a reduced speed which makes the real-time operation critical. Also, while one of the networks operates the other one can not be used due to multiplexed I/O's, i.e. one of the networks will be idle at all times. However, the implementation of the networks as two single-chips will avoid these undesired results.

#### 4. VLSI DESIGN METHODOLOGY

#### 4.1 VLSI Design Approach

For the design of any kind of systems, a systematic approach is necessary; especially for the design of complex and large systems, the systematic approach becomes very important. For design of a chip, starting from the problem definition, a systematic way should be followed throughout the design steps. For system design in VLSI, there are some proposed approaches in the literature [21,46,52]. In fact, all approaches are based on dividing the task into four main subtasks which are the problem specification, behavioral description, circuit description, and layout description. The problem specification consists of the detailed definition of the problem and well defined constraints. The behavioral description is the algorithm found as the solution of the problem whereas the circuit and layout descriptions are the implementations of the algorithm in circuit and layout levels. Further divisions of those main subtasks, and their orders depend on the application and probably on the designer.

For our design, the two main subtasks, the problem specification and the behavioral description, are given in the previous chapters. Our problem is to design and implement a general purpose median filter which has the extensibility, unlimited word length and real-time operation capability. We have a solution to that problem in the form of two median filter algorithms that satisfy the constraints. The algorithms are described in terms of the network block diagram representations with functional descriptions. A testing strategy is also determined in that step. All these complete the two main subtasks. Now, the remaining parts are the circuit and layout implementations. Since our networks are modular and have regular and simple communication schemes, it is quite easy to divide the circuit and layout implementation in further subparts: we can design the circuits of the units (compare-and-swap

unit, delay unit, and I/O cells) instead of designing the full network at a time. Obviously, the same partitioning can be performed in the layout level. All these point out the importance of the structured algorithms (e.g. systolic algorithms) since the complexity and difficulty of the tasks at circuit and layout levels are determined by the algorithm.

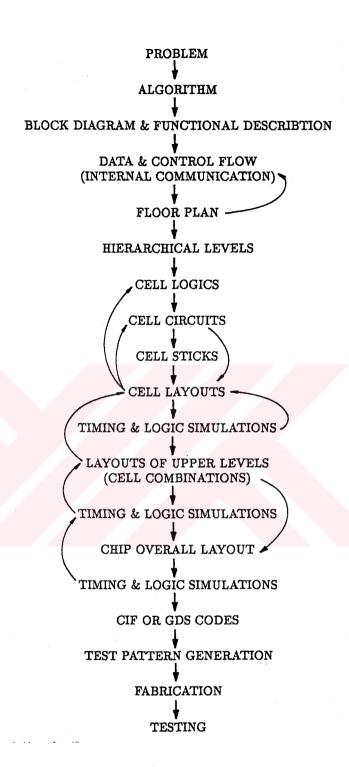

The flow chart given in Fig. 4.1 shows the all steps which we have followed throughout the design of the extensible and the real-time median filter chips. After completing the problem and behavioral description parts, it is essential to construct a floor plan for the chip. The floor plan at this step is not necessarily strict but it is rather flexible for modifications in layout steps. The floor plan strongly depends on the structure of the algorithm, especially on the data flow and control flow of the algorithm. The determination of the hierarchical levels is to classify the groups of the cells and combinations of them level by level such that the lowest level consists of probably the smallest cells and the second level has the units that are the combinations of a number of subcells and so on. Obviously, the top level in the hierarchy is the overall chip.

The next step in the approach is the logic design of cells. If the cells are standard gates or consisting of a few them, then the logic expressions of the cell parameters and their representations in terms of gates need to be determined so that, in the circuit design, the only task will be to replace the gates with their known equivalent circuits. However, if the cells consist of rather large number of gates, then the cell parameters must be expressed as logical functions but the gate representation is not essential because the circuit implementations in transistor level of such cells may be simpler than doing that in gate level. The designer must consider the testing of the chip at this step so that the extra logic circuits are included for testing if necessary.

For the circuit implementation of cells, the designer should choose a circuit design technique in a particular technology (e.g, NMOS or CMOS) which shows the best performance for his application. Each technology offers some circuit techniques employing different properties. The performance of the technologies and circuit techniques vary depending on the design criteria. For example, CMOS is preferable for the designs requiring a low power consumption. We will discuss the selection of a suitable circuit design technique in detail in the next section.

Figure 4.1: The VLSI design steps.

The cell circuits can be mapped into layout either directly or after representing them in stick forms. For a well organized layout, the sticks may be helpful especially to match the constructed floor plan. But in general, the circuits can be directly converted to layout forms by experience. In any way, during the generation of cell layouts, one should care about the physical behavior of the layout (transistor sizes, the resistive and capacitive effects, coupling, etc.). Furthermore, the cell boundaries for cell combinations, the data and control flow between them, and the floor plan must be also considered.

After the generation of cell layouts, the next step is the simulation. The circuits corresponding to the layouts are first extracted and then simulated by using software simulators. The simulation can be performed in two steps: timing analysis and logic analysis. But these two steps can be handled in a single step if there are a few cell parameters. For example, an OR gate can be simulated in a single step, since the parameters are two or three inputs and one output, so that the timing analysis can include also the logic test. If there are reasonably many cell parameters, timing and logic simulations must be performed separately by a timing simulator and a logic simulator, since the logic test with timing simulator will be costly in terms of simulator runtime. According to our experience, the mostly used feedback loop is the cell simulations to cell layouts because the most of the optimizations (speed, area, power, etc.) are performed at the cell level since it is the lowest hierarchical level.

After the cell layouts, the following design step is the layouts of upper hierarchical levels. The simulation at these levels are not essential because all subcells are simulated at the lowest (or lower) level. But if the designer worries about the operation of cells when they are combined, he must perform the necessary simulations. However, if the simulations at lower levels are performed with consideration of the combinations (e.g., some extra capacitances may be need to add to the output capacitances of the cell being simulated), simulations at upper levels are not necessary.

As a last step of the layout level, the overall chip layout is obtained including the I/O cells (buffers, pad drivers, pads, etc.) Finally, a timing and a logic simulation of the chip must be performed. If the simulator run-time is feasible, the logic simulation can be performed by using the test vectors which will be used at the physical testing of the chip. But in general, the

number of test vectors is too large so that the simulation by using them is not possible. In fact, since all the voltages and currents within the chip are observable in the simulation, the simulation with test vectors are not so essential. Consequently, if the test vectors will be used in the simulations, they are generated at that step.

The last two tasks are the generation of the CIF or GDS-II codes and the test patterns (test vectors). The CIF or GDS-II codes are generated by the layout editor automatically. The test vectors can be obtained by either a test pattern generator or manually. In general, the test vectors are generated manually since a general purpose test pattern generator is a very expensive tool. However, one can write a software program to generate the test vectors for his own purpose. The chip testing can be performed either by the manufacturer or by the designer. If the chip will be tested by the manufacturer, the test vectors must be generated before the fabrication.

## 4.2 Circuit Technique

In integrated circuit design, especially for digital applications, NMOS technology has been used with a growing potential since early of 1960's. Due to the increase in density of devices on chips, the power dissipation and complexity of chips have become a serious problem. Since the late 1960's, CMOS technology is being used to overcome these problems by possessing a reasonable low power consumption, a rather easy design and a comparable speed with NMOS [55]. Also, the noise immunity of the CMOS is better than that of NMOS. For these reasons, we have implemented the median filter chips in CMOS technology. In particular, it is a 3-micron double metal double poly n-well process.

During the implementation of circuits in CMOS, one should consider the *latchup*, the *charge sharing*, the *body effect*, and the *noise margins*. [46,56,53,54]. Note that, these problems except the latchup are also present in circuits implemented in any technology (e.g. NMOS).

The latchup problem is caused by the improperly biased parasitic bipolar transistors formed within the CMOS structure. In some cases, these parasitic transistors are biased in such a way that Vdd and Vss (positive and negative power sources) are shorted resulting in destruction of the chip due to excessive current flow. In order to overcome this problem, one should bias the parasitic

transistors so that they do not cause to the short circuit. In practice, one can reduce the chances of the latchup in n-well CMOS by a proper number of connections from the p-substrate to Vdd and from the n-well to Vss, and increasing the distance between n-well and n-diffusion.

If the output capacitance of a subcircuit, say a gate, is not comparable with the load capacitance (sum of input capacitances of the gates derived by that gate) then a charge sharing occurs between the capacitances resulting in that the output voltage of the gate oscillates before settling in its final value. On the other hand, the asynchronized inputs of a gate can cause the charge sharing at the output of the gate. In other words, the charge sharing creates some glitches which may cause wrong logical output. However, the charge sharing problem can be avoided by making the output capacitance and load capacitance to be comparable, and synchronizing the input signals by means of weak buffers.

If the source voltage of a p/n-transistor is not equal to Vdd/Vss, then the threshold voltage of that transistor changes depending on the source voltage since the threshold voltage is a function of the source to substrate voltage. In many circuits, some transistors are cascoded so that the source of every transistor is not connected to Vss. This causes the change of expected results especially in timing, due to the body effect. The only precaution for that problem is to increase the Vss connections, and to decrease the internal node capacitances as much as possible. Furthermore, in timing simulations, a worst case approach is essential.

The noise margin parameter is a measure of allowable noise voltage on the input of a circuit such that the output is not affected. In general the high and low noise margins are equalized by the equal low and high going transition times. Also, the selection of the logic style is important to maximize the noise margins.

In CMOS technology, there are some circuit implementation techniques called *logic styles*. These are complementary (standard) CMOS logic, pseudo NMOS logic, dynamic CMOS logic, clocked CMOS logic, CMOS domino logic, cascade voltage switch logic (CSVL), and pass transistor logic [46,53,54]. Each logic style possesses some different properties. In other words, the optimization of the cost function (speed, area, power, complexity, etc.) is different. For example, dynamic CMOS logic is the choice for fast circuits but its timing is critical. Hence, the designer must choose the best style for

his particular application. In our design, the standard CMOS logic style is used since this logic style possesses a more reliable timing, a rather easier mapping in layout, a lower power consumption, and a better noise immunity compared to the other styles. Furthermore, its area and speed performances are comparable with the other styles.

#### 4.3 VLSI Tools

At the layout step of a VLSI design, it is necessary to use some software tools in order to edit the layout of a chip which consists of thousands of transistors, and to perform its simulations. In our design, we have used the Berkeley CAD Tools of University of California and VLSI Tools of University of Washington [57,58] running under the Unix operating system on SUN workstations. For editing of layouts, we have used MAGIC which is an interactive editor that can make on-line design rule check by using information in the design rule file. Thus the designer must provide the design rules that are prescribed by the manufacturer. Unfortunately, MAGIC can not realign the symbolic layers if the design rule file is changed, so the layout must be reedited or modified according to the new design rules. MAGIC allows editing the layouts hierarchically, and extracting the circuit of the layout.

In order to perform simulation of a cell, first the circuit of the cell is extracted, and then it is further processed by some intermediate tools [57,58]. There are three simulators: SPICE, RNL, and ESIM. SPICE can be used for the timing simulations with a high accuracy. Before running SPICE, extracted circuit must be processed by EXT2SIM and SIM2SPICE tools to convert the extracted circuit to SPICE format. In addition, the model parameters of the transistors, and the timing commands should be entered into the SPICE input file. The results of SPICE simulations are either observed on the screen by using SPCVIEW and SPICE2SUMMARY tools or plotted by SPCPLOT tool. RNL is used for logic simulations with approximate timing. In order to use RNL, extracted circuit is processed by PRESIM. If RNL is used in interactive mode, the control and timing commands are entered interactively, otherwise RNL needs a control file consisting of control commands, and a time commands file consisting of input signals ordered in time. One can use GEN\_TIME and GEN\_CONTROL to generate the control and timing command files, respectively. ESIM is used for logic simulations of only combinational circuits, but it is very fast since it performs switch-level simulation. The results of simulations with RNL and ESIM are stored in ordinary files, thus user can read and analyze the results from these files.

After completing the layout editing and simulation tasks, the final layout is converted to CIF or GDS-II codes by using MAGIC. These codes are used to generate the masks of the layers for fabrication of the chip. If it is required, one can plot the masks from codes by using CIFPLOT tool, and convert the codes back to layout format by using MAGIC.

#### 5. VLSI IMPLEMENTATION

## 5.1 Implementation of the Extensible Median Filter

In the description of the algorithm of the extensible median filter, it is proposed to multiplex the I/O's of the extensible median filter chip to reduce the pin number from 40 to 28. However, in the layout implementation of the chip, it is observed that there is no increase in the area when 40 pads are used. This is due to fact that there are empty spaces between the pads when the 28 pads are placed. For this reason, we have used 40 pads in the extensible median filter chip. Since there is no multiplexing in this case, the speed of the chip is increased by about 30 percent, and the data loading and reading operations are simplified. The only disadvantage is increased package size in the case of "dip" package. In this section, the implementation of the 40 pin extensible median filter chip with no multiplexing is described. Here, let's point that one can easily add multiplexers around the network and reduce the pin number to 28.

As the first step, the floor plan of the chip is designed (Fig. 5.1). Then, the power distribution scheme of the chip is determined. A clock distribution scheme is selected such that the lengths of the paths that the clock signals propagate are equal and small enough so that the clock skew is not a serious problem. Hence, a single clock buffer is used for each clock phase, instead of a distributed clock buffering scheme [59]. The power and clock distribution scheme is shown in Fig. 5.2.

In the following subsections, logic expression(s), the circuit and layout descriptions, and the timing and/or logic simulations will be described for each unit of the chip. The complete layout and the logic simulation results of the chip will be given. Finally, an overview of the chip and its testing will be presented.

Figure 5.1: The floor plan.

Figure 5.2: The power and clock distribution scheme.

## 5.1.1 Compare-and-Swap Unit-1 (CSU1)

The logic expressions of the CSU1 are obtained from the state diagram given in Fig. 3.3. They are minimized by using the carnough-map method [60]. The resultant logic expressions and the circuit diagram of the CSU1 are given in Fig. 5.3. In this circuit, inputs enter the cell during  $\phi_1$  ( $\phi = 1$ ,  $\phi^- = 0$ ). The computation of the outputs starts as soon as the inputs are latched. When the outputs are computed, they are latched at the outputs of the inverters during  $\phi^-$ . In the circuit, the weak buffers are used to prevent the charge sharing. The inverters at the output of the circuit are necessary to latch the outputs. These inverters are dynamic latches so they can not hold data more than about 1 millisecond without refreshing [21]. This means that the clock frequency can not be less than 1 KHz.

The circuit of the CSU1 is converted to the layout by considering its geometry in the floor plan. After the equivalent circuit of the layout is extracted and simulated, the layout is modified to increase the speed, to prevent the charge sharing and to have equal rise and fall times by resizing the proper transistors. The maximum average current is about 0.7 mA. The power lines of the layout are wide enough so that the *metal migration* does not take place (the allowable maximum current density of each layer is determined by the manufacturer). The final form of the layout of the CSU1 is shown in Fig. 5.4. This layout consists of 39 p-channel and 39 n-channel transistors.

The timing simulations of the CSU1 are performed with different clock frequencies and with different rise and fall times by using SPICE. Here, we give the input and the output waveforms for 40 MHz clock which is the maximum clock frequency (Fig. 5.5). In these waveforms, the rise and fall times of the clock, inputs, and outputs are about 5 nsec. However, the rise and fall times may be larger than 5 nsec for low operation frequencies if it is desired. The ripples on the waveforms are less than 1 V, thus they are negligible. The logic simulation of the CSU1 is performed by using RNL for all possible inputs. As an example, the results of the logic simulation for three different 4-bit input words are given in Table. 5.1. For the sake of the clearness, the clocks and time steps are not shown. As a result, the timing and the logic simulations show that the CSU1 with the given layout functions correctly.

Figure 5.3: Circuit diagram of the CSU1.

Figure 5.4: Layout of the CSU1.

Figure 5.5: Timing simulation results of the CSU1.

| R                                      | $A_i$ | $B_i$            | $A_{\circ}$           | $B_o$       |

|----------------------------------------|-------|------------------|-----------------------|-------------|

| 0                                      | 0     | 0                | 0                     | 0           |

| 0                                      | 1     | 1                | 1                     | 1           |

| 0                                      | 0     | 0                | 1<br>0                | 0           |

|                                        | 1     |                  |                       |             |

| 1 0                                    | 1     | 1<br>0           | 1                     | 1<br>0      |

| 0                                      | 0     |                  | 1<br>0<br>1<br>0<br>1 | 1<br>0      |

| 0                                      | 1     | 1                | 1                     | 0           |

| 1                                      | 0     | 1                | 0                     | 1           |

| $\begin{vmatrix} 1 \\ 0 \end{vmatrix}$ | 1     | 1<br>1<br>1<br>0 | 1                     | 1<br>1<br>0 |

| 0                                      | 0     | 1                | 1                     |             |

| 0                                      | 1     |                  | 0                     | 1           |

| 1                                      | 0     | 1                | 1                     | 0           |

Table 5.1: Logic simulation results of the CSU1.

## 5.1.2 Delay Unit

Since the reset signal must propagate through the delay units one stage per cycle, a shift register cell can be used as the delay unit. The static D-type master-slave flip-flop is chosen as the delay unit in order to have a reliable shift operation [60,53]. The circuit diagram and the layout of the shift register cell are shown in Fig. 5.6 and Fig. 5.7. In this circuit, the input is latched at the output of the master flip-flop during  $\phi = 1$ . The master flip-flop is disabled when  $\phi$  is low. The input is latched at the output of the slave flip-flop during  $\phi^- = 1$ . The output of the master flip-flop is buffered and sent to the compare-and-swap stage as the complement of the reset signal. The results of the timing simulations of the cell are given in Fig. 5.8.

#### 5.1.3 Clock Buffers

The total capacitive load of  $\phi$  and  $\phi^-$  lines are about 15 pF and 20 pF respectively. Four buffers are used to drive these loads with 100 percent tolerances: two oninverting buffers for  $\phi$ , and two inverting buffers for  $\phi^-$ . The noninverting buffer can drive a 15 pF load with the 2.5 nsec rise and fall times whereas the inverting buffer can drive a 20 pF load with the 2.5 nsec rise and fall times. In order to minimize the delay of the buffers, the number of stages and their ratios are calculated [61,20]: the noninverting buffer has 4 stages with 3.6 stage ratio while the inverting buffer has the 5 stages with 2.9

( to the compare-and-swap stage)

Figure 5.6: Circuit diagram of the shift register cell.

Figure 5.7: Layout of the shift register cell.

Figure 5.8: Timing simulation results of the shift register cell.

$W_p/W_n$  16/5 46/14 135/39 392/119 1180/360  $\bar{\varrho}$  (b)

Figure 5.9: Circuit diagrams of the clock buffers.

Figure 5.10: Layouts of the clock buffers: a) noninverting, b) inverting.

stage ratio. The circuit diagrams and the transistor ratios of each stage of the buffers are given in Fig. 5.9, and their layouts are shown in Fig. 5.10. The timing simulations of the buffers with their loads are performed for 50 MHz and 20 MHz (Fig. 5.11). According to the timing simulations, the delay of each buffer is about 7.5 nsec with a clock skew about 0.5 nsec between  $\phi$  and  $\phi^-$ .

## 5.1.4 Chip Overall Layout

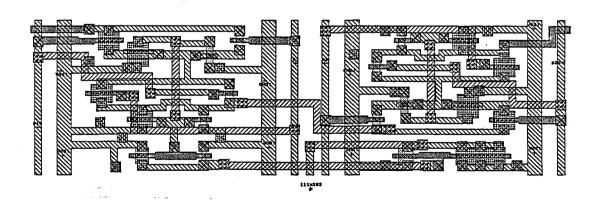

After completing the layouts and simulations of the cells (CSU1, one bit register, and clock buffers), the cells are combined hierarchically to form the overall layout of the network: the first and second stages of the network are obtained by combining five CSU1's for each. These two stages are used to form the sorter which consists of nine stages. The nine bit shift register is obtained as an array of one bit shift register cells. Finally, the clock buffers are placed at two sides of the network, and 40 pad cells are placed around the network. The pad cells are supported by the manufacturer as black box standard cells with given I/O connection schemes and parameters (size, delay, etc.). The complete layout of the chip is shown in Fig. 5.12.

The logic simulations of the chip are performed with the test vectors which will be also used for the physical testing of the chip after fabrication. The test vectors, which consists of the sorted, reverse sorted and equal set of elements, are applied to the inputs of the chip, and the generated outputs are found to be matching to the expected results. The outputs of the chip corresponding to the inputs which enter at k'th clock cycle are ready at the output pads at end of the k + 8'th clock cycle. The logic simulation results are given in Fig. 5.13 (also see Fig. 5.14 for signal labels).

# 5.1.5 An Overview of the Extensible Median Filter Chip

In this section, we will give the information about how the chip can be used. The extensible median filter chip has 40 pins: the pin configuration is shown in Fig. 5.14. The pin labels are given in Table. 5.2.

The timing diagrams of the data load and read operations for the extensible median filter chip are given in Fig. 5.15. The input data must be ready

Figure 5.11: Timing simulation results of the clock buffers: a) for 50 MHz, b) for 20 MHz.

Figure 5.12: Complete layout of the extensible median filter chip.

| LABEL    | FUNCTION                |

|----------|-------------------------|

| RI       | RESET INPUT             |

| DI1-DI10 | DATA INPUTS             |

| DO1-DO10 | DATA OUTPUTS            |

| UI1-4    | UPPER EXTENSION INPUTS  |

| UO1-4    | UPPER EXTENSION OUTPUTS |

| LI1-4    | LOWER EXTENSION INPUTS  |

| LO1-4    | LOWER EXTENSION OUTPUTS |

| CLK      | CLOCK INPUT             |

| VSS      | 0 V POWER SUPPLY        |

| VDD      | 5 V POWER SUPPLY        |

Table 5.2: Pin labels of the extensible median filter chip.

#### RI DI1-10 UI1-234 LI1-234 O1-10 UO1-234 LO1-234

```

1 0000000000 1111 0000 11111111101 1111 0111

0 0000000010 1111 0000 11111111101 0111 0111

0 0000000110 1111 0000 11111110101 1111 0011

0 0000001110 1111 0000 1111110101 1011 0011

0 0000011110 1111 0000 1111010101 1111 0001

0 0000111110 1111 0000 1111010101 1101 0001

0 0001111110 1111 0000 1101010101 1111 0000

0 0011111110 1111 0000 1101010101 1110 0000

0 0111111110 1111 0000 0000000000 1111 0000

0 1111111110 1111 0000 1000000000 1111 0000

1 0000000000 1111 0000 1100000000 1111 0000

0 1000000000 1111 0000 1110000000 1111 0000

0 1100000000 1111 0000 1111000000 1111 0000

0 1110000000 1111 0000 1111100000 1111 0000

0 1111000000 1111 0000 11111110000 1111 0000

0 1111100000 1111 0000 1111111000 1111 0000

0 1111110000 1111 0000 1111111100 1111 0000

0 1111111000 1111 0000 1111111110 1111 0000

0 1111111100 1111 0000 0000000000 1111 0000

0 1111111110 1111 0000 1000000000 1111 0000

1 0000000000 1111 0000 1100000000 1111 0000

0 0000000000 1111 0000 1110000000 1111 0000

0 1111111110 1111 0000 1111000000 1111 0000

0 1111111110 1111 0000 1111100000 1111 0000

0 0000000000 1111 0000 1111110000 1111 0000

0 1111111110 1111 0000 11111111000 1111 0000

0 0000000000 1111 0000 11111111100 1111 0000

0 0000000000 1111 0000 1111111110 1111 0000

0 1111111110 1111 0000 0000000000 1111 0000

0 1111111110 1111 0000 0000000000 1111 0000

1 0000000000 0000 0000 1111111111 0000 0000

0 000000000 0000 0000 1111111111 0000 0000

0 0000000001 1111 1111 0000000001 1111 0111

0 0000000001 1111 1111 11111111111 1111 0011

0 1111111110 0000 0000 0000000000 0000 1000

0 1111111111 1111 1111 11111111111 1111 1001

0 1111111111 1111 1111 11111111111 1111 1100

0 1111111110 0000 0000 0000000000 0000 1100

0 1111111110 0000 0000 0010001000 0000 1110

1 0000000001 1111 1111 1000100010 1111 0110

0 0000000001 1111 1111 1000100010 1111 0111

0 000000000 0000 0000 0010001000 0000 0011

0 0000000000 0000 0000 0111011101 0000 0011

0 0000000001 1111 1111 1101110111 1111 0001

0 1111111111 1111 1111 1101110111 1111 1001

0 1111111110 0000 0000 0111011101 0000 1000

0 1111111110 0000 0000 0111011101 0000 1100

0 1111111111 1111 1111 1000100010 1111 1100

0 1111111111 1111 1111 1000100010 1111 1110

```

Figure 5.13: Logic simulation results of the extensible median filter chip.

Figure 5.14: Pin configuration of the extensible median filter chip.

at the input pins while the clock is rising. Since there is an extra 7.5 nsec delay at clock signals due to delay of the clock buffers, input data signals may rise/fall while the clock is rising. But, the input signals must not change before the clock falls to logic low. The reset input signal, RI, must be at logic 1 during the last clock cycle of every word, and at logic 0 during the other clock cycles. For example, if the word length is 4-bit, then RI will be the sequence, 000100010.... At the beginning of running of the chip, the chip must be reset by entering logic 1 to RI for at least one clock cycle. The outputs are ready at the end of the clock cycle, and they do not change until the end of the next clock cycle.

#### The Normal Operation Mode

If the extensible median filter chip is used to find the medians of 9 elements, which is the normal operation mode, the input data are loaded from the first nine data inputs (DI1, DI2,..., DI9) (Table. 5.3). The upper extension inputs (UI1, UI2, UI3, and UI4) must be connected to logic 1's whereas the lower extension inputs (LI1, LI2, LI3, and LI4) and the lowest data input (DI10) must be connected to logic 0's. In this mode, the reset input signal (RI) is used such that logic 1 is entered at the end of the every word (together with

Figure 5.15: Timing diagrams for data load and read operations of the extensible median filter chip.