# A 5.2 GHz RF COMBINED POWER AMPLIFIER WITH FULLY INTEGRATED ON-CHIP IMPEDANCE MATCHING WILKINSON POWER COMBINER AND SPLITTER

# by ERCAN KAYMAKSUT

Submitted to the Graduate School of Engineering and Natural Sciences

in partial fulfillment of

the requirements for the degree of

Master of Science

Sabanci University

July, 2008

# A 5.2 GHz RF COMBINED POWER AMPLIFIER WITH FULLY INTEGRATED ON-CHIP IMPEDANCE MATCHING WILKINSON POWER COMBINER AND SPLITTER

| PPROVED BY:                                              |

|----------------------------------------------------------|

|                                                          |

| Assoc. Prof. Dr. İbrahim TEKİN (Dissertation Supervisor) |

| Asst. Prof . Dr. Ayhan Bozkurt                           |

| Assoc. Prof. Dr. Meriç Özcan                             |

| Asst. Prof. Dr. Cem Öztürk                               |

| Assoc. Prof. Dr. Erhan Budak                             |

| DATE OF APPROVAL:                                        |

# A 5.2 GHz RF COMBINED POWER AMPLIFIER WITH FULLY INTEGRATED ON-CHIP IMPEDANCE MATCHING WILKINSON POWER COMBINER AND SPLITTER

# Ercan Kaymaksüt

Electronics Engineering, Master of Science Thesis

Jury Members: Assoc. Prof. İbrahim Tekin(Thesis Advisor), Assoc. Prof. Meriç Özcan, Asst. Prof. Cem Öztürk, Asst. Prof. Ayhan Bozkurt, Assoc. Prof. Erhan Budak

Keywords: IEEE, 802.11a, WLAN, RF IC, SiGe, BiCMOS, HBT, power amplifier, Wilkinson power combiner

#### Abstract

In this thesis a 5.2 GHz combined power amplifier is designed for Wireless Local Area Network (WLAN) application. A new on-chip power combining technique by using impedance matching Wilkinson power divider circuits will be presented. Two impedance matching Wilkinson power dividers are employed for matching the input and output impedances of the amplifier to 50  $\Omega$  as well as splitting the input power into two amplifiers and combining their output powers. A 5.2 GHz fully integrated class-A mode combined power amplifier is designed in 0.35µ SiGE BiCMOS technology to asses the power combining technique for WLAN applications. The power amplifier with the on-chip lumped element impedance matching Wilkinson power divider circuits has a measured small signal gain of 5.21 dB. The output power at 1 dB compression point is measured as 22.4 dBm and the power added efficiency of 17% is achieved at 1 dB compression point. The chip area is significantly reduced by using lumped element impedance matching Wilkinson power dividers; the total die size is 1.2mm x 1.25mm, including RF and bias pads. The simulated (Cadence) and measured performance of Combined Power Amplifier are well matched. Thus the RF power amplifier and combiner/splitter circuits can be used for 5.2 GHz WLAN applications.

# EMPEDANS UYUMLU WILKINSON GÜÇ BÖLÜCÜ İLE 5.2 GHZ BİRLEŞTİRİLMİŞ GÜÇ KUVVETLENDİRİCİSİ TASARIMI

# Ercan Kaymaksüt

Elektronik Mühendisliği, Yüksek Lisans Tezi

Tez Jürisi: Doç. Dr. İbrahim Tekin (Tez danışmanı), Yrd. Doç. Dr. Ayhan Bozkurt, Doç. Dr. Meriç Özcan, Yrd. Doç. Dr. Cem Öztürk, Doç. Dr. Erhan Budak

Anahtar Kelimeler: IEEE, 802.11a, WLAN, RF IC, SiGe, BiCMOS, HBT, Güç Kuvvetlendiricisi, Wilkinson Güç Bölücü

# Özet

Bu tezde 5.2 GHz Kablosuz Yerel Ağ uygulamaları için bir birleştirilmiş güç kuvvetlendiricisi tasarlanmıştır. Empedans uyumlu Wilkinson güç kuvvetlendiricileri kullanılarak yeni bir güç birleştirme yöntemi ortaya konmuştur. İki tane empedans uyumlu Wilkinson Güç kuvvetlendiricisi kullanılarak hem kuvvetlendirici katının giriş çıkış empedansı 50 Ω'a uyumlaştırılmıştır hem de giriş gücü iki kuvvetlendiriciye bölünmüş ve iki kuvvetlendiricinin çıkış gücü toplanmıştır. Bu güç birleştirme tekniğini sınamak için 5.2 GHz de A sınıfı çalışan tamamen entegre bir güç kuvvetlendiricisi gerçeklenmiştir. Entegre edilmiş güç bölücü ve güç toplayıcı devreler ile güç kuvvetlendiricisinin kazancı 5.2 GHz de 5.21 dB olarak ölçülmüştür. 1 dB bastırma noktasında 22.4 dBm çıkış gücü ölçülmüş ve bu çıkış gücünde %17 katılmış güç verimliliği elde edilmiştir. Kırmığın toplam alanı yapılan ayrık eleman tasarımı sayesinde önemli oranda küçültülmüş ve 1.2mm x 1.25mm olarak gerçeklenmiştir. Similasyon sonuçları(Cadence) ile ölçüm sonuçları uyum içerisindedir. Tasarlanan güç kuvvetlendiricisi ve güç birleştirici/güç toplayıcı devreleri 5.2 GHz Kablosuz yerel ağ uygulamaları için uygundur.

#### **ACKNOWLEDGEMENTS**

This work was supported by Turkish Scientific and Technology Research Institution TUBITAK Grant 105E178 and in the context of the network TARGET—"Top Amplifier Research Groups in a European Team" and supported by the Information Society Technologies Program of the EU under contract IST-1-507893-NOE, http://www.target-org. In addition, I would like to thank TUBITAK for BIDEB scholarship.

First and foremost I would like to thank my thesis supervisor Assoc. Prof. Ibrahim Tekin for his guidance, support and for keeping me motivated all the time. It was a great honor for me to have the chance to work with him for two years. I certainly could not come this far without his assistance. Moreover, I appreciate his patience and encouragement during the long laboratory hours.

I also specially thank Asst. Prof. Ayhan Bozkurt and Assoc. Prof. Yaşar Gürbüz for their help in answering my questions. I would also like to thank my dissertation members, Asst. Prof. Cem Öztürk, Assoc. Prof. Erhan Budak and Assoc. Prof. Meri. Özcan for spending their invaluable time to review my thesis.

Next, I would like to thank my friends in my research group, Mehmet Kaynak and Onur Esame for their invaluable assistance throughout the preparation of my dissertation.

Last but not least, I would like to thank my family for their endless support in every step I take. With their unconditional love and moral support, I accomplished this dissertation

# **TABLE OF CONTENTS**

| 1 | INTF                       | RODUC                                         | ΓΙΟΝ                                                    | 1    |  |  |

|---|----------------------------|-----------------------------------------------|---------------------------------------------------------|------|--|--|

| 2 | POW                        | POWER AMPLIFIER BASICS                        |                                                         |      |  |  |

|   | 2.1                        | Power                                         | Amplifier Performance Parameters                        | 5    |  |  |

|   |                            | 2.1.1                                         | Output Power                                            | 6    |  |  |

|   |                            | 2.1.2                                         | Gain                                                    | 6    |  |  |

|   |                            | 2.1.3                                         | Linearity                                               | 7    |  |  |

|   |                            | 2.1.4                                         | Efficiency                                              | 11   |  |  |

|   |                            | 2.1.5                                         | Error Vector Magnetude                                  | 11   |  |  |

|   | 2.2                        | Power                                         | Amplifier Classes                                       | 13   |  |  |

|   |                            | 2.2.1                                         | Class A                                                 | 14   |  |  |

|   |                            | 2.2.2                                         | Class B.                                                | 17   |  |  |

|   |                            | 2.2.3                                         | Class AB                                                | 20   |  |  |

|   |                            | 2.2.4                                         | Class C                                                 | 21   |  |  |

|   |                            | 2.2.5                                         | Class D                                                 | 23   |  |  |

|   |                            | 2.2.6                                         | Class E                                                 | 24   |  |  |

| 3 | POW                        | POWER AMPLIFIER DESIGN FUNDAMENTALS           |                                                         |      |  |  |

|   | 3.1                        | Device Selection 2:                           |                                                         |      |  |  |

|   | 3.2                        | Plotting the I-V Characteristics              |                                                         |      |  |  |

|   | 3.3                        | Load Pull Technique                           |                                                         |      |  |  |

|   | 3.4                        | Input and Output Matching Circuit Design      |                                                         |      |  |  |

| 4 | POWER COMBINING TECHNIQUES |                                               |                                                         |      |  |  |

|   | 4.1                        | Distributed Amplifier Design                  |                                                         |      |  |  |

|   | 4.2                        | Transformer Based Power Combining Techniques  |                                                         |      |  |  |

|   | 4.3                        | Spatial Power Combining Techniques            |                                                         |      |  |  |

|   | 4.4                        | Wilkinson Power Divider Based Power Combining |                                                         |      |  |  |

|   |                            | 4.4.1                                         | Proposed Power Combining Technique by Using Impedance   | e    |  |  |

|   |                            | Match                                         | ing Wilkinson Power Dividers                            | 42   |  |  |

|   |                            | 4.4.2                                         | Impedance Matching Wilkinson Power Divider Design       | 43   |  |  |

|   |                            | 4.2.3                                         | Experimental Results for Impedance Matching Wilkinson I | ower |  |  |

|   |                            | Divide                                        | ers                                                     | 50   |  |  |

| 5    | COMBINED | POWER AMPLIFIER DESIGN                            | 5 <del>6</del> |

|------|----------|---------------------------------------------------|----------------|

|      | 5.1      | Comparison with Singe Stage Power Amplifier       | 59             |

|      | 5.2      | Experimental Results For Combined Power Amplifier | 63             |

| 6    | CONCLUSI | ONS AND FUTURE WORK                               | 67             |

| REFE | ERENCES  |                                                   | 69             |

# LIST OF FIGURES

| Figure 2.1: Schematic view of a single stage RF power Amplifier                     | 5  |

|-------------------------------------------------------------------------------------|----|

| Figure 2.2: 1 dB compression point characteristics                                  | 8  |

| Figure 2.3: Output Power spectrum for a PA with intermodulation products            | 9  |

| Figure 2.4: Graphical explanations of the intercept points                          | 10 |

| Figure 2.5: Non-distorted 16-QAM input signal and the same signal after a nonlinear | .r |

| distortiondistortion                                                                | 12 |

| Figure 2.6: Error vector is shown in IQ plot for a digitally modulated signal       | 13 |

| Figure 2.7: Topology for linear Power Amplifiers                                    | 14 |

| Figure 2.8: Class A power amplifier Bias Point and input/output swings              | 15 |

| Figure 2.9: Collector Voltage swing versus efficiency and Output power for Class A  |    |

| PA                                                                                  | 17 |

| Figure 2.10: Class B power amplifier Bias Point and input/output swings             | 18 |

| Figure 2.11: Push-Pull Amplifier Topology                                           | 19 |

| Figure 2.12: AB power amplifier Bias Point and input/output swings                  | 21 |

| Figure 2.13: Class C power amplifier Bias Point and input/output swings             | 22 |

| Figure 2.14: Approximate output power and efficiency curves with respect to         |    |

| conduction angle                                                                    | 23 |

| Figure 2.15: Class D power amplifier topology                                       | 24 |

| Figure 2.16: Class E power amplifier topology                                       | 25 |

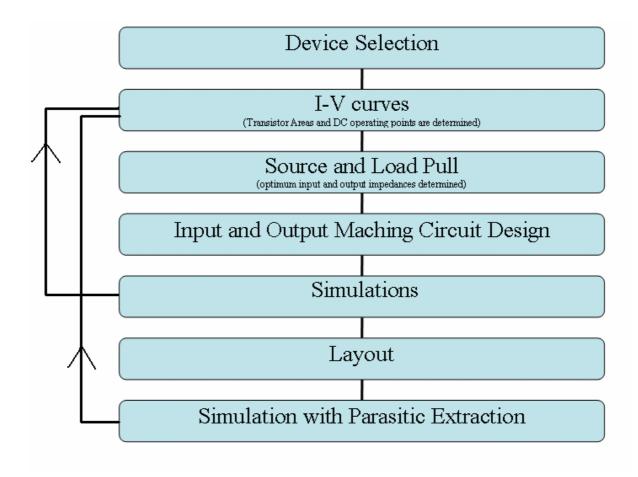

| Figure 3.1: Power Amplifier Design Road Map                                         | 27 |

| Figure 3.2: Schematic View of the test setup for I-V curve simulations              | 28 |

| Figure 3.3: Load Lines for a power amplifier on the IV curve                        | 28 |

| Figure 3.4: Output Power-Input Power curves for power matched and gain matched      |    |

| cases                                                                               | 30 |

| Figure 3.5: Optimum Load impedance shown on the IV curves                           | 31 |

| Figure 3.6: Power Contours for different Load impedances                             | 31   |

|--------------------------------------------------------------------------------------|------|

| Figure 3.7: An amplifier schematic showing $Z_{in}$ , $Z_{out}$ , $Z_L$ and $Z_S$    | .32  |

| Figure 3.8: Schematic view of L-type matching networks                               | .32  |

| Figure 4.1: Schematic view of Distributed Amplifier Topology                         | 36   |

| Figure 4.2: Transformer Based power combining topology depicted from [13]            | .37  |

| Figure 4.3: General Representation of Spatial Power Combining Technique              | 38   |

| Figure 4.4: A transmission line two-way Wilkinson power combiner                     | 39   |

| Figure 4.5: Wilkinson Power Divider in symmetric form                                | 39   |

| Figure 4.6: Even Mode half circuit representation for the Wilkinson Power Divider    | 40   |

| Figure 4.7: Mode half circuit representation for the Wilkinson Power Divider         | 41   |

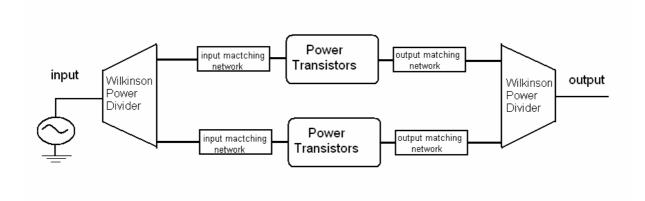

| Figure 4.8: Representation of Wilkinson Power Divider with port 1 excitation         | 42   |

| Figure 4.9: Conventional Power combining schematic by Using Wilkinson power          |      |

| dividers                                                                             | 43   |

| Figure 4.10: Proposed Power Combining Technique using Impedance Matching             |      |

| Wilkinson Power Dividers                                                             | 44   |

| Figure 4.11: $\pi$ -network lumped equivalent two-way Wilkinson power divider        | 45   |

| Figure 4.12: Insertion loss for $\pi$ -type and L-type matching networks for various |      |

| quality factors                                                                      | 46   |

| Figure 4.13: Phase difference for L-type matching network for various quality factor |      |

| inductors                                                                            | 47   |

| Figure 4.14: L-network lumped element impedance matching Wilkinson power divide      | er   |

| circuit                                                                              | 47   |

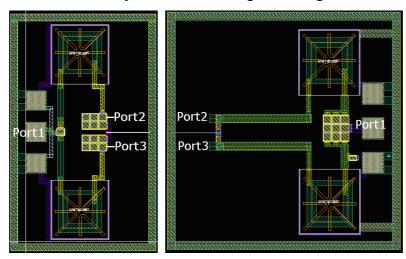

| Figure 4.15: Layout of impedance matching Wilkinson power dividers used as           | a)   |

| Splitter b) Combiner.                                                                | 48   |

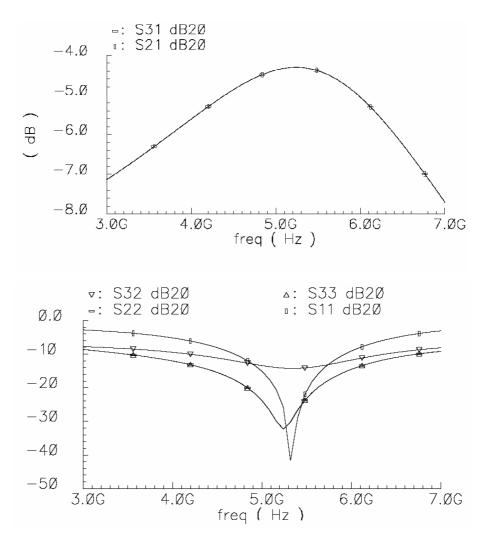

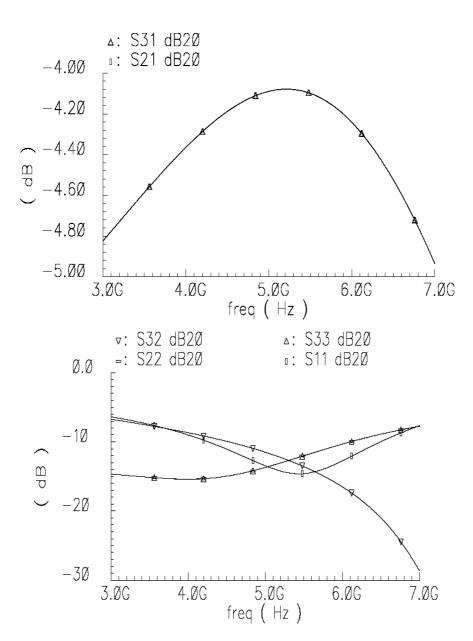

| Figure 4.16: S-Parameter Simulation Results for impedance matching Wilkinson         |      |

| power dividers used as Splitter                                                      | 49   |

| Figure 4.17: S-Parameter Simulation Results of impedance matching Wilkinson          |      |

| power dividers used as Combiner                                                      | 50   |

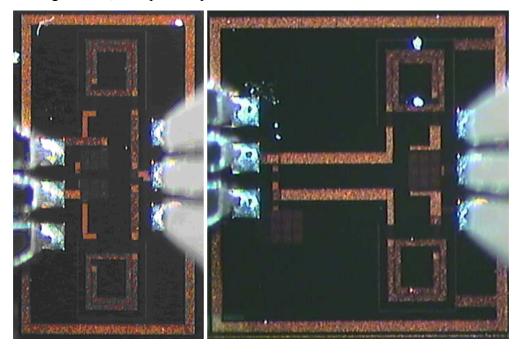

| Figure 4.18: Microphotograph. of a) Splitter b) Combiner                             | 51   |

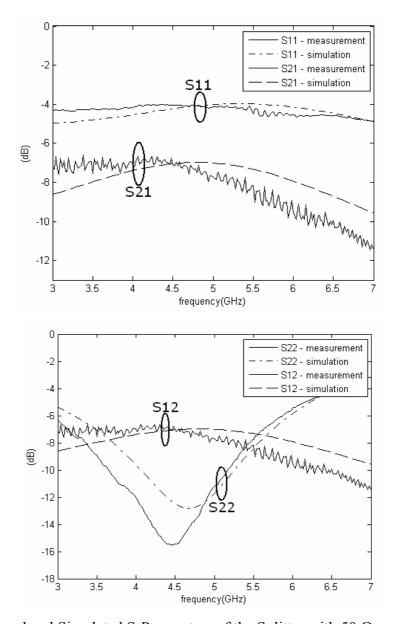

| Figure 4.19: Measured and Simulated S-Parameters of the Splitter with 50 $\Omega$    |      |

| measurement setup                                                                    | . 52 |

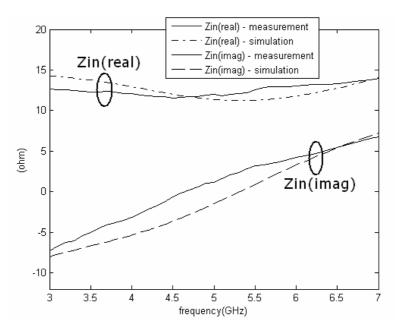

| Figure 4.20: Measured input impedance seen from Port3 of splitter                    | . 53 |

| Figure 4.21: Measured and Simulated S-Parameter Results of Combiner with $50\Omega$  |      |

| measurement setup                                                                    | 54   |

| Figure 4.22: Measured input impedance seen from Port3 of combiner                | . 55 |

|----------------------------------------------------------------------------------|------|

| Figure 4.23: Measured loss of Splitter                                           | . 56 |

| Figure 4.24: Measured loss of Combiner                                           | . 56 |

| Figure 5.1: Schematic view of the combined power amplifier                       | . 58 |

| Figure 5.2: Microphotograph of the fabricated PA with on-chip combining circuits | . 59 |

| Figure 5.3: Schematic view of Single PA                                          | . 60 |

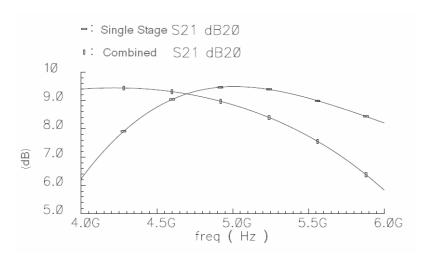

| Figure 5.4: S21 simulation results for Single PA and Combined PA                 | . 60 |

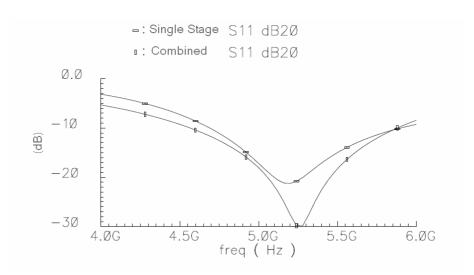

| Figure 5.5: S11 simulation results for Single PA and Combined PA                 | . 61 |

| Figure 5.6: S22 simulation results for Single PA and Combined PA                 | . 61 |

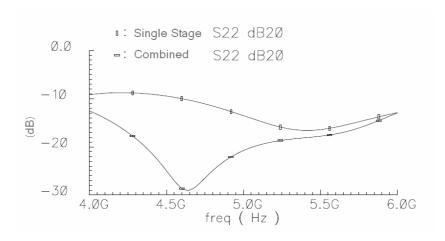

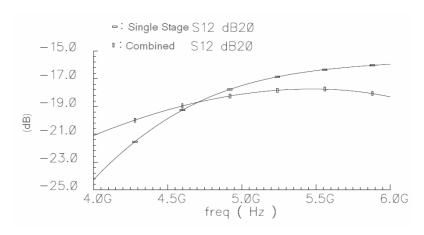

| Figure 5.7: S12 simulation results for Single PA and Combined PA                 | . 62 |

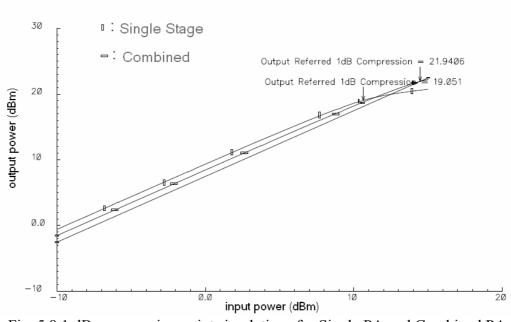

| Figure 5.8: 1 dB compression point simulations for Single PA and Combined PA     | . 62 |

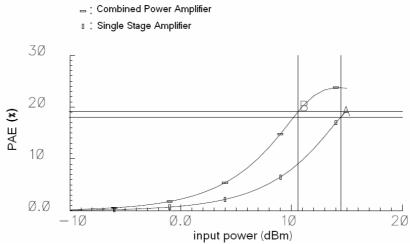

| Figure 5.9: PAE simulation results for Single PA and Combined PA                 | . 63 |

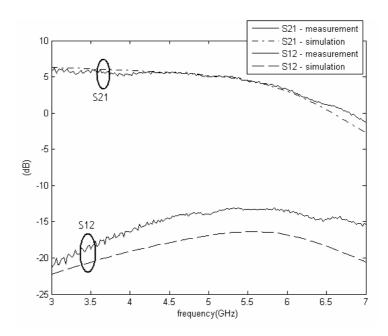

| Figure 5.10: Measured and Simulated S21, S12 (dB) of combined PA                 | . 64 |

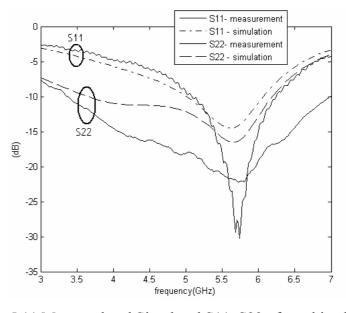

| Figure 5.11: Measured and Simulated S11, S22 of combined PA                      | . 64 |

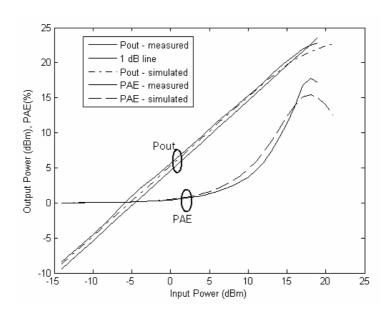

| Figure 5.12: 1 dB compression point and PAE of combined PA                       | . 66 |

# Chapter 1

#### 1. Introduction

Wireless Local Area Networks (WLAN) connects two or more computers without using wire. This gives the users the mobility to move around within the coverage of the network. WLAN applications generally use the 83.5 MHz bandwidth in the 2.4 GHz band. The WLAN gains popularity mostly because of replacing personal computers with portable laptops. WLAN attracts home users with its ease of installation and location freedom. The growing interest in the WLAN market motivated for the new technologies that can enable higher data rates and capacity. Therefore the IEEE 802.11a WLAN standards have associated 5 GHz band for WLAN applications. The 200 MHz bandwidth available in the 5 GHz band enables high data rate, increased system capacity and low interference [1]. WLAN utilizes orthogonal time division multiplexing modulation scheme in order to achieve high data rates. The IEEE 802.11g standards offers 5 to 10 times more data rates at 5 GHz band than the conventional IEEE 802.11b systems [2].

The output power of the devices has an important effect on the coverage of the wireless network. Standards arranges the maximum allowable output power for each frequency band. Each of the standards requires a power amplifier for the final amplification.

Traditionally, III-V heterojunction bipolar technologies (HBT) such as Ga-As is preferred for high power applications at high frequencies. Integrating the power amplifier is the most challenging part in the single chip transceiver design. However, SiGe BiCMOS technology

has a unique opportunity in the wireless marketplace because it can provide the performance of III-V HBTs and the cost benefits of silicon bipolar technology. Therefore a higher level integration can be accomplished by using CMOS for digital processor and HBT's in the high frequency design[3]. Silicon Germanium (SiGe) HBTs have proven themselves as cheaper, viable replacements for GaAs in many different applications.

This thesis describes the design of a fully integrated SiGe BiCMOS combined power amplifier. We address the design of a 5 GHz PA for WLAN 802.11a applications. SiGe devices capable of 5 GHz operation have a low collector-emitter breakdown voltage. Therefore low load impedance is needed to achieve high output power. Matching a few ohms to 50  $\Omega$  results in very high losses due to low resistivity silicon substrate. Therefore, the solution could be to use power combining techniques. To overcome this restriction various power combining techniques have been developed over years. These different power combining techniques are summarized and discussed in [8]. In recent works distributed amplifier topology [9-11] are used to combine multiple amplifiers output power. However this technique is used for achieving high gain bandwidth product. Therefore this topology is not suitable for high power applications. On the other hand, transformer based power combining techniques [12-15] are the most common on-chip method for achieving high powers. Main drawback of this power combining technique is the large size and high insertion loss of the on-chip transformers. Another high combining efficiency power combining technique is spatial combining technique [16], [17]. But integrating spatial combiners is very challenging because of the size limitations of the antennas. For circuit level combining, Wilkinson power divider based power combining techniques are widely used in the industry. This technique can also be applied to chip level combining [19]. In this thesis two integrated Wilkinson power dividers are used to combine output powers of the two amplifiers. The power combining techniques are discussed in detail in chapter 4.

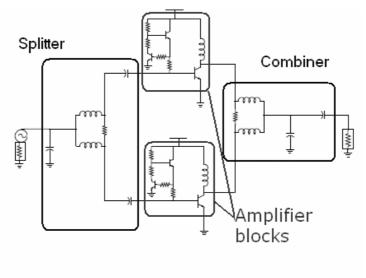

In this thesis, impedance matching Wilkinson power dividers are used to combine two amplifier blocks so that higher output power is obtained. In addition, impedance matching Wilkinson power dividers accomplishes the matching duty so that no additional impedance matching is needed. The power combining technique increases the linearity of the power amplifier therefore higher output power can be obtained with respect to single amplifier for a given technology.

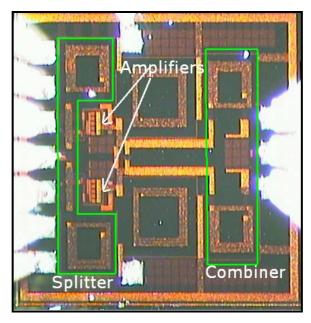

Two impedance matching Wilkinson power dividers are employed for matching the input and output impedances of the amplifier to 50  $\Omega$  as well as splitting the input power into two amplifiers and combining their output powers. A 5.2 GHz fully integrated class-A mode combined power amplifier is designed in 0.35µ SiGE BiCMOS technology to asses the power combining technique for WLAN applications. The impedance matching Wilkinson power dividers and power amplifier are designed and simulated by using Cadence and Advanced System Design (ADS). The impedance matching Wilkinson power dividers and PA are fabricated and measured separately in order to classify their performance individually. Two fabricated IMWPD circuits (splitter and combiner) have insertion losses better than 1.4dB, and return losses less than -13dB and port-to-port isolation > 12 dB at 5.2GHz. The power amplifier with the on-chip lumped element impedance matching Wilkinson power divider circuits has a measured small signal gain of 5.21 dB. The output power at 1 dB compression point is measured as 22.4 dBm and the power added efficiency of 17% is achieved at 1 dB compression point. The chip area is significantly reduced by using lumped element impedance matching Wilkinson power dividers; the total die size is 1.2mm x 1.25mm, including RF and bias pads. The simulated (Cadence) and measured performance of Combined Power Amplifier are well matched. Thus the RF power amplifier and combiner/splitter circuits can be used for 5.2 GHz WLAN applications.

The material in this thesis is organized as follows:

Chapter 2 contains basic information about power amplifiers. Design parameters for power amplifier is described in this chapter. In addition power amplifier classes and different power amplifier topologies are discussed in this chapter.

In Chapter 3, basic design procedure of a 5 GHz Class A single stage power amplifier is given in detail. The device I-V characteristics, load pull simulations and input/output matching network design are all presented as part of the PA design roadmap.

In Chapter 4, some common power combining techniques will be described and the proposed power combining technique will be presented. The theoretical background of the impedance matching Wilkinson power dividers are supported with simulation and measurement results of the two manufactured impedance matching Wilkinson power dividers in  $0.35\mu$  AMS SiGe HBT technology.

In Chapter 5, the simulation and measurement results for the overall combined power amplifier will be given.

And finally in Chapter 6, the thesis will be concluded with comments on the performance of both impedance matching Wilkinson power divider and the overall power amplifier.

# Chapter 2

# 2. Power Amplifier Basics

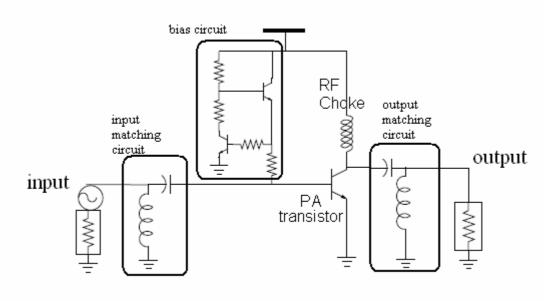

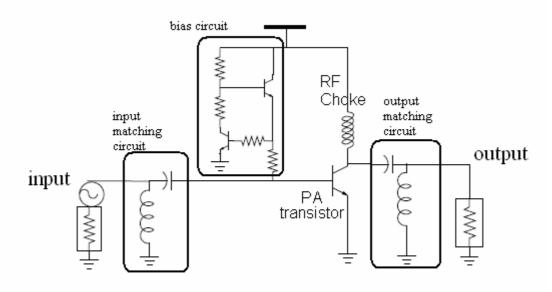

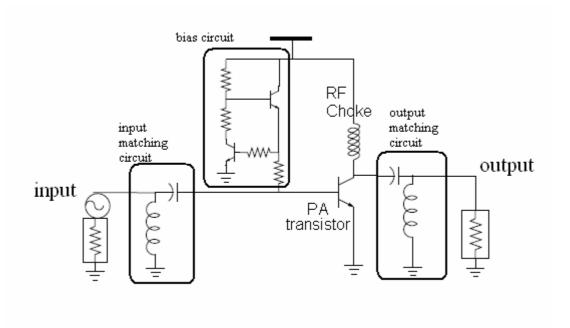

Power amplifiers (PA) are being used in many diverse applications. Power amplifiers are the last stage of the transmitter chain where highest RF power is generated and highest DC power is consumed. A schematic of a basic RF power amplifier is given in Fig. 2.1. Schematic of the RF power amplifiers is very similar to an ordinary RF amplifier. The PA consists of RF choke and DC bias circuits for biasing the RF transistor and input/output matching circuits are used for matching the optimum source and load impedances to  $50\Omega$  as in all RF devices.

Fig. 2-1 Schematic view of a single stage RF power Amplifier

The main difference of the power amplifiers with respect to the small signal amplifiers are mainly the output matching circuit. In power amplifier designs, the output matching circuit is configured such that the maximum voltage and current swing occurs in the load of the transistor. The requirements of PA vary depending on application. For characterizing the power amplifiers, some criteria are developed. In this chapter firstly some of the major figures of merit of Power Amplifiers will be explained, then power amplifier classes will be mentioned.

### 2.1 Power Amplifier Performance Parameters

# 2.1.1 Output Power

The output power of a power amplifier is the main design parameter for a power amplifier. The power level needed to be delivered to the transmitted antenna is defined by the communication standards of the system. The combined PA is designed for 5.2 GHz WLAN applications and the maximum allowed effective radiated power for this system is 200 mW (23 dBm). The effective radiated power is the multiplication of driven power to the antenna and antenna gain. Therefore 21 dBm maximum output power is needed assuming the antenna gain is 2 dBi (antenna is approximately omni directional)

#### 2.1.2 Gain

An amplifier's gain can be described as voltage gain, current gain, or power gain. The gain of power amplifiers are generally described in power gain. The small signal power gain can be described by three definitions; transducer gain  $(G_T)$ , operating gain  $(G_P)$ , available gain  $(G_a)$ . Transducer gain is defined by:

$$G_{T} = \frac{Power\_Delivered\_to\_the\_Load}{Power\_Available\_From\_Source}$$

(2.1)

In this power definition the reflection losses at the input and output ports are taken into account. The transducer gain is the most widely used gain definition for power amplifiers. The gain of the amplifier is constant in the low power region. Amplifiers generally operate linearly in this region. The transducer gain of an amplifier can be given as by using scattering parameters as:

$$G_{T}[dB] = 10 \log |S_{21}|^{2}$$

(2.2)

In the operating power gain definition, only the reflections at the output are taken into account. So the power input to the amplifier is considered instead of power available from source. The operating power gain is defined as:

$$G_{P} = \frac{Power\_Delivered\_to\_the\_Load}{Power\_input\_to\_the\_Amplifier}$$

(2.3)

The available power gain considers the reflections at the input so the input power defines as the power available from the source but the reflections at the output is not considered. The available gain is defined as:

$$G_a = \frac{Power\_Available\_From\_the\_Amplifier}{Power\_Available\_From\_Source}$$

(2.4)

According to the power definitions given above we can conclude that  $G_P \ge G_T$  and  $G_a \ge G_{T.}$ In the conjugate matched condition the gain of the amplifier should be the same according to all three gain definitions.( $G_T = G_P = G_a$ )

The gain of the amplifiers starts to drop in the high power region. The saturated gain is the power gain when the maximum output power is obtained from the amplifier. The saturated gain can be defined as:

$$G [dB] = P_{out}(sat)[dB] - P_{in}(sat)[dB]$$

(2.5)

The required gain of the power amplifiers varies from application to application but generally by using high gain amplifiers the number of amplifier stages can be reduced which gives an important cost reduction. In addition to high gain, generally the gain of the amplifier is required to be flat over the operating frequency band.

# 2.1.3 Linearity

In the linear region of an amplifier, gain is constant for a given frequency. As the input power is increased, the gain of the amplifier starts to drop. Linearity is a measure of how much linear power can be delivered to the load. Linearity is the most important criteria for power amplifiers for WLAN applications because of the higher order modulation shames used in this system. There are two important parameters that can be measured for evaluating the linearity performance of the amplifier: 1 dB compression point and third order intercept point.

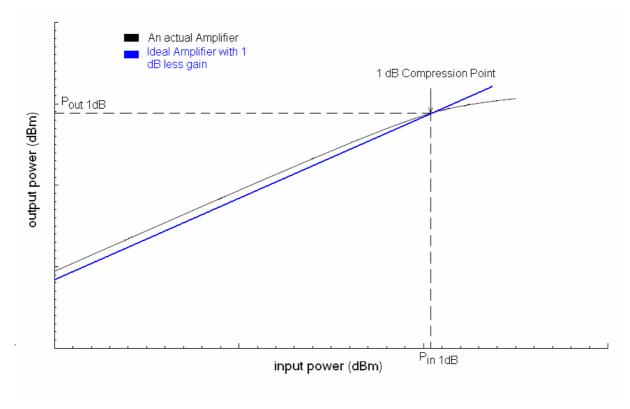

### a) 1 dB compression point

1dB compression point is defined as the power level for which the gain of the amplifier drops down 1 dB with respect to the linear gain for a specific frequency. 1 dB compression point can be expressed as input or output referred. This power level can be interpreted as the end of the linear operation. The 1 dB compression point for an amplifier is given in Fig. 2.2. 1dB compression point can be found by intersecting the actual gain and (small signal gain-1 dB) curves.

Fig. 2.2 1 dB compression point characteristics

# b) N<sup>th</sup> order intercept point

In the high power region, an amplifier introduces distortions into the output signal. For a BJT amplifier the relationship between collector current and base emitter voltage can be given as in (2.6) where  $K_1$  is the Tranconductance of the amplifier and  $K_2$ ,  $K_3$  ... are the square ,cubic, etc. nonlinearity coefficients.

$$I_C = K_1 v_{BE} + K_2 v_{BE} + K_3 v_{BE} + \dots (2.6)$$

Assuming an input signal consisting of two very close tones  $\omega_1$  and  $\omega_2$  both in amplitudes of  $A_1$ , Base- Emitter voltage  $v_{BE}$  can be written as,

$$v_{RE} = A_1 \cos(w_1 t) + A_1 \cos(w_2 t) \tag{2.7}$$

Where

$$w_1 - w_2 << w_1, w_2 \tag{2.8}$$

These input signals create outputs with intermodulation products at the frequencies:

$$w_{out} = nw_1 \mp mw_2 \tag{2.9}$$

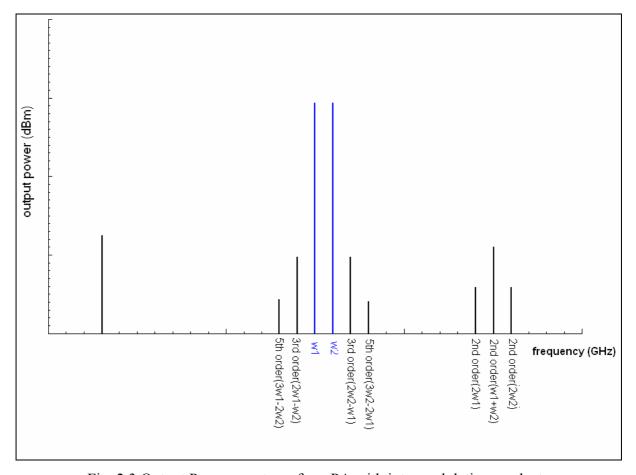

Fig. 2.3 Output Power spectrum for a PA with intermodulation products

The orders of intermodulation products are given as (n+m). The power of these intermodulation products can be given as,

$$P_{IMP} = (K_{IMP} P_{in})^{(n+m)}$$

(2.10)

Where  $K_{\text{IMP}}$  is the coefficient for that intermodulation product.

The output frequency spectrum of an amplifier with intermodulation products is given in Fig. 2.3.

The third order intermodulation products (at frequencies 2w1-w2 and 2w2-w1) are typically the most critical ones because they are the closest products to the fundamental and it is hard to filter them out from the pass band. (see Fig.2.3). The power of the third order intermodulation products has a cubic relationship given in (2.10) so as the power increases the intermodulation products increases more rapidly than the fundamental products.

In the dB scale, power of third order intermodulation products increase by 3dB when the fundamental tones increase by only 1dB.

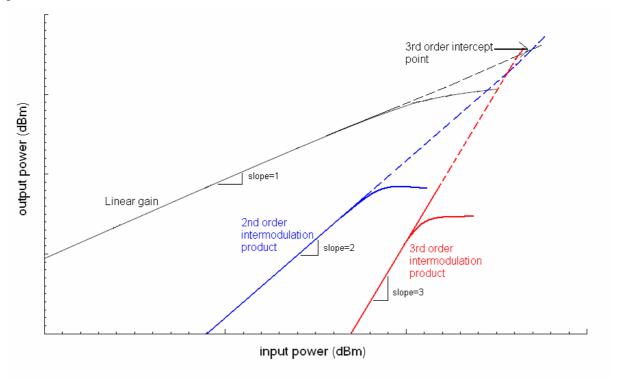

Minor harmonic distortion occurs when power amplifiers are operating with small input power, in the linear region. However with the increase of the input power nonlinearities and intermodulation products start to be visible on the output as nonlinear effects increase. The 3<sup>rd</sup> order intercept point, IP3, is defined by the crossing of the fundamental frequency and the 3<sup>rd</sup> order intermodulation curve. As the transistors saturate at the higher power region, (2.10) is not valid beyond some power range. The 3<sup>rd</sup> order intercept point can be found by extrapolating the fundamental frequency term and 3<sup>rd</sup> order intermodulation term as given in Fig.2.4. The other order intercept points are defined the same way as the 3<sup>rd</sup> order intercept point.

Fig. 2.4 Graphical explanations of the intercept points

It can be seen in Fig.2.4 that 3<sup>rd</sup> order intercept point can be determined geometrically from the output power spectrum for any given power level when the intermodulation terms are presented.

The output referred 3<sup>rd</sup> order intercept point OIP3 can be given as,

$$OIP3[dBm] = P(f1) + \frac{P(f1) - P(IMP)}{2}$$

(2.10)

# 2.1.4 Efficiency

The efficiency is very important figure of merit for a power amplifier. Power amplifiers are generally the most power consuming block of the transmitter. For this reason the overall efficiency of the transmitter is pretty much determined by the efficiency of the power amplifier. There are two commonly used definitions available for this key parameter of the power amplifier: drain efficiency, power added efficiency.

# a) Drain efficiency

Drain efficiency is the ratio of the output power to the DC power consumption:

$$Eff_{drain} = \frac{P_{RFout}}{P_{DC}}$$

(2.11)

Drain efficiency is a measure of how much of the DC power is converted to RF power. This efficiency definition does not take into account the input RF power.

# b) 2.4.2 Power Added Efficiency

Power added efficiency takes into account the input RF power to drive the amplifier. The power added efficiency is defined as the ratio of the RF power added by the amplifier to the DC power consumption:

$$PAE = \frac{P_{RFout} - P_{RFin}}{P_{DC}}$$

(2.12)

The power added efficiency is less than the drain efficiency for finite gain amplifiers. The difference between these two efficiency definitions extends as the gain of the amplifier increases.

# 2.1.5 Error Vector Magnitude (EVM)

The nonlinearities in power amplifiers cause also degradation in the digitally modulated systems. The digital data transferred onto and RF carrier by changing the RF carrier's amplitude and phase by the help of modulators. The carrier occupies a point in I versus Q plane and can be treated as a vector starting from the origin. The nonlinearities introduced by the PA can produce distortion in of phase and amplitude, which results in a distorted constellation diagram, as shown in Fig. 2.5.

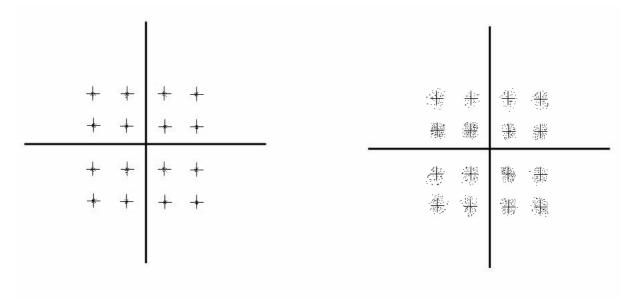

Figure 2.5 Non-distorted 16-QAM input signal (left) and the same signal after a nonlinear distortion (right).

Error vector magnitude (EVM) is a measure of degradation of the digitally modulated signals. The EVM is a direct function of Bit Error Rate which is an important measure in digital communication systems [4]

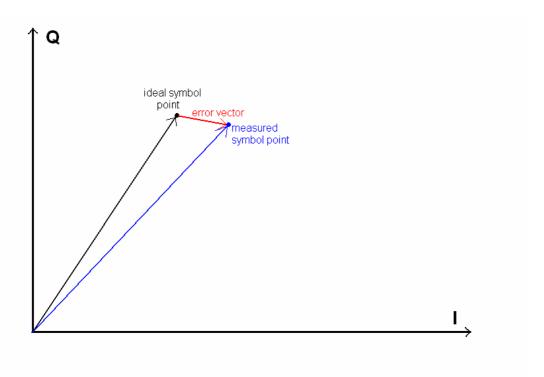

Assuming that the ideal signal is known, it is possible to calculate the error between the distorted signal and the ideal signal. The modulation schemes decide the ideal transmitted signal. EVM is defined by the scalar distance between two signal vector end points as shown in Fig. 2.6. It is common that EVM is reported as a percentage of the peak signal level.

Fig. 2.6 Error vector is shown in IQ plot for a digitally modulated signal

# 2.2 Power Amplifier Classes

Efficiency is very important parameter in a power amplifier design, therefore many different power amplifier topologies are developed for improving efficiency. Power Amplifiers can be categorized by their operating mode into two groups as linear power amplifiers and non-linear (switching-mode) power amplifiers. The class of the amplifier is determined by the topology, bias condition for the active device and the driving input signal. Class A, AB, B and C can be classified in linear mode power amplifiers as the output signal is a linear multiplication of the input signal for all or some portion of the input signal. For the linear power amplifiers efficiency drops drastically as the amplified fraction of the input signal increases.

Class D, E and F are some of the non-linear power amplifiers. The active device works as a switch for these topologies. The efficiency improves in these non-linear classes but the output signal is no longer a linear function of the input signal level. Therefore switching mode power amplifiers are not suitable for amplitude modulated signals.

Brief background information about different classes of PA's will be presented in the next subsections. However, Class A will be emphasized more than other classes.

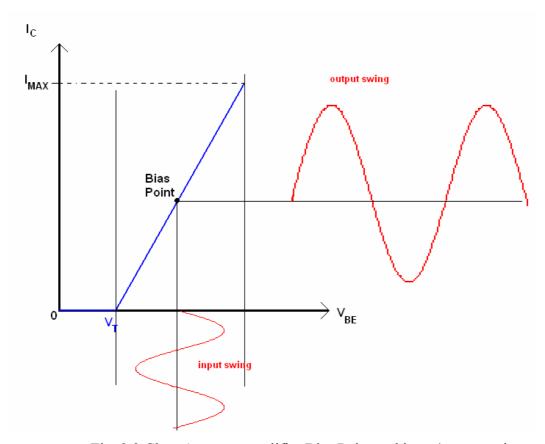

#### 2.2.1. Class A

The linear amplifiers are classified by their bias conditions. Every small signal amplifier is biased in the middle of its active region, and it stays in the active region for the complete period of the input signal. The conduction angle is defined as the angle of the input signal oven which the transistor stays in the active region-"conducts". Class A amplifiers are used to amplify with high linearity which means minimum distortion. So the class A amplifiers are biased as small signal amplifiers. Class A amplifier can be defined as the transistor is always biased on. The conduction angle for a Class A amplifier is 360°. Commonly Class A power amplifiers are built by using the general topology for linear power amplifiers given in Fig.2.7. This topology is called inductively loaded class A power amplifier as RF choke is used for achieving two times more voltage swing as the resistor loaded case.

Fig. 2.7 Topology for linear Power Amplifiers

Assuming the input signal is sinusoidal (this assumption is valid for most of the modern communication systems), we can write the total amplifier current as:

$$I_C = I_O + I_{Peak} \cos wt \tag{2.13}$$

Where I<sub>O</sub> is the bias current and I<sub>Peak</sub> is the peak value of AC current.

The total current swing should be less than the maximum allowed current for the transistor:

$$I_O + I_{Peak} \le I_{MAX} \tag{2.14}$$

The maximum allowed current for a given transistor is generally based on thermal considerations for a BJT transistor. For the FET case in addition to thermal conditions saturation condition is also considered [5].

As the device designed to be always biased on in the class A topology:

$$I_{Peak} \le I_O \tag{2.15}$$

For Class A, choosing  $I_Q = I_{MAX}/2$  gives the maximum RF current swing where

$$I_{Peak} = I_{MAX} / 2$$

(2.16)

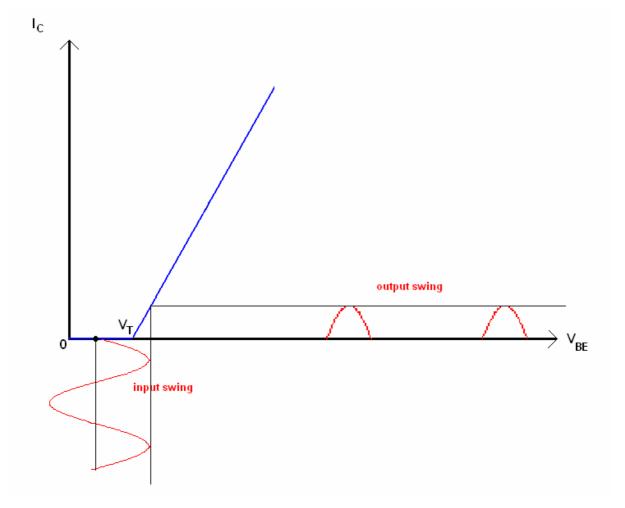

Fig. 2.8 Class A power amplifier Bias Point and input/output swings

The bias point for the class A condition is given in Fig 2.8 with corresponding input voltage swing and output current swing.

The peak Voltage can be represented by the multiplication of peak current and load resistor and for the inductively loaded class A PA peak voltage can be represented as:

$$V_{Peak} = I_{Peak} R_L \le V_{CC} - V_{SAT}$$

(2.17)

The DC power consumption can be calculated as:

$$P_{DC} = I_{O}V_{CC}$$

(2.18)

Then the output RF power is:

$$P_{RF} = \frac{I_{Peak}^{2} R_{L}}{2}$$

(2.19)

Therefore the efficiency can be calculated as:

$$\eta = \frac{I_{Peak}^{2} R_{L}}{2I_{O} V_{CC}}$$

(2.20)

The efficiency expression given in (2.20) stated that as the drive increases the efficiency also increases with the square of the output current or voltage swing. The maximum efficiency occurs when the current and voltage swings take on their maximum values. ( $I_{Peak}=I_Q$ ,  $V_{Peak}=V_{CC}-V_{SAT}$ ). This condition can be satisfied by choosing a proper load impedance.

$$P_{RFMAX} = \frac{I_{Q}(V_{CC} - V_{SAT})}{2}$$

(2.21)

$$\eta_{MAX} = \frac{V_{CC} - V_{SAT}}{2V_{CC}}$$

(2.22)

Therefore the maximum efficiency from a class-A amplifier cannot exceed 50% This efficiency is a theoretic value assuming  $V_{SAT}=0$ .

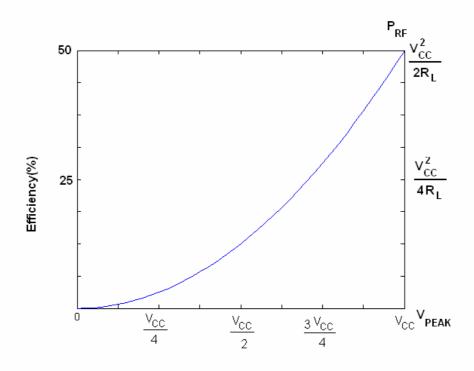

The collector voltage swing versus efficiency is plotted in Fig 2.9. The efficiency for a class A amplifier drops rapidly as the output voltage swing decreases. When the amplitude modulated signals are applied to the power amplifier, the overall efficiency will drop drastically as the overall output power decreases.

Fig. 2.9 Collector Voltage swing versus efficiency and Output power for Class A PA

# **2.2.2 Class B**

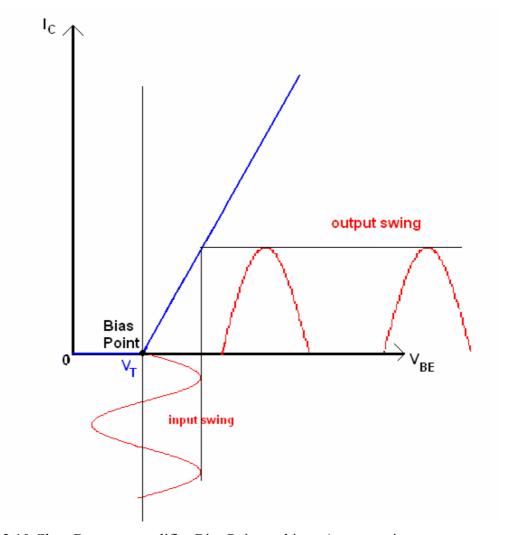

Class B is another linear amplifier class. Therefore the output voltage amplitude is a constant multiplication of the input voltage amplitude. The difference between Class A and Class B amplifiers are the conduction angle. The conduction angle of a Class B amplifier remains  $180^{\circ}$ , independent of the input drive level. The conduction angle of class B amplifier is given schematically in Fig. 2.10. In Fig. 2.10 the transfer function of the transistor is given with tranconductance G and threshold voltage  $V_T$ .

Fig. 2.10 Class B power amplifier Bias Point and input/output swings

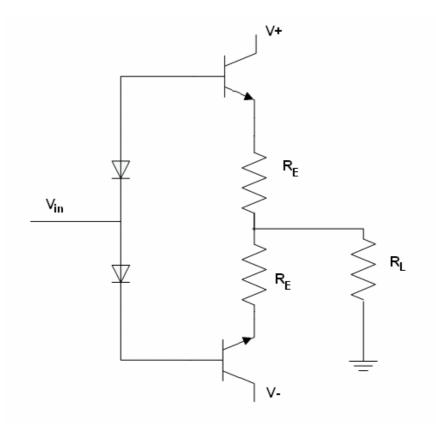

Class B power amplifiers are commonly realized by using push-pull topology given in Fig.2.11. In this topology two transistors are used and each of them biased at the threshold points. Therefore each of them conducts only half of the period. The output is the combination of two class B amplifiers so full sinusoidal waveform can be obtained [6].

Fig. 2.11 Push-Pull Amplifier Topology

When the applied voltage Vin exceeds the threshold voltage, the output voltage can be calculated as Io=G(Vin-Vt) for the given basic transfer fuction. And the current is zero when the input voltage falls below the threshold. To satisfy the 180° conduction angle, the bias voltage should be choosen exactly as the threshold voltage. The output current is simply half wave sinusoids given in Fig. 2.10. This time domain output can be expanded as Fourier series

$$I_0(t) = \frac{I_P}{\pi} + \frac{I_P}{2}\cos wt + \frac{2I_P}{3\pi}\cos w2t - \frac{2I_P}{15\pi}\cos w4t...$$

(2.23)

Low Pass or bandpass filters can be used to eliminate the higher order harmonics [6]. Therefore output would be full sinusoid with zero DC offset. The peak voltage of the output after filtering can be given as:

$$V_{PEAK} = \frac{V_{in}GR_L}{2}$$

(2.24)

Note that (2.24) shows a linear relation ship between the input and output as expected. The DC current consumption can be calculated from equation (2.23) as  $\frac{I_P}{\pi}$ , Therefore the DC power consumption can be calculated as

$$P_{DC} = \frac{V_{CC}I_P}{\pi} \tag{2.25}$$

$$P_{RF} = \frac{{I_P}^2 R_L}{8} \qquad (2.26)$$

$$\eta = \frac{I_P R_L \pi}{8V_{CC}} \tag{2.27}$$

The maximum output RF power of Class B amplifier is the same as the class A amplifier, as both topologies can have an RF current swing of  $I_{MAX}/2$  at the desired frequency. See (2.23). (2.27) states that efficiency rises linearly with input drive. Maximum efficiency can be achieved by choosing load impedance to generate maximum current and voltage swing at the same time. The maximum output current swing for class B amplifier is  $I_{MAX}$  and maximum output voltage swing is ( $V_{CC}$ - $V_{sat}$ ) Therefore maximum efficiency can be calculated as

$$\eta_{MAX} = \left(\frac{V_{CC} - V_{SAT}}{V_{CC}}\right) \frac{\pi}{4} \tag{2.28}$$

In (2.28 )assuming  $V_{sat}$ =0 the efficiency can be achieve as high as  $\frac{\pi}{4} \approx 78\%$

# **2.2.3 CLASS AB**

The assumption of constant  $G_m$  for the entire active region is not valid for practical transistors. Especially near the threshold region the reduction of  $G_m$  causes distortions. The most linear  $G_m$  can be obtained at the middle of the active region. This is the reason that class A amplifiers are the most linear out of all classes [5].

The conduction angles of class AB amplifiers are between 360°-180°. The transistors generally biased at a little bit higher voltage than threshold voltage. Therefore the transistor operates in a more linear Gm region. The bias point and conduction angle can be seen in Fig. 2.12.

Fig. 2.12 Class AB power amplifier Bias Point and input/output swings

Class AB is a trade-off between class A and Class B in terms of linearity and efficiency. Generally push pull topology is used for class AB amplifiers (see Fig.2.11)

# **2.2.4 CLASS C**

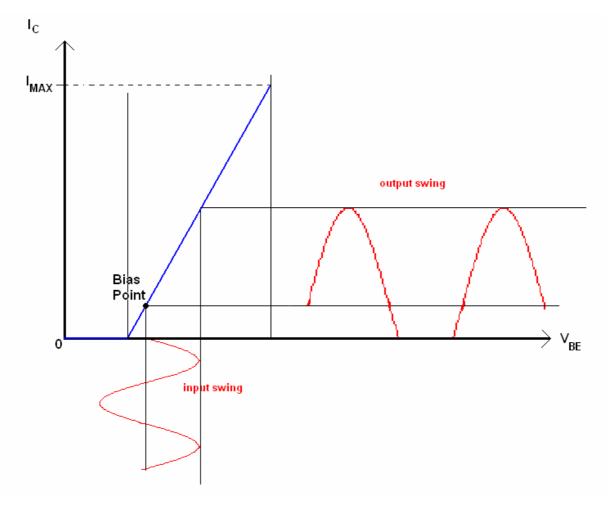

The efficiency of the power amplifier can be further increased by decreasing the conduction angle. Class C amplifier is biased below the threshold voltage of the transistors so the transistor is biased on less than half of the period. The efficiency increases because the turn on time of the transistor decreases. In Fig 2.13 the bias point and input/output voltage swings are given.

Fig. 2.13 Class C power amplifier Bias Point and input/output swings

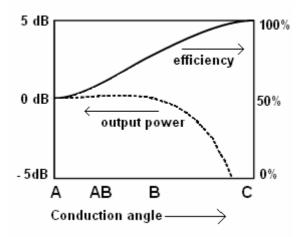

The conduction angle of class C amplifiers is a function of input drive. The efficiency increases as the conduction angle decreases. The efficiency achieves 100% when conduction angle is zero. In other words, the efficiency is 100% when the amplifier generates no RF power.

The main drawback of the class C power amplifier is the decease in power handling capability and the power gain. As the conduction angle drops below 180° the output power can be obtained from the transistor decreases because of the increased harmonic distortions. Also power gain starts to drop down as the conduction angle goes to 0 from 180. The approximate output power and efficiency curves with respect to conduction angle are plotted in Fig. 2.14.

Fig. 2.14 Approximate output power and efficiency curves with respect to conduction angle

In class C amplifiers the fundamental component of the output current is no longer a linear function of the input drive. Therefore best used of Class C amplifiers are constant envelope modulation schemes, such as FM or filtered FSK [6].

# 2.2.5 Switching Mode Power Amplifiers

In switching mode amplifiers the transistor works as a switch which means that it is either in "on" state or "off" state. In the on state transistor acts as a short circuit. In the off state it acts as open circuit. Assuming the circuit exhibits ideal switching characteristics, voltage and current do not exists on the transistors simultaneously. Therefore, the theoretical peak efficiency of switching mode PA's are 100%. Therefore ideally the device operates at 100% efficiency. Analog changes in the input amplitude will disappear in the switching mode amplifiers as the device does not have analog states. Therefore switching mode amplifiers can be used in frequency modulation, pulse width modulation, Gaussian minimum shift keying modulation, as there is no information on the amplitude in these modulation schemes. The phase and zero crossing of the input are preserved in the switching mode amplifiers. Most common switching mode power amplifiers are class D and class E. As the transistors works as a switch in these topologies generally field effect transistors preferred.

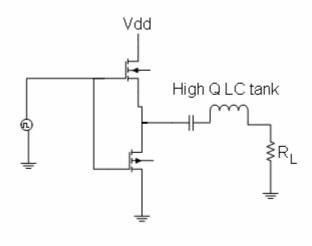

# 2.25.5 a) Class D

In Fig 2.15 basic class D power amplifier topology is given. Complimentary transistors used as in inverter topology therefore the output would be  $180^{\circ}$  phase shifted version of the input. Assume that the input is at the voltage of  $V_{dd}$  initially. Therefore top switch acts as open circuit and bottom switch acts as short circuit and the output is zero. For the next half circle

the input instantly goes to zero so top switch is switched to short circuit and bottom switch acts as an open circuit.

The output waveform is shaped by the output band pass filter which is tuned to the input signal frequency. This causes the output current to be a continuous sinusoid at the input frequency.

Fig. 2.15 Class D power amplifier topology

In practice, there are several sources of power dissipation that cause the Class D topology to have less than 100 % efficiency. Instant switching between the states could not be realized because of the output capacitances of the transistors. Finite switching time causes the efficiency to reduce. In addition, the transistors dissipate power since a finite resistance exists across its terminals during conduction, they can not act as an ideal short circuit [7].

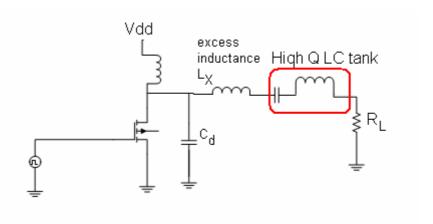

# 2.2.5 b) CLASS E

In Fig. 2.16 schematic view of shunt capacitor class E power amplifier is given. The shunt capacitor configuration employs the transistors parasitic output capacitor as a part of output matching circuit. Therefore the parasitic effects caused by the transistors output capacitance decreased by this configuration.

Fig. 2.16 Class E power amplifier topology

Unlike the Class D configuration, no power is lost due to the shunt capacitor in the ideal Class E power amplifier. Because, in the shunt capacitor Class E configuration,  $C_d$  provides an AC current path while the device is cut-of. The excess inductance is purposefully included in the output network to insure that  $C_d$  is completely discharged before the device begins conducting current [7].

# Chapter 3

# 3. Power Amplifier Design Fundamentals

In this section general Power amplifier design fundamentals will be discussed. First the design road map for a RF power amplifier design will be introduced and design details will be explained in the subsections.

The design of a power amplifier starts with the device selection. Then the device area is determined by the power requirement. The IV curve of the transistor has a key importance in the PA design. The DC operating points can be determined by the IV curves. In addition, approximate load lines and linear output power can be determined by using the IV curves. Optimum input and output impedances are determined by using parametric simulations including load pull technique. The matching network designed by using optimum source and load impedance values. If the simulation results do not meet the requirements, the device area and impedance matching networks should be changed. After completing these states the layout phase of the design starts. According to the parasitic extraction due to layout, design should be modified. The final design should be achieved in an iterative manner. A simple road map for PA design can be given in Fig. 3.1

Fig. 3.1 Power Amplifier Design Road Map

### 3.1 Device Selection

In this thesis, the PA is designed by using AMS 0.35µm SiGe BiCMOS HBT technology. High voltage HBT transistors are used for the design. The transistors are symbolized as npn <2><5><4>h5 HBT and the numbers refer to the number of collector, base and emitter contacts, respectively. The transistor is preferred for the PA applications because of its high breakdown voltage and relatively high transition frequency.

# 3.2 Plotting the I-V characteristics

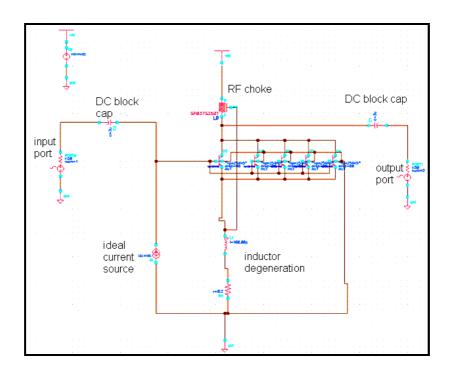

The next step for the PA design is plotting the I-V curves for the selected transistor. By this way the device area for the required power and the corresponding DC operating point can be determined. The base current  $(I_B)$  and collector voltage  $(V_C)$  is swept and collector voltage and current is plotted for determining the maximum linear output operation for the transistor. The schematic view for plotting the I-V curves is given in Fig.3.2. The emitter degeneration is applied with an inductor for increasing the linearity of the amplifier.

Fig. 3.2 Schematic View of the test setup for I-V curve simulations

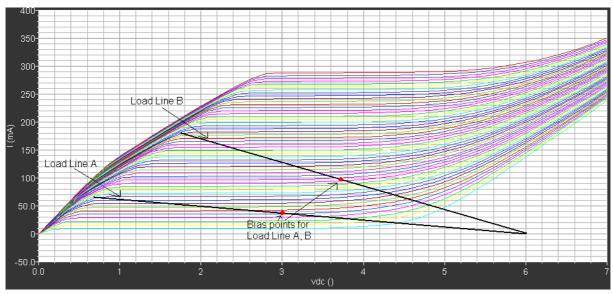

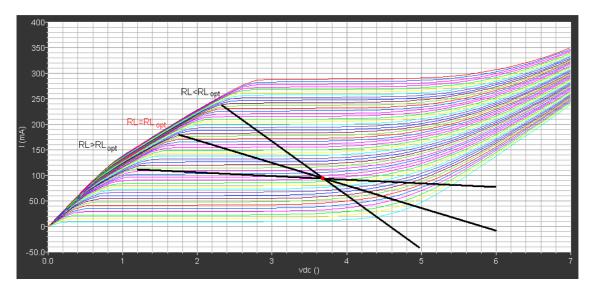

A general I-V curve is given in Fig.3.3. We can determine the transistors maximum voltage and current swings by using I-V curves. The upper limit for the voltage swing is determined by the collector emitter breakdown voltage of the transistor. The breakdown voltage of the transistor is specified by the foundries. The selected transistor has a breakdown voltage of 6V. The lower limit of the voltage swing is the knee voltage. On the other hand, the output current swings between zero and the bias current.

Fig. 3.3 Load Lines for a power amplifier on the IV curve

In Fig 3.3 two possible load lines are given for a fixed transistor size. Load line A symbolizes the low current operation whereas the load line B points out the high current density operation. Increasing the current density has a negative effect on the voltage swing as the knee voltage for the transistor increases in the high current region. Therefore the voltage swing decreases. The decrease in the voltage swing has a negative effect on the efficiency of the amplifier as the DC power consumption is linearly increasing with the bias current but the output RF power does not grow linearly because of the decrease in the voltage swing. The bias point for a power amplifier is very critical. The bias voltage of the amplifier should be the middle point of the knee voltage and threshold voltage. The bias current should be chosen as the maximum current level for the selected load line. The maximum current level is determined by using the maximum allowed current for the metal layers of the process and thermal considerations.

The collector current given in Fig 3.3 can be approximately scaled by the transistor area. Therefore increasing the transistor area increases the available current swing without degrading the efficiency. However increasing the transistor size, adding more transistors in parallel, reduces the impedance levels so that matching the input/output of the transistor impedances to  $50 \Omega$  becomes challenging. The difficulty in matching will also limit the power obtained for a given technology.

# 3.3 Load Pull Technique

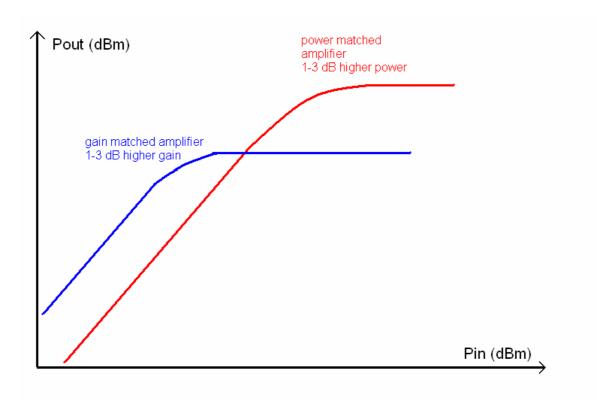

Input and output matching is very important for an RF amplifier design. The method of obtaining the optimum source and load impedance for a transistor changes from application to application. The optimum source and load impedances for a given transistor are different for maximum gain and maximum power cases. For obtaining the highest gain, the source and load impedances should be the complex conjugate of the input and output impedances of the transistor. However in power amplifier design the transistor should be "power matched" for maximum available power and efficiency, resulting in reduced gain. Maximum power and gain can not be obtained simultaneously for a given transistor. In Fig. 3.4 the input power versus output power is plotted for the same transistor for small-signal gain match and power match cases.

Fig. 3.4 Output Power-Input Power curves for power matched and gain matched cases

Choosing the proper load impedance is very important for obtaining the highest available power for a given transistor. The load resistor can be optimized for maximum power after the transistor area and bias point determined. The optimum load should be a resistor for the internal transistor satisfying the maximum voltage and current swing at the same time.[mavi kitap]. Therefore the load resistor can be given as:

$$R_L = \frac{V_{\text{max}} - V_{\text{min}}}{I_{\text{max}}} \tag{3.1}$$

The effect of load impedance is shown in Fig 3.5 in the I-V curve of the transistor. All of the load lines for the different load impedances pass through the bias point. The bias point corresponds the zero crossing of the AC signal. Three different load resistances are given in Fig 3.5. The optimum load resistance satisfies the maximum voltage and current swing condition. For the condition the load resistances lower than the optimum load resistance the transistor could not achieve the maximum voltage swing as the current swing run out. On the other hand the load resistances greater than the optimum load resistance complete the current swing while using only a portion of the available voltage swing.

Fig 3.5 Optimum Load impedance shown on the IV curves

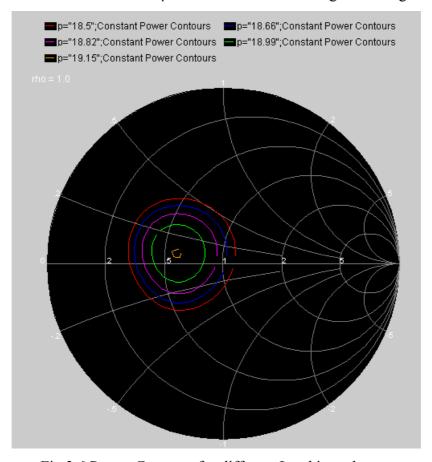

The device parasitic transforms the optimum load resistor ( $R_L$ ) to optimum load impedance ( $Z_L$ ). The optimum load impedance which gives the maximum power can be found by parametric simulations. For a given load impedance the output power can be calculated. (The load impedances yield the same output power contours in the Smith chart.) The power contour simulation results of the  $5x96 \ \mu m^2 \ 254h5$  transistors are given in Fig. 3.6.

Fig 3.6 Power Contours for different Load impedances

### 3.4 Input and Output Matching Circuit design

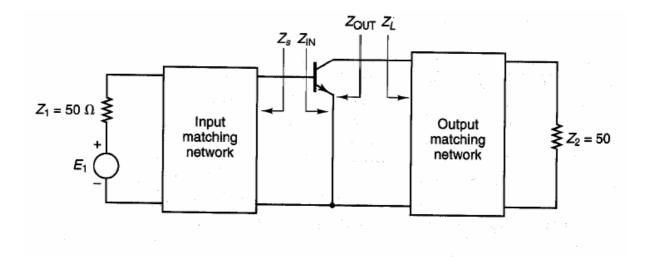

In an RF system all the discrete components are designed for 50  $\Omega$  so there is no reflection between them. For this reason the input ( $Z_{in}$ ) and the output ( $Z_{out}$ ) impedance of the amplifier should be 50  $\Omega$ . Therefore the optimum load ( $Z_L$ ) and source ( $Z_S$ ) impedance obtained in the previous step should be transformed to 50  $\Omega$ . A power amplifier view is given in Fig. 3.7 showing optimum source and load impedances.

Fig. 3.7 An amplifier schematic showing  $Z_{in}$ ,  $Z_{out}$ ,  $Z_L$  and  $Z_S$

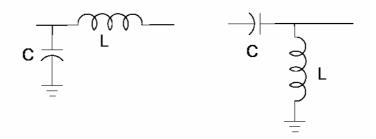

In the RF systems generally distributed transmission lines are used for matching. But transmission lines can not implemented on-chip, due to size limitations below certain frequency of operation. The most common impedance matching method for on-chip matching is using L-type matching networks. The schematic of some L-type matching networks consisting of just an inductor and a capacitor is given in Fig. 3.8.

Fig. 3.8 Schematic view of L-type matching networks

The ideal L-type matching network can transform every impedance value to 50  $\Omega$  without loss. But considering the losses of the passive elements the insertion loss of the matching

network grows extensively with decreasing matched impedance. So, matching low impedances to  $50~\Omega$  causes extensive losses.

After the matching networks are designed the performance of the Power amplifier can be tested. The main parameter for defining the performance of a power amplifier is the 1 dB compression point, efficiency and gain. If these parameters meet the requirements the designer can go forward to the layout step. If these parameters do not meet the requirements the designer should go through the previous steps. The layout, simulation and measurement results for the combined power amplifier will be given in chapter 5.

# **Chapter 4**

# 4. Power Combining Techniques

Designing high power devices at high frequencies is very challenging because of the trade off between high breakdown voltage and high mobility in solid-state devices. Various power combining techniques are developed over many years to overcome this restriction. However most of these techniques are circuit level combining techniques and can not be applied to chip-level combining [8]. In this section some of the widely used power combining techniques will be presented and their compatibility to chip-level combining will be discussed.

Chip level power combining techniques are required for high power single chip transmitter architectures. Chip-level power combining techniques offers size, cost and weight reduction and very high reproductivity, but suffers from increased losses due to low quality factor of integrated passives, especially inductors.

Usually, an impedance matching network is used to transform the  $50\Omega$  input/output impedance to lower equivalent source/load impedance seen by the PA (Fig.3.7). Because of the low supply voltage in silicon based technologies, the required load impedance could be extremely low when high power is required. Lower the value of load resistor ( $Z_L$ ), the higher the output power. However, matching a lower value of  $Z_L$  to  $50\Omega$  will result in excessive losses in the matching network and it will degrade the overall efficiency of the amplifier. Some of the powers combining techniques have an impedance matching capability in addition to power combining. Usually these techniques offer less loss with respect to independent

designs of power combining and impedance matching circuits. In this manner the impedance matching capabilities of the power combining techniques will also be discussed.

Some of the most common power combining techniques can be classified as distributed amplifier, transformer based power combiners, spatial power combiners and Wilkinson power divider based power combiners.

Brief background information about these power combining techniques will be presented in the next subsection. In this thesis an improvement on the Wilkinson power divider architecture will be presented. For this reason Wilkinson power divider based power combining techniques will be emphasized more than other techniques. The proposed power combining technique will be presented in the Wilkinson power divider based power combining techniques subsection with the simulation and measurement results.

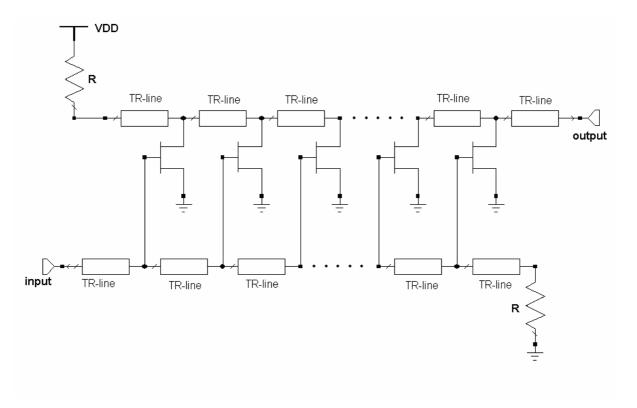

# 4.1 Distributed Amplifier Design

Distributed amplifiers can be considered as a power combining technique as many transistors are used in the design and output powers of these transistors added. A distributed amplifier consists of two transmission lines and multiple transistors providing gain through multiple signal paths. One of the transmission lines carries the input wave; the other carries the output wave. Transistors are placed between these transmission lines and supplies gain between input and output. Each transistor's output power adds in phase with the output wave so the output powers of the amplifiers are combined at the end of the transmission line. Transmission lines are terminated by resistors from one end to prevent reflections. General schematic representation of distributed amplifier topology is given in Fig. 4.1.

Fig 4.1 Schematic view of Distributed Amplifier Topology

FET based transistors are preferred for this topology for their high input impedance. FET device will not load the input transmission line. The distributed amplifier topology can be modified by using distributed transmission lines. The artificial transmission lines consist of series inductance and shunt capacitance can act like actual transmission lines. By this way parasitic gate and drain capacitances of the FET device taken into account for better frequency response. Using transistors parasitic capacitances as a transmission line, the frequency limitations of FET device can be avoided. The distribute amplifier idea is proposed for circuit level combining. But the idea can be applied for chip level combining, as the integration became the major motivation for the RF industry.

The main advantage of this technique is not achieving high power but increasing the bandwidth [9]. In [11], 12.5 dBm output power at 1 dB compression point is obtained in the 2-25 GHz frequency bandwidth. Both the transmission line [10], [11] and artificial transmission line [9] versions of this technique are applied for building single chip broadband amplifiers.

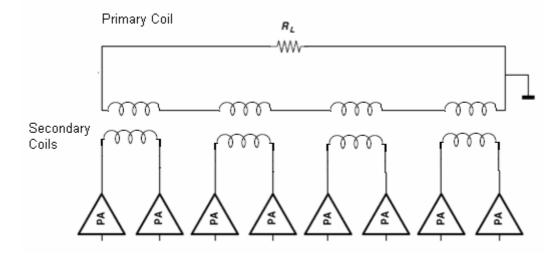

### 4.2 Transformer Based Power Combining Techniques

Transformer is a well known impedance matching element. For the ideal transformer the impedance matching ratio is  $1/N^2$  where N is the ratio of number of windings in each side of the coil namely primary and secondary coil. On-chip transformers can be realized by placing metal layers on top of each others. Therefore, signal will couple the adjacent metal layer. On-chip transformers can be used for power combining by driving one of the coils with more than one amplifier. Different on-chip transformer topologies developed for accomplishing power combining and impedance matching duty at the same time[12-15]. In Fig 4.2 general principle of power combining transformer is described.

Fig. 4.2 Transformer Based power combining topology

For impedance matching, primary coil of the transformer should be more than one winding. However, increasing the number of windings to satisfy the matching condition increases the insertion losses dramatically.

In [13] this technique is applied for 5.8 GHz WLAN applications and 20.5 dBm output power is obtained at 1dB compression point with a drain efficiency of 15%.

Power combining transformers can be used for on-chip power combining and impedance matching at the same time but low resistivity substrate degrade the performance of the amplifier greatly [13].1

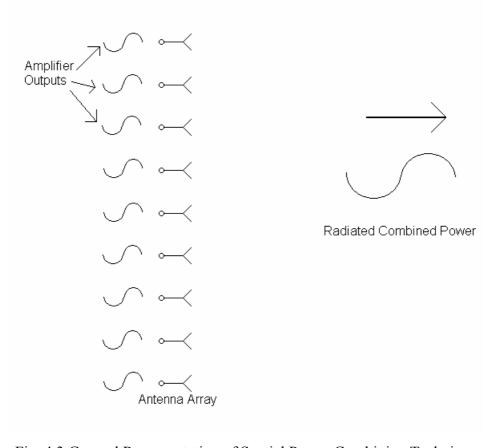

### 4.3 Spatial Power Combining Techniques

In this technique the output power of several solid state circuits are combined in free-space as opposed to in a lossy substrate. In this approach, the output of each amplifier is connected to an antenna [16]. Antennas are placed to form an array configuration so that the radiated power is added in a specific direction. This technique was first demonstrated in [17] by using

100 element array. General representation of the spatial power combining technique is given in Fig.4.3.

Fig. 4.3 General Representation of Spatial Power Combining Technique

The efficiency of spatial combiners are not effected by the number of combined devices. Therefore, larger number of elements can be combined efficiently by using this technique. The elements can be fed by using circuit level splitting techniques or spatially by using another antenna. This combining technique is not approperate for chip level combining for WLAN frequencies because of the extensive chip area of the antenna arrays.

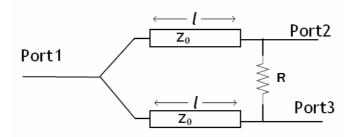

# 4.4 Wilkinson Power Divider Based Power Combining

The Wilkinson power divider was invented in 1960's. In this early topology, quarter wave transmission lines and a resistor used to match 3 ports in a lossless manner as shown in Fig. 4.4.

Fig. 4.4. A transmission line two-way Wilkinson power combiner

Wilkinson power dividers are generally designed for all three ports are matched to the same impedance. As all the ports have the same impedance values  $(Z_1)$  the design parameters for the transmission line of the Wilkinson Power divider is:

$$Z_0 = \sqrt{2}Z_1 \tag{4.1}$$

$$l = \lambda/4 \tag{4.2}$$

And

$$R=2 Z_1$$

(4.3)

for the isolation resistor.

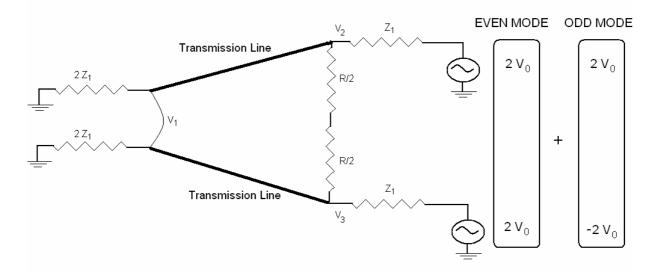

Wilkinson power divider circuit can be analyzed by using even and odd mode excitation method [18]. This method allows us to use symmetry in the 3 port device and decrease the effort to analyze. The Wilkinson power divider given in Fig. 4.4 can be depicted in a symmetrical manner including the port impedances as given in Fig. 4.5. The network given in Fig. 4.5 is drawn symmetric to the mid-plane.

Fig 4.5 Wilkinson Power Divider in symmetric form

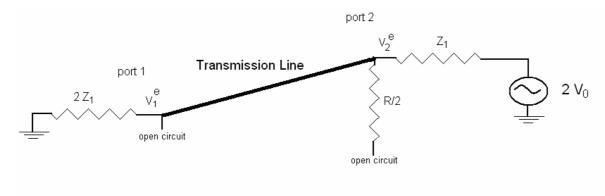

For the even mode excitation Ports 2 and 3 are excited by a voltage 2 V0. As the impedances of the port 2 and 3 are the same there is no current flow through the R/2 resistors due to symmetry with respect to mid plane. Therefore the network in Fig. 4.5 can be analyzed as two symmetric half circuits given in Fig. 4.6.

Fig. 4.6 Even Mode half circuit representation for the Wilkinson Power Divider In Fig. 4.6 the input impedance of the port 2 can be found by using  $\lambda/4$  transformation:

$$Z_{in2}^e = \frac{Z_0^2}{2Z_1},\tag{4.4}$$

Therefore if  $Z0 = \sqrt{2}Z_1$ ,

$Z_{in2}^e$  can be calculated as  $Z_1$  from Equation 4.1.

Therefore, the Port 2 is matched for the even mode excitation.

The  $V_1^e$  in Fig.5 can be found by using the voltage on transmission line as:

$$V_2^e = V_0 (4.5)$$

$$V_1^e = -jV_0\sqrt{2} (4.6)$$

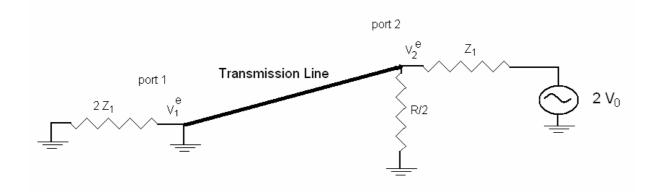

For the odd mode excitation, Ports 2 is excited with 2 V0 and Port 3 is excited with -2V0 therefore there is a voltage null across the mid plane of the circuit given Fig. 4.5. We can use the half circuit method by grounding the mid plane for the odd mode excitation. The half circuit for the odd mode excitation is given in Fig. 4.7.

Fig. 4.7 Odd Mode half circuit representation for the Wilkinson Power Divider

The input impedance seen from port 2 is the parallel of the impedance seen from the transmission line and R/2 resistor. As the  $\lambda/4$  transmission line is grounded at one end the impedance seen from port 2 is infinity and overall input impedance of the port 2 is R/2. Therefore, choosing R=2\* Z1 satisfies the matching condition for the port 2 in the odd mode excitation. Then  $V_2^o$  and  $V_1^o$  can be calculated as:

$$V_2^o = V_0, (4.7)$$

$$V_1^o = 0 (4.8)$$

With these even-odd mode method we can calculate

$$S_{22} = S_{33} = 0 (4.9)$$

because port 2 and 3 are matched for both even and odd mode excitation and

$$S_{21} = S_{12} = \frac{V_1^e + V_1^o}{V_2^e + V_2^o} = \frac{-j}{\sqrt{2}}$$

(4.10)

$S_{31} = S_{13}$  would be equal to  $S_{21} = S_{12}$  due to symmetry of Port 2 and Port 3.

And

$$S_{32} = S_{23} = 0 (4.11)$$

Because the mid plane of the network is grounded for the odd mode excitation and open circuit for the even mode excitation.

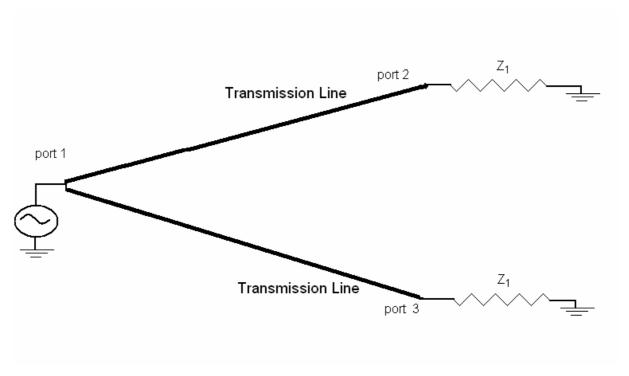

For determining the input impedance of the Port 1, a signal should applied to that port. As Ports 2 and 3 are symmetric, no current flows on the isolation resistor. The simplified schematic of the network for this condition is given in Fig. 4.8.

Fig. 4.8 Representation of Wilkinson Power Divider with port 1 excitation

As the Ports 2 and 3 are terminated with matched loads  $(Z_1)$  the input impedance of the Port 1 can be calculated as the parallel of the impedances seen from the transmission line.

As the  $Z_0$  of the  $\lambda/4$  transmission line is  $\sqrt{Z_1}$ :

$$Z_{in1} = \frac{(\sqrt{2}Z_1)^2}{2} = Z_1 \tag{4.12}$$

Therefore Port 1 is also matched and the S-parameters of the Wilkinson Power divider are calculated as follows:

$$S = \frac{-j}{\sqrt{2}} \begin{vmatrix} 0 & 1 & 1 \\ 1 & 0 & 0 \\ 1 & 0 & 0 \end{vmatrix}$$

(4.13)

The Wilkinson power dividers are used for power combining over many years in the RF industry. The schematic view of power combining circuit by using Wilkinson power divider is given in Fig. 4.9.

Fig. 4.9 Conventional Power combining schematic by Using Wilkinson power dividers

In common power combining method, the dividers are built that all of its ports are matched to  $50~\Omega$ . Therefore, input and output matching circuits are needed to match power transistors input and output impedance to  $50~\Omega$ . The power combining method generally used for circuit level combining by using distributed transmission line elements. However in [19] the idea is applied for on-chip combining at 24 GHz by using on-chip transmission line elements. The proposed power combining method is an improvement of the conventional Wilkinson power divider based power combining method. The proposed power combining method by using impedance matching Wilkinson power dividers are mentioned in the next subsection.

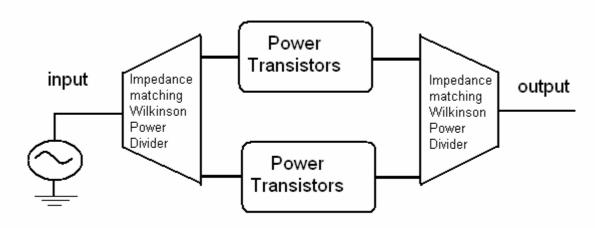

# 4.4.1 Proposed Power Combining Technique by Using Impedance Mathcing Wilkinson Power Dividers

The novel idea in this thesis is designing the Wilkinson power divider not for 50  $\Omega$  but for the input and output impedances of the power transistors. Therefore the input and output matching circuits can be eliminated. The overall schematic of the proposed power combining technique is given in Fig. 4.10.

Fig. 4.10 Proposed Power Combining Technique using Impedance Matching Wilkinson Power Dividers

Eliminating the input and output matching circuits decreases the matching losses therefore higher gain and higher power can be achieved with respect to conventional power combining method. In addition, the area of the circuit is reduced by eliminating the matching circuits and replacing conventional 50  $\Omega$  matched Wilkinson power divider with approximately the same sized impedance matching Wilkinson power dividers.

### 4.4.2 Impedance Matching Wilkinson Power Divider Design

The analyses of Wilkinson power divider given in chapter "4.3 Wilkinson Power divider based power combining" can be extended by choosing the impedances of Port 2 and 3 differ from Port 1(common port). As the impedances of the Port 2 and 3 are still the same even-odd mode analyses is also valid for this situation.

Assume that Port 1 is terminated with impedance  $Z_1$ , and Ports 2 and 3 are terminated with impedance  $Z_2$  where  $Z_1$  and  $Z_2$  are purely resistive (Fig. 4.4). For perfect match condition at all ports, the following equations should be satisfied.

$$l = \lambda/4$$

$$Z_0 = \sqrt{2Z_1Z_2}$$

$$R = 2Z_2$$

(4.14)

The characteristic impedance for the  $\lambda/4$  transformer of the impedance matching Wilkinson power divider is now  $Z_0 = \sqrt{2Z_1Z_2}$  to match 2  $Z_1$  to  $Z_2$ . Therefore the matching conditions for the even mode excitation (Fig. 4.6) and common port excitation (Fig. 4.8) are satisfied. Choosing the value of the isolation resistor as  $2Z_2$  satisfies the matching condition for the odd mode excitation (Fig. 4.7) so the same S parameters (Equation 4.13) can be obtained for the different impedance case.

The design equation given in (4.14) is an extension for the Wilkinson power divider design and the author does not meet this extension in any other published book or paper. As the new design equations allow us to choose different impedances for port 1 and the ports 2 and 3 the Wilkinson power divider can also be used for impedance matching duty. Therefore, it can be called "impedance matching Wilkinson power divider".

This extension has also the restriction of choosing the impedances of Port 2 and 3 the same as in the common Wilkinson power divider. This restriction does not limit the usage of the Wilkinson power dividers for the combined power amplifier application. Because the port impedances of Port 2 and Port 3 should be the same as the transistor blocks connected to these ports are identical.

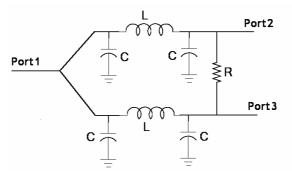

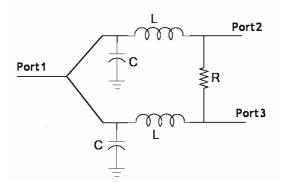

A quarter-wavelength transformer can be easily realized on PCB's by using distributed transmission line structures for microwave frequencies. However, for frequencies below 10 GHz, transmission line structures become too long to be placed in a reasonably small-sized chip. The designs can be miniaturized by using lumped element equivalent circuits [20], [21]. In this way the lumped element Wilkinson dividers can be realized in standard CMOS technology and 1.4 dB insertion loss is already reported at 24 GHz [22]. The lumped equivalent of the circuit in Fig. 4.4 is given in Fig. 4.11 where the transmission lines are replaced by a  $\pi$ -network of L-C elements.

Fig. 4.11  $\pi$ -network lumped equivalent two-way Wilkinson power divider

The values of inductance L and capacitance C are given by

$$L = \frac{Z_0}{2\pi f}$$

$$C = \frac{1}{2\pi f Z_0}$$

(4.15)

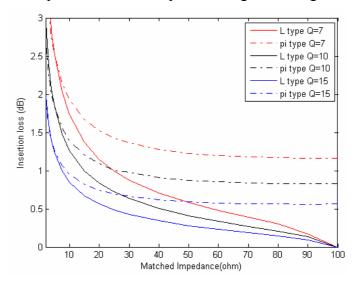

The  $\pi$ -network accomplishes the 90° phase shift and matching duty at the same time but suffers from high insertion loss when realized with low quality factor inductors which are generally less than 15 in silicon based technologies. On the other hand, the L-type matching network offers better insertion loss but does not satisfy the 90° phase shift; so degraded isolation is expected by the L-network realization. The  $\pi$ -type and L-type matching networks are designed to match 2 $Z_1$  to  $Z_2$  (Port 1 to Ports 2 and 3); therefore, very low return loss is obtained at all three ports of impedance matching Wilkinson power divider circuits.

In our case,  $Z_1$  is 50  $\Omega$ , so matching networks should match 100  $\Omega$  (2 $Z_1$ ) to the desired impedance levels at the Ports 2 and 3. The insertion loss of the impedance matching Wilkinson power divider directly relates with the insertion loss of matching networks. The insertion loss and phase shift for  $\pi$ -type and L-type matching networks are studied as a function of their inductor unloaded quality factor and the desired impedance levels at Ports 2 and 3. As the quality factors of the on-chip capacitors are significantly higher than the inductors, their losses are not considered here. The insertion loss of  $\pi$ -type and L-type matching network with respect to matched impedance is given in Fig.4.12.

Fig. 4.12 Insertion loss for  $\pi$ -type and L-type matching networks for various quality factors

Fig. 4.12 shows that the insertion loss for L-type network is smaller than pi-type network for the simulated values of impedances ranging between 2-100  $\Omega$ . For the higher matched impedances, difference between the two matching networks increases.

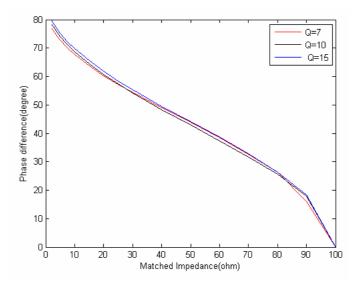

The  $\pi$ -type matching network offers a 90° phase shift which is needed for the isolation between Port 2 and Port 3. On the other hand, L-type matching network does not exactly satisfy this 90° phase shift condition. The phase difference for the L-type matching network which is designed to match 100  $\Omega$  to different impedances is plotted in Fig. 4.13.

Fig. 4.13 Phase difference for L-type matching network for various quality factor inductors

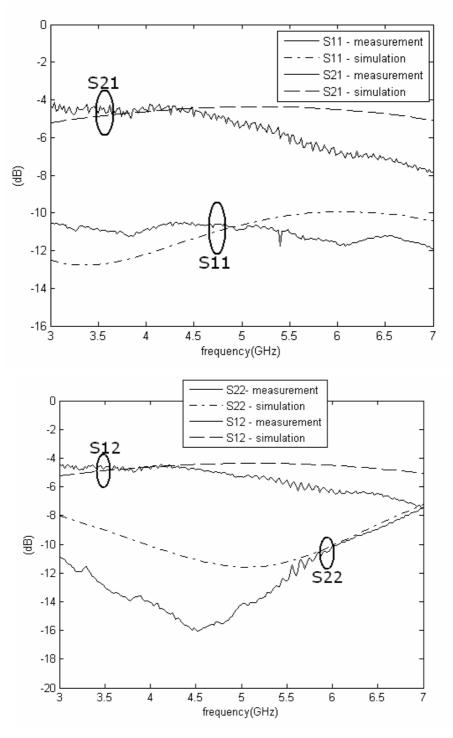

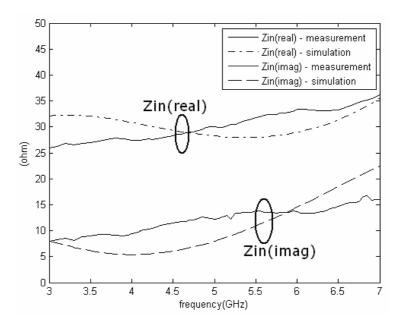

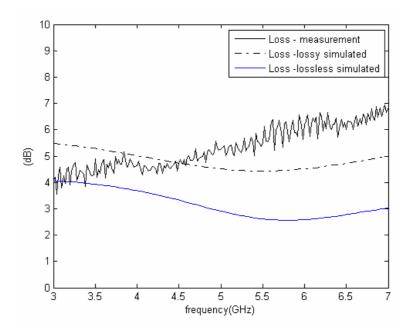

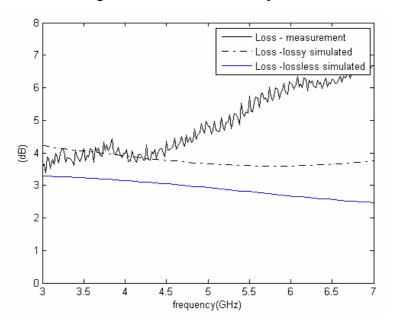

The desired  $90^{\circ}$  phase shift can be obtained in high matching ratios; for example, while matching  $100~\Omega$  to few ohms. However, this condition will not be satisfied if the matching impedance level increases. If the matched impedance level is  $100~\Omega$ , L and C values of the L-type network become zero, so both the insertion loss and phase shift is zero.