# REALIZATION OF A VOLTAGE CONTROLLED OSCILLATOR USING 0.35 $\mu m$ SiGe-BiCMOS TECHNOLOGY FOR MULTI-BAND APPLICATIONS

by AHMET KEMAL BAKKALOĞLU

Submitted to the Graduate School of Engineering and Natural Sciences

in partial fulfillment of

the requirements for the degree of

Master of Science

Sabancı University

Summer 2008

# REALIZATION OF A VOLTAGE CONTROLLED OSCILLATOR USING 0.35 $\mu m$ SiGe-BiCMOS TECHNOLOGY FOR MULTI-BAND APPLICATIONS

#### APPROVED BY:

Assoc. Prof. Dr. Yasar GÜRBÜZ .....

(Thesis Advisor)

Assist. Prof. Dr. Cem ÖZTÜRK .....

Assist. Prof. Dr.Ayhan BOZKURT .....

Assoc. Prof. Dr. Meric ÖZCAN

Assoc. Prof. Dr. Erhan BUDAK

DATE OF APPROVAL: .....

© Ahmet Kemal BAKKALOĞLU 2008

All Rights Reserved

# THE REALIZATION OF A VOLTAGE CONTROLLED OSCILLATOR USING 0.35 µm SiGe-BiCMOS TECHNOLOGY FOR MULTI-BAND APPLICATIONS

Ahmet Kemal BAKKALOĞLU

EE, MS Thesis, 2008

Thesis Supervisor: Assoc. Prof. Dr. Yaşar GÜRBÜZ

Keywords: Voltage controlled oscillator, multi-band multi standard radios, phase noise, wideband VCO

# Abstract

The stable growth in wireless communications market has engendered the interoperability of various standards in a single broadband frequency range from hundred MHz up to several GHz. This frequency range consists of various wireless applications such as GSM, Bluetooth and WLAN. Therefore, an agile wireless system needs smart RF front-ends for functioning properly in such a crowded spectrum. As a result, the demand for multi-standard RF transceivers which put various wireless and cordless phone standards together in one structure was increased. The demand for multi-standard RF transceivers gives a key role to reconfigurable wideband VCO operation with low-power and low-phase noise characteristics. Besides agility and intelligence, such a communication system (GSM, WLAN, Global Positioning Systems, etc.) required meeting the requirements of several standards in a cost-effective way. This, when cost and integration are the major concerns, leads to the exploitation of Si-based technologies.

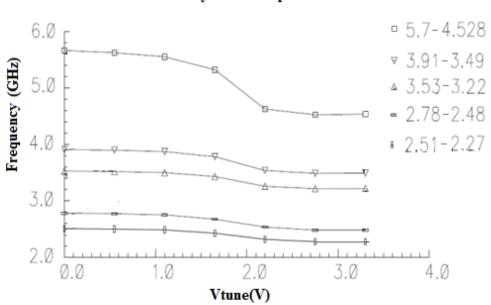

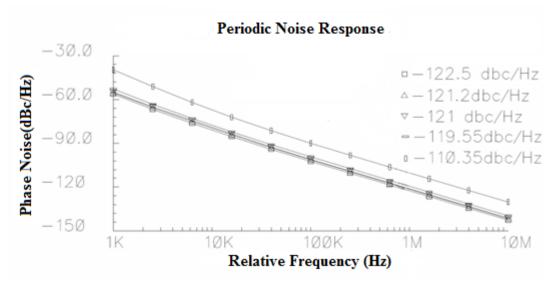

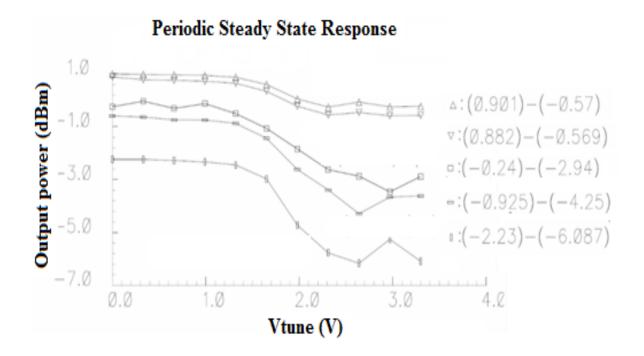

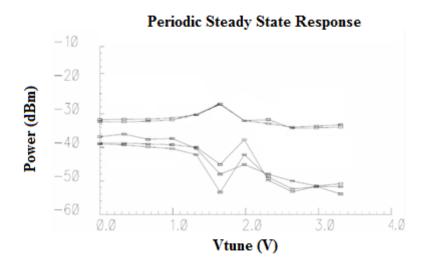

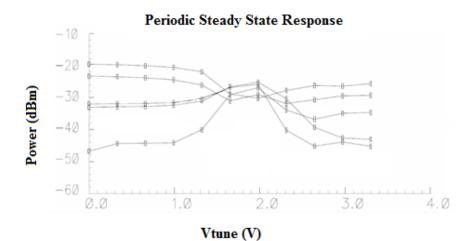

In this thesis, an integrated 2.2-5.7GHz Multi-band differential LC VCO for Multistandard Wireless Communication systems was designed utilizing 0.35µm SiGe BiCMOS technology. The topology, which combines the switching inductors and capacitors together in the same circuit, is a novel approach for wideband VCOs. Based on the post layout simulation results, the VCO can be tuned using a DC voltage of 0 to 3.3V for 5 different frequency bands (2.27-2.51 GHz, 2.48-2.78GHz, 3.22-3.53GHz, 3.48-3.91GHz and 4.528-5.7GHz) with a maximum bandwidth of 1.36GHz and a minimum bandwidth of 300MHz. The designed and simulated VCO can generate a differential output power between 0.992 dBm and -6.087 dBm with an average power consumption of 44.21mW including the buffers. The average second and third harmonics level were obtained as -37.21 dBm and -47.6 dBm, respectively. The phase noise between -110.45 and -122.5 dBc/Hz, that was simulated at 1 MHz offset, can be obtained through the frequency of interest. Additionally, the figure of merit (FOM), that includes all important parameters such as the phase noise, the power consumption and the ratio of the operating frequency to the offset frequency, is between -176.48 and -181.16 and comparable or better than the ones with the other current VCOs. The main advantage of this study in comparison with the other VCOs, is covering 5 frequency bands starting from 2.27 up to 5.76 GHz without FOM and area abandonment.

## 0.35 μm SiGe-BiCMOS TEKNOLOJİSİ KULLANILARAK ÇOKLU BAND UYGULAMALARI İÇİN GERİLİM KONTROLLÜ OSİLATÖR DEVRESİNİN GERÇEKLENMESİ

Ahmet Kemal BAKKALOĞLU

EE, Master Tezi, 2008

Tez Danışmanı: Doç. Dr. Yaşar GÜRBÜZ

Anahtar Kelimeler: Gerilim kontrollü osilatör (VCO), çok bandlı ve çok standardlı alıcı vericiler, faz gürültüsü, geniş band gerilim kontrollü osilatör

### Özet

Kablosuz iletişim piyasasındaki büyüme, 100 MHz'lerden GHz'lere kadar uzanan geniş frekans bandında çalışan standardlarıda beraberinde getirdi. Bu frekans bandındaki uygulamalardan bazıları; GSM, Bluetooth ve WLAN'dır. Kablosuz sistemlerin böylesine karmaşık spektrumlarda çalışabilmesi için akıllı RF devrelerine ihtiyaç vardır. Bunun sonucu olarak birçok standartta çalışabilen ve bunları tek yapıda toplamış radyo frekansında devrelere ihtiyaç artmıştır. En çekici rf bloklarından biri olan dar bandlı osilatör devreleri yerini çok bandlı devrelere bırakmıştır. Çok standartlı alıcı verici devreleri düşük güç tüketimli, düşük faz gürültülü ve yapılandırılabilir osilatörlere kritik bir rol vermiştir. Bunun yanı sıra sistemin maliyet açısından da efektif olması gerekmektedir. Maliyet ve entegrasyon söz konusu olduğunda Silikon tabanlı teknolojiler ön plana çıkmaktadır. Heterojen bipolar transistörlerin (HBT), CMOS ve pasif elemanların entegrasyonundaki rahatlık da bu teknolojinin avantajlarındandır.

Bu tezde, 2,2-5,7 GHz frekans aralığında çalışabilen çok kanallı diferansiyel LC gerilim kontrollü osilatör devresi (0.35 µm SiGe-BiCMOS teknolojisi kullanılarak) tasarlanmıştır. Aynı topoloji içerisinde endüktans ve kapasitans anahtarlama, geniş bandlı osilatör devrelerinde yeni bir yaklaşımdır. Devrenin serim sonrası sonuçlarında, beş farklı frekans band aralığında (2.27-2.51 GHz, 2.48-2.78GHz, 3.22-3.53GHz, 3.48-3.91GHz ve 4.528-

5.7GHz) maksimum 1.36 GHz ve minimum 300MHz band genişliğinde çalıştığı gözlemlenmiştir. Devre, 0.992 dBm ve -6.087 dBm arasında değişen diferansiyel çıkış gücüne sahiptir. Ayrıca, buffer katı da dahil olmak üzere ortalama 44.21 mW güç tüketimi vardır. Faz gürültüsü değerleri 1 MHz offset frekansında, seçilen frekans bandına göre -110.45 den - 122.5 dBc/Hz 'e kadar değişmektedir. Bunun yanında osilatör için en önemli parametreleri içinde bulunduran figure of merit (FOM), kıyaslanan osilatörlerle hemen hemen aynı veya daha iyi bulunmuştur. Bu çalışmayı öne çıkaran en önemli faktör alan ve FOM 'den taviz vermeksizin beş farklı frekans bandında çalışabilen bir yapı olmasıdır.

#### Acknowledgements

I was accepted to the Gradute Faculty of Sabanci University in 2006. The acceptance gave me the chance of not only being a member of elit research group but also gaining many experience in engineering and academic area. I could not describe this thesis without the help of my professors, co-workers and my friends in Sabanci University.

First of all, I would like to thank to my thesis advisor, Assoc. Prof. Yaşar GÜRBÜZ for his great support. He always strengthens me not only in academic life but also in real life. I am greatful to Assist. Prof. İbrahim TEKİN for gaining me new perspectives. Also I am thankful to Assist. Prof Ayhan Bozkurt for his patience in technical discussions and help for Solaris based problems. I would also like to thank to my thesis defence committee members, Assist. Prof. Dr. Cem ÖZTÜRK, Assoc. Prof. Dr. Meric ÖZCAN and Assoc. Prof. Dr. Erhan BUDAK for their important supports, comments and presences. Before starting this project, I have worked at ASELSAN project group. The background of the thesis is the experiences at the project. In this regard, I am thankful to Arzu MİNARECİ ERGİNTAV, Hüseyin KAYAHAN and Ömer CEYLAN for their technical support and friendship.

Moreover, I want to thank to İbrahim Onur ESAME for his great support at the beginning of the project and afterwards. Special thanks to my collegues and friends who had contributions to this work, Emre HEVES, Bülent KÖROĞLU and Mehmet KAYNAK.

Finally, I would like to thank to private people in my life, my parents Ayşe, Dursun BAKKALOĞLU and my sister Hilal. Also special thanks to Nejla ERASLAN for being near me not only at good times but also hard times.

My thesis is fully devoted to my mother...

# **Table of Contents**

# **CHAPTER 1 INTRODUCTION**

| 1.1 The briefing on the Wireless LAN Standards | . 1 |

|------------------------------------------------|-----|

| 1.1.1 IEEE 802.11a                             | . 1 |

| 1.1.2 IEEE 802.11b                             | . 2 |

| 1.1.3 IEEE 802.11g                             | . 3 |

| 1.1.4 IEEE 802.11n                             | . 4 |

| 1.1.5 HIPERLAN/2                               | . 4 |

| 1.1.6 IEEE 802.16                              | . 4 |

| 1.2 Communication Transceivers                 | . 5 |

| 1.3 Thesis Overview                            | . 7 |

# **CHAPTER 2 OSCILLATORS IN TRANSCEIVERS**

| 2.1 Frequency operations by using Oscillators | 8  |

|-----------------------------------------------|----|

| 2.2 Performance Parameters                    | 9  |

| 2.2.1 Phase Noise                             | 9  |

| 2.2.2 Power Consumption                       | 10 |

| 2.2.3 Operating Frequency                     | 11 |

| 2.2.4 Stability                               | 12 |

| 2.2.5 Output power                            | 12 |

| 2.3 Topology and Technology                   | 12 |

| 2.3.1 Ring Oscillator                         | 13 |

| 2.3.2 Relaxation Oscillator                   | 13 |

| 2.3.3 LC Oscillators                          | 14 |

# **CHAPTER 3 VCO DESIGN**

| 3.1 Topology and Design procedure |  |

|-----------------------------------|--|

| 3.2 LC Tank Design                |  |

| 3.2.1 Tank inductance             |  |

| 3.2.2 Tank Capacitance            |  |

| 3.2.3 Switch Method               |  |

| 3.2.4 Varactor                    |  |

| i. Varactor Types                                         |    |

|-----------------------------------------------------------|----|

| PN-JUNCTION VARACTOR                                      |    |

| MOS VARACTOR                                              |    |

| ii. Large signal analysis of MOS Varactors in -Gm LC VCOs |    |

| 3.3 Design of gm stage                                    |    |

| 3.4 Design of bias circuitry                              |    |

| 3.5 Switched Circuitry                                    |    |

| 3.6 Fine Tuning Circuitry                                 |    |

| Main parameters and Simulation results                    |    |

| 3.7 Design of VCO buffer                                  |    |

| 3.8 Small Signal Analysis                                 | 51 |

| 3.9 Layout Design                                         |    |

| 3.10 Simulation Results                                   |    |

| 3.11 Measurement Results                                  |    |

|                                                           |    |

# CHAPTER 4 CONCLUSION AND FUTURE WORK

# REFERENCES

# List of Figures

| Figure 1 802.11a OFDM system channel frequency locations                                   | 2    |

|--------------------------------------------------------------------------------------------|------|

| Figure 2 Operation frequencies for wireless communication                                  | 5    |

| Figure 3 Typical super heterodyne communication transceiver                                | 5    |

| Figure 4 Removal of the image                                                              | 6    |

| Figure 5 Phase-Locked Loop                                                                 | 9    |

| Figure 6 Spectrum of a typical oscillator                                                  | . 10 |

| Figure 7 SNR degradation                                                                   | . 10 |

| Figure 8 Ring Oscillator                                                                   | . 13 |

| Figure 9 Relaxation Oscillator                                                             | . 14 |

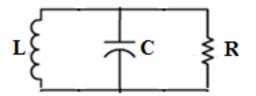

| Figure 10 Parallel LC resonator                                                            | . 14 |

| Figure 11 Impedance of the Tank                                                            | . 15 |

| Figure 12 (a) Colpitts and (b) Hartley Oscillators                                         | . 16 |

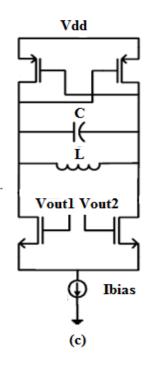

| Figure 13 Cross-coupled Oscillators (a) NMOS only (b)PMOS only (c) Complementary           | . 17 |

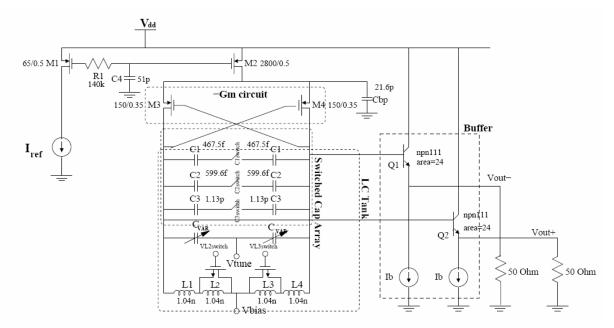

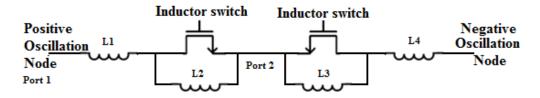

| Figure 14 Multi-band VCO schematic including L-C switched resonators                       | . 21 |

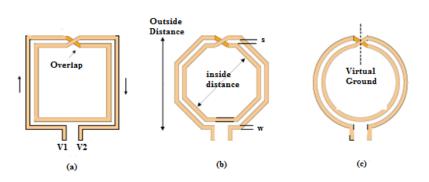

| Figure 15 Inductor Geometries ; (a)square (b) octagonal, (c) circular                      | . 23 |

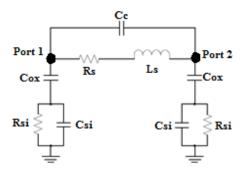

| Figure 16 Inductor Modeling : Lumped -model of the two port spiral inductor                | . 23 |

| Figure 17 Equivalent circuit of one port grounded inductor                                 | . 24 |

| Figure 18 Inductance value of AMS library inductor.                                        | . 25 |

| Figure 19 Quality factor of the AMS Library Inductor                                       | . 25 |

| Figure 20 Inductor Layout                                                                  | .26  |

| Figure 21 Cross Sections of (a) Double Poly capacitor (b) the MIM capacitor                | . 27 |

| Figure 22 Equivalent circuit Model of an MIM Capacitor                                     | . 27 |

| Figure 23 Binary weighted array of switched capacitors                                     | . 29 |

| Figure 24 Improved differential switched-tuning circuit                                    | . 31 |

| Figure 25 Schematic of switched resonator                                                  | . 31 |

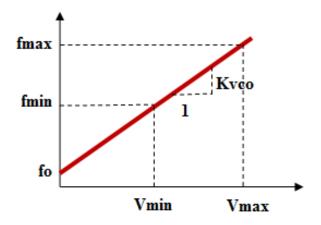

| Figure 26 Ideal Frequency Tuning Curve                                                     | . 33 |

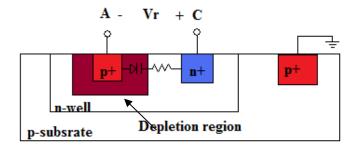

| Figure 27 Cross section of p <sup>+</sup> /n-well junction capacitance                     | . 33 |

| Figure 28 Typical tuning characteristics for the PMOS capacitor with $B \equiv S \equiv D$ |      |

| Figure 29 Charge carrier path for the IMOS capacitor                                       | . 35 |

| Figure 30 Typical tuning characteristics for the inversion mode varactor                   | . 35 |

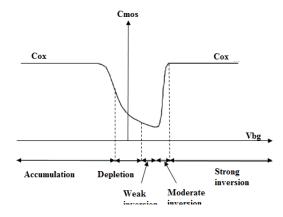

| Figure 31 Accumulation-mode MOS capacitor                                                  | . 36 |

| Figure 32 Typical tuning characteristics for the accumulation mode varactor                | . 36 |

| Figure 33 The configuraiton of the g <sub>m</sub> stage that actually is the VCO core      | . 41 |

| Figure 34 The Additional of gm-stage output resistance to R <sub>L,inductor</sub>          | . 42 |

| Figure 35 Current Mirror                                                                   | . 44 |

| Figure 36 Simplified model of the switched circuitry                                       | . 46 |

| Figure 37 Subcircuit Model of Accumulation mode MOS varactor                               |      |

| Figure 38 Layout of the A-MOS                                                              | . 48 |

| Figure 39 Varactor capacitance value versus voltage change                                 |      |

| Figure 40 Quality Factor variation with voltage change                                     | . 49 |

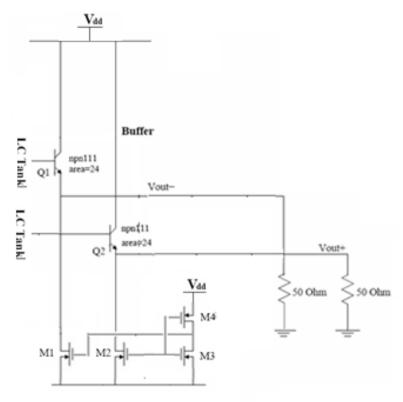

| Figure 41 Buffer Circuit                                                              | 50      |

|---------------------------------------------------------------------------------------|---------|

| Figure 42 VCO small signal model. (a)Simplified VCO circuit schematic, (b)the equi    | ivalent |

| small signal model for VCO, (c) equivalent circuit model for inductors and (d) a para | llel LC |

| oscillator model                                                                      |         |

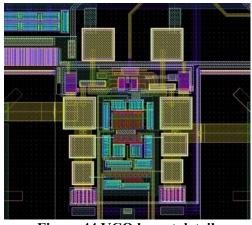

| Figure 43 Multi-Band Layout                                                           |         |

| Figure 44 VCO layout detail                                                           |         |

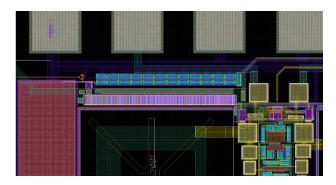

| Figure 45 VCO layout detail bias circuitry                                            |         |

| Figure 46 Frequency tuning range of Multiband VCO                                     | 59      |

| Figure 47 Phase Noise performance at three frequencies for multi-band VCO             | 59      |

| Figure 48 Fundamental frequency output power vs. tuning voltage                       |         |

| Figure 49 Second harmonic output powers vs. tuning voltage                            |         |

| Figure 50 Third harmonic output powers vs. tuning voltage                             |         |

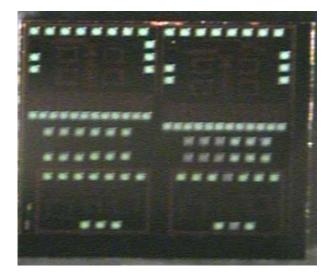

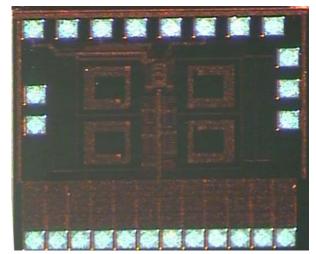

| Figure 51 The fabricated chip                                                         |         |

| Figure 52 The multi-band VCO part of the chip                                         |         |

| Figure 53 The measurement setup                                                       |         |

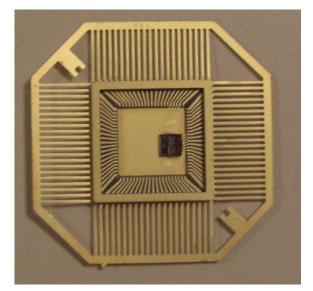

| Figure 54 Die Package                                                                 |         |

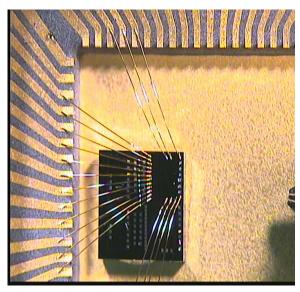

| Figure 55 Closer view of Package                                                      |         |

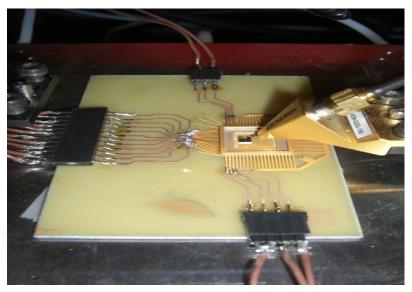

| Figure 56 Measurement setup                                                           |         |

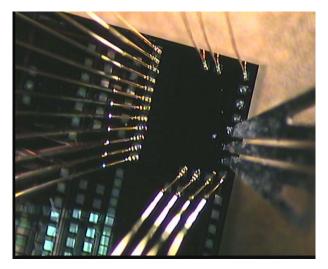

| Figure 57 Closer view of measurement setup                                            |         |

# List of Tables

| 3  |

|----|

| 11 |

| 28 |

| 37 |

| 37 |

| 42 |

| 42 |

| 46 |

|    |

| 49 |

| 51 |

| 55 |

| 60 |

| 61 |

|    |

## **CHAPTER 1 INTRODUCTION**

## 1.1 The briefing on the Wireless LAN Standards

The fastest growing segment of the semiconductor industry has been the wireless communication market in the recent years. For the indoor access, wireless local area networks (WLANs) have been introduced as a set of standards to provide a simple and flexible way for people plugging into a network. IEEE 802.11 is a set of standards for wireless local area network (WLAN) computer communication, developed by the IEEE LAN/MAN Standards Committee (IEEE 802) in the 5 GHz and 2.4 GHz public spectrum bands. Furthermore, IEEE developed a new standard called Wireless Metropolitan area networks (WMANs) for urban area coverage wireless access [1]. IEEE 802.16 WMANs standard uses frequency band from 2 to 11 GHz. The following sections include brief information about IEEE frequency bands which are widely used in wireless communication.

## 1.1.1 IEEE 802.11a

IEEE 802.11a devices and many wireless devices use Unlicensed National Information Infrastructure (U-NII) band which operates around 5 GHz. In comparison with 802.11b, it employs a different multiplexing technique: orthogonal frequency division multiplexing (OFDM). The OFDM system uses parallel subcarriers to transmit and receive a single data stream [2,4]. In 802.11a [4], each channel contains 52 sub-carriers as 48 data carriers and 4 pilot carriers.

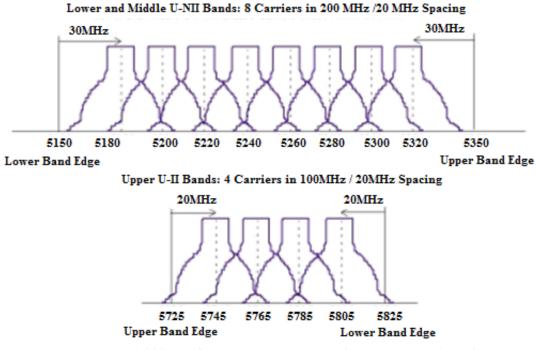

U-NII band includes three subbands: U-NII lower sub-band, from 5.15 GHz to 5.25 GHz; U-NII middle sub-band, from 5.25 to 5.35 GHz; and U-NII upper band, from 5.725 to 5.825 GHz. The lower and middle U-NII sub-bands accommodate eight channels in a single band with a total bandwidth of 200 MHz. The upper U-NII band accommodates four channels in a 100-MHz bandwidth. The channel frequency spacing is 20 MHz and the occupied channel bandwidth is 16.6 MHz. The U-NII bands with channel locations are shown in Figure 1.

Figure 1 802.11a OFDM system channel frequency locations[4]

## 1.1.2 IEEE 802.11b

In USA (FCC) and Europe (ETSI), the operating frequency band for 802.11b is in the range of 2.4–2.4835 GHz. Additionally, it is allocated by the regulative authority of Japan as 2.471–2.497 GHz. For high data rate channels in the USA, three channels centered at 2412, 2437 and 2462 MHz have been allocated. The channel spacing is 25 MHz and null-to-null bandwidth is 22 MHz. France allows in the range of 2.4465–2.4835 GHz, and also this operation is allowed in the range of 2.445–2.475 GHz band in Spain. The frequency channel plan of IEEE 802.11b for each country is indicated in Table 1[3].

| CHNL_ID  | Frequency | X'10' | X'20' | X'30' | X'31' | X'32'  | X'40' |

|----------|-----------|-------|-------|-------|-------|--------|-------|

| CIINL_ID | (MHz)     | FCC   | IC    | ETSI  | Spain | France | MKK   |

| 1        | 2412      | x     | x     | x     | -     | -      | -     |

| 2        | 2417      | X     | X     | x     | -     | -      | -     |

| 3        | 2422      | X     | X     | x     | -     | -      | -     |

| 4        | 2427      | X     | X     | x     | -     | -      | -     |

| 5        | 2432      | x     | x     | x     | -     | -      | -     |

| 6        | 2437      | x     | x     | x     | -     | -      | -     |

| 7        | 2442      | X     | X     | x     | -     | -      | -     |

| 8        | 2447      | X     | X     | x     | -     | -      | -     |

| 9        | 2452      | X     | X     | x     | -     | -      | -     |

| 10       | 2457      | X     | X     | X     | x     | X      | -     |

| 11       | 2462      | X     | X     | X     | x     | X      | -     |

| 12       | 2467      | -     | -     | x     | -     | X      | -     |

| 13       | 2472      | -     | -     | X     | -     | X      | -     |

| 14       | 2477      | -     | -     | -     | -     | -      | x     |

Table 1 Frequency channel plan for IEEE 802.11b

#### 1.1.3 IEEE 802.11g

IEEE 802.11g is the 802.11a standard which operates in the 802.11b band (2.4 GHz Industrial, Scientific and Medical band). IEEE 802.11a OFDM system has a higher maximum data rate (54 Mbit/s) than 802.11b (11 Mbit/s). However, 802.11a has higher free space path loss than 802.11b, because its operation frequency is higher than IEEE 802.11b. This means that 802.11a has a shorter range compared to 802.11b for the same transmitted power. The 802.11g standard was designed for supporting high data rate and a larger range at the same transmitted power.

#### 1.1.4 IEEE 802.11n

IEEE 802.11n is an amendment version of previous wireless local area network standards such as IEEE 802.11b and IEEE 802.11g. IEEE 802.11n was developed by adding Multiple Input and Multiple Output (MIMO) system and 40 MHz operation to the physical layer (PHY). MIMO uses multiple receiver and transceiver system to improve the system performance. In order to support higher data rates, 802.11n provides wider bandwidth (40MHz) than the previous 802.11 operation.

#### 1.1.5 HIPERLAN/2

For countries outside of the USA, the wireless LAN may or may not be compatible with the 802.11 standards. But it is worthwhile to briefly introduce another important wireless LAN standard: high performance local area network type 2 (HIPERLAN/2) standards. HIPERLAN/2 is used in Europe and its territories, and defined by the European Telecommunication Standards Institute (ETSI). HIPERLAN/2 is very similar to the IEEE 802.11a standard expect its operation frequency range [4]. HIPERLAN/2 operates in two subbands 5.15-5.35 GHz, and 5.47-5.725 GHz. The OFDM system in HIPERLAN/2 is almost similar to 802.11a.

#### 1.1.6 IEEE 802.16

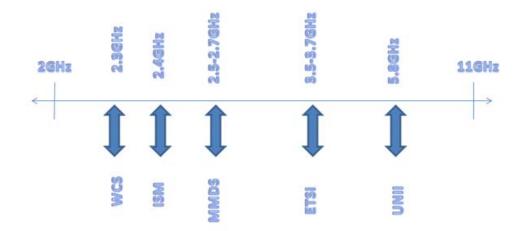

In order to give wireless access to the urban areas, IEEE 802.16a wireless Metropolitan Area networks(WMANs) standard was introduced firstly on 1 April 2003 [2]. This system utilizes frequencies from 2 to 11 GHz. There are licensed and un-licensed bands in the wide frequency band. The licensed bands are 2.3 GHz (WCS), between 2.5 to 2.7 GHz (MMDS), between 3.5 to 3.7 GHz (ETSI), and unlicensed bands are 2.4 GHz (ISM) and 5.8 GHz (U-NII) in which WLANs operates as well [4-5]. As a result, multi-band multi-standard transceiver architecture should have five different frequency bands in a wide range as represented in Figure 2.

Figure 2 Operation frequencies for wireless communication

# **1.2 Communication Transceivers**

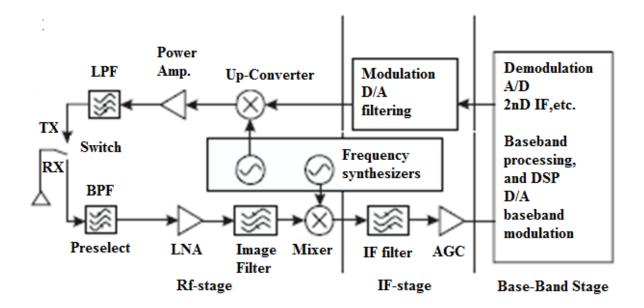

Figure 3 shows the diagram of the major sub-circuit blocks of a typical super heterodyne communication transceiver. The sub-block are commonly the same for all transceivers.

Figure 3 Typical super heterodyne communication transceiver [6]

The antenna connects both the transmit side and the receive side. Depending on the communication state the antenna transmits or receives a signal through antenna switch or

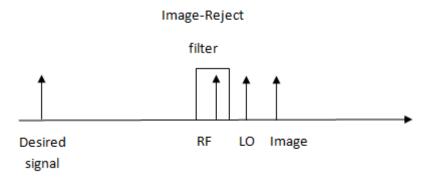

duplexer. At the receiver part, firstly the input pre-selection filter takes the broad spectrum of signals coming from the antenna and removes the signals that are not in the band of interest. This process prevents overloading of the low-noise amplifier(LNA). The main goal of LNA is amplifying the input signal without adding much noise. This process should be performed firstly, because the input signal that comes to the antenna at lower power has to be amplified without a distortion. Thus, any noise added after this stage becomes less of concern for the system. The signals that are at the same distance at the above and below of the LO produce an output at the same frequency. The frequency that we do not want to receive is called the image. We can write the relations for the frequencies as  $f_{rf} = f_{lo} - f_a$  and  $f_i = f_{lo} + f_a$ . Where are  $f_i$  the image problem frequency and  $f_a$  the desired frequency. This means that there will be a problem if we have a station at RF frequency and at the image. This problem is called as image problem. The image reject filter selects only the RF frequency for removing the image as shown in Figure 4.

Figure 4 Removal of the image

The output of the mixer is the addition and subtraction of the RF and LO frequencies. The addition is filtering by using intermediate frequency filter. Thus, after the IF filter, the RF signal is translated down to the IF frequency. The other input of the mixer is coming from a voltage-controlled oscillator located inside a frequency synthesizer.

There may be many different channels or frequency bands at the input of the radio. Therefore, the local oscillator should have a controlled block to get the same intermediate frequency. Before the signal passes on to the back end of the receiver, the automatic gain control (AGC)

stage has to bring the signal to a specific amplitude level. After that operation, the signal will be digitalized through the use of an analog-to-digital converter.

The aforementioned receiving process could be seen as a reverse function of transmitter part. The back-end digital signal is used to modulate the carrier in the IF stage. A mixer converts the modulated signal and IF carrier up to the desired RF frequency. As in receiver part, the other input for the mixer comes from the local oscillator. A power amplifier must be used to increase the signal power, because the RF carrier and associated modulated data have to be transmitted over large distances through the loss media. Depending on the application, the power should be increased from the milliwatt range to a level in the range of hundreds of milliwatts. In order to avoid transmission of the unwanted frequencies after the PA operation, a low pass filter sould be used for removing any possible harmonics.

## **1.3 Thesis Overview**

Chapter II start with application areas of Voltage Controlled Oscillators. Additionally, specific performance parameters such as phase noise, power consumption, operation frequencies, stability and output power were described. At the end of the chapter, VCO topologies were introduced with a brief comparison.

The topology and design procedure that were used in this design have been described in Chapter III. The core part of the VCO, LC tank, was defined through the detailed investigations of the of tank inductances, the tank capacitances, the switching method and the varactors. Moreover, the other parts of VCO like  $G_{m, buffer}$ , fine tuning, bias and switched circuits were presented. Following the small signal model of whole design, layout issues, post-layout simulation and measurement results were presented.

Finally, the performance and novel characteristics of the multi-band voltage controlled oscillator were covered in Chapter IV. This section also includes the future work for developing the performance of the multi-band VCO.

# **CHAPTER 2 OSCILLATORS IN TRANSCEIVERS**

In communication systems, the oscillators are utilized for providing the clock signals in digital circuits and frequency conversion in analog circuits. The oscillators are called as Local oscillators when used for frequency conversion. In this thesis, the voltage controlled oscillator was designed as a local oscillator in a radio transceiver.

The proceeding sections include a literature survey about typical frequency operation, performance parameters and topology types of local oscillators. Finally, as a result of the literature survey, the appropriate topology and technology was chosen for the multi-band operation.

# 2.1 Frequency operations by using Oscillators

The typical application of LO (with a mixer) in the front-end of a typical receiver is downconverting the incoming radio frequency (RF) signal to a lower, intermediate frequency (IF).

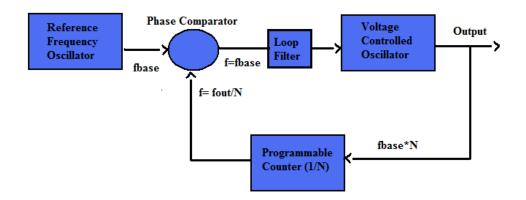

Another usual implementation of LO is PLL (Phase Locked Loop). A typical PLL is composed of a reference frequency oscillator, voltage-controlled oscillator (VCO), a loop filter, a phase detector, and a frequency divider, as shown in Figure 5.

A PLL forces the output frequency to become exactly equal to the input frequency. In order to provide a stable high frequency signal, the reference signal is compared with the divided version of the VCO output. If the divider has value N, then the output frequency will be N times of the input frequency. Furthermore, if the divider value is adjustable, we can generate different LO frequencies by simply changing N. If phase comparator detects a difference between these signals, the following circuits operate for removing the difference. A fixed, low-frequency (~10 MHz) reference oscillator can be used to generate multiple LO frequencies in the low-GHz range. Typically, a crystal oscillator is utilized as the reference oscillator due to its high stability.

Figure 5 Phase-Locked Loop

The output contains noise characteristics of the reference signal, the phase detector, the loop filter, the divider, and the VCO. Out of the loop bandwidth, the output only contains the noise characteristics of the VCO. Therefore, the spectral purity of the VCO affects the phase noise performance of the PLL.

## 2.2 Performance Parameters

The spectral purity, which is usually characterized by phase noise, is the most critical specification when designing a VCO. In many wireless transceivers, the design goal is the minimum power consumption. However, there is a trade-off between power consumption and phase noise. The other specifications are the operating frequency, the stability, the output power. In this section, the affects of each parameter on the oscillation performance were explained.

#### 2.2.1 Phase Noise

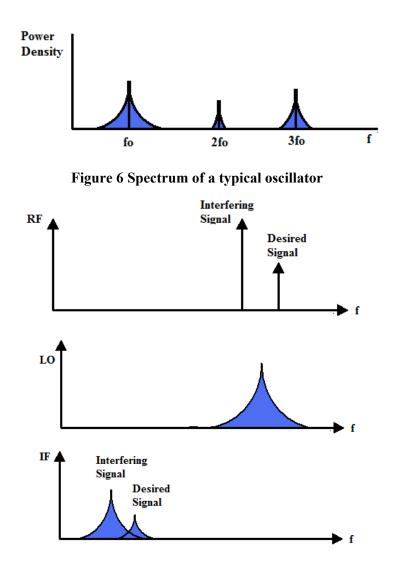

The most important charateristic of an oscillator is its phase noise. The spectral purity is a measurement of the power distribution around the center frequency and its harmonics. Ideally, the spectrum of an oscillator is an impulse located at the desired frequency. However, all practical oscillators have im-perfect spectral purities and so they develop skirts as shown in Figure 6. This is an undesirable power distribution around the oscillation frequency and the harmonics are known as the *phase noise*.

In order to understand the negative effect of phase noise, consider the receiver's front-end. The desired signal is shown in the presence of a stronger signal in an adjacent channel in Figure 7. As shown in the figure, the phase noise of the VCO is modulated onto the stronger signal at IF. This phenomenon reduces the signal-to-noise ratio (SNR) of the desired signal at IF and limits the proximity of the placement of the channels [7]. Similarly, in a transmitter, LO phase noise is modulated onto the desired signal, resulting in unwanted energy being transmitted outside of the desired band.

**Figure 7 SNR degradation**

#### 2.2.2 Power Consumption

An arbitrarily small phase noise can be achieved by simply increasing the bias current, but there are practical limitations such the possible smallest phase noise achievement. Increasing the bias current means much more amplification in gm stage and it also means rise at the VCO's output voltage amplitude. However, any MOS transistor has a maximum voltage that may not be exceeded without permanent damage. Also, in usual applications the n-well in a PMOS device is connected to the power supply. The drain cannot exceed the power supply voltage by more than about 0.6 V because the drain-well diode will be turned on resulting in clipping of the output voltage. As a result, the bias current directly depends on the process. Also, we would like to minimize current consumption of the VCO as much as possible (considering the phase noise trade-off) to maximize battery life of transceiver.

#### 2.2.3 Operating Frequency

The operating frequency is the major issue for Voltage Controlled Oscillator. In section I, the wireless communication standards were given in terms of the frequency band aspects. If VCO is used for a multi-standard application, output oscillation must satisfy all frequency bands that are standardized by the multi-band transceiver block.

A multi-band multi-standard RF frontend for IEEE 802.6a and IEEE 802.11 a/b/g applications have been designed [8]. This design could be a reference for the frequencies cover in VCO in a multi-band RF transceiver. For IEEE 802.11 b/g, and WCS and MMDS bands of 802.16a that share nearly same frequency bands aroud 2.4 GHz, the first local oscillator was located between 3.45 to 4.05 GHz. Moreover, IEEE 802.11b and UNII band of IEEE 802.16a was covered by providing 3.85-4.37 frequency band from VCO.

Another example could be given from a multi-band dual-conversion zero IF Receiver that was designed for IEEE 802.11a/b/g standards. The bands required to be covered are 2.4-2.5 GHz, 5.15-5.35 GHz and 5.725-5.825 GHz. For this operation the frequency plan of the multi-band WLAN receiver is presented in Table 2 [9].

| Band (GHz)    | LO (GHz) | IF(MHz)   | Image (GHz) |

|---------------|----------|-----------|-------------|

| 2.4 - 2.5     | 2.9      | 400 - 500 | 3.3 - 3.4   |

| 5.15 - 5.35   | 4.8      | 350 - 550 | 4.25 - 4.45 |

| 5.725 - 5.825 | 5.275    | 450 - 550 | 4.725-4.825 |

#### Table 2 The frequency plan of multi-band WLAN receiver

#### 2.2.4 Stability

The stability is another performance parameter that affects the peripheral circuitry of the oscillator. In a transceiver block, if we have unstable frequency, we cannot get the desired RF or IF signal at the output of the mixer. From the PLL perspective, a stable and fixed signal at the output will not be guaranteed at the presence of an unstable VCO.

### 2.2.5 Output power

In typical applications, oscillators always drive circuits such as mixer in transceiver and divider in PLL. So, the output power becomes an important parameter when designing the whole circuit.

# 2.3 Topology and Technology

The main concern while choosing RF technologies for wide ranging communication applications is optimization for performance and or cost. This leads to the exploitation of Sibased technologies when cost and integration are the major concerns. The convenience of integration of high performance HBTs with the state-of –art CMOS and passive elements is the main advantage of SiGe BiCMOS technology against the other technologies [10].

As a consequence of second and third generation wireless systems, the multi-band and multistandard mobile communication systems are required. The recent transceiver components must also cover the frequency band of various systems. With the introduction of the Ultra Wide Band (UWB), the communication standards operate in the frequency ranges up to 10 GHz. As a result, the demand for multi-standard RF transceivers which put various wireless and cordless phone standards together in one single structure is increased. So, the narrowband voltage controlled oscillators, which are one of the most attractive blocks among the RF building blocks, were replaced with single low noise wideband VCO. The demand for multistandard RF transceivers imposes a key role to reconfigurable wideband VCO operation with low-power and low-phase noise characteristics [11-13].

The Voltage Controlled Oscillators (VCOs) are one of the essential building blocks of modern RF transceiver architectures. The LC-tank VCO topology is the most popular implementation

among others due to its higher spectral purity which is mentioned in section 3.2.1 in details. Below, various types of oscillators and a comparison between their performances will be presented.

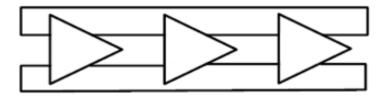

### 2.3.1 Ring Oscillator

Basically, the odd number of the cascaded invertors in a feedback loop constructs a ring oscillator. The oscillation frequency is  $f_{osc} = \frac{1}{2T_d M}$  which is related to the delay and number of each stage ( $T_d$  is the delay of each stage and M is the number of stages).

Figure 8 shows a three-stage differential ring oscillator. The ring oscillators are not faster and also cover lesser area relative to the other types of oscillators. However, the main disadvantages of ring oscillators are the lower operating frequency, poor spectral purity (Low pass behavior due to lacking inductors) and higher power consumption.

**Figure 8 Ring Oscillator**

### 2.3.2 Relaxation Oscillator

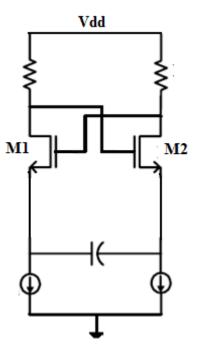

The relaxation oscillators, presented in Figure 9 are resonatorless oscillators. The ring oscillators could be given as the example of relaxation oscillators. In the topology, the positive feedback transistors (M1 and M2) enable the oscillation in this topology.

**Figure 9 Relaxation Oscillator**

The major advantage of the resonatorless oscillators is lack of large passive devices such as inductors and capacitors. This advantage makes relaxation oscillators small-sized and suitable for integration. However, the lacking of passive devices will cause no filtering of noise at the output signal. So, resonatorless circuits will suffer from phase noise performance, and this topology is not suitable for our application.

#### 2.3.3 LC Oscillators

In order to get a better phase noise, the resonators have been added to the feedback network. A very simple resonator is an LC tank. The oscillator that is shown in Figure 10 resonates at frequency  $\omega_c = \frac{1}{\sqrt{LC}}$ .

**Figure 10 Parallel LC resonator**

In theory, the impedances of the inductor and capacitor are equal with opposite signs at resonance frequency. The formula of the ideal circuit is  $\left|\frac{1}{j\omega_c c}\right| = |j\omega_c L|$ , which makes the impedance of the tank equal to infinite at this frequency. However in practice both the inductor and capacitor suffer from resistive components. Additionally,  $Q_c$  and  $Q_L$  are the quality factors of capacitor and inductor, and they are defined as  $\frac{1}{\omega R_s C}$  and  $\frac{\omega L}{R_s}$ . Generally, the quality factors of the capacitors are much higher than the quality factors of the inductor of the tank equal resistance of the tank,  $R_p$ , is mainly determined by the inductor ( $R_p \approx R_{p_I}$ ).

According to the model in Figure 11, the impedance of the circuit could be given as the paralleled impedance of the inductor, capacitor and resistor. At resonance, impedance of the inductance and capacitance are equal and the voltage gain equals  $+g_m R_p$ . It should be noted that Barkhausen's criteria [7] has to be fulfilled to start the oscillation.

Figure 11 Impedance of the Tank

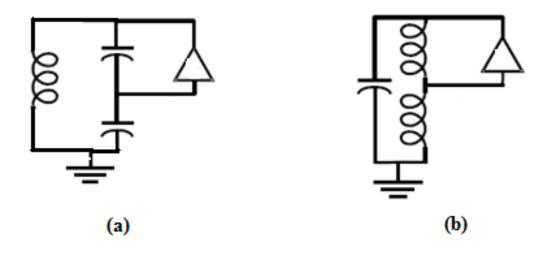

#### **Topology** Types

There are different approaches in designing an LC oscillator. The most common methods are Colpitts oscillator, Hartley oscillator, and Cross-Coupled oscillator. Colpitts and Hartley, shown in Figure 12, use one transistor to provide sufficient gain and phase shift. The frequency of oscillation in both topologies is  $\omega_C = \frac{1}{\sqrt{LeqCeq}}$ .

Figure 12 (a) Colpitts and (b) Hartley Oscillators

The Colpitts oscillator is known by its using a tapped capacitor and amplifier to form the feedback. Apart from Colpitts, the Hartley oscillator uses tapped inductor to form the loop. Because of using only one inductor, the Colpitts oscillator is smaller and more suitable for integrated circuits than the Hartley oscillators. The gain equation for colpitts oscillator is driven from small signal analysis;

$$g_m R_P = \frac{(C_1 + C_2)^2}{C_1 C_2} \tag{1}$$

where  $g_m$  is the gain of the amplifier (generally MOSFET transistor) and  $R_p$  is loss of the LC tank. The minimum required gain occurs when  $\frac{C_1}{C_2} = 1$ , resulting the following expression to fulfill the Barkhausen's criteria;

$$g_m R_P \ge 4 \tag{2}$$

Another approach in designing an LC oscillator is Cross-Coupled oscillator, which is divided into three different types in

Figure 13, PMOS-Only, NMOS-Only and Complementary Cross-Coupled.

Figure 13 Cross-coupled Oscillators (a) NMOS only (b)PMOS only (c) Complementary

In [7] it is presented that the total phase shift around the loop is zero at resonance, because each stage provides a zero frequency dependant phase shift, resulting in the following limitation on gain to start the oscillation:

$$g_{m1}R_Pg_{m2}R_P \ge 1 \longrightarrow (g_mR_p)^2 \ge 1$$

(3)

When choosing between Colpitts oscillator and Cross-Coupled oscillator, it should be noted that Colpitts suffer from two drawbacks; Firstly, with regards to equations (2) and (3) it can be seen that the gain has to be 4 times higher in Colpitts with identical LC tank, resulting with either larger transistor size or higher biasing current and as a consequence of this higher power consumption. Secondly, there is no differential output in Colpitts oscillators. Here, it should be mentioned here that maximum noise rejection is feasible in fully differential oscillator compared to the one in single mode oscillator, and the level of SNR (Signal to Noise Ratio) is higher in differential circuit. Consequently, a fully differential model has been chosen for this project.

## **CHAPTER 3 VCO DESIGN**

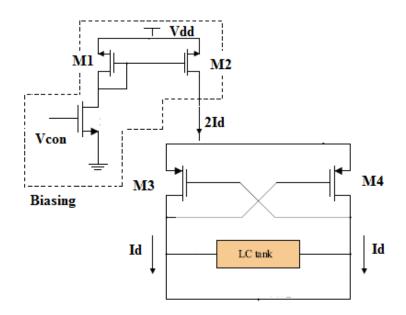

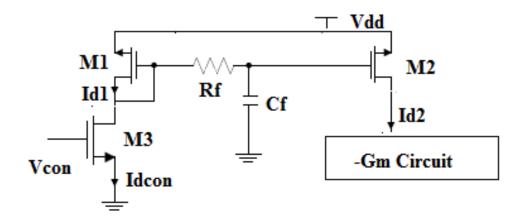

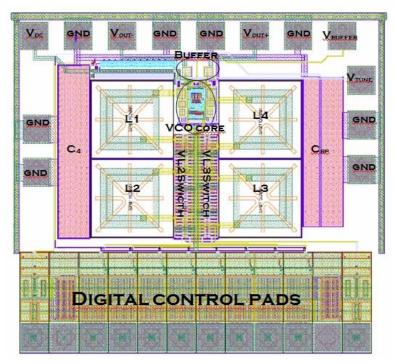

In this chapter, a 2.2-5.7 GHz Multi-band Differential LC Voltage Controlled Oscillator (VCO) for the Multi-band Multi-standard is presented. It was designed for a multi-band transceiver architecture that utilizes a controllable VCO which operates at different frequencies in a wide frequency range. The advantages of Multi-band Differential LC VCO topology are: 1) 5 controllable frequency bands, which are utilized by multi-standard; by the help of switching inductor and capacitor method 2) the provision of low phase noise by using all PMOS current sources topology which has minimum intrinsic and extrinsic sources of noise. Five frequency bands, which are obtained from wireless communication standards in Section I, are the multi-band view of the design. Additionally, another goal is achieving multiband operation with low phase noise. The circuit is designed with AMS 0.35µm SiGe BiCMOS process that includes high-speed SiGe Heterojunction Bipolar Transistors (HBTs). 0.35 um Sige BiCMOS is fairly old technology. However, in this project, technology is not major concern. Figure of merit of the project is comparable with the previous VCO designs that are used newer technology. The advantage of this project is covering wider frequency band than the other VCOs. This is succeed by adding a novel switch approach to the circuit which was defined in this chapter.

#### 3.1 Topology and Design procedure

### VCO Circuit Design Review

Various material systems and transistor technologies such as InGaP/GaAs HBT, SiGe BiCMOS, Si CMOS, and Silicon-on-insulator (SOI) CMOS can be used to meet the specification of multi-communication standards mentioned in Section I.

A CMOS dual band Voltage Controlled Oscillators realized with 0.18µm CMOS technology operates at 2.15 GHz - 2.756 GHz and 4.756 GHz - 4.996 GHz [47]. This VCO demonstrates a phase noise of -121.45 and -118.4 dBc/Hz at 1MHz offset from the frequencies of 2.4 and 4.86 GHz. The tuning range is relatively low in comparison with 5-6GHz coverage of the standard. Moreover, the design with two different LC tanks providing dual-band oscillation is not a cost-effective design when compared to single LC tank topology.

A remarkable work performed with 0.13µm SOI CMOS demonstrates a 3.065-5.612 GHz coverage with -114 dBc/Hz phase noise at 1 MHz offset while drawing 2mA from 1V supply. This performance is succeeded by taking the advantage of SOI structure and eliminating the adverse effect of Accumulation mode varactors (AMOS) using band switching topology [23].

The Ultra-wide band voltage controlled oscillator (VCO) have been designed by using 0.35 um SiGe BiCMOS technology [45]. The VCO provides an oscillation band between 2.67 to 4.37 GHz. Novel resonant circuit, which consists of three NMOS varactor pairs, p-n diodes, two spiral inductors and a control unit, allows the VCO to have a wideband tuning range. At a collector voltage of 4.0 V, the DC current consumption of the VCO is 5.8 mA. A phase noise of -111 dBc/Hz at 1 MHz offset at an oscillation frequency of 4.37 GHz was ensured.

All-PMOS wideband VCO having Automatic Amplitude controller for multi-band multistandard radios was fabricated by using improved capacitor switching method in TSMC 0.18 µm CMOS technology. The frequency band and tuning voltage are 2.78-3.78 GHz and 0-1.8 V, respectively. The measured phase noises at 1 MHz from carrier frequencies of 2.83, 3.24, and 3.77 GHz are -126.5, -125.0 and -122.7 dBc/Hz, respectively. With 1.8 V voltage supply, the current flowing into the VCO core varies between 4.9 mA to 5.7 mA[47].

#### VCO Design in this work

The ring oscillators [17], multivibrator oscillators [6] and Resonator (LC) based oscillators [19] can be used as an RF VCO topology. The Multi-vibrator oscillators are utilized for very high tuning ranges. The ring oscillator topology that is composed of an odd number of inverter stages has also high tuning range. However, these oscillators usually have less spectral purity than does their LC counterparts. The LC based oscillators are the most appropriate topology for low phase noise designs.

In a practical circuit, the oscillators will die away unless feedback is added in order to sustain the oscillation. The feedback (or negative resistance) is usually provided by tapped inductor and amplifier (Hartley oscillator), two amplifiers ( $-G_m$  oscillators) or tapped capacitor and amplifiers (Collpitts oscillator). Due to the difficulties in IC tapped-inductor implementations, Hartley topology is usually not prefered. Although there are some successful realizations of Collpitts configurations, -  $G_m$  topology generally results in higher performance wireless applications [6].

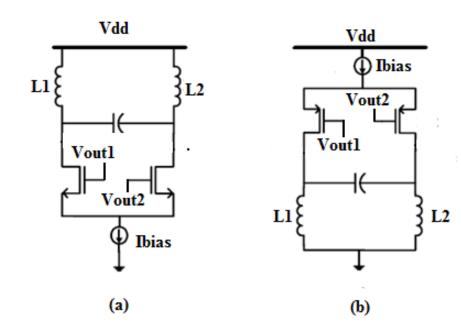

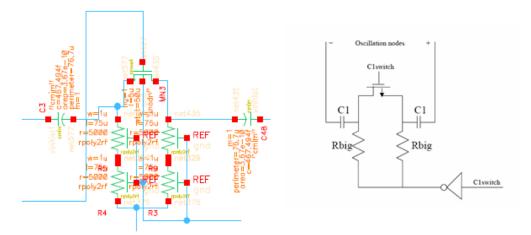

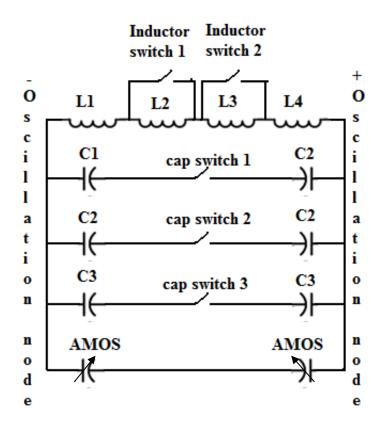

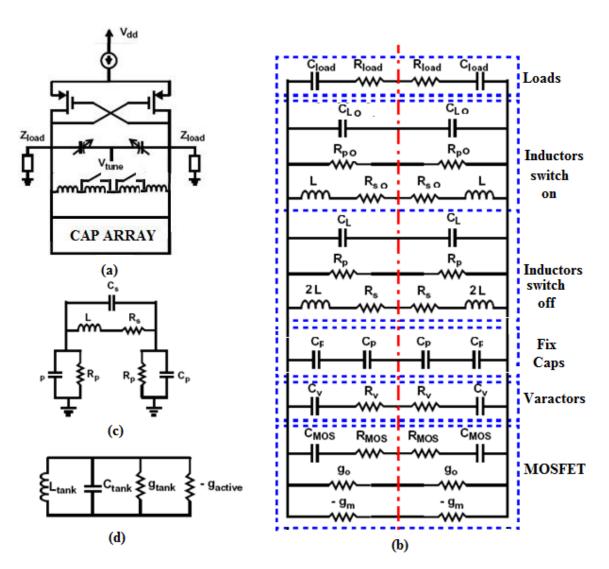

The differential LC -  $G_m$  configuration shown in Figure 14 is chosen for Multi-band VCO because of meeting the phase noise requirements of the communication standards and topological advantages. In an RF transceiver block, VCO usually drives the mixer which is composed of differential Gilbert Cell. Moreover, differential topology enhances the output power in exchange with the increased power consumption, the larger chip area and the increased complexity. Finally, differential LC  $-G_m$  configuration provides a higher common-mode rejection ratio (CMRR), thus higher linearity [20].

Figure 14 Multi-band VCO schematic including LC switched resonators

The NMOS, PMOS, or complementary cross-coupled designs can be used as LC VCO circuit topologies for wideband VCOs. Since it consumes less current to compensate losses in the tank and has lower upconversion factor of flicker noise, a complementary cross-coupled VCO is quite attractive. However, it reduces the voltage headroom of the current source, and introduces more parasitic capacitance as well as noise sources to the tank [21]. Thus, a non-complementary topology is used for the thesis project.

All-PMOS VCO topology is the most appropriate in terms of low phase noise performance because the topology has minimum intrinsic and extrinsic sources of noise [24]. The Cross-Coupled has two more transistors compared to PMOS Only, resulting in almost five times more parasitic capacitance and hence degradation in tuning range and the introduction of more noise sources. The reason why an all-PMOS VCO topology is chosen is explained in detail in section 3.4.

# 3.2 LC Tank Design

The method which is used to design the capacitive and inductive part of the LC-tank, was based on information about the desired VCO characteristics in section I and II. In order to cover the desired bands, VCO tank is divided into three blocks as switched inductor, switched capacitance and fine tuning circuitry. The detailed information is given about these three parts in the following sections and also all sections define why the designed topology or type of component was chosen.

#### 3.2.1 Tank inductance

The low Q values of inductors implemented in BiCMOS with RF operation are the drawbacks of VCO design. The lowest Q value means that the loss in the LC tank was mainly caused by the inductor. Therefore, the quality factor of the inductor is the dominant influence on the phase noise performance of the VCO. The selection of the inductor could be seen as a starting point of VCO design because of limited library of AMS. This chapter studies necessary considerations for utilization of inductors implemented in BiCMOS. Finally, the inductor that will be used in actual VCO design is presented.

Previously, the discrete components and usually surface-mounted devices were utilized in the circuit. Because of cost and size issues that approach is unsuitable today. Based on the fact that monolithic on-chip inductors are now widely utilized in radio frequency integrated circuit design. They are typically used in resonators such as in VCO or matching networks. In both applications, the critical parameter for the inductors is the quality factor because it improves circuit performance in terms of efficiency, insertion loss, gain and noise figures. The metal and substrate losses are the reasons for low Q-value inductors in BiCMOS technology.

The integrated spiral inductors are the square, circular and octagonal shapes, as shown in Figure 15. The Q-value and the utilization of minimum die area are the selection criteria for a specific type of geometry. An obvious and efficient inductor structure is the circular shape that was based on a smooth continuous circular conductor. Therefore the circular shape has

minimum die area for a given inductance and provides the best area/length relationship compared to the other inductor shapes. The trace length determines the series resistance while the area determines the inductance. However, the process technologies set limitations regarding inductor shapes because of limitations in the masking process.

Figure 15 Inductor Geometries ; (a)square (b) octagonal, (c) circular

The differential inductors are preferred such as those depicted in Figure 15 when designing cross-coupled VCOs. This symmetry enables the cross-coupled VCO to be completely symmetric and thereby ensures that a virtual ground exists at the plane of symmetry. In the designed case where the VCO is an PMOS only type, a center tap is added to the differential inductor thereby enabling DC biasing through the inductor.

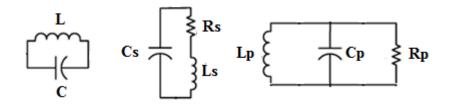

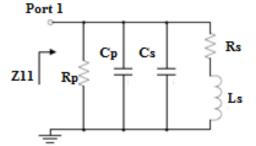

#### **Inductor Model**

The differential and single-ended inductors can be shown by an equivalent circuit in terms of a two-port  $\pi$ -network consisting of lumped passive components. The equivalent circuit represents different assumptions and correspondingly exhibits different complexity. The equivalent lumped model used for modeling is depicted in Figure 16.

Figure 16 Inductor Modeling: Lumped -model of the two port spiral inductor

$R_{\rm s}$ : The series conductor loss is represented by the series resistance  $R_{\rm s}$ .

$C_{\rm c}$  ( $C_{\rm p}$ ): The capacitive coupling between the turns and the coupling originating from over/underpass

*L*<sub>s</sub>: Self and mutual inductances.

$C_{\text{ox}}$ : The oxide capacitance found between the inductor and the silicon substrate.

$R_{\rm si:}$  The resistance of the conductive silicon substrate

$C_{\rm si:}$  The parasitic capacitance found in the substrate.

If the inductor has to perform single-ended operation as in the VCO, the port-2 of the equivalent  $\pi$ -model shown in Figure 16 must be connected to ground as Figure 17 thus obtaining the definition of the single-ended Q-factor [25]:

$$Q_{L,11} = \frac{imag(Z_{11})}{real(Z_{11})} = \frac{imag(\frac{1}{Y_{11}})}{real(\frac{1}{Y_{11}})}$$

(4)

Figure 17 Equivalent circuit of one port grounded inductor

The same principle applies for derivation of the single-ended inductance:

$$L_{11} = \frac{imag(Z_{11})}{2\pi f} = \frac{imag(\frac{1}{Y_{11}})}{2\pi f}$$

(5)

The quality factor of the overall tank circuit is determined from the parasitic conductance of capacitance and inductance. Since the accumulation mode MOS varactors have relatively

higher Q values than on-chip inductors, inductor Q is the main determining factor of the overall Q of the tank circuit.

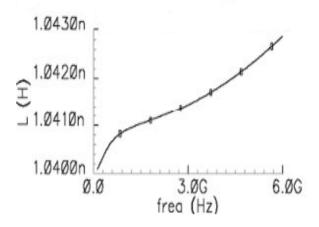

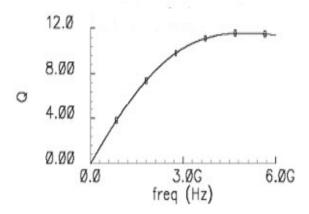

The inductors and capacitors in LC tank are simulated and analyzed individually. The AMS library inductor is used as inductor of the LC tank; its characteristics can be observed in Figure 18 and Figure 19. From the Figure, the inductor has an inductance of 1.04nH with a quality factor varying between 8.7 at 2.4 GHz to 11.8 at 5 GHz.

Figure 18 Inductance value of AMS library inductor.

Figure 19 Quality factor of the AMS Library Inductor

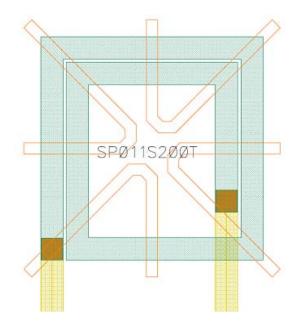

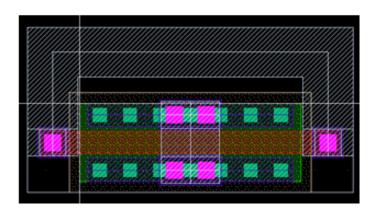

The layout of the square-shaped AMS Library inductor is shown in Figure 20 Inductor Layout. The top metal layer is utilized for the traces of the inductor. Each inductor has an area of  $287.4\mu m \approx 0.076 mm^2$ .

**Figure 20 Inductor Layout**

#### 3.2.2 Tank Capacitance

In the BiCMOS process, the capacitors that use Metal-insulator-metal (MIM) capacitors [25,26], MOSFET gate oxide and Poly-insulator-gate (Double Poly) capacitors are the available capacitors. The MOS capacitors and junction capacitors that have higher capacitance density are not suitable for these applications because of their non-linearity that means their capacitance value changes with applied voltage. Also their values depend on temperature [25]. Additionally, MOS capacitors have a very poor quality factor due to the high series resistance. To achieve a better linearity and quality factor, the parallel plate metal-to-metal capacitors can be chosen. However, as a result of large vertical spacing between the plates means low capacitance value. The metal finger capacitors could be seen as a solution to increase the capacitance density of parallel plate capacitors.

The double poly capacitor is a well-established component but it suffers from the limited RF capability in multi-GHz range. Due to the the resistive losses in the plates and contacts and parasitic capacitance between passive component and the loss silicon substrate. The

limitations in the quality factor are naturally reduced for the MIM capacitor, where the bottom plate is positioned further from the substrate (Figure 21) and metal plates are inherently low in resistance. The MIM capacitors have much better voltage linearity, lower series resistance, much lower parasitic capacitance, and excellent matching. Moreover, the fabrication process of the MIM capacitors has less heat which is important for sub-micron transistors.

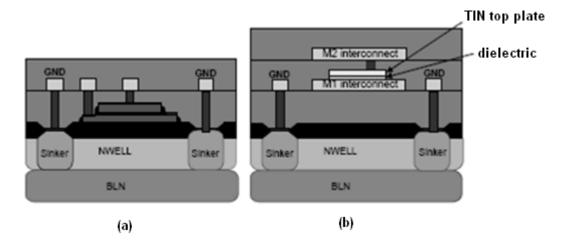

Figure 21 Cross Sections of (a)Double Poly capacitor (b) the MIM capacitor[27]

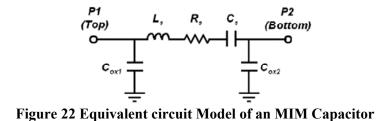

MIM capacitor was chosen for this design because of its advantages for the RF applications discussed above. The equivalent circuit model for an MIM capacitor is shown in Figure 22. In this circuit,  $C_s$  is the main element of the capacitor,  $R_s$  and  $L_s$  are the parasitics existing in the electrodes, and  $C_{ox1}$  and  $C_{ox2}$  are the parasitics that represent the capacitance to ground due to the bottom and the top plate metal, respectively.

A remarkable work regarding two-port, parallel plate, square structure MIM capacitors [28] helps to form an opinion about the parasitics of MIM capacitances. In this work, MIM capacitors that have different sizes (The width of the edge per side of the squares is 10, 15, 25 and 50  $\mu$ m) are utilized to describe the behavior of MIM capacitors for various device

geometries. After performing the measurements and extractions for each device, they drive the scaling rules as shown in Table 3 [29].

|                  |            | Scaling Rule                       |

|------------------|------------|------------------------------------|

| R <sub>s</sub>   | $[\Omega]$ | $14.52 / L_{MIM} + 0.91$           |

| Ls               | [pH]       | 404.93 / L <sub>MIM</sub> + 132.82 |

| Cs               | [pF]       | $0.00106^{*}(L_{MIM} + 0.388)^{2}$ |

| C <sub>ox1</sub> | [fF]       | 7.5                                |

| C <sub>ox2</sub> | [fF]       | $0.00220*(L_{MIM}+55.893)^2$       |

Table 3 Scaling Rules for a square MIM capacitor with  $L_{top}$  in the range of 10~50  $\mu$ m. L<sub>MIM</sub> is the edge per side of the MIM layer in  $\mu$ m

## 3.2.3 Switch Method

The total quality factor of the resonance tank limits the phase noise performance of an oscillator, whereas the capacitance ratio is important as it limits the achievable tuning range.

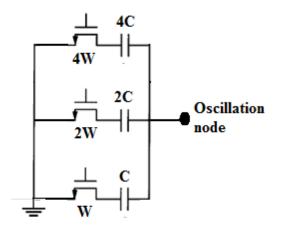

The traditional switch circuit implementation is presented at Figure 23. When the transistor is at ON state, there would be no DC current flowing through the capacitor and thereby the transistor. The transistor's drain-source DC voltage equals zero, therefore, MOSFET operates in the triode region [7].

The ON resistance of the transistor can be calculated by using a simple transistor model,

$$r_{ds0} = \frac{1}{g_{ds0}}$$

$g_{ds0} = \mu . C_{ox.} \frac{W}{L} . (V_{gs} - V_t)$  (6)

where  $\mu$ ;  $C_{ox}$ ; W, and L are the mobility, gate oxide capacitance per area, width, and length of the transistor.

Figure 23 Binary weighted array of switched capacitors

The quality factor of the resulting series RC-link is, thus, equals to

$$Q = \frac{1}{2\pi f C r_{dso}} \tag{7}$$

In order to provide a high quality factor, the transistor dimensions (width and length) can be changed by designers. As can be seen at (6) equation, the minimum length should be used for best performance. The width will be determined by compromising between tuning range and quality factor. At the OFF state, the conductance  $g_{ds0}$  will be negligibly small. The  $C_{gd}$  and  $C_{db}$ capacitances (neglected at the ON state) dominate the transistor's impedance. There is a pn junction formed by the p-doped substrate and the n-doped drain between drain and bulk, whereas the gate-drain capacitance is due to the overlap between gateand drain.

# $C_{off} = Capacitance \ value \ of \ switched \ capacitor + drain \ capacitance$

When the transistor is OFF,  $C_{off}$ , the capacitance of the tuning circuit seen by the oscillator, is the series connection of the capacitor being switched OFF and the drain capacitance  $C_d$  of the transistor ( $C_d = C_{db} + C_{gd}$ ). The drain capacitance is related with the width of the transistor. A wide transistor thus increases the quality factor but reduces the tuning range, leading to a compromise. Since (7) contains the frequency in the denominator, obtaining a good compromise is difficult at higher frequencies. The following equations show that an achievable performance can be related to the ratio of the transistor transition frequency  $f_t$  to the operating frequency

$$f_t = \frac{g_m}{2\pi C_g} \tag{8}$$

$$\frac{\Delta C}{C_{OFF}} = \frac{C_{ON} - C_{OFF}}{C_{OFF}} = \frac{C - \frac{C \cdot C_d}{C + C_d}}{\frac{C \cdot C_d}{C + C_d}} = \frac{C(C + C_d) - C \cdot C_d}{C \cdot C_d} = \frac{C}{C_d}$$

(9)

$$Q.\frac{\Delta C}{C_{OFF}} = \frac{1}{2\pi f r_{ds0}C_d} = \frac{g_m}{2\pi f C_g} \cdot \frac{1}{g_m r_{ds0}} \cdot \frac{C_g}{C_d}$$

$$=\frac{f_t}{f} \cdot \frac{g_{ds0}}{g_m} \cdot \frac{c_g}{c_d} \tag{10}$$

where gm: the transconductance of the transistor in saturation

$\Delta C$ : is the difference in capacitance between the ON and OFF state.

The last expression is used as a performance measure. In modern BiCMOS process,  $C_g/C_d$  is approximately equal to unity, but  $g_{ds0}/g_m$  which is equal to unity in the long channel low electric field situation, can be substantially larger for short channel devices with high gate voltages [7]. In such a situation, disregarding this term in (10) would lead to an underestimation of the achievable performance.

The novel idea here is to use just one transistor as shown in Figure 24 instead of two transistors for switching the same capacitance value in whole circuit. The performance of the switch circuit could be seen from (8), (9) and (10) equations. When a branch is ON it will contain two  $r_{ds0}$  in series going from one side of the differential circuit to the other. So this limits the quality factor. With the improved differential switched-tuning circuit the quality factor of the switch circuit will be doubled while keeping the transistor sizes the same and switching the same fixed capacitance. The purpose of the big resistors in the circuit is to ensure that the transistor is OFF at all times in an OFF state and obtain the maximum gate to

source (and drain) voltage in the ON state. Moreover, the other purpose of giving Vdd to drain and source at OFF state is reducing and getting a better control of reverse biased drainbulk capacitance [15].

Figure 24 Improved differential switched-tuning circuit

The multi-band tuning concept in a wideband range has been attempted by a utilizing switched inductor with a poor phase noise outcome [30]. The switched inductor concept that is shown in Figure 25 is used for increasing the tuning range and for achieving low phase noise. According to the transistors ON and OFF states, the inductance that is seen between ports 1 and 2 is changed. At the OFF state, the total inductance is approximately the sum of the L1 and L2. When transistor is on, the branch is shorted and inductance seen from port 1 is decreased to L1. Also, the capacitance seen from L1 side is reduced because of shorting the transistor capacitances and the capacitances associated with L1 (partially) and L2 to the ground by a low resistance path. By the help of switching method, the circuit has the ability of simultaneously decreasing inductance and capacitance [31]. This tuning ability provides circuit flexibility for trade off between the phase noise and power consumption [32] compared to the case of using only switched capacitors [33].

Figure 25 Schematic of switched resonator

#### 3.2.4 Varactor

For the multi-standard operation, a VCO needs to cover a wide frequency range. Typically, in the LC-oscillators, the varactors are used for continuous frequency tuning. However, high tuning sensitivity means high sensitivity to noise and disturbances on the control voltage. Moreover, large metal–oxide-semiconductor (MOS) varactors convert harmless amplitude noise into harmful phase noise. In this work, an improved switching inductor and capacitance technique have been used as a controller concept of a LC tank to cover a wide frequency range and reduce the noise problem.

In the BiCMOS and CMOS technologies, the tuning range is also a critical performance parameter in designing VCO. The accumulation mode MOS varactors are commonly preferred for tuning owing to the fact that p-n junction varactors and inversion mode MOS varactors have limited tuning range. The AMOS varactors have the highest tuning range among other varactors types. Moreover, with AMOS varactors, VCO can be tuned more linearly [15].

This chapter presents an overview on different varactors configurations suitable for BiCMOS implementation. Furthermore, the AMOS varactor, which was chosen for this application as appropriate, was researched considering its large signal analysis and subcircuit model.

#### i. Varactor Types

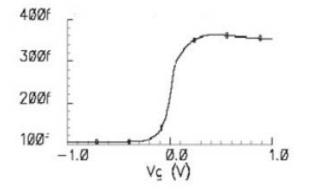

The minimum and maximum capacitances and Q-value are the main specifications of a varactor. Because of dominant influence on the tuning linearity of the VCO frequency, the linearity of the tuning curve of varactors shown in Figure 26 is important.

The output frequency is expressed by:  $\mathbf{f}_{out} = \mathbf{f}_o + \mathbf{K}_{vco} \cdot \mathbf{V}_{const}$ , where  $\mathbf{K}_{vco}(voltage gain)$  has the unit of Hz/V. Ideally, as shown in Figure 26, the slope of the line is constant. In practical, the gains of the varactors are not constant. The main differences between various types of varactors are found at their C-V characteristics and Q-values. The differences will be clear in the following subsections, where different varactor types suitable for BiCMOS implementation are introduced.

Figure 26 Ideal Frequency Tuning Curve

#### **PN-JUNCTION VARACTOR**

The first option for the realization of varactor tuning elements in SiGe BiCMOS process is pn-junction varactors. The varactor is obtained from p+/n- well junction also known as diode. A cross section of a junction capacitance is sketched in Figure 27.

Pn junction varactor operation was achieved by applying a reverse bias voltage,  $V_{R}$ , across the anode (A) and cathode (C) terminals. The reversed bias voltage determines the width of depletion region, thereby the junction capacitance. Thus, the varactor capacitance value is related with the depletion region between the p+ diffusion and the n-well. A p /n-well structure can typically have a quality factor of 20 or better. The drawback of this varactor approach is that the diode can be forward biased if the signal voltage is high so that the diode enters the breakdown region. As a consequence, the varactor will be short circuited and will short circuit the two VCO nodes, thereby blocking the oscillation.

Figure 27 Cross section of p<sup>+</sup>/n-well junction capacitance

#### **MOS VARACTOR**

By connecting drain, source and bulk (B,S,D) together, a MOS capacitor of whose capacitance value changes with  $V_{bg}$  could be realized. For a pMOS capacitor, an inversion channel with mobile holes builds up for  $V_{bg} > |V_t|$ . The condition  $V_{bg} >> |V_t|$  guarantees that the MOS capacitor works in the strong inversion region. In this region, the MOS device shows a transistors behavior. The MOS device enters the accumulation region for  $V_g > V_b$  where the voltage at the interface between gate oxide and semiconductor is positive and high enough to allow electrons to move freely.

The value of the MOS capacitance  $C_{mos}$  is;

$$C_{ox} = \frac{\varepsilon_{ox} \cdot S}{t_{ox}}$$

(S: transistor channel,  $t_{ox}$ : oxide thickness region)

in both strong and accumulation region.

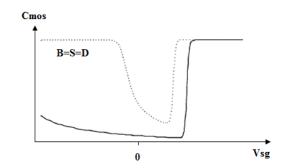

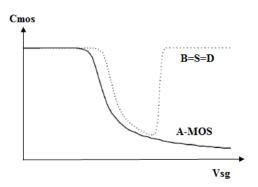

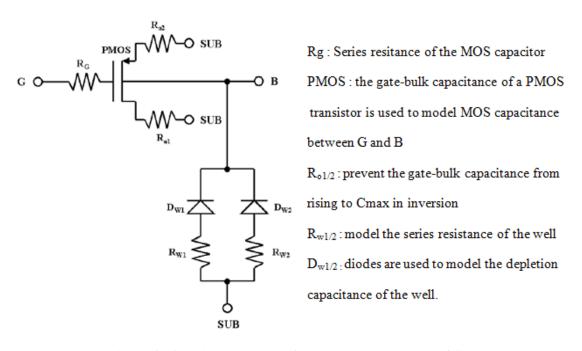

The moderate inversion, the weak inversion, and the depletion are three more regions that change with intermediatevalues of  $V_{bg}$  [34]. When passing from the accumulation region to the depletion region the capacitance will drop because of the number of major carriers. After the depletion region, Vg will be less than Vb with a difference of  $|V_t|$ . So the inversion layer starts to be obtained under the gate oxide. As a result of the decreased gate voltage, capacitance will rise sharply because of the strong inversion layer. The characteristics for the PMOS capacitor are shown in Figure 28.

Figure 28 shows the  $C_{mos}$ – $V_{bg}$  characteristics for a very small signal superimposed on the bias voltage. If the signal at the transistor gate (for MOS capacitances) is large, then the instantaneous value of capacitance changes throughout the signal period. The designer should not allow the capacitance changing of the LC tank (non-monotonicity). An almost monotonic function for  $C_{mos}$  can be obtained if the transistor does not enter the accumulation region for a wide range of values of  $V_{g}$ .

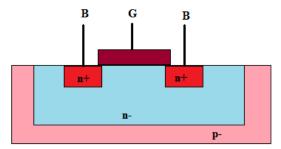

The monotonic function is obtained by breaking the connection between D-S and B, and giving the highest DC-voltage available in the circuit ( $V_{dd}$ ) to the Bulk (Inversion MOS capacitor, Figure 29). Figure 30 shows the comparison between the typical  $C_{mos}$ - $V_{sg}$

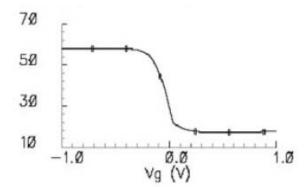

Figure 28 Typical tuning characteristics for the PMOS capacitor with  $B \equiv S \equiv D$

characteristics of pMOS capacitors and B=S=D capacitor. It can be seen that the tuning range of the IMOS capacitor is much wider than that of the previous capacitor, since the former capacitor is working in the strong, moderate, or weak inversion region only, and never enters the accumulation region.

Figure 29 Charge carrier path for the IMOS capacitor

Figure 30 Typical tuning characteristics for the inversion mode varactor

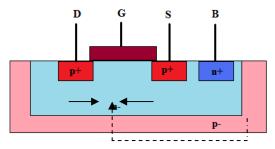

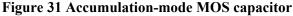

The rationale of obtaining an AMOS (accumulation-mode MOS) type capacitor is to ensure that the formation of the strong, weak, and moderate inversion regions is inhibited (which means the suppression of any injection of holes in the MOS channel). The structure, in turn, can be accomplished with the removal of the D–S diffusions ( $p^+$ -doped) from the MOS device (since we are dealing with circuits working at radio frequencies, we do not need worrying about thermal generation of hole-electron pairs). Implementation of the bulk contacts ( $n^+$ ) in the left by D–S is required, as shown in Figure 31, for minimizing the parasitic n-well resistance of the device. The tuning characteristics of the A-MOS capacitor and also comparison with the B=S=D capacitor is shown in Figure 32.

In order to chose a suitable varactor type for VCO, research on VCO performance has been done [28]. Three different varactors (tuned by a diode varactor, an I-MOS varactor, and an A-MOS varactor, respectively) were utilized in VCO in order to obtain the tuning range and the center frequency. All varactors were designed for maximum Q (i.e., the lengths of the devices are the minimum lengths allowed by the process). Three important parameters were taken into account for comparing with the VCOs such as minimum current consumption, phase noise and tuning range. The minimum current consumption for oscillation measurement gives a rough indication of the (relative) parasitic resistance in the LC-tank. Also phase noise measurement is an important indication for comparison while the other parameters are equal [35].

Figure 32 Typical tuning characteristics for the accumulation mode varactor

The measurement results given at Table 4 and 5, show that the performances of both MOS varactor VCO's are superior to that of the diode varactor VCO [28]. In particular, the accumulation-mode MOS varactor VCO clearly displays the lowest power consumption and the lowest phase noise at large offset frequencies from the carrier.

| Varactor | f <sub>L</sub> -f <sub>H</sub><br>(Ghz) | f <sub>C</sub><br>(GHz) | Tuning<br>Range |

|----------|-----------------------------------------|-------------------------|-----------------|

| Diode    | 1.73-1.93                               | 1.83                    | 10.9%           |

| I-MOS    | 1.71-1.91                               | 1.81                    | 11.0%           |

| A-MOS    | 1.70-1.89                               | 1.80                    | 10.6%           |

**Table 4 Frequency Behavior of the VCOs**

Minimum current consumption for all varactor types

A-MOS: 0.87 mA  $< I_{dd} < 0.99 mA$ Diode: 1.80 mA  $< I_{dd} < 2.44 mA$ I-MOS: 1.45 mA  $< I_{dd} < 1.65 mA$

| Varactor | I <sub>dd</sub><br>(mA) | Phase noise<br>100 kHz, 600 kHz, 3Mhz<br>Offset from carrier (dBc /Hz) |

|----------|-------------------------|------------------------------------------------------------------------|

| Diode    | 4.5                     | -100, -116,-130                                                        |

| I-MOS    | 3.8                     | -100, -117, -132                                                       |

| A-MOS    | 2.7                     | -101, -121, -137                                                       |

Table 5 Phase Noise Behavior of the VCOs

#### ii. Large signal analysis of MOS Varactors in -Gm LC VCOs

The specific MOS varactor topologies resulting from the connections and their corresponding C–V characteristics are detailed in previous section. It should be added that there were no AC signal analysis while defining the characteristics. When varactors are utilized in VCO tank circuit, there would be large signal swing of the VCO output oscillation that modulates the varactor capacitance in time. Thus, this utilization affects tuning curve as deviating from the typical C-V curve or the practical varactor device structure.

The instantaneous value of the capacitance changes throughout the signal period when the signal voltage swing across these devices is large (as it would be the case in VCO tank). The effective capacitance seen by the large signal will be a weighted average of the small-signal capacitance over a single period. Because of this "averaging" effect, the oscillator RF output frequency versus tuning voltage curve and the DC/smallsignal C–V curve will not be equivalent [36].

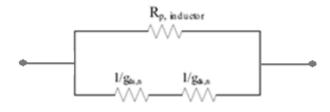

# 3.3 Design of gm stage

Initially, the design of the gm-stage was based on the inductor loss i.e. the inductor Q-value was assumed to be the dominating component regarding loss in the LC-tank hence  $g_{tank} \approx g_L$ . It was necessary to make this assumption, since the drain-source conductance values of the gm-stage FETs were not known at that time. The case was the same for the switch and fine tuning circuitry since the design of these sub-modules was based on the value of parasitics capacitances of the gm-stage.

The Q-value of the inductor is dominant and hence the  $R_L$  will be used as the target resistance that must be canceled out. The simulated Q-value of the inductor model is 11.8 at 5 GHz.

The loaded Q-value of the tank representing the total losses of the tank is stated as:

$$Q_{loaded} = \frac{R_p}{\omega_0 L} \tag{11}$$

where  $R_p$  is the equivalent parallel resistance modeling the total loss of the tank while  $\omega_0$  is the resonance frequency. The loaded Q-value is related to the Q-value of the inductive and capacitive components, as follows:

$$\frac{1}{Q_{loaded}} = \frac{1}{Q_L} + \frac{1}{Q_C} \tag{12}$$

Equation 12 defines the relation between the loaded Q-value and the individual Q-value of the inductor and capacitor. The component Q-value of the inductor is given by  $Q_L = \frac{\omega_0 L}{R_s}$  where *R*s symbolizes the series resistance of the inductor. The Q-value of the capacitor is stated as

$$Q_c = \frac{1}{R_s \omega_0 c} \tag{13}$$

where *R*s denotes the series resistance of the capacitor. Based on the fact that the Q-value of the actual capacitive part of the tank is assumed to be sufficiently higher than the inductor Q-value, the following statement is valid:

$$Q_L \ll Q_c \Rightarrow Q_L \approx Q_{loaded} \tag{14}$$

Using the statement shown in Equation (13) the equivalent parallel resistance of the loss tank is defined by:

$$R_P = Q_{loaded}.\,\omega_0.\,L = \frac{(\omega_0.L)^2}{R_s} = (\frac{\omega_0.L}{R_s})^2.\,R_s = Q_L^2.\,R_s \tag{15}$$

where  $R_s$  is the series resistance of the inductor. It is desirable to have the  $R_p$  as large as possible since this can be translated to a higher loaded Q-value and thereby lower series resistance of the tank. A higher loaded Q means better phase noise performance which is one of the main goals in VCO design. Furthermore, a lower series resistance is likewise beneficial, since the low resistance relaxes the requirement of the needed value of negative resistance to start and to maintain the oscillation. The series resistance of the inductor is the only resistive part influencing the equivalent parallel resistance of the tank. Knowing that the Q-value of the actual inductor is 11.8 the parallel resistance of the tank can now be found. The inductance is then 1.05 nH (at 5GHz) which leads to the following value of Rp:

$$R_P = Q_L^2 \cdot \left(\frac{\omega_o \cdot L}{Q_L}\right) = (11.8)^2 \cdot \left(\frac{2\pi \cdot 5 \cdot 10^9 \cdot 1 \cdot 05 \cdot 10^{-9}}{11.8}\right) \cong 389\Omega$$

(16)

Using the computed value of  $R_P$ , the parallel inductor conductance is found by:

$$g_L = \frac{1}{389\Omega} = 2.57mS$$

(17)

Since  $g_L \approx g_{tank}$  is assumed to be valid, by using safety factor of two and the PMOS must be designed such that they all two individually exhibit a transconductance value of:

$$g_{mn} = 4.2.57mS = 10.28mS \tag{18}$$

Each of the amplifying transistors must have a conductance g<sub>m</sub> of 10.28mS,

$$g_{mn} = \sqrt{2.\,\mu_o.\,C_{ox.}\frac{W}{L}.\,I_D} \tag{19}$$

where  $\mu_0$  is the mobility of the carriers in the channel while  $I_D$  is the drain current through the MOSFET. In order to determine the drain current, the desired single ended output voltage swing of the VCO must firstly be specified. The tank amplitude is given by:

$$V_{tank} = I_{bias} R_P = I_{bias} \cdot \omega_o \cdot L \cdot Q_L \tag{20}$$

The desired tank amplitude is set to  $V_{tank} = 500 \text{ mV}$  and thus the required bias current is:

$$I_{bias} = I_{tail} = \frac{0.5 \, mV}{389\Omega} = 1.2 \, mA \tag{21}$$

The drain current of each FET in the VCO is half the value of the bias current, since the bias current flows through the two VCO branches equally at DC. The remaining parameters of Equation (19), which must be specified, are the carrier mobility:

$$\mu_{\rm p} = 126 \, {\rm cm}^2 / {\rm Vs}$$

and the oxide capacitance is :

$$C_{ox,n} = C_{ox,p} = \frac{\epsilon_r \epsilon_o}{t_{ox}} = 4.57 f F / \mu m^2$$

Using the shown values, the W/L ratio was computed for PMOS transistor

*PMOS*:

$$\frac{W}{L} = 536$$