# COMPACT, FLEXIBLE AND FAST COPROCESSOR DESIGN FOR ELLIPTIC CURVE PAIRING OPERATION ON RECONFIGURABLE HARDWARE

by

#### ERTUĞRUL MURAT

Submitted to the Graduate School of Engineering and

Natural Sciences in partial fulfillment of

the requirements for the degree of

Master of Science

Sabancı University

August 2011

# COMPACT, FLEXIBLE AND FAST COPROCESSOR DESIGN FOR ELLIPTIC CURVE PAIRING OPERATION ON RECONFIGURABLE HARDWARE

| APPR          | OVED BY:                            |  |

|---------------|-------------------------------------|--|

|               |                                     |  |

|               | Associate Prof. Dr. Erkay Savaş:    |  |

|               | (Thesis Advisor)                    |  |

|               |                                     |  |

|               | Associate Prof. Dr. Albert Levi:    |  |

|               | Associate Prof. Dr. Cem Güneri:     |  |

|               | Associate Prof. Dr. Yücel Saygın:   |  |

|               | Assistant Prof. Dr. Selim Balcısoy: |  |

|               |                                     |  |

|               |                                     |  |

| <b>7 A</b> TE | E OE ADDDOVAL                       |  |

© Ertuğrul Murat 2011

All Rights Reserved

### **ABSTRACT**

Proposal of Identity-Based cryptography by Shamir in 1984 opened a new area for researchers. Failing to provide a feasible implementation of identity based encryption (IBE), Shamir developed a signature scheme, whereby signatures can be verified by publicly available information such as signer's identity. Since the first efficient implementation of IBE realized using pairing operation on elliptic curves due to Boneh and Franklin a plethora of papers has been published and many studies have been conducted covering different aspects of pairing-based cryptography. Today, pairing is used in many cryptographic applications including, identity based cryptography, key exchange protocols, short signatures, anonymous signatures and in many other newly emerging protocols and schemes. Also, pairing is still a developing research field yielding important challenges for the research community.

Pairing computation involves fairly complicated operations compared to classical symmetric and asymmetric cryptosystems. Multitudes of pairing types have been proposed after its first appearance in the literature. Also, each of them involves selection of many parameters such as the choice of the underlying field and its characteristics, order of the embedding degree, type of the elliptic curve etc. Therefore, different types of optimisations are possible rendering selection process extremely difficult. Because of the abundance of choices, for an efficient pairing implementation many criteria have to be examined. For instance, selection of pairing type, construction of finite fields and elliptic curves, coordinate systems to represent points on the curve and algorithms and architecture for arithmetic operations play a crucial role on the performance of the specific implementation of the pairing-based cryptography.

A multitude of implementations regarding to pairing-based cryptography have been proposed in the literature. However, most of them are software realizations; the reason being is the complexity of the overall system. Some hardware implementations have already been proposed, but most of them are very specific, therefore lacks flexibility and scalability. Due to the complexity of the system, some researches advice to use dedicated implementations for specific set of parameters even in software, limiting the flexibility of the implementation further.

In this thesis, we propose a very generic, flexible and compact hardware coprocessor for all kinds of pairing implementations intended for implementation on

reconfigurable devices (e.g. FPGA). Our co-processor supports all types of pairing

operations with different parameter classes via making use of highly-optimized

hardware implementations of basic arithmetic operations common not only to pairing

operations, but also to elliptic curve cryptography and other public key cryptography

algorithms. Our design utilizes the idea of hardware-software co-design concept. To

accelerate pairing computation we implement some units responsible for performing the

most time-consuming operations as a generic, but highly optimized hardware circuits,

whereas we prefer to implement some complex parts (unworthy of hardware resources)

in low-level software of micro-instructions. Although we use two arithmetic cores

running concurrently, our design still manages to be compact thanks to its careful and

generic design.

## ÖZET

Kimlik-temelli kriptografik sistemin 1984'te Shamir tarafından ortaya atılmasıyla, araştırmacılar için yeni bir kapı aralanmış oldu. Kimlik-temelli şifreleme işlemi için uygulanabilir bir algoritma önermeyen Shamir, imzanın geçerliliğinin imzalayanın herkese açık bilgileriyle, örneğin kimliği, doğrulanabildiği uygulanabilir bir elektronik imzalama sistemi geliştirdi. Kimlik-temelli şifrelemenin ilk uygulanabilir örneğinin Boneh ve Frankin tarafından eliptik eğriler üzerinde tanımlanmış eşleme (pairing) işlemi ile verilmesinden bu yana, kriptografi alanında eşleme temelli pek çok çalışmalar yapılıp, yayınlar çıktı. Günümüzde eşleme operasyonu pek çok kriptografik uygulamada kullanılmaktadır, kimlik temelli kriptografik sistemler, anahtar değişim protokolleri, kısa imzalar, anonim imzalar ve yeni gelişen pek çok protokol ve uygulama bunların arasındadır. Özet olarak kriptografik eşleme, içerisinde çözülmesi gereken birçok problemi barındıran ve halen gelişen bir araştırma alanıdır.

Eşleme operasyonu klasik simetrik ve asimetrik kriptografik sistemlere göre oldukça karmaşıktır. İlk eşleme operasyonunun geliştirilmesinden bu yana eşleme operasyonunun birçok sayıda türevi çıkmıştır. Her bir türev kullanılan cebrik cismin seçimi ve onun karakteristiği, yerleştirme derecesi gibi birçok parametre kullanmaktadır. Bundan dolayı parametre seçim sürecini oldukça zorlaştıran bir hayli optimizasyon bulunmaktadır. Seçenek bolluğundan dolayı etkili bir eşleme operasyonu gerçeklemesi için pek çok ölçüt incelenmelidir. Örneğin, eşleme işleminin tipi, uygun cebrik cismin ve eliptik eğrinin seçimi, kullanılacak koordinat sisteminin, algoritmaların ve aritmetik operasyonlar için donanım mimarilerinin seçimi gibi konular eşleme operasyonunun etkin gerçeklenmesinde önemli rol oynamaktadır.

Literatürde pek çok eşleme işlemi gerçeklemesi mevcuttur; fakat bunların çoğu salt yazılımsal gerçeklemelerdir. Bunun sebebi gerçeklenen operasyonun karmaşıklığıdır. Bunlar dışında bazı donanımsal gerçeklemeler mevcutsa da bunların çoğu çok özelleşmiş uygulamalardır ve bu nedenle esneklik ve ölçeklenirlikten yoksundur. Operasyonun karmaşıklığından dolayı bazı araştırmacılar verimli bir gerçeklemeye sahip olmak için yazılımsal dahi olsa, tasarımın esnekliğini sınırlayarak, özelleşmiş tasarımlara gidilmesini salık vermektedir.

Bu tezde, programlanabilir donanım cihazlarında gerçekleştirilmek üzere, her türde eşleme operasyonları için çok esnek, genel ve kompakt bir yardımcı-işlemci tasarımı sunulmaktadır. Geliştirilen tasarım, değişik parametre sınıflarında her eşleme operasyonu türevini desteklemektedir. Bunu yaparken sadece eşleme operasyonu için değil, diğer birçok asimetrik anahtarlı şifreleme sistemlerinde de kullanılan temel aritmetik operasyonları gerçekleyen son derece optimize edilmiş donanımsal işlevsel birimler kullanmaktadır. Tasarımda ortaya koyduğumuz yaklaşım, yazılım ve donanımın ortak kullanımıdır. Eşleme operasyonunu hızlandırmak için en çok zaman harcayan operasyonlar parametrik ve oldukça optimize donanımsal birimler olarak gerçeklenirken, karmaşık operasyonlar (kısıtlı donanım kaynaklarını verimli olarak kullanamayan) mikro-operasyonlar vasıtasıyla yazılımsal olarak gerçeklenmiştir. Tasarımda her ne kadar eş zamanlı çalışan ve aritmetik işlemleri gerçekleyen ikiçekirdek kullanılsa da, dikkatli tasarım ve esnek yapı sayesinde tasarım karşılaştırmalı olarak az yer kaplamaktadır.

Dedicated to my family...

### **ACKNOWLEDGEMENTS**

I would like to present my special thanks to my thesis advisor, Associate Prof. Dr. Erkay Savaş for his valuable mentorship, not only about this thesis but also for his guidance in general manner. He helped me in all points that I cannot make progress. For all the difficult corners of this thesis he became very elucidative. I also thank to members of my thesis jury, Associate Prof. Dr. Albert Levi, Associate Prof. Dr. Cem Güneri, Associate Prof. Dr. Yücel Saygın and Assistant Prof. Dr. Selim Balcısoy, for very useful suggestions on my thesis. Besides I would like to thank to Ersin Öksüzoğlu for sharing his valuable work, Mongomery multiplier, with me. I also sincerely thank to Ali Can Atıcı for all his helps during design process.

Last but not least, I thank to my family for their unlimited support. They are the ones who helped me stay where I stay in all respects. I do not forget the friends whom I did not count the names but who are always with me and fortify me. I thank to all.

# **Table of Contents**

| 1    | NTRODUCTION                                                             | 1        |

|------|-------------------------------------------------------------------------|----------|

| 2    | UNDERLYING FPGA ARCHITECTURE & BACKGROUND INFORMATION                   | 4        |

| 2    | Underlying FPGA Architecture                                            | 4        |

| 2    | BACKGROUND INFORMATION ON ALGEBRAIC STRUCTURES                          | 8        |

|      | .2.1 Finding Tate Pairing Parameters                                    | 10       |

|      | .2.2 Finding Elliptic Curve                                             | 11       |

|      | 2.3 Polynomial Arithmetic for <i>Fqk</i>                                | 14       |

|      | .2.4 Elliptic Curve Arithmetic on Projective Coordinates                | 16       |

|      | .2.5 Line Evaluation Function                                           | 17       |

|      | .2.6 Final Exponentiation                                               | 18       |

| 3    | PARAMETRIC AND COMPACT IMPLEMENTATION OF H                              | IARDWARE |

| CO   | OCESSOR FOR PAIRING ON FPGA                                             | 21       |

| 3    | ARITHMETIC CORE & INVERSION UNIT                                        | 26       |

| ,    | .1.1 Arithmetic Core                                                    |          |

|      | 3.1.1.1 Multiplication Module                                           |          |

|      | 3.1.1.2 Addition/Subtraction/Shifter Module                             |          |

|      | .1.2 Inverter Controller                                                | 32       |

|      | 3.1.2.1 Montgomery Inverter Module                                      | 34       |

|      | 3.1.2.1.1 Montgomery Modular Inversion Algorithm                        | 35       |

|      | 3.1.2.1.2 Montgomery Inverter Architecture                              | 38       |

|      | 3.1.2.1.3 Implementation Results of the Inverter Unit and Other Metrics | 42       |

| 3    | PROGRAM AND DATA MEMORY                                                 | 46       |

|      | .2.1 Program Memory                                                     | 46       |

|      | .2.2 Data Memory                                                        | 49       |

| 3    | THE CONTROLLER                                                          | 50       |

| 3    | THE TOP CONTROLLER                                                      | 54       |

| 3    | DEBUGGING OF THE HARDWARE                                               | 56       |

| 4    | CONCLUSION AND COMPARISON                                               | 57       |

| REI  | RENCES                                                                  | 60       |

| A DI | NDIY                                                                    | 64       |

# **List of Terms and Symbols**

> ACIU: Arithmetic core and inversion unit.

➤ ASIC: Application Specific Integrated Circuit

**BMC:** Block of micro code.

**BRAM**: Block RAM; hardwired RAM in FPGA.

➤ CIOS: Coarsely Integrated Operand Scanning

> **DLP:** Discrete logarithm problem.

**DMA:** Direct memory access

> **DSP48A1:** Hardwired arithmetic unit in FPGA

> **DSS:** Digital Signature Standard

> FDEU: Fetch decode and execute unit.

> FPGA: Field Programmable Gate Array

➤ LSW: Least significant word. If a variable is thought as sequence of words having same bit size each, then LSW defines the least significant word.

➤ LUT: Both stands for number of LUTs and look up tables: Boolean function generators in FPGA

➤ M: Modulus

> m: bit size of modulus.

> ms: milliseconds: 10<sup>-3</sup> seconds.

➤ MF: Maximum frequency; achievable maximum frequency in an FPGA design.

➤ MM: Montgomery multiplier: A special multiplier specialized for hardware.

> MSW: Most significant word.

- ➤ **Opcode:** Operation code. This is the part of the micro code which defines what kind of operation to be executed.

- ➤ PAR: Place and route: Last step in the implementation before embedding the core.

- > **REG:** Flip flop numbers used in a design.

- > T: Total time to complete the operation

- > **TA:** Time are product; LUT\*T/1000

- ➤ us: microseconds: 10<sup>-6</sup> seconds.

- > WL: Word length; bit size of a processing word.

# **List of Figures**

| FIGURE 1: CONNECTION OF SLICES [6]                                | 6  |

|-------------------------------------------------------------------|----|

| FIGURE 2: INTER CLB CARRY PROPAGATION [6]                         | 6  |

| FIGURE 3: GENERAL OVERVIEW OF THE PROCESSOR ARCHITECTURE          | 24 |

| FIGURE 4: ARITHMETIC CORE I/O INTERFACE                           | 27 |

| FIGURE 5: MONTGOMERY MULTIPLIER I/O INTERFACE                     | 30 |

| FIGURE 6: MODULAR ADDITION ARCHITECTURE                           | 31 |

| FIGURE 7: MODULAR ADDITION I/O INTERFACE                          | 32 |

| FIGURE 8: INVERTER CONTROLLER I/O INTERFACE                       | 33 |

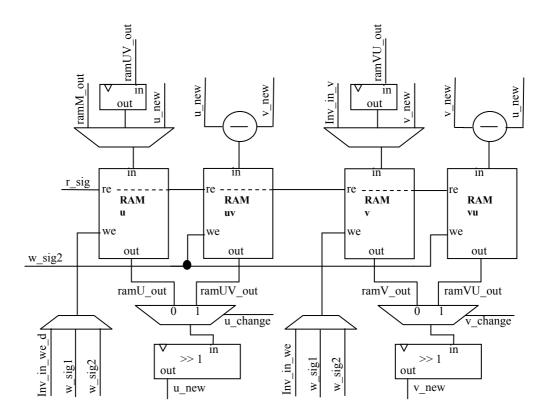

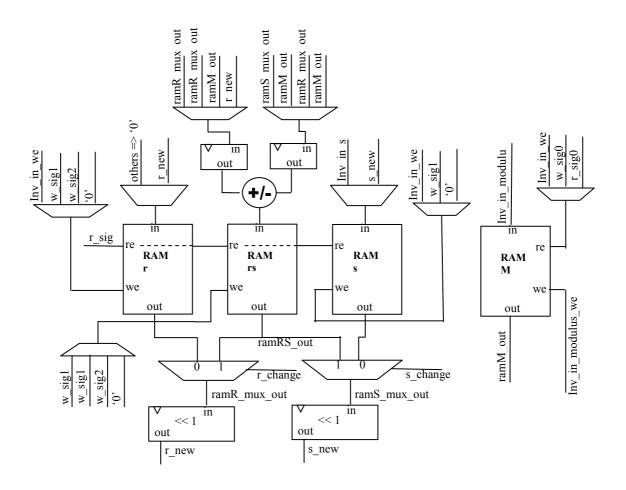

| FIGURE 9: U/V PART OF THE INVERTER                                | 39 |

| FIGURE 10: R/S PART OF THE INVERTER                               | 41 |

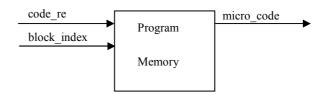

| FIGURE 11: I/O INTERFACE OF PROGRAM MEMORY                        | 49 |

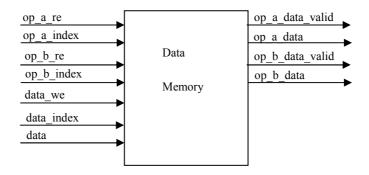

| FIGURE 12: I/O INTERFACE OF DATA MEMORY                           | 50 |

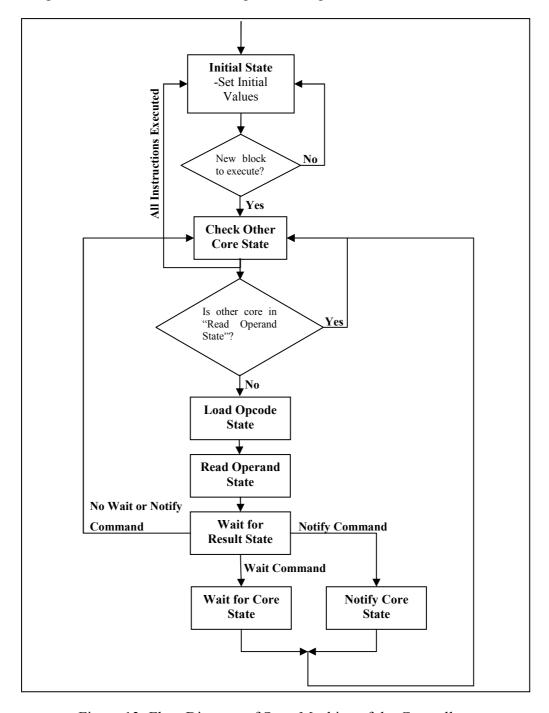

| FIGURE 13: FLOW DIAGRAM OF STATE MACHINE OF THE CONTROLLER        | 52 |

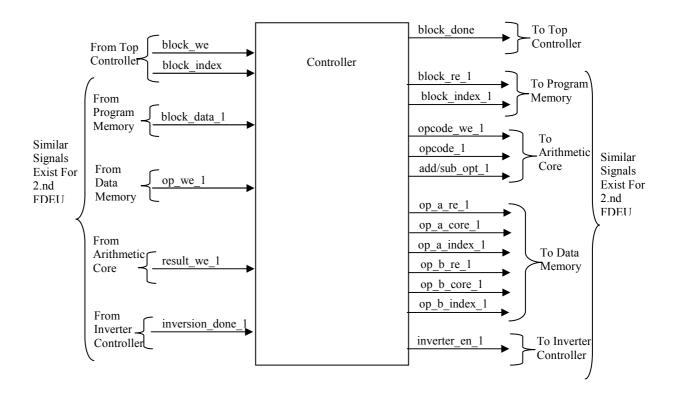

| FIGURE 14: I/O INTERFACE OF CONTROLLER                            | 53 |

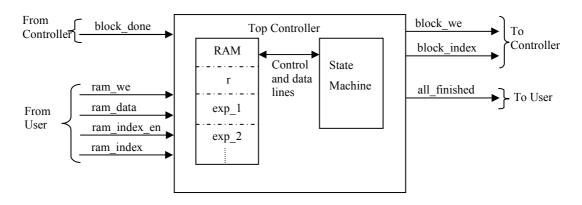

| FIGURE 15: I/O INTERFACE AND INNER ABSTRACTION OF TOP CONTROLLER. | 55 |

# **List of Tables**

| TABLE 1: a0 AND b0 VALUES FOR DISCRIMINANT [33]                    | 12   |

|--------------------------------------------------------------------|------|

| TABLE 2: OPCODES AND THEIR DEFINITIONS FOR ARITHMETIC CORE         | 28   |

| TABLE 3: PAR RESULTS USING DISTRIBUTED RAM UNDER AREA OPTIMIZATION | N 43 |

| TABLE 4: PAR RESULTS USING DISTRIBUTED RAM UNDER SPEED OPTIMIZATIO | N 43 |

| TABLE 5: PAR RESULTS USING BRAM UNDER AREA OPTIMIZATION            | 44   |

| TABLE 6: PAR RESULTS USING BRAM UNDER SPEED OPTIMIZATION           | 44   |

| TABLE 7: COMPARISON WITH A PREVIOUS WORK USING SAME FPGAS          | 45   |

| TABLE 8: FORMAT OF THE MICRO-INSTRUCTION                           | 46   |

| TABLE 9: I/O PORT DEFINITIONS FOR THE FIRST FDEU                   | 54   |

| TABLE 10: PAR RESULTS FOR CO-PROCESSOR IMPLEMENTING TATE PAIRING   | 58   |

| TABLE 11: COMPARISON RESULTS                                       | 59   |

# **List of Algorithms**

| ALGORITHM 1: BKLS TATE PAIRING ALGORITHM [4]            | 9  |

|---------------------------------------------------------|----|

| ALGORITHM 2: FINDING THE CURVE AND GENERATOR POINT [33] | 13 |

| ALGORITHM 3: FINDING A POINT $P$ OF ORDER $r$ [33]      | 14 |

| ALGORITHM 4: IMPLEMENTATION OF KARATSUBA METHOD ON Fq2  | 15 |

| ALGORITHM 5: IMPLEMENTATION OF KARATSUBA METHOD ON Fq4  | 16 |

| ALGORITHM 6: Fq2 INVERSION USING Fq INVERSION           | 19 |

| ALGORITHM 7: Fq4 INVERSION USING Fq2 INVERSION          | 20 |

| ALGORITHM 8: CIOS MONTGOMERY MULTIPLICATION METHOD [42] | 29 |

| ALGORITHM 9: ALMMONINV(A, M) (PHASE I) [49]             | 36 |

| ALGORITHM 10: MONINV(R, M, K) (PHASE II) [49]           | 37 |

### 1 Introduction

Most commonly accepted definition of the pairing operation is as follows: Pairing is a bilinear map which is defined from  $G_1 \times G_2$  to  $G_T$ ,  $(G_1 \times G_2 \to G_T)$ , where  $G_1$  and  $G_2$  are usually additive groups implemented on elliptic curves and  $G_T$  is multiplicative group [3]. Pairing is first introduced to cryptographic community by Menezes et al., with a destructive example, MOV attack [1]. In their study, they propose a method for converting discrete logarithm problem, which is defined over an elliptic curve on a finite field  $F_p$ , to the discrete logarithm problem over an extension field  $F_{pk}^*$ . However, real take off in pairing is realized with application of pairing to the identity-based cryptography (IBC) by Boneh and Franklin [2]. Since then, pairing has been a very active research topic with multitude of papers published every year. Pairing is mainly used in IBC, certificate-less cryptosystem, in key agreement protocols [10], [11] and many new cryptographic applications [12].

Many pairing types are proposed in the literature [13], [14], [15]. Also many optimization methods are proposed for operations in pairings to efficiently implement it in hardware and software [16], [17], [13]. However, most studies are about software implementations of pairings [18], [19], [20]. There are some publications which aim hardware realizations, but they are few in number and besides, it is very difficult to find common points among them to make a fair comparison. This is due to the fact that, each implementation uses a special type of pairing or special parameters. There is a multitude of parameters that affect the efficiency and scalability of a pairing implementation; both in hardware or software. Some of the parameters includes: type of the curve, type of the coordinate systems used for elliptic curve point representation, underlying field, and extension degree of the fields, and even hamming weight of an input variable [3].

In this thesis, we design a general-purpose pairing coprocessor for arbitrary elliptic curves and embedding degrees targeted for reconfigurable hardware implementation. We propose a balanced mixture of hardware-software methods and architectures for realization of pairing operation. It aims to use advantages of both software and hardware. While hardware is very efficient in realizing some dedicated operations that constitute the computational bottleneck of the pairing operation (e.g. field multiplication), it is a valuable resource and cannot be easily spent on complex operations, which are not worthy of hardware resources. At this point software remedies the situation by providing cost-effective solutions to complex operations, even though it is not as fast as hardware. We aim to propose an architecture that can fit into small and old fashioned FPGAs, like Xilinx Spartan 3S400 [21]; and when used with very modest middle range FPGAs, like Xilinx Spartan-6SLX45T [5], there remains plenty of implementation space for other purposes. However, being small is not the only goal of the design; an acceptable speed performance is required. Our processor employs two arithmetic cores, which provide shorter operation time by using parallelization. In addition to these, our design is parametric and very flexible. It provides trade-off between area and speed in a very wide spectrum. According to design privileges, design can be easily changed from an area-efficient design to speed-efficient design. Variables that facilitate the flexibility of our design are listed below:

- ➤ Word Length (WL): Our processor operates over variables of words similar to a general-purpose CPU. However, our word size is changeable. This parameter defines the bit length of the word.

- ➤ Input Length (IL): Some dedicated hardware implementations are designed to operate on a constant input size. However, our design can easily be adapted to work on different input lengths. This parameter defines the total bit length of the longest input variable (e.g modulus in modular arithmetic).

- ➤ Pipeline Stage Number (PSN): This parameter defines the total number of pipeline stages used in multiplier for the underlying prime field, which is an important part of the design.

Main subject of this study is a pairing processor, as previously mentioned, since many parameters affect the efficiency of pairing operation. We also need suitable parameters and curves to work on.

Pairing operation can be realized over certain classes of elliptic curves satisfying some special parameters, as explained in [4], and detailed in the next chapter, are known as pairing-friendly elliptic curves. Pairing operation involves arithmetic over an extension field, thus we have to decide and find a suitable elliptic curve and extension field to use in our implementations.

In addition, we also have to be careful about the efficiency and security of the system. One parameter that directly affects the security and efficiency of the system is the bit length of prime integer (*the* modulus) for the field over which we construct our elliptic curve. As bit length of the modulus increases, arithmetic operations begin to slow down, but security increases. Another factor that affects the security and speed is the embedding degree of elliptic curve, which is also the degree of irreducible polynomial that the extension field is built upon. As embedding degree gets bigger that can increase the security level, complexity of arithmetic operations in the extension field increases.

One of the optimizations to reduce the execution time of pairing is proposed for extension field multiplication. We use Karatsuba-Ofman [22] algorithm to reduce multiplication time in the extension field. Before completing pairing operation, an exponentiation operation has to be done on extension field. Here again we use an optimized method to considerably decrease the total exponentiation time.

Pairing is an operation defined over elliptic curves whereby choice of the coordinate systems is important for efficiency reasons. For example, in affine coordinate system during elliptic curve point addition and point doubling, a division operation has to be performed. But the division is very time consuming operation. Therefore, we have to choose a coordinate system that does not need division. We prefer to use Jacobian mixed projective coordinate system as it needs no division operation during point addition and point doubling. Moreover, it exhibits better performance than other projective coordinate systems.

In the next section we provide the details about the underlying FPGA architecture, selection of elliptic curves, extension field operations and elliptic curve arithmetic operations. Also Tate pairing is explained in detail and some optimization techniques are discussed to reduce the overall running time of the algorithm.

# 2 Underlying FPGA Architecture & Background Information

In this section we provide information about the structure of the FPGA which we use to implement our co-processor architecture. Also we give information about pairing operation in general and Tate pairing in particular. We choose to implement our design in Spartan-6SLX45T, due to the fact that it is a low-cost middle-range FPGA, meaning it does not have abundance of logic resources like high-end FPGA devices, but has a modest level of logic resources close to low-end FPGA devices [5]. Another reason is that Xilinx Spartan-6 family members are optimized for low power consumption. In the following subsection underlying FPGA architecture is discussed.

### 2.1 Underlying FPGA Architecture

Spartan-6 provides low power solutions with its 45 nm manufacturing technology. It provides low power consumption with high performance with the help of its 1.2 V core voltage. Compared to the previous members of Spartan family, its power consumption is as low as half of theirs. Also, it provides moderate logic resources [5]. One member of the Spartan-6 family, Spartan-6SLX45T, is 84.4\$ today, whereas a cheap and older FPGA, Spartan-3S400 costs about 31\$ [7]. However, Spartan-6 has five to six times more logic resources than Spartan-3. Therefore, cost of per logic unit in Spartan-6 is lower than the cheapest FPGA. Hence Spartan-6 offers the best price-performance ratio compared to the older Spartan family. If we look at all the advantages, Spartan-6 appears as a good choice for low-cost, low-power embedded cryptographic applications, which necessitate considerably complicated operations.

Understanding architecture and capabilities of underlying FPGA architecture is essential for efficient designs. This is only possible provided that complete insight of FPGA attributes is available to make right decisions about the design.

There are several special building blocks inside the Xilinx Spartan-6 FPGA, which we use in our design. These are configurable logic blocks (CLBs), block RAMs (BRAM) and digital signal processor units (DSP48A1s). These components provide flexibility in the design and efficient use of resources.

CLBs are the main reconfigurable logic block of the FPGA. One CLB contains two slices and every slice contains four look-up tables (LUTs) and eight flip-flops. LUTs are mostly known as Boolean function generators of the FPGA. However, they can also serve as RAM and shift register. LUTs in Spartan-6 have six inputs and two output ports. These LUTs are, in fact, composed of two smaller, five-input LUTs. Therefore, with one LUT either two five-input logic functions or a six-input logic function can be realized. There are several types of slices; SLICEX, SLICEL and SLICEM. Differences between them are as follows: SLICEX is the simplest one, where LUTs are only capable of realizing logic functions. It does not contain arithmetic structure, nor can it be used as shifter or RAM. SLICEL contains carry-logic and its LUTs can be combined to construct large multiplexers. SLICEM is the most functional one. In addition to the functions in SLICEL, LUTs in SLICEM can be used as distributed RAM and shifter. Both SLICEL and SLICEM feature carry look-ahead logic for fast addition operation. By default, addition is implemented using carry look-ahead adder logic in the FPGA. Thus, we do not use any structure other than the one automatically inferred by the FPGA for addition. Trying to implement addition by using other logic resources does not result in a better adder due to the fact that default adder type of FPGA is already carry look-ahead adder, moreover it is placed into a specialized area. What is meant by specialized area is that logic elements used in carry generation have very low latency values.

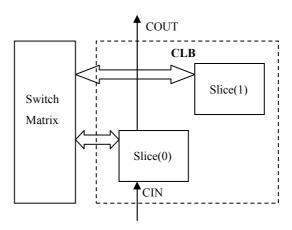

Since there are four LUTs in a slice, a 4-bit adder/subtractor is easily realized within a slice. For operands larger than four bits, a special structure reduces the latency in carry generation path. Normally, slices in a CLB are not directly connected to each other; they are connected to a switching matrix outside the FPGA, as can be seen in

Figure 1. After switching matrix, they connect to global routing resources; then appropriate routing is achieved.

Figure 1: Connection of Slices [6]

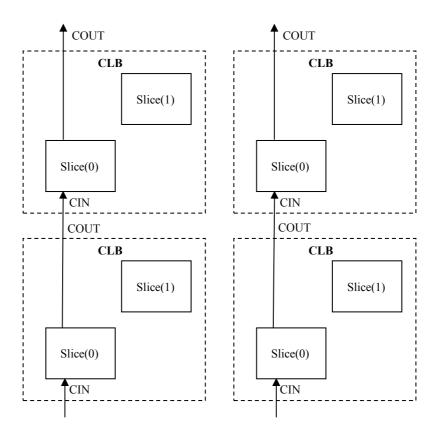

However in the case of carry propagation, carry output of one slice directly connects to the carry input of the other slice. Hence, fast propagation of carry is possible. This situation is depicted in Figure 2.

Figure 2: Inter CLB Carry Propagation [6]

The feature related to carry propagation is not new to Spartan-6, while it exists even in older Spartan-3 family; the implementation is much faster in Spartan-6.

LUTs have many other useful features. LUTs can be configured to construct wide multiplexers. As previously mentioned, LUTs in Spartan-6 have six inputs which enable us to realize a  $(4 \times 1)$  multiplexer in one LUT. Thus, when using multiplexers equal or smaller than  $(4 \times 1)$ , only one LUT is used. It is important to keep this property in mind and trying not to use larger multiplexers than  $(4 \times 1)$ . For example, when a  $(5 \times 1)$  multiplexer is used logic usage doubles rather than a linear increase. To implement multiplexers having sizes between  $(5 \times 1)$  to  $(8 \times 1)$ , we need the same amount of LUTs, which is double of  $(4 \times 1)$  in this case. We understand that this is important especially when we think about multiplexers used in large data buses. Number of multiplexer utilized for one bit switching is multiplied with size of bus in a multiplexer used in bus switching.

Another important feature of LUTs is that they can be configured as *distributed RAM*. However, only LUTs in SLICEMs can be used as RAM. These LUTs have some additional attributes that enable them to act like a RAM. They have inputs for data as well as a write enable. Thus in most basic version, they can be configured as single port,  $64 \times 1$  RAM with synchronous write and asynchronous read. Nevertheless, their output can be made synchronous by using the flip-flops in SLICEM. RAM, that is constructed using LUTs are called distributed RAM. Distributed RAM and BRAM can be employed interchangeably [6].

BRAMs are hardwired memory blocks inside the FPGA. They have synchronous read/write operations. A BRAM can have different widths and depths. Wider BRAMs are automatically formed by the implementation tool. BRAMs are utilized generally when a need for high memory usage arises. Especially when big variables are used, like in our case and generally in most cryptographic applications, employing of BRAMs saves significant amount of logic resources. BRAMs have fixed places in the FPGA which is actually physically in the middle of FPGA. This may cause some unexpected latency in some cases when circuit is placed away from the BRAMs. In these cases outputs and inputs of the BRAMs should be registered [8].

DSP48A1 is a special hardwired block for arithmetic and logic operations. There are equivalent functional units in older versions of FPGAs. It contains hardwired and

pipelined adders/subtractors and multipliers. In our design we use 18 × 18 hardwired multipliers. We do not use hardwired adders/subtractors inside of DSP48A1, since CLBs also have specialized carry logic as explained previously. Moreover using DSP48A1 for addition/subtraction may cause some extra delay due to routing to resources. To overcome this problem registered inputs and outputs are usually used. In this case registers adds extra clock cycles at each access of source and this increases the overall processing time. This is not worthwhile in case of adder/subtractor. On the other hand, since implementing multiplier with logic resources consumes too much area, we use DSP48A1 units for performing multiplication [9].

### 2.2 Background Information on Algebraic Structures

$G_1$  and  $G_2$  are two additive groups and  $G_3$  is a multiplicative group. And let all of them have a group order r, which can be further assumed to be prime number. Then pairing is a map defined as follows:  $e: G_1 \times G_2 \to G_3$ , which satisfies the following properties, given that P is a generator of  $G_1$  and  $G_2$  is a point on  $G_2$ , which is linearly independent of  $G_2$  is a point on  $G_2$ .

**1. Bilinearity**: For all

$$P, R \in G_1$$

and for all  $Q, S \in G_2$

$$e(P+R,Q) = e(P,Q) \times e(R,Q)$$

$$e(P,Q+S) = e(P,Q) \times e(P,S)$$

$$e(iP,Q) = e(P,Q)^i \text{ and } e(P,iQ) = e(P,Q)^i$$

where  $\times$  denotes the multiplication in  $G_3$ .

**2. Non-degeneracy:** For all  $P \in G_1 - \{0\}$ , there exists some  $Q \in G_2$  such that;  $e(P,Q) \neq 1$  and for all  $Q \in G_2 - \{0\}$ , there exists some  $P \in G_1$  such that;  $e(P,Q) \neq 1$

Tate pairing over elliptic curves is one type of the pairing operation that can be calculated efficiently and satisfies the aforementioned properties. P and Q are chosen as follows: Let  $F_q$  is a prime field and  $E(F_q)$  is curve over that field. Let r be a prime such that, there exists a point on the elliptic curve  $E(F_q)$  with order of r. Moreover  $r \mid \#(E(F_q))$  [24] where  $\#(E(F_q))$  denotes the number points on the elliptic curve. Let k be the smallest number satisfying  $r \mid q^k - 1$ , and  $r \nmid q^l - 1$  for  $1 \leq l < k$

[25]. The integer k is referred as the embedding degree of  $E(F_q)$ . Set of the points on  $E(F_q)$  of order r is denoted as  $E(F_q)[r]$ . Then  $P \in E(F_q)[r]$  and  $Q \in E(F_{q^k})$  are the inputs of the Tate pairing operation. More precisely, Tate pairing is defined as a map  $e: E(F_q)[r] \times E(F_{q^k}) \to F_{q^k}^*/(F_{q^k}^*)^r$  and considered as the evaluation of a rational function  $f_P$ , whose divisor is  $div(f_P) = r[P] - r[\infty]$  ( $[\infty]$  is point at infinity), such that:

$$e(P,Q) = f_P(D_O)^{q^k - 1/r},$$

where  $D_Q \sim [Q] - [\infty]$  is the divisor for Q [24] (for more information about divisors see [26]).

The most efficient implementations for pairing computation use Miller's algorithm proposed in [27], which evaluates the rational function  $f_P$  at point Q. Tate pairing algorithm consists of elliptic curve and polynomial arithmetic operations over finite fields. Without any optimizations, the computation becomes prohibitively time-consuming. One of the algorithms that computes Tate pairing efficiently is BKLS algorithm [28], as described in Algorithm 1.

```

Algorithm 1: BKLS Tate Pairing Algorithm [4]

Inputs: P,Q \in E and r \in \mathbb{Z}

T \leftarrow P,f \leftarrow 1

Output: f_{r,P}(Q)^{\frac{p^{k}-1}{r}}

1. for i = \lfloor \lg(r) \rfloor - 2 to 0

2. f \leftarrow f^2 * l_{T,T}(Q)

3. T \leftarrow \lfloor 2 \rfloor T

4. if r_i = 1 then

5. f \leftarrow f * l_{T,P}(Q)

6. T \leftarrow P + T

7. end if

8. end for

9. f \leftarrow f^{\frac{p^k-1}{r}}

```

Many possible optimizations exist for Algorithm 1. Some optimizations are possible for arithmetic operations over  $F_{q^k}$ , for evaluation of line computation function  $l_{A,B}(Y)$  (steps 2 and 5), for elliptic curve operations (point addition and point

doubling) (steps 3 and 6) and for final exponentiation operation (step 9). Moreover even selection of proper r value can be included into these optimizations.

Potential optimizations are explained in the next subsection. But prior to this finding the appropriate elliptic curve and pairing parameters are detailed since Tate pairing performance also depends on these parameters.

#### 2.2.1 Finding Tate Pairing Parameters

We choose to operate on a field with embedding degree being k = 4. Although another embedding degree can be selected for different security requirements we believe that this degree provides optimum security-complexity trade-off. Security of a pairing operation depends on two parameters: The bit size of the subgroup in elliptic curve, which is  $log_2r$ , and the bit size of extension field, which is  $k * log_2q$ . Values of these parameters should be chosen according to the best known attack towards them. Most successful attack for elliptic curve discrete logarithm problem (ECDLP) is Pollard- $\rho$  technique whose complexity is  $O(\sqrt{r})$  [29]. On the other hand best attack to prime extension fields,  $F_{a^k}$ , is index-calculus method whose complexity is given by;  $\mathcal{O}(L_{q^k}(1/3))$  and  $L_{q^k}(1/3) = exp((32/9)^{1/3} * (\log q^k)^{1/3} * (\log \log q^k)^{2/3})$  [31]. According to NIST suggestions [30] for 80 bit security it is proper to choose r as a 160bit integer and  $q^k$  as 1024-bit integer. We choose r as 160 bits and q as 256 bits for 80 bits security following the NIST's advice. However choosing the bit length is only one aspect of the task, since all together r, q and k should satisfy some equations explained as in section 2.2. We use the following formulas proposed in [32] to find appropriate r, q values for k = 4.

$$t(x) = -4x^{3}$$

$$r(x) = 4x^{4} + 4x^{3} + 2x^{2} + 2x + 1$$

$$q(x) = \frac{1}{3}(16x^{6} + 8x^{4} + 4x^{3} + 4x^{2} + 4x + 1)$$

Some other formulas can be used but above equations give the whole set of elliptic curves whose embedding degree k = 4 and having a discriminant value equals

to 3 (as explained in subsequent sections). With the help of a software program using these equations for desired bit lengths, r and q values can be found. Note that both and r and q are prime numbers, so for each value found, primality test have to be run.

Another point to note is that extension fields are built using irreducible polynomials whereas q is just the prime of the field so we have to choose an irreducible polynomial. Since degree of our extension field is k=4 then the degree of the irreducible polynomial should be 4. We choose a small irreducible polynomial in the form of  $x^k - \beta$  to simplify the extension field arithmetic operations. In our case  $\beta$  is 2 since it is a small number and moreover multiplying a number with 2 means shifting it to the left by 1 bit, which is a very easy operation compared to multiplication. Thus, another constraint is added to check when pricking a suitable q: To make  $x^k - 2$  irreducible polynomial, 2 should be quadratic non-residue in modulo q. In the equations, t(x) represents the trace of elliptic curve. As can be remembered r should divide  $\#E(F_q)$ , which is equal to q+1-t. This variable is used in finding elliptic curve in next section.

#### 2.2.2 Finding Elliptic Curve

After finding q, r and t values we can build an ordinary elliptic curve using these parameters. We use following elliptic curve equation:  $y^2 \equiv x^3 + a * x + b \pmod{q}$ , where  $a = a_0 * k_a$  and  $b = b_0 * k_b$ . To find elliptic curve variables a, b, IEEE 1363 standard [33], which defines standards for elliptic curve cryptography, is used. According to the standard for a given discriminant  $a_0$  and  $b_0$  values are predetermined and  $k_a$  and  $k_b$  values are random. Since we already choose our discriminant value as 3,  $a_0$  and  $b_0$  values are known. Table 1 shows the values of  $a_0$  and  $a_0$  for given discriminants:

| D  | $a_0$ | $b_0$ |

|----|-------|-------|

| 1  | 1     | 0     |

| 2  | -30   | 56    |

| 3  | 0     | 1     |

| 7  | -35   | 98    |

| 11 | -264  | 1694  |

Table 1:  $a_0$  and  $b_0$  Values for Discriminant [33]

We define another variable, k', for finding proper elliptic curve. This value comes from Hasse's theorem;  $k' * r = \#E(F_q) = q + 1 - t$  since we know the right hand side of the equation we can compute k' and curve parameters can be calculated using q, k', r and  $a_0, b_0$ . Note that k' has no relation with embedding degree k. Curve parameters and generator point of  $\#E(F_q)$ , P, can be found using Algorithm 2 defined in IEEE 1363.

#### Algorithm 2: Finding the Curve and Generator Point [33]

**Inputs:** EC parameters p,r and k' and coefficients  $a_0,b_0$ **Output:** A curve E modulo q and a generator point P on E with order r, or a "wrong order" message

- 1. Select an integer  $\delta$  s.t.  $0 < \delta < q$

- 2. If D = 1, then  $a\leftarrow a_0\delta \bmod q$  and  $b\leftarrow 0$ ; if D=3 then  $a\leftarrow 0$  and  $b\leftarrow b_0\delta \bmod q$ . Otherwise,  $a\leftarrow a_0\delta^2 \bmod q$  and  $b\leftarrow b_0\delta^2 \bmod q$

- 3. Look for a point P of order r on the curve  $y^2 = x^3 + a * x + b \pmod{q}$  via A.11.3

- 4. If the output of A.11.3 is "wrong order", then output the message "wrong order" and stop

- 5. Output the coefficient a,b and the point P. Selection of  $\delta$  in the first step of the algorithm relies on the kind of coefficients wanted. For instance:

- If D $\neq$ 1 or 3, and it is wanted a=-3, then  $\delta$  is taken as the solution to  $a_0\delta^2\equiv -3\ (mod\ q)$  if there exists. If does not exists or selection of  $\delta$  causes a message "wrong order", then choose another curve as follows. If  $q\equiv 3\ (mod\ 4)$  and the result was "wrong order" then choose  $-\delta\ mod\ q$  instead of  $\delta$ ; the result leads to a curve with a=-3 and the right order. If no solution  $\delta$  exists, or if  $q\equiv 1\ (mod\ 4)$ , then repeat A.14.4.1 with another root of the reduced class polynomial. The ratio of roots leading to a curve with a=-3 and the right order is roughly one-half if  $q\equiv 3\ (mod\ 4)$ , and one-quarter if  $q\equiv 1\ (mod\ 4)$ .

- If there is no restriction on coefficients, then choose  $\delta$  at random. If it turns out "wrong order", then repeat the algorithm till a set of parameters a,b and P is obtained. This occurs for half the values of  $\delta$ , unless D=1 (one quarter of values) or D=3 (one-sixth of values)

For Step 3 of Algorithm 2, where a base point is found, is given in Algorithm 3.

### Algorithm 3: Finding a Point P of Order r [33]

**Inputs:** A prime r, a positive integer k' not divisible

by r, an elliptic curve  $E(F_q)$

Output: If  $\#(E(F_q)) = k'r$ , a P on E with order r, If not, "wrong order" message

- 1. Generate a random point P (not  $[\infty]$ ) on E

- 2.  $P \leftarrow k'P$

- 3. If  $P = [\infty]$  then go to step 1

- $4 \cdot P' \leftarrow rP$

- 5. If  $P' \neq [\infty]$  then output "wrong order" and stop

- 6. Return P

Using the Algorithms 2 and 3 an elliptic curve  $E(F_q)$  and a generator point P is found. As can be remembered there is no constraint on the point Q, other than being linearly independent of P. Thus, it is easy to find a Q point for starting the Tate pairing operation [23].

#### 2.2.3 Polynomial Arithmetic for $F_{ak}$

The values f and  $l_{A,B}(Q)$  in Algorithm 1 are in  $F_{q^k}$ . Thus there are considerably high numbers of polynomial operations for arithmetic of  $F_{q^k}$ . Most time-consuming operation of them is the inversion; but due to the algorithm used [4], denominator elimination can be applied. At the end of the Miller's loop (for loop) in the Algorithm 1, denominator of the variable f goes to 1. Thus, there is no need to perform inversion during the Miller's loop. Therefore multiplication stands as the most time consuming operation in the Miller's loop. We use an optimized method, called Karatsuba multiplication method [22], to reduce the number of  $F_q$  multiplications used to perform  $F_{q^k}$  multiplications. The method is summarized as follows [34]. Let A and B be polynomials of degree k-1, with k coefficients:

$$A(x) = \sum_{i=0}^{k-1} a_i x^i, B(x) = \sum_{i=0}^{k-1} b_i x^i$$

For each i = 0,1,....,k-1 the terms  $D_i := a_i b_i$  are computed. Also, for j = 1,2,...,2k-3 and for all s and t given s+t=j and  $t>s\geq 0$  the following terms are calculated

$$D_{s,t} \coloneqq (a_s + a_t)(b_s + b_t)$$

Afterwards,  $C(x) = A(x)B(x) = \sum_{i=0}^{2k-2} c_i x^i$  can be calculated as follows:

$$c_0 = D_0$$

,  $c_{2k-2} = D_{k-1}$

$$c_i(x) = \begin{cases} \sum_{s+t=i; t>s\geq 0} D_{s,t} - \sum_{s+t=i; t>s\geq 0} (D_s + D_t), for\ odd\ i; 0 < i < 2k-2\\ \sum_{s+t=i; t>s\geq 0} D_{s,t} - \sum_{s+t=i; t>s\geq 0} (D_s + D_t) + D_{i/2}, for\ even\ i; 0 < i < 2k-2 \end{cases}$$

Rightness of the formula and its complexity are discussed in [35]. This method requires  $\mathcal{O}(1/2(k^2+k))$  multiplications in  $F_q$  while classical method requires  $\mathcal{O}(k^2)$  to perform one  $F_{q^k}$  multiplication.

In calculation of  $F_{q^4}$  multiplication we use two Karatsuba multiplications recursively. First we calculate  $F_{q^2}$  multiplication using  $F_q$  multiplication, for which explicit formulas used, when k=2, is given in Algorithm 4. We build  $F_{q^2}$  over  $F_q$  as  $F_{q^2}=F_q[x]/(x^2-\beta)$ , where  $\beta$  is a quadratic non-residue in  $F_q$ .

```

Algorithm 4: Implementation of Karatsuba method on F_{q^2}

Inputs: a = a_0 + a_1 i, b = b_0 + b_1 i

Output: c = a * b where c = c_0 + c_1 i.

1. t_1 = a_0 b_0

2. t_2 = a_1 b_1

3. t_3 = \beta t_2

4. c_0 = t_1 + t_3 = a_0 b_0 + \beta a_1 b_1

5. t_3 = t_1 + t_2 = a_0 b_0 + a_1 b_1

6. t_1 = a_1 + a_0

7. t_2 = b_1 + b_0

8. t_4 = t_1 t_2 = (a_0 + a_1)(b_0 + b_1)

9. c_1 = t_4 - t_3 = (a_0 + a_1)(b_0 + b_1) - (a_0 b_0 + a_1 b_1)

Total cost of the operation: 4F_q multiplication + 5F_q addition

```

Then we implement  $F_{q^4}$  multiplication using  $F_{q^2}$  multiplications.  $F_{q^4}$  field is built upon  $F_{q^2}$  field using tower construction.  $F_{q^4} = F_{q^2}[y]/(y^2 - \gamma)$  and  $F_{q^2} = F_{q^2}[y]/(y^2 - \gamma)$

$F_q[x]/(x^2-\beta)$  where  $i=\sqrt{\beta}\in F_{q^2}$  and  $\gamma=i$  where  $I=\sqrt{i}=\sqrt{\gamma}\in F_{q^4}$ . This type of construction is called tower field. The tower field construction makes things easier in extension field operations. Thus, we can effectively build  $F_{q^4}$  operations over  $F_{q^2}$  operations. The method for  $F_{q^4}$  multiplication is given in Algorithm 5.

Algorithm 5: Implementation of Karatsuba method on  $F_{q^4}$ Inputs:  $A = A_0 + A_1I$ ,  $B = B_0 + B_1I$ ;  $A_0, A_1, B_0, B_1 \in F_{q^2}$ Output: C = A \* B where  $C = C_0 + C_1I$ ;  $C_0, C_1 \in F_{q^2}$ 1.  $T_1 = A_0B_0$ 2.  $T_2 = A_1B_1$ 3.  $T_3 = \gamma T_2 = i\left(t_{2,0} + t_{2,1}i\right) = \beta t_{2,1} + t_{2,0}i$ 4.  $C_0 = T_1 + T_3 = A_0B_0 + \gamma A_1B_1$ 5.  $T_3 = T_1 + T_2 = A_0B_0 + A_1B_1$ 6.  $T_1 = A_1 + A_0$ 7.  $T_2 = B_1 + B_0$ 8.  $T_4 = T_1T_2$ 9.  $C_1 = T_4 - T_3$ Total cost of the operation:  $3F_{q^2}$  multiplication +  $1F_q$  multiplication +  $5F_{q^2}$  addition

#### 2.2.4 Elliptic Curve Arithmetic on Projective Coordinates

We use Jacobian mixed coordinate system since in Algorithm 1, point P is in affine coordinate system. This coordinate system is more effective than other projective coordinate systems in terms of overall (both doubling and addition) operation count [45]. Another reason for using projective coordinate systems is to eliminate division (inversion), which is the most time consuming operation, in affine coordinate systems. A point  $T = (x_1, y_1, z_1)$  in projective coordinate system corresponds to the point  $P = (x_1/z_1^2, y_1/z_1^3)$  in affine coordinate system. Point doubling formulas for point  $P = (x_1, y_2, y_3, z_4)$  for the curve  $P = x_3 + ax_4 + b$  is given as follows.  $P = (x_2, y_3, z_4)$  then  $P = (x_3, y_4, z_4)$  for the curve  $P = x_3 + ax_4 + b$  is given as follows.  $P = x_4 + ax_4 + b$  is given as follows.  $P = x_4 + ax_4

$$x_{c} = \lambda_{2A}^{2} - 8x_{A}y_{A}^{2}$$

$$y_{c} = \lambda_{2A}(4x_{A}y_{A}^{2} - x_{C}) - 8y_{A}^{4}$$

$$z_{C} = 2y_{A}z_{A}$$

Addition formula for points  $A = (x_A, y_A, z_A)$  and  $B = (x_B, y_B, 1)$  where  $C = A + B = (x_C, y_C, z_C)$  and  $\lambda_{A,B} = (y_A - z_A^3 y_B)$  is the slope of line AB.

$$z_{C} = (z_{A}^{2}x_{B} - x_{A})z_{A}$$

$$x_{C} = (y_{A} - z_{A}^{3}y_{B})^{2} - (z_{A}^{2}x_{B} + x_{A})(x_{A} - z_{A}^{2}x_{B})^{2}$$

$$y_{C} = z_{C}^{2}\lambda_{AB}(z_{C}^{3}x_{B} - z_{C}x_{C}) - z_{C}^{3}y_{B}$$

Please note that denominators of the results are not given because, denominator of f goes to 1 at the end of the algorithm thanks to denominator elimination property. So we never compute denominators.

#### 2.2.5 Line Evaluation Function

The function denoted by  $l_{A,B}(Q)$  in Algorithm 1 is known as *line evaluation* function. Geometrically it is the distance between the point Q and the line that intersects the points A and B [36]. Formulas related to  $l_{A,B}(Q)$  and  $l_{A,A}(Q)$  are given as follows:

$$l_{A,B}(Q) = (y_0 z_A^3 - y_A) z_C - \lambda_{A,B} (x_0 z_A^3 - x_A z_A)$$

Formula for  $l_{A,A}(Q)$  is the same as above except that  $\lambda_{2A}$  is used instead of  $\lambda_{A,B}$ . As might be remembered  $Q=(x_Q,y_Q)$  is in  $E(F_{q^k})$ , and therefore, line computation involves arithmetic in  $E(F_{q^k})$ , which is costly. However, there is a trick to make the computation of line evaluation much easier. Instead of using the full point Q on  $E(F_{q^k})$ , we can use the twist of  $E(F_{q^k})$  in a smaller field such as  $E'(F_{q^{k/d}})$ , where d is a proper integer that divides k. The elliptic curve  $E'(F_{q^{k/d}})$  can be called as the twist of  $E(F_{q^k})$  if there exists an isomorphism between them such that  $\psi \colon E'(F_{q^{k/d}}) \to E(F_{q^k})$  [37]. Since our embedding degree is 4 we can choose d as 2 and in this case twist is named as  $quadratic\ twist$ , which is defined as follows:

$$E'(F_{q^2})$$

:  $y^2 = x^3 + aw^{-2}x + bw^{-3}$ ,  $a, b \in F_q$ ;  $w \in F_{q^2}$

where w is a quadratic non-residue in  $F_{q^2}$  thus  $\sqrt{w} \in F_{q^4}$  and the isomorphism is given by [38]:

$$\psi_2 : \begin{cases} E'(F_{q^2}) \to E(F_{q^4}) \\ (x, y) \to (xw, yw^{3/2}) \end{cases}$$

Thus by using the twist curve, we can choose coordinates of the point Q on  $F_{q^2}$  instead of choosing them on  $F_{q^4}$ . The twisted coordinates  $y_Q^{'}, x_Q^{'} \in F_{q^2}$  are the coordinates on twist such that  $y_Q^{'} = (0+0i) + (y_{Q_{10}}^{'} + y_{Q_{-11}}^{'}i)I$  and  $x_Q^{'} = (x_{Q_{00}}^{'} + x_{Q_{01}}^{'}i) + (0+0)I$  where  $I = \sqrt{i} = \sqrt{\gamma} \in F_{q^4}$  as can be remembered from section 2.2.3. So the line evaluation formula given above can be expressed as below:

$$l_{AB}(Q) = (-\lambda_{AB} z_A^3 x'_O - x_A z_A \lambda_{AB} - z_C y_A) + (z_A^3 z_C y'_O) I$$

Note that an element of  $F_{q^4}$  is represented as  $A_0 + A_1 I$  where  $A_0, A_1 \in F_{q^2}$ .

#### 2.2.6 Final Exponentiation

Final exponentiation in Step 9 of Algorithm 1,  $f \leftarrow f^{(q^k-1)/r}$ , can be reduced to two smaller hard exponentiations with the help of property described in [16]. Exponent  $(q^4-1)/r$  is separated into two parts;  $(q^2-1)$  and  $(q^2+1)/r$ . The method for performing the final exponentiation using these two parts is described below.

Let's write  $f = F_0 + IF_1$  such that  $F_0, F_1 \in F_{q^2}$ . We can handle the first exponent operations with  $(q^2 - 1)$  as follows:

$$t = f^{q^2 - 1} = (F_0 + IF_1)^{q^2 - 1}$$

$$= (F_0 + IF_1)^{q^2} (F_0 + IF_1)^{-1}$$

$$= (F_0 + I^{q^2} F_1) (F_0 + IF_1)^{-1}$$

$$= (F_0 - IF_1) (F_0 + IF_1)^{-1} [16].$$

If we include the other exponent  $(q^2 + 1)/r$  we obtain

$$f^{(q^4-1)/r} = t^{(q^2+1)/r} = t^{k_1q+k_2},$$

where  $k_1=[(q^2+1)/r]/q$ ,  $k_2=[(q^2+1)/r]\ mod\ q$  and  $t\in F_{q^4}$ ,  $t=(T_0+IT_1)$  such that  $T_0,T_1\in F_{q^2}$ .

The first part of  $t^{k_1q+k_2}$  can be calculated as follows:

$$s = t^{q} = (T_{0} + IT_{1})^{q} = (T_{0}^{q} + I^{q}T_{1}^{q})$$

$$= (t_{00}^{q} + i^{q}t_{01}^{q}) + I^{q}(t_{10}^{q} + i^{q}t_{11}^{q})$$

$$= (t_{00} - it_{01}) + I^{q}(t_{10} - it_{11})$$

where  $I^q = I^{q-1}I$  and  $Fr = I^{q-1} = (I^2)^k = i^k \in F_{p^2}$ .

$$s = (t_{00} - it_{01}) + Fr * (t_{10} - it_{11}) * I = S_0 + IS_1$$

Finally we have

$$f^{(q^4-1)/r} = s^{k_1} * t^{k_2}.$$

Two small exponentiations with exponents  $k_1$  and  $k_2$  are realized separately with basic binary exponentiation method [39] or using simultaneous exponentiation algorithm.

During calculation of variable t, one  $F_{q^4}$  inversion is computed. A  $F_{q^4}$  inversion can be reduced into  $F_{q^2}$  inversion and couple of multiplication in the subfield  $F_{q^2}$ . Since we use tower construction for extension fields, one inversion in  $F_{q^2}$ , in turn, can be written in terms of an inversion in  $F_q$  as described in Algorithm 6.

```

Algorithm 6: F_{q^2} Inversion Using F_q Inversion

Inputs: a = a_0 - a_1 i, a_0, a_1 \epsilon F_p

Output: b = a^{-1}, b = b_0 + b_1 i

1. t_1 = a_1 a_1

2. t_2 = \beta t_1

3. t_1 = a_0 a_0

4. t_3 = t_1 - t_2

5. t_4 = t_3^{-1}

6. b_0 = a_0 t_4

7. b_1 = -a_1 t_4

- Total cost of the operation: 5F_q multiplication + 1F_q inversion + 2F_q addition

```

Finally, a  $F_{q^4}$  inversion is realized using a  $F_{q^2}$  inversion as described in Algorithm 7.

# Algorithm 7: $F_{q^4}$ Inversion Using $F_{q^2}$ Inversion

```

Inputs: A = A_0 + A_1 I; A_0, A_1 \in F_{q^2}

Output: B = A^{-1}, B = B_0 + B_1 I such that B_0, B_1 \in F_{q^2}

1. T_1 = A_1 A_1

2. T_2 = \gamma T_1

3. T_1 = A_0 A_0

4. T_3 = T_1 - T_2

5. T_4 = T_3^{-1}

6. B_0 = A_0 T_4

7. T_1 = -A_1

8. B_1 = T_1 T_4

- Total cost of the operation: 5F_{q^2} multiplication + 1F_{q^2} inversion + 2F_{q^2} addition

```

In the following section hardware architecture of the design is explained.

# 3 Parametric and Compact Implementation of Hardware Coprocessor for Pairing on FPGA

Public key cryptosystems such as elliptic curve and pairing-based cryptography require complicated arithmetic operations. For example an  $F_{q^2}$  multiplication requires 3  $F_q$  multiplications and several  $F_q$  additions and if the extension degree is increased, the operation becomes much more complex and time consuming. For instance, if the extension degree is increased to four, a multiplication on  $F_{q^4}$  requires 12  $F_q$  multiplications. Since operations on extension fields are too complicated and require a diverse set of operations in the subfields, separate implementation of each operation in hardware may require prohibitively high logic area which makes software implementation preferable.

If implementation of these operations is realized on dedicated hardware, ASIC, for mostly speed concerns, it has some disadvantages compared to reconfigurable solutions as enumerated in the following:

- 1. Probably, the most problematic part of ASIC design is its cost; production of an ASIC design is many times more expensive than production of a design on FPGA, depending on the volume of the production.

- 2. Production of ASIC designs takes again much longer than making a design usable on FPGA (time-to-market factor).

- 3. Design and improvement of ASIC implementations takes much longer compared to the FPGA alternative.

- 4. If security levels or overall system architecture changes, ASIC no longer can be used and a new design and production are required.

5. As name implies, it is most of the time "dedicated" and cannot be used for any other purposes.

In this design, we make use of both the advantage of software and the flexibility of reconfigurable hardware designs. As indicated above, separate implementations of extension field operations may require too much logic area. Moreover, if the design choices change for some reasons (e.g. security, performance, compatibility), a specific unit computing a particular operation can become obsolete and requires re-design. For instance, if a dedicated unit is designed for solely  $F_{q^4}$  multiplication, and when the design is modified from  $F_{q^4}$  to  $F_{q^8}$  it becomes useless. Instead, we design and implement a programmable coprocessor on FPGA having basic arithmetic logic operation unit in its center, which is highly optimized for the target device. Thus, by changing the program of the coprocessor, many different operations can be performed on a simple reconfigurable hardware.

Our coprocessor is designed mainly for pairing operations; several pairing types such as Tate, Ate, on arbitrary elliptic curves can be calculated by simply changing the program of the processor. There is no need to change the hardware design. Other cryptographic calculations can also be implemented but some changes in state machines of the control circuit are needed. It is worth to note that, adapting processor for most of the other types of cryptographic applications can be realized by just modifying the control state machine, not all the design. So even if this processor is designed essentially for pairing operation, it can be adjusted for other applications with relatively small effort compared to designing it from the scratch. At this point we can see the advantages of this design over the pure software and ASIC solutions:

- 1. It is relatively cheap and easy to design, test and implement when compared to ASIC realizations.

- 2. It can be reconfigurable easily for different applications and design preferences whereas, ASIC cannot be.

- 3. It is much faster than software and it saves valuable CPU time for other operations

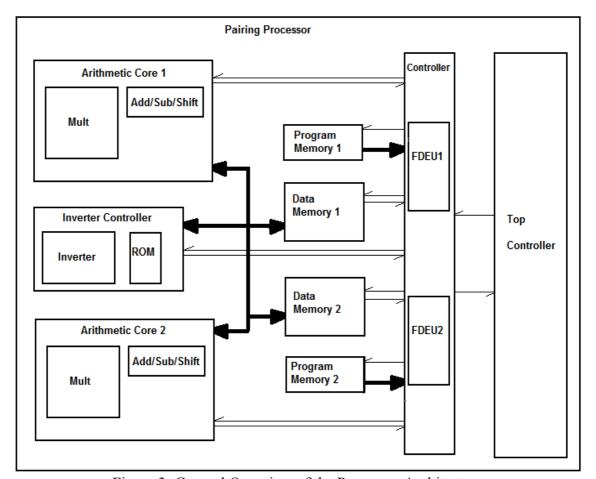

Performance and flexibility of the design is supported by the underlying architecture. General architecture of the design can be grouped into five parts: i)

arithmetic logic unit with modular inversion block, **ii**) fetch-decode-execute unit, **iii**) top controller, **iv**) program memory and **v**) data memory. Sub-modules of the processor can be briefly described as follows:

- Arithmetic Core & Inversion Unit (ACIU): Arithmetic core is composed of a modular adder-subtractor unit and a Montgomery multiplier unit. We have two arithmetic cores in the design, which makes our processor dual-core. In addition, we have a single inversion unit that computes multiplicative inverses in  $F_q$ .

- ➤ Fetch-Decode-Execute Unit (FDEU): This unit controls the program memory, data memory and ACIU. Since we have two arithmetic cores, to make it fully parallel we used two FDEU, each of which is connected to one ACIU.

- ➤ Top Controller: Top controller is the state machine that defines the characteristic of the processor. Namely, we design our top controller specifically for pairing operation. And for other kinds of applications it has to be modified but except for this module, other parts can still be used without any modification. There exists only one top controller that controls all the submodules.

- ➤ **Program Memory**: As the name indicates, this is the memory where the program code (it will be referred as "micro-code") is stored. To make use of full parallelism, this part is also instantiated for each FDEU.

- ➤ Data Memory: This part constitutes register banks used to store program data. Similar to program memory, each FDEU has its own data memory. Naturally, data transfers among FDEUs are allowed to combine the result of each core to a single one.

To summarize, a specialized Top Controller unit commands FDEUs to execute a block program (can be referred as function or micro-code henceforth), then FDEUs fetch that program (micro)-instructions from the program memory. After instructions are fetched, the FDEUs parse the instructions into three parts: Operation type, address of the operands and the address of which the operation result will be written. Then FDEU fetches the required data from the data memory and commands ACIU to execute

a given operation with given data. When ACIU finishes its operation, the result is sent to the data memory area which is pointed by the instruction. General overview of the co-processor architecture is depicted in Figure 3.

Figure 3: General Overview of the Processor Architecture

In Figure 3, bold lines represent a bus which carries both data bits and the control signals, the thin lines denotes buses that carry only control signals.

There are some other points that need further explanation. Firstly, inverter is capsulated into a controller and it has a separate program ROM. Secondly, FDEUs are encapsulated into a single controller unit. And eventually, FDEUs do not have direct connection with the data memory; instead they only have control lines. These are adopted design preferences here and will be clarified in the subsequent chapters.

Top controller informs the controller to execute a specific block of micro-code (BMC). If a function is parallelizable and if it is coded in a parallel manner, then for that function there will be a micro-code in both of the program memories for the corresponding block of the code. So when commands come from top controller, FDEUs

read the corresponding BMC from the program ROM and begin to execute them in a parallel manner. Program memory is filled by the programmer with micro-code of the processor before the execution. Data input is transferred to the controller via program memory. The controller does not directly handle the input and the output data to ACIUs; rather it handles the switching of data. Thus, ACIU can read and write data directly, which is much faster. This method can be considered as micro-DMA (direct memory access). We add the word "micro" because in normal DMA, the processor does not participate in data transfer and thus can deal with other processes while peripherals makes memory access faster. But in our case, the data transfer happens within the processor, hence the name micro-DMA. Yet, if we consider the controller as a processor, we can say that this method makes data access faster for ACIUs through a shortcut to the data memory. Although controller starts the transfer operation, it does not carry data blocks over itself to ACIU.

After the execution is performed by the ACIUs, the controller returns a done signal to the top controller which becomes ready for the next functions. At the end of all operations, top controller raises a finish flag and result is accessible in the predetermined address of the data memory. Last, but not least point is about the choice of RAM type to implement data memory. It is designed as dual port RAM, which allows simultaneous read operations. The reason that makes this choice is important is related to the arithmetic core. Since, the arithmetic cores use two operands for most operations, such as multiplication, addition and subtraction, it requires that operands be ready at both input ports at the same time. So, dual port RAM is a compact solution for the requirement.

ACIU includes multiplier, adder/subtractor/shifter and inverter. In fact, multiplier and inverter unit could be implemented by using just adder/subtractor/shifter unit, but this case would have two drawbacks. First, writing a program for the processor for this purpose would be too complicated. Secondly, total execution time for a cryptographic operation would be affected badly although working frequency does not change. What makes the execution time longer is that the control mechanism and data transfer cycle at each step of the multiplication and inversion algorithms. Especially, when we consider that the size of operands is around hundreds of bits, the effort needed for data transfer cycles would be prohibitively high. Because of this reason, multiplication and inversion

units are realized in hardware in highly optimized fashion. Detailed description of each sub module is explained in the following sections.

#### 3.1 Arithmetic Core & Inversion Unit

ACIU composed of two main parts: arithmetic cores and inversion controller. These two parts are detailed in following two sub sections.

#### 3.1.1 Arithmetic Core

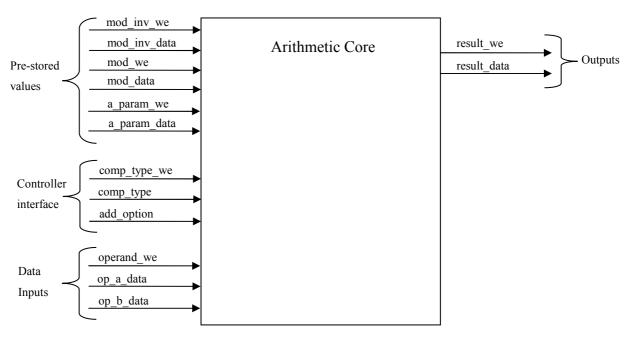

Arithmetic core composed of two components: multiplier and adder/subtractor/shifter block. Instead of making a separate shifter, adder is also used as a shifter. Before going further into details of the sub modules, we explain general overview of the arithmetic core itself and I/O signals that belong to the core.

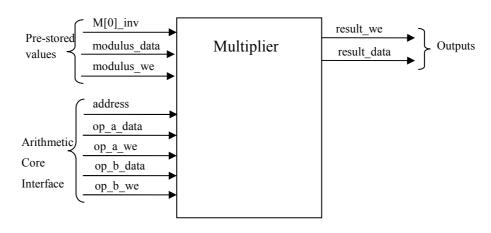

Arithmetic core is designed to present a user friendly interface to the controller and to gain speedup during the most common instructions. Arithmetic core accommodates a state machine between the controller and operation units as an interface. With the help of this interface, the controller can communicate easily and efficiently with the arithmetic cores. The controller interacts with the arithmetic cores using commands which also constitute the opcode part of the micro code. The controller sends its command and then adjusts the data memory address to provide the appropriate operands to the arithmetic cores. After the result is found, data is written to indicated part of the data memory directly by the arithmetic core, which also sends a signal to the controller to indicate that operation is completed. I/O interface of the arithmetic core is depicted in Figure 4.

Figure 4: Arithmetic Core I/O Interface

Pre-stored values that are constant and frequently used during the operations should be stored in the arithmetic core before the execution of any operation. Therefore, pre-stores values are kept in a RAM inside of the arithmetic core. Storing these values inside the arithmetic core reduces the load over the controller per operation. For example, the controller is saved from loading the modulus at every operation.

As can be seen in Figure 4, the controller interface is pretty simple; controller should load the "opcode" along with an "enable" signal. This signal takes one clock period. An additional input is used to tell the arithmetic core whether to make addition or subtraction.

Data is fed into the core directly from the data memory. Decision about the location of data is made by the controller. After opcode is stored in the core, operands come from the data memory with the help of switching of the controller. Finally, when the result is produced it is directly written in the data memory by the core. Again the data bus switched to the correct location by the controller just after the loading of opcode. Only a signal is sent to the controller to indicate that the operation is finished.

Determining the possible opcodes is the focal point in the arithmetic core design. The operations that are performed often are made an opcode. For example, if squaring is executed many times or if it might be used frequently in other applications, then squaring can be made an opcode. Thus, we get rid of read and write cycles every time in

certain and commonly used operations. Again, there is a trade-off between time and area. If this kind of optimization were not made in the opcode selection, the core would be much simpler. However we prefer to improve the execution time of the overall system. Below a list of opcodes is given in Table 2.

| Opcode | Definition                                                 |

|--------|------------------------------------------------------------|

| 0000   | Idle: Do nothing                                           |

| 0001   | $c = a \times b$ : Regular multiplication                  |

| 0010   | c = a + b: Regular addition                                |

| 0011   | c = a + a: Regular shift left once                         |

| 0100   | $c = 3 * (a * b)$ : First $a \times b$ , then two addition |

| 0101   | $a^2 \times b$ , $b^2 \times a$ , $a^3$                    |

| 0110   | A*a*b                                                      |

|        | A is elliptic curve coefficient a in $y^2 = x^3 + ax + b$  |

| 0111   | c = 2 * a * b: Multiply then add                           |

Table 2: Opcodes and their Definitions for Arithmetic Core

Arithmetic core can take a new opcode when it finishes the current operation. It is not allowed to load new opcode during an operation. Operands are fed into the core word by word and all the sub modules process the data on word-basis. Size of words is changeable. As can be seen from the Table 2, four bits are reserved for the opcode while most significant bit is always zero. This is optional part. Opcodes can be extended with some changes in the core logic for different kinds of applications. Detailed explanation about the building blocks of the core is given in the following subsections.

#### 3.1.1.1 Multiplication Module

Since Montgomery [40] offered one of the most efficient methods for hardware multiplication, this block is designed to implement Montgomery multiplication. Selection of this block as a Montgomery multiplier (MM), affects also the choice of inverter and the way data is given to circuit. The MM produce a result for given inputs "a" and "b",  $MM(a, b, M) = a \times b \times R^{-1} \pmod{M}$ , where R is constant and usually

chosen as  $R = 2^{modulus\ bit\ length}$ . For this reason, our arithmetic units accepts operands in Montgomery domain (i.e.  $a \times R$  instead of just a,) to avoid information loss.

The MM is taken from a previous work [41]. It is a generic architecture and uses Coarsely Integrated Operand Scanning (CIOS) Montgomery Multiplication algorithm:

```

Algorithm 8: CIOS Montgomery Multiplication Method [42]

Inputs: a[j], b[j]: jth. word of operands (w bits each)

M[j]: j<sub>th.</sub> word of modulus (w bits each)

k: Number of words in the operands and modulus

W: 2^{w}, C: carry, S: sum

M[0]<sup>-1</sup>: multiplicative inverse<sup>1</sup> of M[0]

|  : used for concatenation

:= 0

t

Output: t[i]:= intermediate and final results

1. for i=0 to k-1

C := 0

for j=0 to k-1

C||S := t[j] + a[j] \times b[i] + C

t[j] := S

C | | S := t[k] + C

6.

7.

t[k] := S

8. t[k+1] := C

9.

:= 0

С

:= t[0] \times (-M[0]^{-1}) \mod W

10.

11.

C||S := t[0] + M[0] \times z

12. for j=1 to k-1

13.

C||S := t[j] + M[j] \times z + C

t[j-1] := S

14.

15.

C \mid \mid S := t[k] + C

16.

t[k-1] := S

17.

t[k] := t[k+1] + C

```

The CIOS method is a word based method as can be seen in Algorithm 8. It takes and processes the operands word by word and it forms the result in the same

-

<sup>&</sup>lt;sup>1</sup> "Least significant word of inverse M" in mod  $2^r$  where  $2^{r-1} < M < 2^r$

manner. The CIOS is one of the most efficient algorithms for implementing the MM on FPGA [42].

Algorithm 8 is implemented in a pipelined manner to take advantage of parallelism and to speed up the design in FPGA. It makes use of hardwired multiplier blocks in the FPGA thus, both gains from logic area and provides acceleration in multiplication operations. The design is very flexible and parametric. Number of pipeline stages, number of bits in each word and number of words in operands can be adjustable. Therefore it provides time-area trade-off. For example, area can be reduced by decreasing both the number of pipeline stages and the number of bits a word. In return, the total execution time increases. This kind of design is very helpful for adjusting overall time-area trade-off because multiplication is the most commonly used operation in the pairing. Changes in its timing characteristics affect total timing of the application in a substantial manner. In Figure 5, I/O interface of the multiplication until is given:

Figure 5: Montgomery Multiplier I/O Interface

Pre-stored values are stored into the module before the calculation starts. Each input operand has separate load inputs. Thus, for some operations as indicated in the opcode, such as "0101", as one operand from previous calculation remains intact, the other operand takes a new value. Address input specifies the address in the RAM where the operands are stored. This input is automatically increased by the arithmetic core. When calculation finishes, the result becomes available with an active write enable signal. Output of the multiplier is switched as indicated in the opcode by the core.

#### 3.1.1.2 Addition/Subtraction/Shifter Module

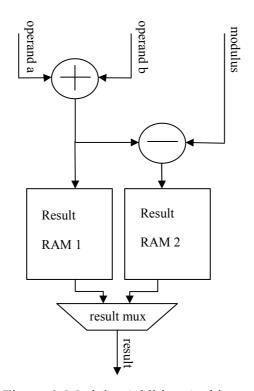

All three modules (i.e. adder, subtractor and shifter) are realized in the same unit. Although it is normal to have adder and subtractor together, we prefer to implement shifter using addition. This has two reasons: Firstly, it makes the control circuit simpler, secondly even if we use normal shifter, we need a modular adder since we must guarantee that after shift operation result may have to be reduced since this is a modular shift operation (i.e. shift operation in  $F_q$ ). Inner structure of the modular adder is given in Figure 6.

Figure 6: Modular Addition Architecture

Figure 6 is an illustration of modular addition, and in case of the subtraction operation, the adder (+) and subtractor (-) units are switched. Operation immediately starts with the load of operands. Operands are added and stored into RAM 1 and modulus is subtracted from the addition of the operands and stored into the RAM 2. Both operands and the modulus fed into the module word by word, and carry-out from the previous word is fed into the next word as carry-in. After all the words are exhausted, carry-out of the last word is examined. If the result of subtraction with the modulus M (i.e. a + b - M) is negative then, it is concluded that a + b < M and result in

the RAM 1 is valid and vice versa otherwise. The reason of using two RAMs is providing the result immediately after the data load finishes.

We use registers between the two adders to break the long delay in the critical path. Other than that we do not make anything to speed up the adders. This is due to the fact that, while synthesizing the adder the router automatically places the logic around the fast carry propagate lines hence, it does not create a bottleneck for the design.

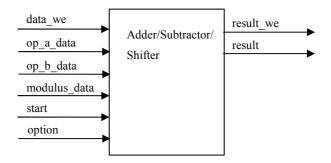

Adder is also parametric like the other parts of the design. Input word bit length and the total input word number can be adjusted. I/O interface of the adder is shown in Figure 7.

Figure 7: Modular Addition I/O Interface

The "option" input is used to alternate from subtractor to adder; the "start" input is used to start the output stream. This input is utilized to postpone the output in case of such a need occurs in timing adjustment. To start an operation, the modulus and the operand data should be given with an active write enable signal. For every operation modulus data is fed into the module and start signal is adjusted automatically by the core.

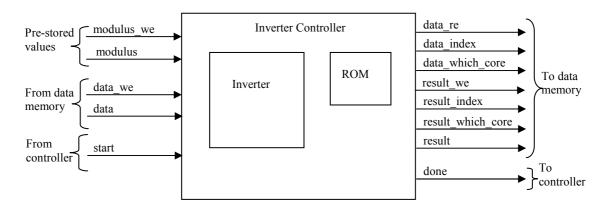

#### 3.1.2 Inverter Controller

Inversion is used in the final exponentiation part of the pairing. Although it is not used many times, it plays a critical role to reduce the execution time spent on the final exponentiation. The execution time of extension field exponentiation is halved if a dedicated inversion unit is used. We prefer to add an inverter unit to make use of the

advantage it brings in timing with the cost of some logic area. Since inversion is a rare operation, instead of inserting it to the arithmetic core we build a single inversion unit.

During the execution of a functional block for inversion operation, control of the data memory is left to the inverter controller. Inverter controller possesses its own internal program ROM. Every time it is notified by the controller, it executes the micro code coming up next. It reads data and writes the result to the specified addresses.

The structure of the inverter controller is highly simple. It has a state machine to control the read/write operations to the data memory and it switches data in and out of the inversion. The I/O interface of the inverter controller is given together with inner block diagram in Figure 8.

Figure 8: Inverter Controller I/O Interface

Inverter controller starts operation with the active "start" signal from the controller. It reads micro code from the ROM and sends the address of data to be read to the data memory. After the result is obtained it is written to the data memory, then the controller is sent a an active "done" signal.

Inverter controller has two sub modules; ROM and inverter. ROM is either synthesized with "Block RAM (BRAM)", which is a hardwired RAM in the FPGA, or is synthesized using "Distributed RAM", which is a RAM constructed of look-up tables (logic elements) in the FPGA. We picked distributed RAM since, usually work load of the inverter is low and thus it does not need a large memory to store the micro code. Certainly, inversion circuit is the most important part. It is detailed in the following subsection.

#### 3.1.2.1 Montgomery Inverter Module

Modular inversion is widely used in cryptographic applications particularly in public-key crypto-system. For instance, during the calculation of private key in Digital Signature Standard [43] and in RSA [44] and in elliptic curve cryptography, [46]-[48], it is commonly used. For this reason, inversion module is a must for not just pairing operation but also for a cryptographic processor. Thus, we design a low area and parametric modular inverter optimized for FPGA devices. During the design, to eliminate the delays of long carry chains, we favor the word-based design and move away from full precision adders and subtractors. We process the data similar to a general-purpose computer, on word-basis and we make use of the advantage of the FPGA. We use the Montgomery modular inversion algorithm to make it compatible with the Montgomery multiplier. We tested efficiency of the design on Xilinx Spartan-6 FPGA, which is a new generation of low cost FPGA with low power consumption. Implementation results show the design reaches frequencies higher than 200 MHz with a few hundreds of logic resources.

Modular inverse on modulo M, where M is an odd prime, is defined as follows: If  $z, x \in [1, M-1]$  and  $z * x \equiv 1 \pmod{M}$  then, z and x are multiplicative inverse of each other in modulo M. It is displayed as  $x \equiv z^{-1} \pmod{M}$  [50]. Montgomery inverse algorithm is first proposed by Kaliski [49], which works fine with MM.

Generally inversion is used together with other arithmetic operations in cryptography. By looking at its usage ratios in overall application, satisfying high working frequency with high area usage is not acceptable for the inverter design. Since, it is usually not timing bottleneck for most cryptographic applications. On the other hand, its working frequency should not be lower than the multiplier unit in order not to reduce the entire working frequency of the system. As a result, the aims are a low area and a fast inverter module.