# POWER CONSUMPTION REDUCTION TECHNIQUES FOR H.264 VIDEO COMPRESSION HARDWARE

by Yusuf Adıbelli

Submitted to the Graduate School of Engineering and Natural Sciences

in partial fulfillment of the requirements for the degree of Doctorate of Philosophy

Sabancı University

August 2012

## POWER CONSUMPTION REDUCTION TECHNIQUES FOR H.264 VIDEO COMPRESSION HARDWARE

APPROVED BY:

Assist. Prof. Dr. İlker Hamzaoğlu (Thesis Supervisor)

Prof. Dr. Onur Toker

Assist. Prof. Dr. Hakan Erdoğan

Assist. Prof. Dr. Müjdat Çetin

Assoc. Prof. Dr. Albert Levi

Nelijan Ang dete

DATE OF APPROVAL:

03 August 2012

© Yusuf Adıbelli 2012 All Rights Reserved To my Mother, Father and Sisters To my beloved wife Hümeyra

### ACKNOWLEDGEMENT

I would like to thank my supervisor, Dr. İlker Hamzaoğlu for all his guidance, support, and patience throughout my PhD study. I appreciate very much for his suggestions, detailed reviews, invaluable advices and life lessons. I particularly want to thank him for his confidence and belief in me during my study. It has been a great honor for me to work under his guidance.

I would also like to thank my thesis committee members Dr. Onur Toker, Dr. Hakan Erdoğan, Dr. Müjdat Çetin and Dr. Albert Levi for participating in my thesis jury.

I like to convey my heartiest thanks to Mustafa Parlak and his wife Neslihan Parlak for their unlimited support, encouragement. It is very heartwarming to know that one has such friends.

My sincere thanks to System-on-Chip Design & Test group members, Mert Çetin, Merve Peyiç, Çağlar Kalaycıoğlu, Onur Can Ulusel, Aydın Aysu, Abdulkadir Akın, Tevfik Zafer Ozcan, Serkan Yalıman, Kamil Erdayandı, Yusuf Akşehir, Ercan Kalali and Erdem Özcan.

My sincere thanks to all my friends and colleagues in Sabancı University including Mehmet Özdemir, Alisher Kholmatov, Ünal Şen and İbrahim İnanç. I appreciate their friendship and help which made my life easier and more pleasant during my PhD study.

I also would like to express my deepest gratitude to my friends; Malik Sina, Zeynep and Ozgur for their unlimited support, encouragement. It is very heartwarming to know that one has such friends.

I am particularly grateful to my parents and my wife, Hümeyra, for their constant support, encouragement, assistance and patience. Without them, this study would never have been possible.

Finally, I would like to acknowledge Sabancı University and Scientific and Technological Research Council of Turkey (TUBITAK) for supporting me throughout my graduate education.

## POWER CONSUMPTION REDUCTION TECHNIQUES FOR H.264 VIDEO COMPRESSION HARDWARE

Yusuf Adıbelli Electronics, Ph.D. Dissertation, 2012

Thesis Supervisor: Asst. Prof. İlker HAMZAOĞLU

Keywords: H.264, Intra Prediction, Deblocking Filter, Mode Decision, Template Matching

### ABSTRACT

Video compression systems are used in many commercial products such as digital camcorders, cellular phones and video teleconferencing systems. H.264 / MPEG4 Part 10, the recently developed international standard for video compression, offers significantly better compression efficiency than previous video compression standards. However, this compression efficiency comes with an increase in encoding complexity and therefore in power consumption. Since portable devices operate with battery, it is important to reduce power consumption so that battery life can be increased. In addition, consuming excessive power degrades the performance of integrated circuits, increases packaging and cooling costs, reduces reliability and may cause device failures.

In this thesis, we propose novel computational complexity and power reduction techniques for intra prediction, deblocking filter (DBF), and intra mode decision modules of an H.264 video encoder hardware, and intra prediction with template matching (TM)

hardware. We quantified the computation reductions achieved by these techniques using H.264 Joint Model reference software encoder. We designed efficient hardware architectures for these video compression algorithms and implemented them in Verilog HDL. We mapped these hardware implementations to Xilinx Virtex FPGAs and estimated their power consumptions using Xilinx XPower Analyzer tool. We integrated the proposed techniques to these hardware implementations and quantified their impact on the power consumptions of these hardware implementations on Xilinx Virtex FPGAs. The proposed techniques significantly reduced the power consumptions of these FPGA implementations in some cases with no PSNR loss and in some cases with very small PSNR loss.

## H.264 VİDEO SIKIŞTIRMA DONANIMI İÇİN GÜÇ TÜKETİMİ AZALTMA TEKNİKLERİ

## Yusuf Adıbelli Elektronik Müh., Doktora Tezi, 2012

Tez Danışmanı: Yrd. Doç. Dr. İlker HAMZAOĞLU

Anahtar Kelimeler: H.264, Çerçeve İçi Öngörü, Blok Giderici Filtre, Kip Seçimi, Şablon Eşleştirme

## ÖZET

Video sıkıştırma sistemleri, dijital kameralar, cep telefonları ve video telekonferans sistemleri gibi bir çok ticari üründe kullanılmaktadır. Yakın tarihte geliştirilmiş uluslararası bir standart olan H.264 / MPEG4 Part 10, kendinden önceki standartlara göre belirgin şekilde daha iyi sıkıştırma verimi sağlamaktadır. Ancak,bu kodlama kazancı hesaplama karmaşıklığı ve güç tüketimi artışını beraberinde getirmektedir. Taşınabilir cihazlar pil ile çalıştığı için, güç tüketimini azaltmak pil ömrünün uzamasını sağlayacaktır. Bunun yanında aşırı güç tüketimi, entegre devrelerin performansını düşürür, paketleme ve soğutma maliyetlerini arttırır, dayanıklılığını azaltır ve bozulmalarına sebep olabilir.

Bu tezde, H.264 video kodlayıcı donanımı modülleri olan çerçeve içi öngörü, blok giderici filtre, çerçeve içi kip seçimi algoritması ve şablon eşleştirmeli çerçeve içi öngörü algoritmaları için yeni hesaplama karmaşıklığı ve güç tüketimi azaltma teknikleri önerildi. Önerilen tekniklerin hesaplama miktarında yaptığı azalma H.264 referans yazılımı (JM) kullanılarak belirlendi. Bu video sıkıştırma algoritmaları için verimli donanım mimarileri tasarlandı ve donanım mimarileri Verilog HDL ile gerçeklendi. Ayrıca bu donanım uygulamaları Xilinx Virtex FPGA'lerine sentezlendi ve Xilinx XPower Analyzer yazılımı kullanılarak bu donanımların FPGA gerçeklemelerinin detaylı güç tüketim analizleri yapıldı. Daha sonra, önerilen teknikleri bu donanım uygulamalarına entegre edilerek, bu donanımların Xilinx Virtex FPGA'lerindeki güç tüketimine olan etkisi belirlendi. Önerilen teknikler bu FPGA uygulamalarının güç tüketiminde bazen hiçbir PSNR kaybı olmaksızın, bazen de çok küçük PSNR kaybına sebep olarak önemli azalmalara sebep olmuştur.

# **TABLE OF CONTENTS**

| ACH  | KNOWLEDGEMENT                                                    | V   |

|------|------------------------------------------------------------------|-----|

| 1    | ABSTRACT                                                         | VI  |

| 2    | ÖZETV                                                            | III |

| 3    | TABLE OF CONTENTS                                                | .X  |

| LIST | Г OF FIGURESХ                                                    | Ш   |

| LIS  | Γ OF TABLES                                                      | IV  |

| 1    | CHAPTER I INTRODUCTION                                           | 1   |

| 1.1  | H.264 Video Compression Standard                                 | 1   |

| 1.2  | Low Power Hardware Design                                        | 4   |

| 1.3  | Thesis Contributions                                             | 6   |

| 1.4  | Thesis Organization                                              | 9   |

| 2    | CHAPTER II PIXEL EQUALITY AND PIXEL SIMILARITY BASED             |     |

|      | COMPUTATION AND POWER REDUCTION TECHNIQUES FOR H.264 INTR        | А   |

|      | PREDICTION                                                       | 10  |

| 2.1  | H.264 Intra Prediction Algorithm                                 | 12  |

| 2.2  | Proposed Computational Complexity and Power Reduction Techniques | 25  |

| 2.3  | Proposed Intra Prediction Hardware Architecture                  | 41  |

| 2.4  | Power Consumption Analysis                                       | 42  |

| 3    | CHAPTER III DATA REUSE, PECR AND PSCR TECHNIQUES FOR             |     |

|      | COMPUTATION AND POWER REDUCTION IN H.264 INTRA PREDICTION        | 46  |

| 3.1 | Proposed Computational Complexity and Power Reduction Techniques | 47  |

|-----|------------------------------------------------------------------|-----|

| 3.2 | Proposed Intra Prediction Hardware Architecture                  | 56  |

| 3.3 | Power Consumption Analysis                                       | 59  |

| 4   | CHAPTER IV ENERGY REDUCTION TECHNIQUES FOR H.264                 |     |

|     | DEBLOCKING FILTER                                                | 62  |

| 4.1 | H.264 Adaptive Deblocking Filter Algorithm                       | 63  |

| 4.2 | Proposed Energy Reduction Techniques                             | 67  |

| 4.3 | H.264 DBF Hardware and Its Energy Consumption                    | 81  |

| 5   | CHAPTER V A NOVEL ENERGY REDUCTION TECHNIQUE FOR H.264           |     |

|     | INTRA MODE DECISION                                              | 89  |

| 5.1 | Proposed Energy Reduction Technique                              | 93  |

| 5.2 | Proposed 16x16 Intra Mode Decision Hardware Architectures        | 113 |

| 5.3 | Energy Consumption Analysis                                      | 115 |

| 6   | CHAPTER VI A NOVEL ENERGY REDUCTION TECHNIQUE FOR INT            | RA  |

|     | PREDICTION WITH TEMPLATE MATCHING                                | 119 |

| 6.1 | Proposed Computation and Energy Reduction Technique              | 122 |

| 6.2 | Proposed Intra Prediction with Template Matching Hardware        | 131 |

| 6.3 | Energy Consumption Analysis                                      | 136 |

| 7   | CHAPTER VII CONCLUSIONS AND FUTURE WORK                          | 139 |

| 8   | BIBLIOGRAPHY                                                     | 143 |

# **LIST OF FIGURES**

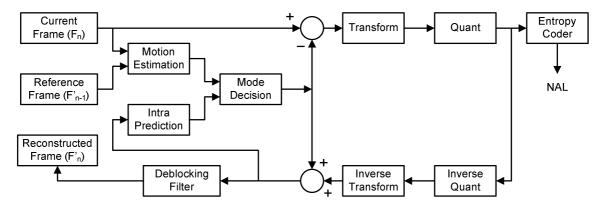

| Figure 1.1 H.264 Encoder Block Diagram   2                                                                                                                                                                                             |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 1.2 H.264 Decoder Block Diagram                                                                                                                                                                                                 |

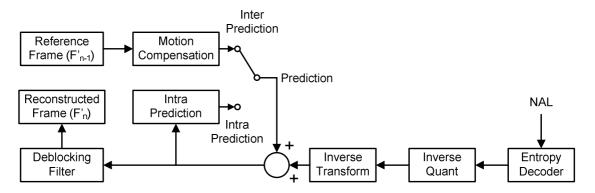

| Figure 2.1 A 4x4 Luma Block and Neighboring Pixels                                                                                                                                                                                     |

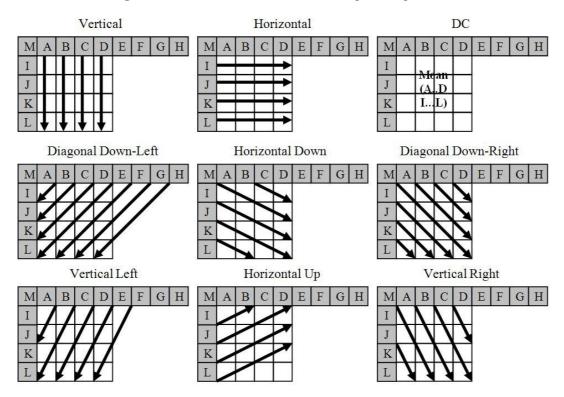

| Figure 2.2 4x4 Luma Prediction Modes    13                                                                                                                                                                                             |

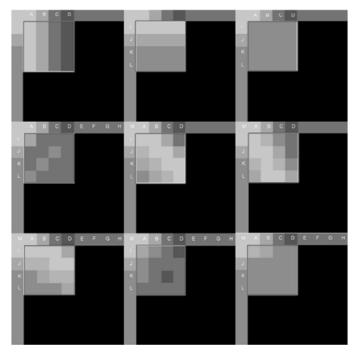

| Figure 2.3 Examples of Real Images for 4x4 Luma Prediction Modes                                                                                                                                                                       |

| Figure 2.4 Prediction Equations for 4x4 Luma Prediction Modes                                                                                                                                                                          |

| Figure 2.5 16x16 Luma Prediction Modes    18                                                                                                                                                                                           |

| Figure 2.6 Examples of Real Images for 16x16 Luma Prediction Modes                                                                                                                                                                     |

| Figure 2.7 Prediction Equations for 16x16 Luma Prediction Modes                                                                                                                                                                        |

| Figure 2.8 Chroma Component of a MB and its Neighboring Pixels                                                                                                                                                                         |

| Figure 2.9 Prediction Equations for 8x8 Chroma Prediction Modes                                                                                                                                                                        |

| Figure 2.10 Four Pixel Groups of Neighboring Pixels of a MB                                                                                                                                                                            |

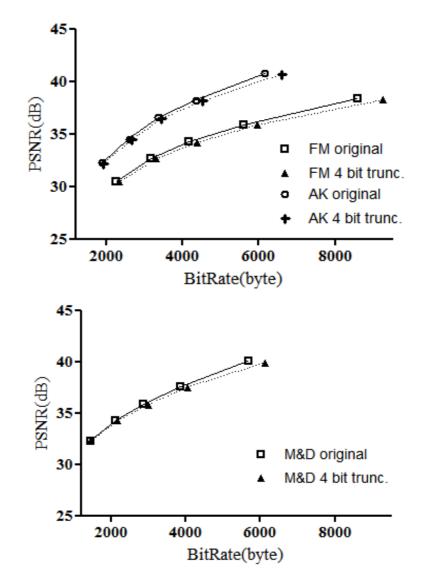

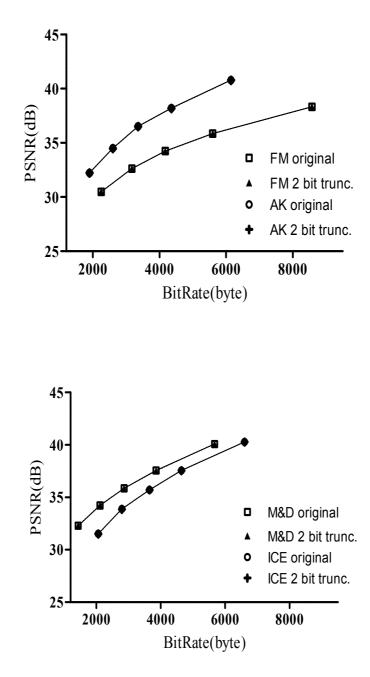

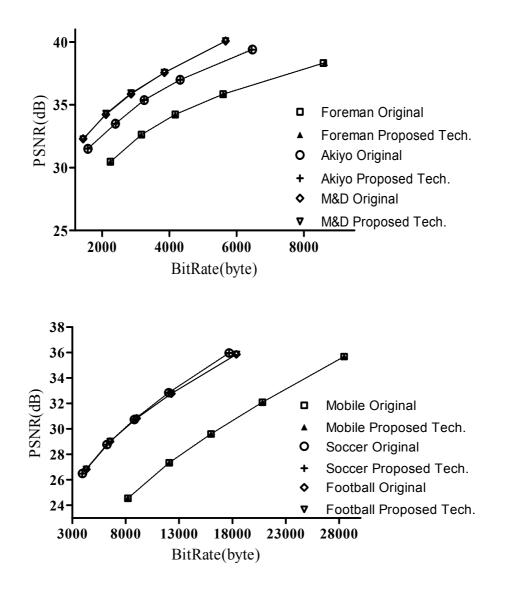

| <b>Figure 2.11</b> Rate Distortion Curves of the Original 4x4 Intra Prediction Algorithm and 4x4 Intra                                                                                                                                 |

| Prediction Algorithm with Proposed Technique                                                                                                                                                                                           |

| Figure 2.12 4x4 Intra Prediction Hardware Architecture    42                                                                                                                                                                           |

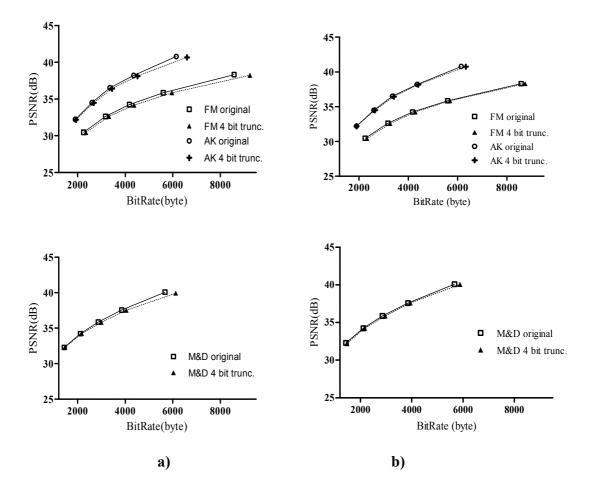

| <b>Figure 3.1</b> Rate Distortion Curves of the Original 4x4 Intra Prediction Algorithm and a) 4x4<br>Intra Prediction Algorithm with PSCR Technique proposed in [9] b) 4x4 Intra Prediction<br>Algorithm with Proposed PSCR Technique |

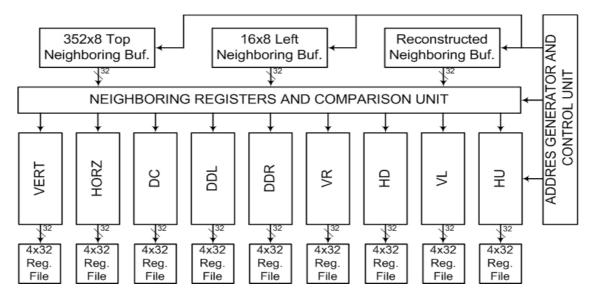

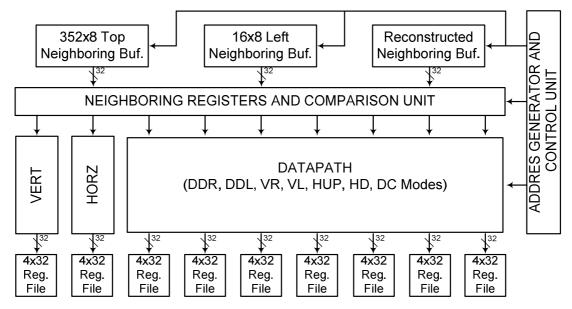

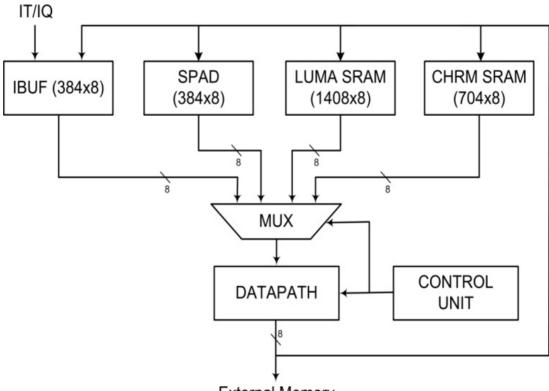

| Figure 3.2 Top-Level Block Diagram of 4x4 Intra Prediction Hardware Architecture                                                                                                                                                       |

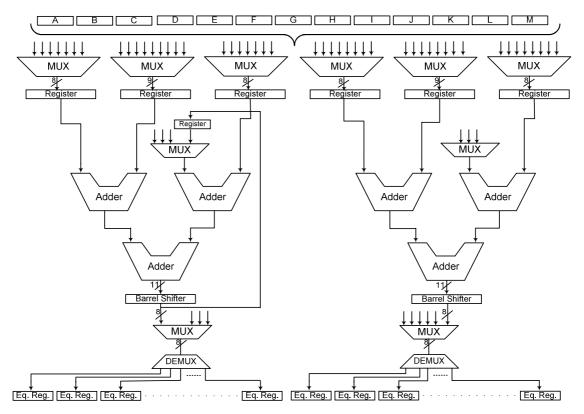

| Figure 3.3 Datapath for The Prediction Equations Used in DDL, DDR, VR, VL, HD, HUP and DC Modes                                                                                                                                        |

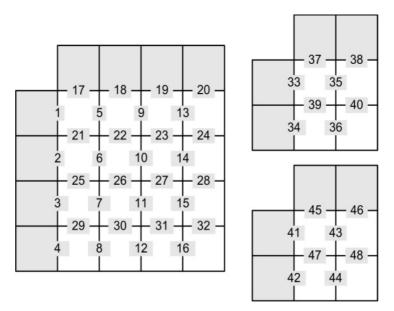

| Figure 4.1 Edge Filtering Order Specified in H.264 Standard                                                                                                                                                                            |

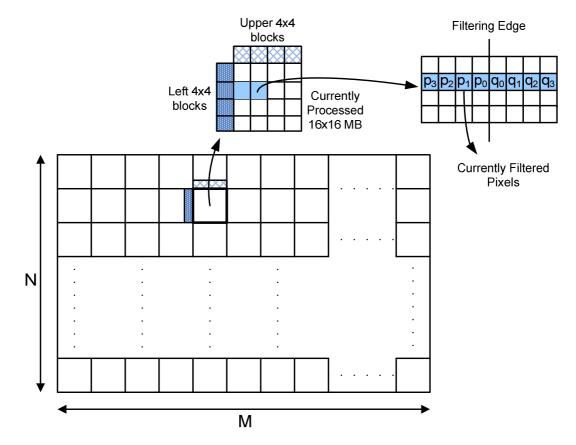

| Figure 4.2 Illustration of H.264 DBF Algorithm    65                                                                                                                                                                                   |

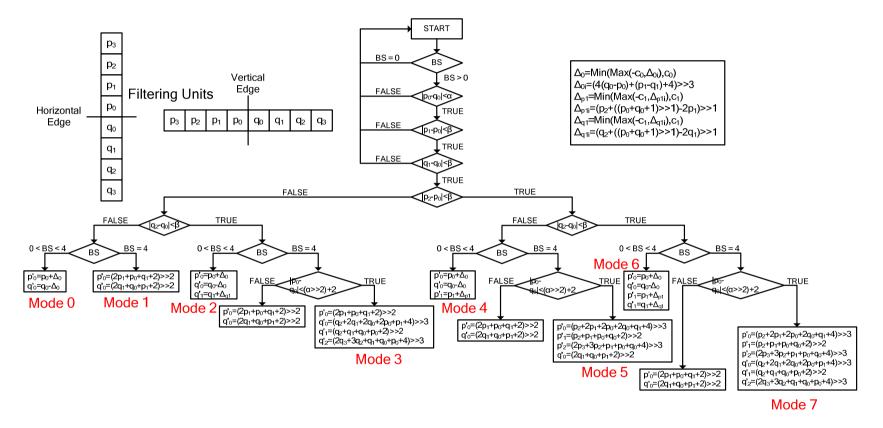

| Figure 4.3 H.264 Deblocking Filter Algorithm                                                                                                                                                                                           |

| Figure 4.4 Rate Distortion Curves of the Original H.264 DBF Algorithm and H.264 DBF                                                                                           |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Algorithm with Proposed PSCR Technique80                                                                                                                                      |

| Figure 4.5 H.264 DBF Hardware Architecture    81                                                                                                                              |

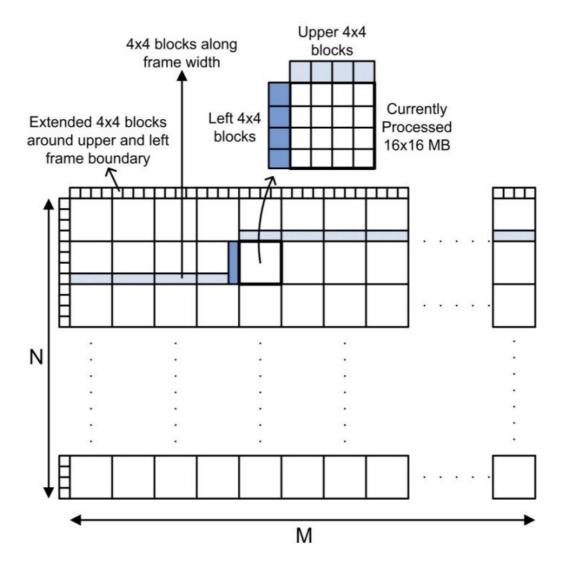

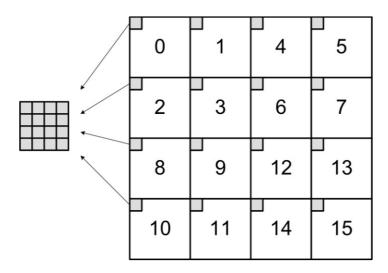

| Figure 4.6 Processing Order of 4×4 Blocks                                                                                                                                     |

| Figure 4.7 4x4 Blocks Stored in LUMA and CHRM SRAMs                                                                                                                           |

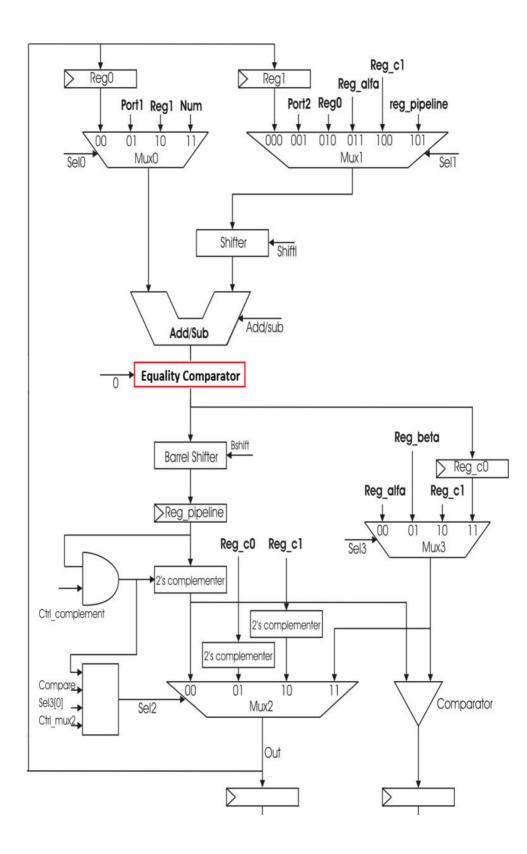

| Figure 4.8 H.264 DBF Datapath                                                                                                                                                 |

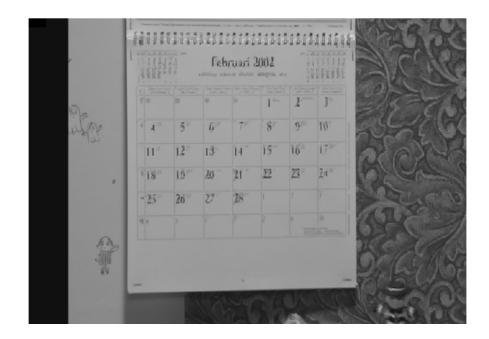

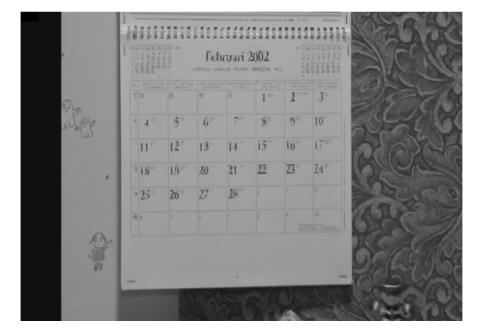

| Figure 4.9 a) Unfiltered Video Frame and b) The Same Frame Filtered by H.264 Deblocking<br>Filter Algorithm                                                                   |

| Figure 5.1 Formation of DC Block for Intra 16x16 Prediction Modes                                                                                                             |

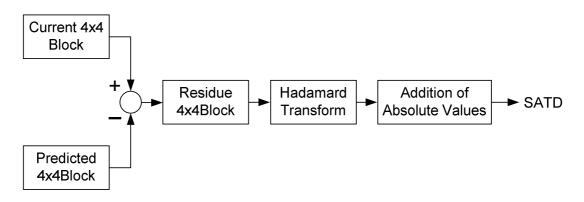

| Figure 5.2 SATD Calculation for Each 4x4 Block                                                                                                                                |

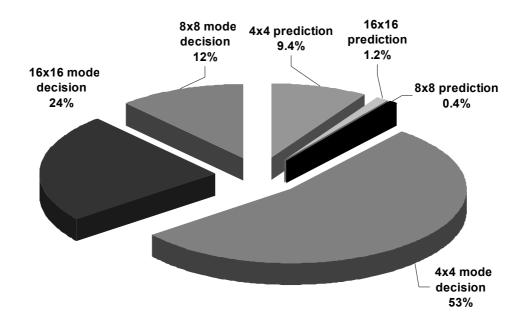

| Figure 5.3 Addition Operations Performed by Intra Prediction and Mode Decision                                                                                                |

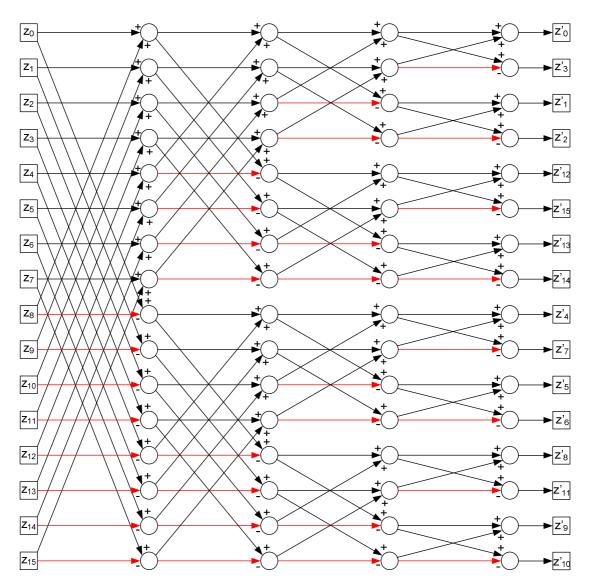

| Figure 5.4 Fast HT Algorithm for a 4x4 Block                                                                                                                                  |

| Figure 5.5 Hadamard Transform of Vertical, Horizontal and DC Modes                                                                                                            |

| Figure 5.6 16x16 MB and its Neighboring Pixels                                                                                                                                |

| Figure 5.7 Rate Distortion Curves of Original SATD Mode Decision and SATD Mode Decision with Proposed Technique                                                               |

|                                                                                                                                                                               |

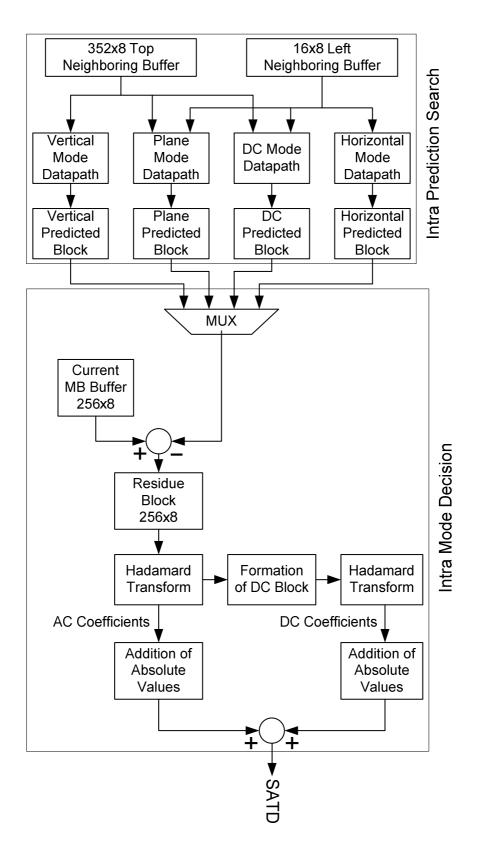

| <b>Figure 5.8</b> Proposed Hardware for Original Intra 16x16 Mode Decision                                                                                                    |

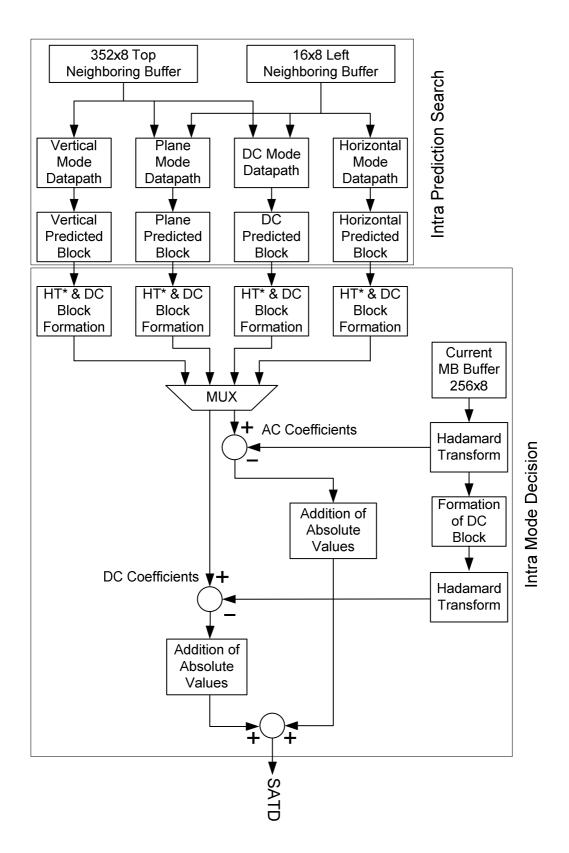

| Figure 5.9 Proposed Hardware for Intra 16x16 Mode Decision with Proposed Technique 117                                                                                        |

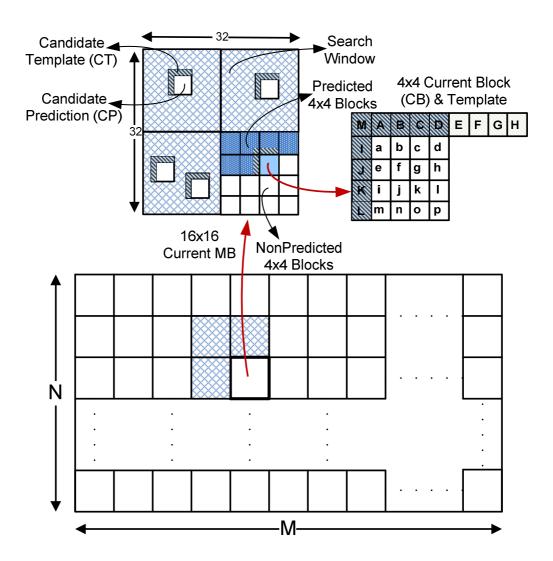

| Figure 6.1 Intra Prediction with Template Matching       120         120       120                                                                                            |

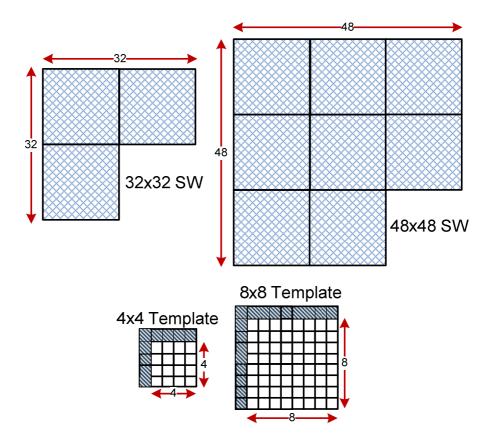

| Figure 6.2 Different Size Templates and Search Windows    123                                                                                                                 |

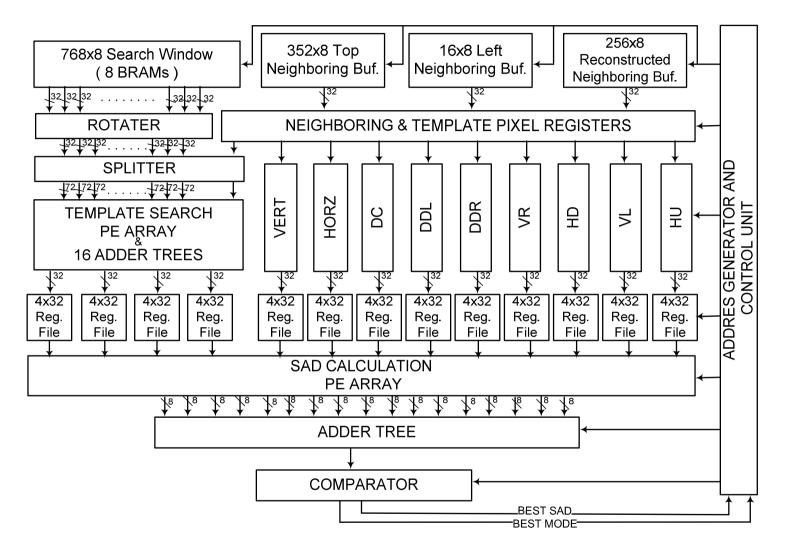

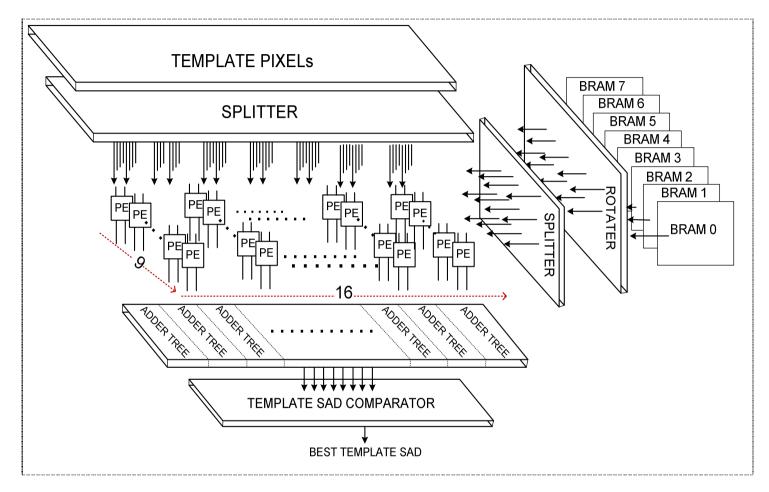

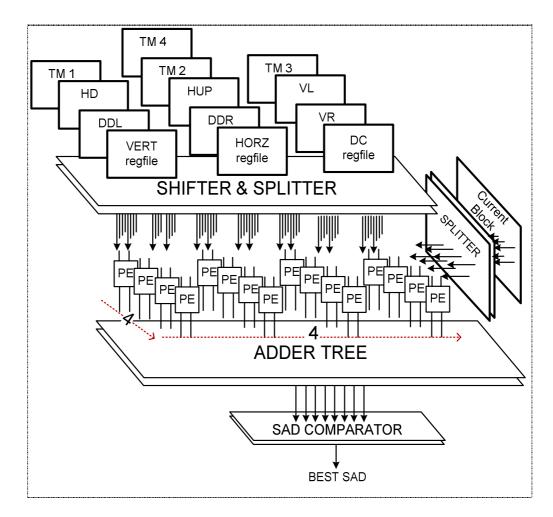

| Figure 6.3 Top Level Block Diagram of Proposed 4x4 Intra Prediction with Template Matching         Hardware       129                                                         |

| Figure 6.4 Template Search PE Array and 16 Adder Tree                                                                                                                         |

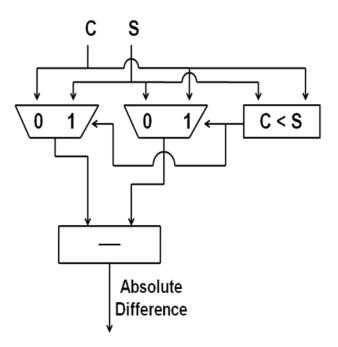

| Figure 6.5 PE Architecture                                                                                                                                                    |

| Figure 6.6 SAD Calculation PE Array and Adder Tree                                                                                                                            |

| Figure 6.7 Memory Organization of 32x32 SW                                                                                                                                    |

| <b>Figure 6.8</b> a) Video Frame Predicted by H.264 4x4 Intra Prediction Modes and b) The Same Frame Predicted by H.264 4x4 Intra Prediction Modes with TM Including Proposed |

| Technique                                                                                                                                                                     |

# LIST OF TABLES

| Table 2.1 Availability of 4x4 Luma Prediction Modes                                                 | 17 |

|-----------------------------------------------------------------------------------------------------|----|

| Table 2.2 Availability of 16x16 Luma Prediction Modes                                               | 19 |

| Table 2.3 Availability of 8x8 Luma Prediction Modes                                                 | 22 |

| Table 2.4 4x4 Intra Modes and Corresponding Neighboring Pixels                                      | 26 |

| Table 2.5 Percentage of 4x4 Intra Prediction Modes with Equal Neighboring Pixels                    | 28 |

| Table 2.6 Percentage of 4x4 Intra Prediction Modes with Similar Neighboring Pixels                  | 29 |

| Table 2.7 Computation Amount of 4x4 Intra Modes                                                     | 29 |

| Table 2.8 Intra 4x4 Modes Computation Reduction Results by PECR Technique                           | 30 |

| Table 2.9 Intra 4x4 Modes Computation Reduction Results by PSCR Technique                           | 30 |

| Table 2.10 Percentage of 16x16 Intra Prediction Modes with Equal Neighboring Pixels                 | 32 |

| Table 2.11 Percentage of 8x8 Intra Prediction Modes (Chroma CB, CR) with Equal Neighbor<br>Pixels   | -  |

| Table 2.12 Percentage of 16x16 Intra Prediction Modes with Similar Neighboring Pixels               | 34 |

| Table 2.13 Percentage of 8x8 Intra Prediction Modes (Chroma CB, CR) with Similar Neighboring Pixels | 35 |

| Table 2.14 Computation Amount of Intra 16x16 and Intra 8x8 Modes                                    | 36 |

| Table 2.15 Intra 16x16 Computation Reduction Results by PECR                                        | 37 |

| Table 2.16 Intra 8x8 (Chroma CB, CR) Computation Reduction Results by PECR                          | 37 |

| Table 2.17 Intra 16x16 Computation Reduction Results by PSCR                                        | 38 |

| Table 2.18 Intra 8x8 (Chroma CB, CR) Computation Reduction Results by PSCR                          | 39 |

| Table 2.19 Average PSNR Comparison of the Proposed PSCR Technique                                   | 41 |

| Table 2.20 Power Consumption Reduction (QP=28) by PECR and PSCR Techniques                          | 44 |

| Table 2.21 Power Consumption Reduction (QP=35) by PECR and PSCR Techniques                          | 44 |

| Table 2.22 Power Consumption Reduction (QP=42) by PECR and PSCR Techniques                          | 45 |

| Table 3.1 Prediction Equations of 4x4 Intra Prediction Modes                                        | 49 |

| Table 3.2 4x4 Intra Modes and Corresponding Neighboring Pixels    50                                                          |

|-------------------------------------------------------------------------------------------------------------------------------|

| Table 3.3 Percentage of 4x4 Intra Prediction Blocks with Equal and Similar Prediction Equation                                |

| Pixels                                                                                                                        |

| Table 3.4 Addition and Shift Operations Performed by 4x4 Intra Prediction for a CIF Frame with                                |

| PECR Technique                                                                                                                |

| Table 3.5 Addition and Shift Operations Performed by 4x4 Intra Prediction for a CIF Frame with                                |

| PSCR Technique                                                                                                                |

| Table 3.6 Computation Reduction by PECR and PSCR (4bT) Techniques for 4x4 Intra         Prediction with Data Reuse         53 |

| Table 3.7 Computation Reduction for 4x4 Intra Prediction by PECR Technique                                                    |

| Table 3.8 Computation Reduction for 4x4 Intra Prediction by PSCR Technique with 4bT 54                                        |

| Table 3.9 Average PSNR Comparison of the PSCR Techniques    56                                                                |

| Table 3.10 Comparison of 4x4 Intra Prediction Hardware                                                                        |

| Table 3.11 Power Consumption Reduction (QP = 28)                                                                              |

| Table 3.12 Power Consumption Reduction (QP = 35)                                                                              |

| Table 3.13 Power Consumption Reduction (QP = 42)                                                                              |

| Table 4.1 Conditions that Determine BS                                                                                        |

| Table 4.2 DBF Modes   68                                                                                                      |

| Table 4.3 Equations for Mode 6 and their Simplified Versions when p2=p1=p0=q0=q1=q269                                         |

| Table 4.4 The Amount of Computation Required by DBF Mode 0 For Different Equal Pixel         Combinations.         70         |

| Table 4.5 The Amount of Computation Required by DBF Mode 1 For Different Equal Pixel                                          |

| Combinations                                                                                                                  |

| Table 4.6 The Amount of Computation Required by DBF Mode 2 For Different Equal Pixel         Combinations                     |

| Table 4.7 The Amount of Computation Required by DBF Mode 3 For Different Equal Pixel                                          |

| Combinations                                                                                                                  |

| Table 4.8 The Amount of Computation Required by DBF Mode 4 For Different Equal Pixel         Combinations                     |

| Table 4.9 The Amount of Computation Required by DBF Mode 5 For Different Equal Pixel         Combinations. |     |

|------------------------------------------------------------------------------------------------------------|-----|

| Table 4.10 The Amount of Computation Required by DBF Mode 6 For Different Equal Pix         Combinations.  |     |

| Table 4.11 The Amount of Computation Required by DBF Mode 7 For Different Equal Pixe<br>Combinations       |     |

| Table 4.12 Amount of Operations Performed by All DBF Modes                                                 | 73  |

| Table 4.13 Filtering Units with All Equal or Similar Pixels for Luma Components                            | 74  |

| Table 4.14 Filtering Units with All Equal or Similar Pixels for Chroma (CbCr) Components                   | 74  |

| Table 4.15 Computation Reductions for Luma Components                                                      | 76  |

| Table 4.16 Computation Reductions for Chroma (CbCr) Components                                             | 77  |

| Table 4.17 Comparison Overhead                                                                             | 79  |

| Table 4.18 Average PSNR Comparison of PSCR Technique                                                       | 79  |

| Table 4.19 FPGA Resource Usage and Clock Frequency After P&R                                               | 84  |

| Table 4.20 Energy Consumption Reduction By PECR Technique                                                  | 87  |

| Table 4.21 Energy Consumption Reduction By PSCR (1bT) Technique                                            | 87  |

| Table 4.22 Energy Consumption Reduction By PSCR (2bT) Technique                                            | 88  |

| Table 5.1 Pre-calculated Values for DDL Prediction Mode                                                    | 100 |

| Table 5.2 DDL Mode Prediction Calculations Using Pre-calculated Values                                     | 100 |

| Table 5.3 Pre-calculated Values for DDR Prediction Mode                                                    | 101 |

| Table 5.4 DDR Mode Prediction Calculations Using Pre-calculated Values                                     | 101 |

| Table 5.5 Pre-calculated Values for VR Prediction Mode                                                     | 102 |

| Table 5.6 VR Mode Prediction Calculations Using Pre-calculated Values                                      | 103 |

| Table 5.7 Pre-calculated Values for HUP Prediction Mode                                                    | 103 |

| Table 5.8 HUP Mode Prediction Calculations Using Pre-calculated Values                                     | 104 |

| Table 5.9 Computation Reductions for Intra Prediction Modes                                                | 112 |

| Table 5.10 Average PSNR (dB) Comparison of Original SATD Mode Decision and SATD                            |     |

| Mode Decision with Proposed Technique                                                                      | 112 |

| Table 5.11 Energy Consumption Reductions                                                                   | 118 |

| Table 6.1 PSNR Results (dB) of Different Size SWs and Templates                               | 123 |

|-----------------------------------------------------------------------------------------------|-----|

| Table 6.2 PSNR Results (dB) of Intra Prediction with TM                                       | 125 |

| Table 6.3 Number of TM Predictions Selected when Th <sub>SAD</sub> Used                       | 126 |

| Table 6.4 Average PSNR (dB) Comparison of the Proposed Technique for Small Th <sub>SAD</sub>  | 126 |

| Table 6.5 Average PSNR (dB) Comparison of the Proposed Technique for Large Th <sub>SAD</sub>  | 127 |

| Table 6.6 Computation Reductions for Intra Prediction with TM for Different $Th_{SAD}$ values | 128 |

| Table 6.7 Energy Consumption Reduction when $Th_{SAD} = 40$                                   | 138 |

| Table 6.8 Energy Consumption Reduction when $Th_{SAD} = 50$                                   | 138 |

| Table 6.9 Energy Consumption Reduction when $Th_{SAD} = 60$                                   | 138 |

### CHAPTER I

## **INTRODUCTION**

### 1.1 H.264 Video Compression Standard

Video compression systems are used in many commercial products, from consumer electronic devices such as digital camcorders, cellular phones to video teleconferencing systems. H.264 / MPEG4 Part 10, the recently developed international standard for video compression, offers significantly better compression efficiency (capable of saving up to 50% bit rate at the same level of video quality) than previous video compression standards [1, 2, 3]. Because of its high coding efficiency and flexibility and robustness to different communication environments, H.264 is expected to be widely used in many applications such as digital TV, DVD, video transmission in wireless networks, and video conferencing over the internet.

The human visual system appears to distinguish scene content in terms of brightness and color information individually, and with greater sensitivity to the details of brightness than color [3]. Same as the previous video compression standards, H.264 is designed to take advantage of this by using YCbCr color space. In YCbCr color space, each pixel is represented with three 8-bit components called Y, Cb, and Cr. Y, the luminance (luma) component, represents brightness. Cb and Cr, chrominance (chroma) components, represent the extent to which the color differs from gray toward blue and red, respectively. Since the human visual system is more sensitive to luma component than chroma components, H.264 standard uses 4:2:0 sampling. In 4:2:0 sampling, for every four luma samples, there are two chroma samples, one Cb and one Cr.

The top-level block diagram of an H.264 video encoder is shown in Figure 1.1. As shown in the figure, the video compression efficiency achieved in H.264 standard is not a result of any single feature but rather a combination of a number of encoding tools such as motion estimation, intra prediction and deblocking filter (DBF). Same as the previous video compression standards, H.264 standard does not specify all the algorithms that will be used in an encoder such as mode decision. Instead, it defines the syntax of the encoded bit stream and functionality of the decoder that can decode this bit stream.

As shown in Figure 1.1, an H.264 encoder has a forward path and a reconstruction path. The forward path is used to encode a video frame and create the bit stream by using intra and inter predictions. The reconstruction path is used to decode the encoded frame and reconstruct the decoded frame. Since a decoder never gets original images, but rather works on the decoded frames, reconstruction path in the encoder ensures that both encoder and decoder use identical reference frames for intra and inter prediction. This avoids possible encoder – decoder mismatches [1,3,4].

Figure 1.1 H.264 Encoder Block Diagram

Forward path starts with partitioning the input frame into macroblocks (MB). Each MB is encoded in intra or inter mode depending on the mode decision. In both intra and inter modes, the current MB is predicted from the reconstructed frame. Intra mode generates the predicted MB based on spatial redundancy, whereas inter mode, generates the predicted MB based on temporal redundancy. Mode decision compares the required amount of bits to encode a MB and the quality of the decoded MB for both of these modes and chooses the mode with better quality and bit-rate performance. In either case, intra or inter mode, the predicted MB is subtracted from the current MB to generate the residual MB. Residual MB is transformed using 4x4 and 2x2 integer transforms. Transformed residual data is quantized and quantized transform coefficients are re-ordered in a zig-zag scan order. The reordered quantized transform coefficients are entropy coded. The entropy-coded coefficients together with header information, such as MB prediction mode and quantization step size, form the compressed bit stream. The compressed bit stream is passed to network abstraction layer (NAL) for storage or transmission [1,3,4].

Reconstruction path begins with inverse quantization and inverse transform operations. The quantized transform coefficients are inverse quantized and inverse transformed to generate the reconstructed residual data. Since quantization is a lossy process, inverse quantized and inverse transformed coefficients are not identical to the original residual data. The reconstructed residual data are added to the predicted pixels in order to create the reconstructed frame. DBF is, then, applied to reduce the effects of blocking artifacts in the reconstructed frame [1,3,4].

Figure 1.2 H.264 Decoder Block Diagram

The compression efficiency achieved by H.264 standard comes with an increase in encoding complexity and therefore in power consumption. H.264 intra prediction and mode decision algorithms have very high computational complexity. Because, in order to improve the compression efficiency, H.264 standard uses many intra prediction modes for a MB and selects the best mode for that MB using a mode decision algorithm. The DBF algorithm used in H.264 standard is more complex than the DBF algorithms used in previous video compression standards. First of all, H.264 DBF algorithm is highly adaptive and applied to each edge of all the 4×4 luma and chroma blocks in a MB. Second, it can update 3 pixels in each direction that the filtering takes place. Third, in order to decide whether the DBF will be applied to an edge, the related pixels in the current and neighboring 4×4 blocks must be read from memory and processed. Because of these complexities, the DBF algorithm can easily account for one-third of the computational complexity of an H.264 video decoder [4,5].

H.264 decoder is similar to the reconstruction path of H.264 encoder. It receives a compressed bit stream from the NAL as shown in Figure 1.2. The bit stream is decoded, inverse quantized and inverse transformed to get residual data. Using the header information decoded from the bit stream, the decoder creates a prediction block, identical to the prediction block generated in reconstruction path of H.264 encoder. The prediction block is added to the residual block to create the reconstructed block. Blocking artifacts are, then, removed from reconstructed block by applying DBF.

H.264 has three profiles; Baseline, Main, and Extended. A profile is a set of algorithmic features and a level shows encoding capability such as picture size and frame rate. In this thesis, we use Baseline profile. Baseline profile has lower latency than main and extended profiles, and it is used for wireless video applications and video conferencing. In Baseline profile, YCbCr color space with 4:2:0 sampling, I and P slices, and context-adaptive variable length entropy coding are supported [1,3].

#### 1.2 Low Power Hardware Design

Multimedia applications running on portable devices have increased recently and this

trend is expected to continue in the future. Since portable devices operate with battery, it is important to reduce power consumption so that battery life can be increased. In addition, consuming excessive power for a long time causes chips to heat up and degrades performance, because transistors run faster when they are cool rather than hot. Excessive power consumption also increases packaging and cooling costs. Excessive power consumption also reduces reliability and may cause device failures [6, 7].

Field Programmable Gate Arrays (FPGA) consume more power than standard cellbased Application Specific Integrated Circuits (ASIC). FPGAs have look-up tables and programmable switches. Look-up table based logic implementation is inefficient in terms of power consumption and programmable switches have high power consumption because of large output capacitances. Therefore, reducing power consumption is even more important for FPGA implementations.

ICs have static and dynamic power consumption. Static power consumption is a result of leakage currents in an IC. Dynamic power consumption is a result of short circuit currents and charging and discharging of capacitances in an IC. Dynamic power consumption is proportional to the switching activity ( $\alpha$ ), total capacitance (C<sub>L</sub>), supply voltage (V<sub>DD</sub>), operating frequency (*f*) and short circuit current (I<sub>SC</sub>) as shown in the following equation. The power consumption due to charging and discharging of capacitances is the dominant component of dynamic power consumption and it can be reduced either by decreasing switching activity, capacitance, supply voltage or frequency.

$$P_{dyn} \approx \alpha_{0 \to 1} C_L V_{DD}^2 f + I_{SC} V_{DD} f \tag{1.1}$$

In this thesis, we focused on reducing the dynamic power consumptions of FPGA implementations of H.264 video compression hardware. The dynamic power consumption of a digital hardware implementation on a Xilinx FPGA is estimated using Xilinx XPower tool. Since the switching activity is input pattern dependent, in order to estimate the dynamic power consumption, timing simulation of the placed and routed netlist of that hardware implementation is done for several input patterns using Mentor Graphics ModelSim and the signal activities are stored in a Value Change Dump (VCD) file. This VCD file is used for estimating the dynamic power consumption of that hardware using Xilinx XPower tool.

#### **1.3 Thesis Contributions**

We propose pixel equality based computation reduction (PECR) technique for reducing the amount of computations performed by H.264 intra prediction algorithm and therefore reducing the power consumption of H.264 intra prediction hardware significantly without any PSNR and bit rate loss. The proposed technique performs a small number of comparisons among neighboring pixels of the current block before the intra prediction process. If the neighboring pixels of the current block are equal, the prediction equations of H.264 intra prediction modes simplify significantly for this block. By exploiting the equality of the neighboring pixels, the proposed technique reduces the amount of computations performed by 4x4 luminance, 16x16 luminance, and 8x8 chrominance prediction modes up to 60%, 28%, and 68% respectively with a small comparison overhead. We also implemented an efficient 4x4 intra prediction hardware including the proposed technique using Verilog HDL. We quantified the impact of the proposed technique on the power consumption of this hardware on a Xilinx Virtex II FPGA using Xilinx XPower, and it reduced the power consumption of this hardware up to 46% [8].

We also propose pixel similarity based computation reduction (PSCR) technique for reducing the amount of computations performed by H.264 intra prediction algorithm and therefore reducing the power consumption of H.264 intra prediction hardware significantly. The proposed technique performs a small number of comparisons among neighboring pixels of the current block before the intra prediction process. If the neighboring pixels of the current block are similar, the prediction equations of H.264 intra prediction modes are simplified for this block. The proposed technique reduces the amount of computations performed by 4x4 luminance, 16x16 luminance, and 8x8 chrominance prediction modes up to 68%, 39%, and 65% respectively with a small comparison overhead. The proposed technique does not change the PSNR for some video frames, it increases the PSNR slightly for some video frames and it decreases the PSNR slightly for some video frames. We also implemented an efficient 4x4 intra prediction hardware including the proposed technique using Verilog HDL. We quantified the impact of the proposed technique on the power

consumption of this hardware on a Xilinx Virtex II FPGA using Xilinx XPower. The proposed technique reduced the power consumption of this hardware up to 57% [9, 10].

We, then, propose to calculate the common prediction equations only once and to use the results for the corresponding 4x4 intra modes, and to apply the PECR and PSCR techniques for each intra prediction equation separately. These techniques exploit pixel equality and similarity in a video frame by performing a small number of comparisons among pixels used in prediction equations before the intra prediction process. If the pixels used in prediction equations are equal or similar, prediction equations simplify significantly. By exploiting the equality and similarity of the pixels used in prediction equations, the proposed PECR and PSCR techniques reduce the amount of computations performed by 4x4 intra prediction modes up to 78% and 89%, respectively, with a small comparison overhead. We also implemented an efficient 4x4 intra prediction hardware including the proposed techniques using Verilog HDL. We quantified the impact of the proposed techniques on the power consumption of this hardware on a Xilinx Virtex II FPGA using Xilinx XPower. The proposed PECR and PSCR techniques reduced the power consumption of this hardware up to 13.7% and 17.2%, respectively. The proposed PECR technique does not affect the PSNR and bitrate. The proposed PSCR technique increases the PSNR slightly for some videos frames and it decreases the PSNR slightly for some videos frames [11, 12].

We also propose pixel equality and pixel similarity based techniques for reducing the amount of computations performed by H.264 DBF algorithm, and therefore reducing the energy consumption of H.264 DBF hardware. These techniques avoid unnecessary calculations in H.264 DBF algorithm by exploiting the equality and similarity of the pixels used in DBF equations. The proposed techniques reduce the amount of addition and shift operations performed by H.264 DBF algorithm up to 52% and 67% respectively with a small comparison overhead. The pixel equality based technique does not affect PSNR. The pixel similarity based technique does not affect the PSNR for some video frames, but it decreases the PSNR slightly for some video frames. We also implemented an efficient H.264 DBF hardware including the proposed techniques using Verilog HDL. We quantified the impact of the proposed techniques on the energy consumption of this hardware on a Xilinx Virtex4 FPGA using Xilinx XPower. The proposed pixel equality and

pixel similarity based techniques reduced the energy consumption of this H.264 DBF hardware up to 35% and 39%, respectively [14, 15].

We propose a novel energy reduction technique for H.264 intra mode decision. The proposed technique reduces the number of additions performed by Sum of Absolute Transformed Difference (SATD) based 4x4, 16x16 and 8x8 intra mode decision algorithms used in H.264 joint model reference software encoder by 46%, 43% and 42% respectively for a CIF size frame without any PSNR loss. In addition, it avoids the calculation of intra 16x16 and intra 8x8 plane prediction modes by slightly modifying SATD criterion used in H.264 Joint Model (JM) reference software encoder which slightly impacts the coding efficiency. It doesn't affect the PSNR for some videos, it increases the PSNR slightly for some videos and it decreases the PSNR slightly for some videos. Since plane mode is the most computationally intensive 16x16 and 8x8 prediction mode, avoiding plane mode calculations reduces the computational complexity of 16x16 and 8x8 intra prediction algorithm by 80%. We also implemented an efficient H.264 16x16 intra mode decision hardware including the proposed technique using Verilog HDL. We quantified the impact of the proposed technique on the energy consumption of this hardware on a Xilinx Virtex II FPGA using Xilinx XPower. The proposed technique reduced the energy consumption of this H.264 16x16 intra mode decision hardware up to 59.6% [16].

H.264 intra prediction algorithm is not well suited for processing complex textures at low bit rates. Therefore, intra prediction with Template Matching (TM) is proposed for improving H.264 intra prediction. However, intra prediction with TM has high computational complexity. Therefore, in this thesis, we propose a novel technique for reducing the amount of computations performed by intra prediction with TM, and therefore reducing the energy consumption of intra prediction with TM hardware. The proposed technique does not change the PSNR for some video frames, but it decreases the PSNR slightly for some video frames. We also designed and implemented a high performance 4x4 intra prediction with TM hardware including the proposed technique using Verilog HDL, and mapped it to a Xilinx Virtex 6 FPGA. The FPGA implementation is capable of processing 53 HD (1280x720) frames per second, and the proposed technique reduced its energy consumption up to 50% [13].

#### 1.4 Thesis Organization

The rest of the thesis is organized as follows.

Chapter II, first, explains H.264 intra prediction algorithm. It, then, presents the proposed PECR and PSCR techniques for H.264 intra prediction. An efficient H.264 intra prediction hardware including these techniques and its power consumption analysis are also presented in this chapter.

Chapter III, presents the data reuse and the application of PECR and PSCR techniques for each intra prediction equation separately. An efficient H.264 intra prediction hardware including these techniques and its power consumption analysis are also presented in this chapter.

Chapter IV, first, explains H.264 DBF algorithm. It, then, presents pixel equality and pixel similarity based techniques for reducing the amount of computations performed by H.264 DBF algorithm. An efficient H.264 DBF hardware including the proposed technique and its energy consumption analysis are also presented in this chapter.

Chapter V, first, explains H.264 intra mode decision algorithm. It, then, presents a novel computational complexity and power reduction technique for H.264 intra mode decision. An efficient H.264 16x16 intra mode decision hardware including the proposed technique and its energy consumption analysis are also presented in this chapter.

Chapter VI, first, explains intra prediction with Template Matching (TM) algorithm. It, then, presents a novel technique for reducing the amount of computations performed by intra prediction with TM. A high performance 4x4 intra prediction with TM hardware including the proposed technique and its energy consumption analysis are also presented in this chapter.

Chapter VII presents conclusions and future work.

## CHAPTER II

# PIXEL EQUALITY AND PIXEL SIMILARITY BASED COMPUTATION AND POWER REDUCTION TECHNIQUES FOR H.264 INTRA PREDICTION

H.264 intra prediction algorithm achieves better coding results than the intra prediction algorithms used in previous video compression standards. However, this coding gain comes with a significant increase in computational complexity. Therefore, in this thesis, we propose pixel equality and pixel similarity based techniques for reducing the amount of computations performed by H.264 intra prediction algorithm and therefore reducing the power consumption of H.264 intra prediction hardware. Both techniques are applicable to 4x4 luminance, 16x16 luminance and 8x8 chrominance prediction modes. Both techniques perform a small number of comparisons among neighboring pixels of the current block before the intra prediction process.

Pixel equality based computation reduction (PECR) technique checks the equality of the neighboring pixels. If the neighboring pixels used for calculating the predicted pixels by an intra 4x4 prediction mode are equal, the predicted pixels by this mode are equal to one of these neighboring pixels. Therefore, the prediction equations simplify to a constant value and prediction calculations for this mode become unnecessary. Furthermore, if the neighboring pixels used for calculating the predicted pixels by an intra 16x16 or an intra

8x8 prediction mode are equal, the prediction equations used by this mode simplify significantly. In this way, the amount of computations performed by H.264 intra prediction algorithm is reduced significantly without any PSNR loss [8].

Pixel similarity based computation reduction (PSCR) technique checks the similarity of the neighboring pixels, and if the neighboring pixels used for calculating the predicted pixels by an intra 4x4 prediction mode are similar, the predicted pixels by this mode are assumed to be equal to one of these neighboring pixels. Therefore, the prediction equations are simplified to a constant value and prediction calculations for this mode become unnecessary. Furthermore, if the neighboring pixels used for calculating the predicted pixels by an intra 16x16 or an intra 8x8 prediction mode are similar, the prediction equations used by this mode are simplified significantly. In this way, the proposed technique reduces the amount of computations performed by H.264 intra prediction algorithm even further with a small PSNR loss [9, 10].

The simulation results obtained by H.264 reference software, JM 14.0 [17], for several video sequences showed that PECR technique reduces the amount of computations performed by H.264 intra 4x4, 16x16 and 8x8 prediction modes up to 60%, 28%, and 68% respectively and PSCR technique reduces the amount of computations performed by H.264 intra 4x4, 16x16 and 8x8 prediction modes up to 68%, 39%, and 65% respectively with a small comparison overhead. The proposed techniques, for each MB, requires 12 and 24 comparisons for intra 4x4 and intra 8x8 prediction modes respectively. Since intra 4x4 and intra 16x16 prediction modes operate on the same MB, the comparison results for intra 4x4 prediction modes are also used for intra 16x16 prediction modes. The simulation results also showed that the proposed PSCR technique does not change the PSNR for some video frames, it increases the PSNR slightly for some video frames and it decreases the PSNR slightly for some video frames.

Several techniques are reported in the literature for reducing the computational complexity of H.264 intra prediction algorithm [18, 19, 20, 21]. These techniques reduce the amount of computation for H.264 intra prediction algorithm by trying selected intra prediction modes rather than trying all intra prediction modes. However, the techniques proposed in this thesis try all intra prediction modes, and they can also be used together with the techniques proposed in [18, 19, 20, 21]. Several hardware architectures for H.264

4x4 intra prediction algorithm are reported in the literature [22, 23, 24, 25]. However, they do not report their power consumption and they do not implement the techniques proposed in this thesis.

We also designed an efficient H.264 4x4 intra prediction hardware architecture including the proposed PECR and PSCR techniques. The hardware architecture is implemented in Verilog HDL. The Verilog RTL codes are verified to work at 50 MHz in a Xilinx Virtex II FPGA. The impacts of the proposed techniques on the power consumption of this hardware implementation on a Xilinx Virtex II FPGA are quantified using Xilinx XPower tool. The proposed PECR and PSCR techniques reduced the power consumption of this hardware on this FPGA up to 46% and 57%, respectively.

#### 2.1 H.264 Intra Prediction Algorithm

Intra prediction algorithm predicts the pixels in a MB using the pixels in the available neighboring blocks. For the luma component of a MB, a 16x16 predicted luma block is formed by performing intra predictions for each 4x4 luma block in the MB and by performing intra prediction for the 16x16 MB. There are nine prediction modes for each 4x4 luma block and four prediction modes for a 16x16 luma block. A mode decision algorithm is then used to compare the 4x4 and 16x16 predictions and select the best luma prediction mode for the MB. 4x4 prediction modes are generally selected for highly textured regions while 16x16 prediction modes are selected for flat regions.

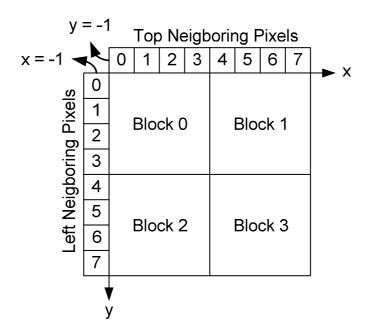

There are nine 4x4 luma prediction modes designed in a directional manner. A 4x4 luma block consisting of the pixels a to p is shown in Figure 2.1. The pixels A to M belong to the neighboring blocks and are assumed to be already encoded and reconstructed and are therefore available in the encoder and decoder to generate a prediction for the current MB. Each 4x4 luma prediction mode generates 16 predicted pixel values using some or all of the neighboring pixels A to M as shown in Figure 2.2. The examples of each 4x4 luma prediction mode for real images are given in Figure 2.3. The arrows indicate the direction of prediction in each mode. The predicted pixels are calculated by a weighted average of the neighboring pixels A-M for each mode except Vertical, Horizontal and DC modes.

The prediction equations used in each 4x4 luma prediction mode are shown in Figure 2.4 where [x, y] denotes the position of the pixel in a 4x4 block (the top left, top right, bottom left, and bottom right positions of a 4x4 block are denoted as [0, 0], [0, 3], [3, 0], and [3, 3], respectively) and pred[x, y] is the prediction for the pixel in the position [x, y].

| Μ | Α | В | C | D | E | F | G | Η |

|---|---|---|---|---|---|---|---|---|

| Ι | a | b | С | d |   |   |   |   |

| J | e | f | g | h |   |   |   |   |

| K | į | j | k | 1 |   |   |   |   |

| L | m | n | 0 | p |   |   |   |   |

Figure 2.1 A 4x4 Luma Block and Neighboring Pixels

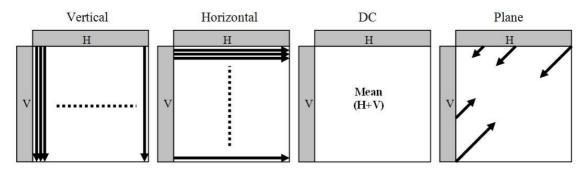

Figure 2.2 4x4 Luma Prediction Modes

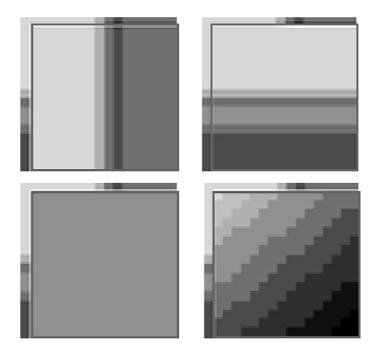

Figure 2.3 Examples of Real Images for 4x4 Luma Prediction Modes

DC mode is always used regardless of the availability of the neighboring pixels. However, it is adopted based on which neighboring pixels A-M are available. If pixels E, F, G and H have not yet been encoded and reconstructed, the value of pixel D is copied to these positions and they are marked as available for DC mode. The other prediction modes can only be used if all of the required neighboring pixels are available [1, 3]. Available 4x4 luma prediction modes for a 4x4 luma block depending on the availability of the neighboring 4x4 luma blocks are given in Table 2.1.

| pred[0, 0] = A | pred[0, 0] = I |

|----------------|----------------|

| pred[0, 1] = B | pred[0, 1] = I |

| pred[0, 2] = C | pred[0, 2] = I |

| pred[0, 3] = D | pred[0, 3] = I |

| pred[1, 0] = A | pred[1, 0] = J |

| pred[1, 1] = B | pred[1, 1] = J |

| pred[1, 2] = C | pred[1, 2] = J |

| pred[1, 3] = D | pred[1, 3] = J |

|----------------|----------------|

| pred[2, 0] = A | pred[2, 0] = K |

| pred[2, 1] = B | pred[2, 1] = K |

| pred[2, 2] = C | pred[2, 2] = K |

| pred[2, 3] = D | pred[2, 3] = K |

| pred[3, 0] = A | pred[3, 0] = L |

| pred[3, 1] = B | pred[3, 1] = L |

| pred[3, 2] = C | pred[3, 2] = L |

| pred[3, 3] = D | pred[3, 3] = L |

(a) 4x4 Vertical Mode

(b) 4x4 Horizontal Mode

If the left and the top neighboring

Else If only the left neighboring

Else If only the top neighboring

pixels are available

pixels are available

pixels are available

pred[x, y] = (A + B + C + D + I + J + K + L + 4) >> 3 pred[x, y] = (I + J + K + L + 2) >> 2 pred[x, y] = (A + B + C + D + 2) >> 2pred[x, y] = 128

Else

*(c)* 4*x*4 *DC Mode*

$pred[0, 0] = A + 2B + C + 2 \gg 2$   $pred[0, 1] = B + 2C + D + 2 \gg 2$   $pred[0, 2] = C + 2D + E + 2 \gg 2$   $pred[0, 3] = D + 2E + F + 2 \gg 2$   $pred[1, 0] = B + 2C + D + 2 \gg 2$   $pred[1, 1] = C + 2D + E + 2 \gg 2$   $pred[1, 2] = D + 2E + F + 2 \gg 2$   $pred[1, 3] = E + 2F + G + 2 \gg 2$  $pred[2, 0] = C + 2D + E + 2 \gg 2$   $pred[0, 0] = A + 2M + I + 2 \gg 2$   $pred[0, 1] = M + 2A + B + 2 \gg 2$   $pred[0, 2] = A + 2B + C + 2 \gg 2$   $pred[0, 3] = B + 2C + D + 2 \gg 2$   $pred[1, 0] = M + 2I + J + 2 \gg 2$   $pred[1, 1] = A + 2M + I + 2 \gg 2$   $pred[1, 2] = M + 2A + B + 2 \gg 2$   $pred[1, 3] = A + 2B + C + 2 \gg 2$  $pred[2, 0] = I + 2J + K + 2 \gg 2$

15

$pred[2, 1] = D + 2E + F + 2 \gg 2$   $pred[2, 2] = E + 2F + G + 2 \gg 2$   $pred[2, 3] = F + 2G + H + 2 \gg 2$   $pred[3, 0] = D + 2E + F + 2 \gg 2$   $pred[3, 1] = E + 2F + G + 2 \gg 2$   $pred[3, 2] = F + 2G + H + 2 \gg 2$  $pred[3, 3] = G + 3H + 2 \gg 2$   $pred[2, 1] = M + 2I + J + 2 \gg 2$   $pred[2, 2] = A + 2M + I + 2 \gg 2$   $pred[2, 3] = M + 2A + B + 2 \gg 2$   $pred[3, 0] = J + 2K + L + 2 \gg 2$   $pred[3, 1] = I + 2J + K + 2 \gg 2$   $pred[3, 2] = M + 2I + J + 2 \gg 2$  $pred[3, 3] = A + 2M + I + 2 \gg 2$

(d) 4x4 Diagonal Down Left Mode

(e) 4x4 Diagonal Down Right Mode

pred[0, 0] = M + A + 1 >> 1pred[0, 1] = A + B + 1 >> 1pred[0, 2] = B + C + 1 >> 1pred[0, 3] = C + D + 1 >> 1pred[1, 0] = I + 2M + A + 2 >> 2pred[1, 1] = M + 2A + B + 2 >> 2pred[1, 2] = A + 2B + C + 2 >> 2pred[1, 3] = B + 2C + D + 2 >> 2pred[2, 0] = M + 2I + J + 2 >> 2pred[2, 1] = M + A + 1 >> 1pred[2, 2] = A + B + 1 >> 1pred[2, 3] = B + C + 1 >> 1pred[3, 0] = I + 2J + K + 2 >> 2pred[3, 1] = I + 2M + A + 2 >> 2pred[3, 2] = M + 2A + B + 2 >> 2pred[3, 3] = A + 2B + C + 2 >> 2

pred[0, 0] = M + I + 1 >> 1

pred[0, 1] = I + 2M + A + 2 >> 2 pred[0, 2] = B + 2A + M + 2 >> 2 pred[0, 3] = C + 2B + A + 2 >> 2 pred[1, 0] = I + J + 1 >> 1 pred[1, 1] = M + 2I + J + 2 >> 2 pred[1, 2] = M + I + 1 >> 1 pred[1, 3] = I + 2M + A + 2 >> 2 pred[2, 0] = J + K + 1 >> 1 pred[2, 1] = I + 2J + K + 2 >> 2 pred[2, 2] = I + J + 1 >> 1 pred[2, 3] = M + 2I + J + 2 >> 2 pred[3, 0] = K + L + 1 >> 1 pred[3, 1] = J + 2K + L + 2 >> 2 pred[3, 2] = J + K + 1 >> 1pred[3, 3] = I + 2J + K + 2 >> 2

(f) 4x4 Vertical Right Mode

(g) 4x4 Horizontal Down Mode

| pred[0, 0] = A + B + 1 >> 1      | pred[0, 0] = I + J + 1 >> 1      |

|----------------------------------|----------------------------------|

| pred[0, 1] = B + C + 1 >> 1      | pred[0, 1] = I + 2J + K + 2 >> 2 |

| pred[0, 2] = C + D + 1 >> 1      | pred[0, 2] = J + K + 1 >> 1      |

| pred[0, 3] = D + E + 1 >> 1      | pred[0, 3] = J + 2K + L + 2 >> 2 |

| pred[1, 0] = A + 2B + C + 2 >> 2 | pred[1, 0] = J + K + 1 >> 1      |

| pred[1, 1] = B + 2C + D + 2 >> 2 | pred[1, 1] = J + 2K + L + 2 >> 2 |

| pred[1, 2] = C + 2D + E + 2 >> 2 | pred[1, 2] = K + L + 1 >> 1      |

| pred[1, 3] = D + 2E + F + 2 >> 2 | pred[1, 3] = K + 3L + 2 >> 2     |

| pred[2, 0] = B + C + 1 >> 1      | pred[2, 0] = K + L + 1 >> 1      |

| pred[2, 1] = C + D + 1 >> 1      | pred[2, 1] = K + 3L + 2 >> 2     |

| pred[2, 2] = D + E + 1 >> 1      | pred[2, 2] = L                   |

| pred[2, 3] = E + F + 1 >> 1      | pred[2, 3] = L                   |

| pred[3, 0] = B + 2C + D + 2 >> 2 | pred[3, 0] = L                   |

| pred[3, 1] = C + 2D + E + 2 >> 2 | pred[3, 1] = L                   |

| pred[3, 2] = D + 2E + F + 2 >> 2 | pred[3, 2] = L                   |

| pred[3, 3] = E + 2F + G + 2 >> 2 | pred[3, 3] = L                   |

(h) 4x4 Vertical Left Mode

(i) 4x4 Horizontal Up Mode

Figure 2.4 Prediction Equations for 4x4 Luma Prediction Modes

| Availability of Neighboring 4x4   | Available 4x4 Luma Prediction                      |

|-----------------------------------|----------------------------------------------------|

| Luma Blocks                       | Modes                                              |

| None available                    | DC                                                 |

| Left available, Top not available | Horizontal, DC, Horizontal Up                      |

| Top available, Left not available | Vertical, DC, Vertical Left, Diagonal<br>Down-Left |

| Both available                    | All Modes                                          |

**Table 2.1** Availability of 4x4 Luma Prediction Modes

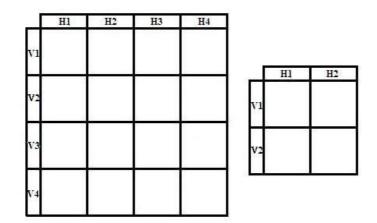

There are four 16x16 luma prediction modes designed in a directional manner. Each 16x16 luma prediction mode generates 256 predicted pixel values using some or all of the upper (H) and left-hand (V) neighboring pixels as shown in Figure 2.5. Vertical, Horizontal and DC modes are similar to 4x4 luma prediction modes. Plane mode is an approximation of bilinear transform with only integer arithmetic. The examples of each 16x16 luma prediction mode for real images are given in Figure 2.6. The prediction equations used in 16x16 luma prediction modes are shown in Figure 2.7 where [y, x] denotes the position of the pixel in a MB (the top left, top right, bottom left, and bottom right positions of a MB are denoted as [0,0], [0,15], [15,0], and [15,15], respectively), p represents the neighboring pixel values and Clip1 is to clip the result between 0 and 255.

DC mode is always used regardless of the availability of the neighboring pixels. However, it is adopted based on which neighboring pixels are available. The other prediction modes can only be used if all of the required neighboring pixels are available [1, 3]. Available 16x16 luma prediction modes for a MB depending on the availability of the neighboring MBs are given in Table 2.2.

Figure 2.5 16x16 Luma Prediction Modes

Figure 2.6 Examples of Real Images for 16x16 Luma Prediction Modes

| Availability of Neighboring 16x16 | Available 16x16 Luma    |

|-----------------------------------|-------------------------|

| Luma Blocks                       | <b>Prediction Modes</b> |

| None available                    | DC                      |

| Left available, Top not available | Horizontal, DC          |

| Top available, Left not available | Vertical, DC            |

| Both available                    | All Modes               |

Table 2.2 Availability of 16x16 Luma Prediction Modes

| pred[x, 0] = p[-1, 0] | pred[0, y] = p[0, -1] |

|-----------------------|-----------------------|

| pred[x, 1] = p[-1, 1] | pred[1, y] = p[1, -1] |

| pred[x, 2] = p[-1, 2] | pred[2, y] = p[2, -1] |

| pred[x, 3] = p[-1, 3] | pred[3, y] = p[3, -1] |

| pred[x, 4] = p[-1, 4] | pred[4, y] = p[4, -1] |

| pred[x, 5] = p[-1, 5] | pred[5, y] = p[5, -1] |

| pred[x, 6] = p[-1, 6]   | pred[6, y] = p[6, -1]   |

|-------------------------|-------------------------|

| pred[x, 7] = p[-1, 7]   | pred[7, y] = p[7, -1]   |

| pred[x, 8] = p[-1, 8]   | pred[8, y] = p[8, -1]   |

| pred[x, 9] = p[-1, 9]   | pred[9, y] = p[9, -1]   |

| pred[x, 10] = p[-1, 10] | pred[10,y] = p[10, -1]  |

| pred[x, 11] = p[-1, 11] | pred[11, y] = p[11, -1] |

| pred[x, 12] = p[-1, 12] | pred[12, y] = p[12, -1] |

| pred[x, 13] = p[-1, 13] | pred[13, y] = p[13, -1] |

| pred[x, 14] = p[-1, 14] | pred[14, y] = p[14, -1] |

| pred[x, 15] = p[-1, 15] | pred[15, y] = p[15, -1] |

(a) 16x16 Vertical Mode

(b) 16x16 Horizontal Mode

$$pred[x, y] = \left(\sum_{x'=0}^{15} p[x', -1] + \sum_{y'=0}^{15} p[-1, y'] + 16\right) >$$

$$pred[x, y] = \left(\sum_{y'=0}^{15} p[-1, y'] + 8\right) >> 4$$

$$pred[x, y] = \left(\sum_{x'=0}^{15} p[x', -1] + 8\right) >> 4$$

$$pred[x, y] = 128$$

>> 5 If the left and the top neighboring pixels are available

Else If only the left neighboring pixels are available

Else If only the top neighboring pixels are available

Else //If the left and the upper neighboring pixels are not available

*(c)* 16x16 DC Mode with x=0..15 and y=0..15

$$pred[x, y] = Clip1((a + b * (x - 7) + c * (y - 7) + 16) >> 5)$$

$$a = 16 * (p[-1,15] + p[15,-1])$$

$$b = (5 * H + 32) >> 6$$

$$c = (5 * V + 32) >> 6$$

$$H = \sum_{x'=0}^{7} (x' + 1) * (p[8 + x', -1] - p[6 - x', -1])$$

$$V = \sum_{y'=0}^{7} (y' + 1) * (p[-1,8 + y'] - p[-1,6 - y'])$$

(d) 16x16 Plane Mode with x, y = 0..15

Figure 2.7 Prediction Equations for 16x16 Luma Prediction Modes

For the chroma components of a MB, a predicted 8x8 chroma block is formed for each 8x8 chroma component by performing intra prediction for the MB. The chroma component of a MB and its neighboring pixels are shown in Figure 2.8. There are four 8x8 chroma prediction modes which are similar to 16x16 luma prediction modes. A mode decision algorithm is used to compare the 8x8 predictions and select the best chroma prediction mode for each chroma component of the MB. Both chroma components of a MB always use the same prediction mode. The prediction equations used in 8x8 chroma prediction modes are shown in Figure 2.9 where [x, y] denotes the position of the pixel in a MB (the top left, top right, bottom left, and bottom right positions of a MB are denoted as [0,0], [0,7], [7,0], and [7,7], respectively), p represents the neighboring pixel values and Clip1 is to clip the result between 0 and 255.

DC mode is always used regardless of the availability of the neighboring pixels. However, it is adopted based on which neighboring pixels are available. The other prediction modes can only be used if all of the required neighboring pixels are available [1,3]. Available 8x8 chroma prediction modes for a MB depending on the availability of the neighboring MBs are given in Table 2.3.

Figure 2.8 Chroma Component of a MB and its Neighboring Pixels

Table 2.3 Availability of 8x8 Luma Prediction Modes

| Availability of Neighboring 8x8   | Available 8x8 Luma      |

|-----------------------------------|-------------------------|

| Luma Blocks                       | <b>Prediction Modes</b> |

| None available                    | DC                      |

| Left available, Top not available | Horizontal, DC          |

| Top available, Left not available | Vertical, DC            |

| Both available                    | All Modes               |

| predc[0, y] = p[0, -1] |

|------------------------|

| predc[1, y] = p[1, -1] |

| predc[2, y] = p[2, -1] |

| predc[3, y] = p[3, -1] |

| predc[4, y] = p[4, -1] |

| predc[5, y] = p[5, -1] |

| predc[6, y] = p[6, -1] |

| predc[7, y] = p[7, -1] |

|                        |

(a) 8x8 Vertical Mode

(b) 8x8 Horizontal Mode

3

$$predc[x, y] = \left(\sum_{x'=0}^{3} p[x', -1] + \sum_{y'=0}^{3} p[-1, y'] + 4\right) >>$$

$$predc[x, y] = \left(\sum_{y'=0}^{3} p[-1, y'] + 2\right) >> 2$$

$$predc[x, y] = \left(\sum_{x'=0}^{3} p[x', -1] + 2\right) >> 2$$

predc[x, y] = 128

If p[x, -1] with x = 0..3, and p[-1, y]with y = 0..3 are available Else If p[-1, y] with y = 0..3 are available and p[x, -1] with x = 0..3are not available Else If p[x, -1] with x = 0..3 are available and p[-1, y] with y = 0..3are not available Else //If p[x, -1] with x = 0..3, and p[-1, y] with y = 0..3 are not available

(c) 8x8 DC Mode with x=0..3 and y=0..3 (Block 0 in Fig. 2.8)

$$predc[x, y] = \left(\sum_{x'=4}^{7} p[x', -1] + 2\right) >> 3$$

$$predc[x, y] = \left(\sum_{y'=0}^{3} p[-1, y'] + 2\right) >> 2$$

If p[x, -1] with x = 4..7 are available

Else If p[-1, y] with y = 0..3 are available

predc[x, y] = 128

Else //If p[x, -1] with x = 4..7, and p[-1, y] with y = 0..3 are not available

(c) 8x8 DC Mode with x=4..7 and y=0..3 (Block 1 in Fig. 2.8)

$$predc[x, y] = \left(\sum_{y'=4}^{7} p\left[-1, y'\right] + 2\right) >> 2$$

$$predc[x, y] = \left(\sum_{x'=0}^{3} p\left[x', -1\right] + 2\right) >> 2$$

$$predc[x, y] = 128$$

If p[-1, y] with y = 4..7 are available

Else If p[x, -1] with x = 0..3 are available

Else //If p[x, -1] with x = 0..3, and p[-1, y] with y = 4..7 are not available

(c) 8x8 DC Mode with x=0..3 and y=4..7 (Block 2 in Fig. 2.8)

$$predc[x, y] = \left(\sum_{x'=4}^{7} p[x', -1] + \sum_{y'=4}^{7} p[-1, y'] + 4\right) >> 3$$

$$predc[x, y] = \left(\sum_{y'=4}^{7} p[-1, y'] + 2\right) >> 2$$

$$predc[x, y] = \left(\sum_{x'=4}^{7} p[x', -1] + 2\right) >> 2$$

predc[x, y] = 128

If p[x, -1] with x = 4..7, and p[-1, y]with y = 4..7 are available

Else If p[-1, y] with y = 4..7 are available and p[x, -1] with x = 4..7are not available

Else If p[x, -1] with x = 4..7 are available and p[-1, y] with y = 4..7are not available

Else //If p[x, -1] with x = 4..7, and p[-1, y] with y = 4..7 are not available

(c) 8x8 DC Mode with x=4..7 and y=4..7 (Block 3 in Fig. 2.8)

$$pred[x, y] = Clip1((a + b * (x - 7) + c * (y - 7) + 16) >> 5)$$

$$a = 16 * (p[-1,7] + p[7,-1])$$

$$b = (17 * H + 16) >> 5$$

$$c = (17 * V + 16) >> 5$$

$$H = \sum_{x'=0}^{3} (x' + 1) * (p[4 + x', -1] - p[2 - x', -1])$$

$$V = \sum_{y'=0}^{3} (y' + 1) * (p[-1,4 + y'] - p[-1,2 - y'])$$

(*d*) 8x8 Plane Mode with x, y = 0..7

Figure 2.9 Prediction Equations for 8x8 Chroma Prediction Modes

#### 2.2 Proposed Computational Complexity and Power Reduction Techniques

PECR technique exploits equality of neighboring pixels for simplifying the prediction calculations done by H.264 intra prediction modes. PSCR technique exploits similarity of neighboring pixels for simplifying the prediction calculations done by H.264 intra prediction modes. Both techniques are applied to H.264 4x4 luminance, 16x16 luminance and 8x8 chrominance prediction modes.

Intra 4x4 modes use 13 neighboring pixels for prediction calculations. PECR technique for intra 4x4 modes is based on the equality of the neighboring pixels A, B, C, D, E, F, G, H, I, J, K, L, M of the currently processed 4x4 block. Each intra 4x4 prediction mode uses some of these neighboring pixels to predict a 4x4 block. H.264 4x4 intra prediction modes and the neighboring pixels they use for prediction calculations are shown in Table 2.4. The prediction equations of a 4x4 intra prediction mode simplify to a constant value if the neighboring pixels used by this mode are all equal.

The prediction equation used by DC mode is given in equation (2.1). If the neighboring pixels A, B, C, D, I, J, K, L are equal, we can substitute one of the neighboring pixels, e.g. pixel A, in place of every neighboring pixel in equation (2.1). Therefore, the equation (2.1) simplifies to A as shown in (2.2).

| 4x4 Intra Modes     | Neighboring Pixels        |

|---------------------|---------------------------|

| Vertical            | A, B, C, D                |

| Horizontal          | I, J, K, L                |

| DC                  | A, B, C, D, I, J, K, L    |

| Diagonal Down Left  | A, B, C, D, E, F, G, H    |

| Diagonal Down Right | A, B, C, D, I, J, K, L, M |

| Vertical Right      | A, B, C, D, I, J, K, M    |

| Horizontal Down     | A, B, C, I, J, K, L, M    |

| Vertical Left       | A, B, C, D, E, F, G       |

| Horizontal Up       | I, J, K, L                |

**Table 2.4** 4x4 Intra Modes and Corresponding Neighboring Pixels

$$pred[y,x] = [(A+B)+(C+D)+(I+J)+(K+L)+4] >> 3$$

(2.1)

pred[y,x] = [8A+4] >>3 = A (2.2)

This is the case for other prediction modes as well. For example, as shown in Figure 2.4, DDL mode uses A, B, C, D, E, F, G, H neighboring pixels in its prediction equations. The prediction equation for the pixel [0, 0] is given in equation (2.3). If neighboring pixels A, B, C, D, E, F, G, H are all equal, all prediction equations of DDL mode simplifies to a constant value as shown in (2.4).

$$pred[0, 0] = A + 2B + C + 2 >> 2$$

(2.3)

$$pred[0,0] = [4A+2] >> 2 = A$$

(2.4)

Since, in this case, all predicted pixels by DDL mode will be the same and equal to one of the neighboring pixels, the calculations done by DDL prediction mode become unnecessary. Therefore, during 4x4 intra prediction, the calculations done by DDL mode can be avoided by only comparing a few neighboring pixels at the beginning of the prediction process. During 4x4 intra prediction, the calculations done by the other prediction modes can be avoided in the same way by comparing the neighboring pixels used by the prediction equations of these modes.

PSCR technique for intra 4x4 modes is based on the similarity of the neighboring pixels of the currently processed 4x4 block. If the neighboring pixels used by the prediction equations of a 4x4 intra prediction mode are similar, the pixels predicted by this mode will

also be similar. PSCR technique determines the similarity of the neighboring pixels by truncating their least significant bits by the specified truncation amount (1, 2, 3, or 4 bits) and comparing the truncated pixels. If the truncated neighboring pixels of a prediction mode are all equal, one of the original neighboring pixels is substituted in place of every neighboring pixel in the prediction equations of this prediction mode. Therefore, prediction equations simplify to a constant value and prediction equation calculations become unnecessary.

The number of 4x4 intra prediction modes with equal and similar neighboring pixels in a frame varies from frame to frame. We analyzed CIF sized Foreman, Akiyo and Mother&Daughter frames at 28, 35 and 42 QP values using JM 14.0 to determine how many prediction modes have equal and similar neighboring pixels. The percentages of 4x4 modes that have equal neighboring pixels for each frame are given in Table 2.5. The percentage of prediction modes with equal neighboring pixels vary from 14% to 89%.

The percentages of 4x4 modes that have similar neighboring pixels for different truncation amounts for each frame are given in Table 2.6. The percentage of prediction modes with similar neighboring pixels vary from 11% to 94%. The percentage increases with higher QP values. Vert, Horz, Horz\_up, DDL and Vert\_left modes typically, on the average, have more than 50% similar neighboring pixels. DDR, Horz\_down and Vert\_right have relatively lower percentage with a typical value of more than 20%.

Table 2.7 shows the amount of computation performed by the prediction equations of each 4x4 intra mode in terms of number of addition and shift operations. Vertical and Horizontal modes require no computation. The prediction equations of the other modes include only addition and shift operations. Vertical right, Horizontal down and Vertical left modes have large amount of computation. A total of 882337 addition and 528045shift operations are performed by the H.264 4x4 intra prediction algorithm for a CIF (352x288) frame.

Based on this information and the information given in Tables 2.5, 2.6 and 2.7, we calculated the computation reduction achieved by the PECR and PSCR techniques for CIF size Foreman, Akiyo and Mother&Daughter frames. As shown in Table 2.8, the computation reduction ranges from 28% to 60% by PECR technique. As shown in Table 2.9, the computation reduction ranges from 18% to 68% by PSCR technique. The proposed

| techniques, | on the | other | hand, | have | an | overhead | of | only | 74882 | comparisons | for a | CIF |

|-------------|--------|-------|-------|------|----|----------|----|------|-------|-------------|-------|-----|

| (352x288) f | rame.  |       |       |      |    |          |    |      |       |             |       |     |

|                 | 4x4 Intra Modes | QP = 28 | QP = 35 | QP = 42 |

|-----------------|-----------------|---------|---------|---------|

|                 | VERT            | 50.17%  | 68.75%  | 84.31%  |

|                 | HORZ/HORZ_UP    | 47.76%  | 65.74%  | 79.51%  |

| Ц               | DC              | 29.34%  | 48.93%  | 68.77%  |

| m               | DDL             | 40.94%  | 61.10%  | 80.26%  |

| Foreman         | DDR             | 14.08%  | 21.26%  | 24.61%  |

| Ŧ               | VERT_RIGHT      | 14.55%  | 21.61%  | 25.02%  |

|                 | HORZ_DOWN       | 14.47%  | 21.89%  | 24.78%  |

|                 | VERT_LEFT       | 41.56%  | 61.58%  | 80.51%  |

|                 | VERT            | 65.01%  | 75.14%  | 85.89%  |

|                 | HORZ/HORZ_UP    | 66.19%  | 78.82%  | 87.06%  |

|                 | DC              | 48.94%  | 62.52%  | 76.69%  |