# HIGH DYNAMIC RANGE PIXEL ARCHITECTURE WITH SMART LIGHT INTENSITY DECISION UNIT

by

MELIK YAZICI

Submitted to the Graduate School of Engineering and Natural Sciences in partial fulfilment of the requirements for the degree of Doctor of Philosophy

Sabancı University

Summer, 2016

# HIGH DYNAMIC RANGE PIXEL ARCHITECTURE WITH SMART LIGHT INTENSITY DECISION UNIT

APPROVED BY

Prof. Yaşar GÜRBÜZ (Thesis Supervisor)

Assoc. Prof. Ayhan BOZKURT

Prof. Erkay SAVAŞ

Assoc. Prof. Arda Deniz YALÇINKAYA

Assist. Prof. Erdinç ÖZTÜRK

- prover

.....

DATE OF APPROVAL: 10/08/2016

# © MELIK YAZICI 2016

All Rights Reserved

#### Acknowledgements

This thesis would not be have been accomplished without the guidance, the support, and the inspiration of the many people: my professors, co-workers, and friends as well as my parents. It is a pleasure to convey my gratitude to them all in my humble acknowledgment.

First and foremost, I would like to express my sincere gratitude to my advisor Prof. Yaşar Gürbüz for the continuous support of my Ph.D study and related research, for his patience, motivation, and immense knowledge. His guidance helped me in all the time of research and writing of this thesis.

I would like to also thank to my thesis committee members, Assoc. Prof Ayhan Bozkurt, Prof. Erkay Savaş, Assoc. Prof. Arda Deniz Yalçınkaya and Assist. Prof. Erdinç Öztürk for their valuable guidance comments and critiques.

Throughout my PhD study, I was supported by TÜBİTAK BİDEB-2211 program. I am grateful for this scholarship and hope that the program can support many young scientists in the future as well. My thesis work is supported by SAN-TEZ program of Ministry of Science, Industry and Technology, with project code 1250.STZ.2012-1. I also would like to thank to Prof. Uğur Çam for his guidance and valuable comments during the process of the project.

I am thankful to my comrade designers Dr. Hüseyin Kayahan and Ömer Ceylan for their contribution to this work and everything during my study. I would like to also tank the former and present members of the ROIC group: M. Burak Baran, Atia Shafique, Arman Galioglu and Shahbaz Abbasi. Especially, I would like to thank İlker Kalyoncu, Can Calışkan and Abdurrahman Burak for their help in my tape-outs and their friendship.

Every member of the IC Design and Test Lab deserve many thanks for creating frendly environment and all their help: Emre Özeren, Murat Davulcu, Barbaros Çetindoğan, Berktuğ Üstündağ, Eşref Türkmen, Elif Gül Özkan Arsoy, Divya Mahalingam, Dr. Geetesh Mishra, Alper Güner, Emre Can Durmaz. I would like to thank laboratory stuff of EE program Ali Kasal for his support and Mehmet Doğan for his design PCB skills.

Finally, I thank to my family Mehmet and Fatma for their encouragement, support and love throughout my life.

### High Dynamic Range Pixel Architecture with Smart Light Intensity Decision Unit

Melik Yazıcı EE, PhD Thesis, 2016 Thesis Supervisor: Prof. Dr. Yaşar GÜRBÜZ

Keywords: ROIC, SWIR, Smart, Unit Cell, SNR, HDR, Infrared, FPA.

#### Abstract

In this thesis, a novel pixel architecture for third generation infrared detectors is proposed. This smart design introduces flux detection mechanism for the broad spectrum short wave infrared detector and dual/multicolor detectors. This architecture achieves very high dynamic range for analog ROICs.

HDR for ROIC means very dark and very bright signal levels is processed at the same time. In practical terms, HDR enables high contrast and accuracy which finds itself many applications from security to industry. The typical unit cell of a ROIC consists of the pre-amplifier, gain switches, multiplexer, output amplifier and some control switches. For a standard single band detector array, a ROIC uses only a single pre-amplifier which optimized for average performance.

In the proposed architecture, instead of using a single preamplifier, two preamplifiers, which are optimized for different light levels, are placed inside each pixel. A smart circuit mechanism, which decides the best input circuit according to the incoming light level, is also designed for the pixel.

In short, the smart pixel selects the best input amplifier circuit that performs the best SNR for the incoming signal level. A 32x32 prototype chip is designed in 0.18  $\mu$ m CMOS technology. Chip achieves minimum 8.6  $e^-$  input referred noise and 98.9 dB dynamic range. Operating temperature is 300 K and power consumption is 2.8  $\mu$ W per pixel.

## Geniş Dinamik Aralıklı Akıllı Işık Yoğunluğu Algılayıcılı Piksel Mimarisi

ROIC, SWIR, Akıllı, Birim Hücre, SNR, HDR, Kızılötesi, FPA.

Melik Yazıcı EE, Doktora Tezi, 2016 Tez Danışmanı: Prof. Dr. Yaşar GÜRBÜZ

#### Özet

Bu tezde üçüncü nesil kızılötesi dedektörler için özgün piksel mimarisi önerilmiştir. Çift/çok bantlı dedektörler ve geniş spektrumlu dedektörler için gelen ışık akısını algılayan akıllı bir tasarım sunulmuştur. Bu mimari analog entegre okuma devreleri arasında çok geniş bir dinamik aralığa erişmektedir.

Okuma devreleri için yüksek dinamik aralık çok karanlık ve parlak sinyallerin aynı anda görüntülenip işlenmesi demektir. Özetle, yüksek dinamik aralık yüksek karşıtlık ve hassaslık sağlamaktadır. Bu özellik güvenlikten endüstriye bir çok alandaki uygulamalarda kendine yer bulmaktadır. Tipik bir entegre okuma devresindeki piksel hücresinde giriş güçlendiricisi, kazanç anahtarları, çoklayıcı, çıkış güçlendricisi ve çeşitli kontrol anahtarları bulunmaktadır. Tek bantlı bir dedektörde kullanılan entegre okuma devresi ortalama bir performans için optimize edilmiş bir tane giriş güçlendiricisi kullanmaktadır.

Onerilen özgün mimaride tek bir giriş güçlendiricisi kullanmak yerine farklı ışık seviyeleri için optimize edilmiş iki giriş güçlendiricisi kullanılmıştır. Gelen ışık seviyesine göre en iyi giriş güçlendiricisini seçen akıllı devre mekanizması da gene özgün pixel mimarisi için tasarlanmıştır.

Kısaca, akıllı pixel gelen sinyal seviyesine göre en iyi SNR seviyesini veren en uygun güçlendiriciyi seçmektedir. 0.18  $\mu$ m CMOS teknolojisi kullanılarak 32x32 boyutunda prototip çip tasarlanmıştır. Çip en düşük 8.6  $e^-$  gürültü seviyesine erişmiştir ve 98.9 dB lik dinamik aralığa sahiptir. 300 K ortam sıcaklığında çalışmaktadır ve piksel başına 2.8  $\mu$ W'lık güç tüketimi vardır.

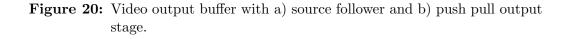

# Contents

| A        | cknov      | wledgements                              | iv   |

|----------|------------|------------------------------------------|------|

| A        | bstra      | let                                      | v    |

| Li       | st of      | Figures                                  | x    |

| Li       | st of      | Tables                                   | xi   |

| Li       | st of      | Abbreviations                            | xiii |

| 1        | Intr       | oduction                                 | 1    |

|          | 1.1        | A Brief History of Sensing the Invisible | 1    |

|          | 1.2        | Infrared Imaging Systems                 |      |

|          |            | 1.2.1 Optics                             |      |

|          |            | 1.2.2 Detectors                          |      |

|          |            | 1.2.3 Cooling of IR Detectors            |      |

|          |            | 1.2.4 Proximity Board                    |      |

|          | 1.3        | Readout Integrated Circuits              |      |

|          | 1.4        | ROIC Performance Parameters              |      |

|          |            | 1.4.1 Charge Handling Capacity           |      |

|          |            | 1.4.2 Frame Rate                         |      |

|          |            | 1.4.3 Input Referred Noise               |      |

|          |            | 1.4.4 Dynamic Range                      |      |

|          |            | 1.4.5 Linearity                          |      |

|          |            | 1.4.6 Uniformity                         |      |

|          |            | 1.4.7 Power Dissipation                  |      |

|          |            | 1.4.8 Gain                               |      |

|          | 1.5        | Motivation                               |      |

|          | 1.6        | Thesis Objectives                        |      |

|          | 1.7        | Organization                             |      |

| <b>2</b> |            | IC Architectures                         | 22   |

| 4        | 2.1        | Analog ROIC Sub-blocks                   |      |

|          | 2.1        | 2.1.1         Preamplifiers              |      |

|          |            | 2.1.2 Signal Processing                  |      |

|          |            | 2.1.2         Signal Processing          |      |

|          |            | 2.1.4 Digital Control                    |      |

|          | 2.2        | Proposed Architecture of the Smart Pixel |      |

|          | 2.2<br>2.3 | High Dynamic Range Imaging               |      |

|          | 2.0        | Ingli Dynamic Range imaging              | . 50 |

| 3        |            | art Pixel Implementation                 | 40   |

|          | 3.1        | 32x32 Prototype                          |      |

|          | -          | 3.1.1 Circuit Design Analysis            |      |

|          | 3.2        | Pixel                                    |      |

|          | 3.3        | Current Source                           |      |

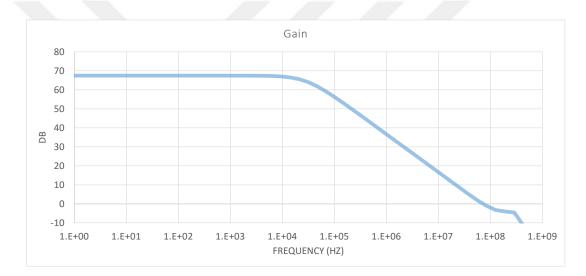

|          | 3.4        | Output Amplifier                         | 49   |

| 4  | Mea   | asurement Results        | <b>54</b>       |

|----|-------|--------------------------|-----------------|

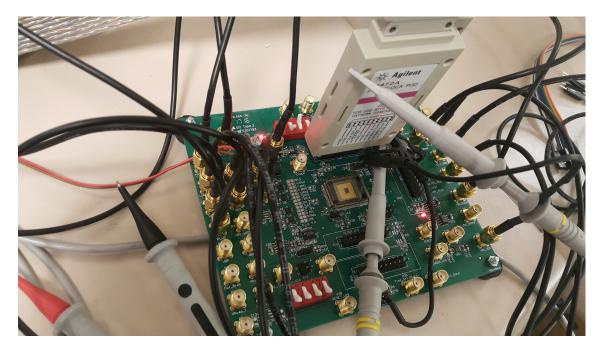

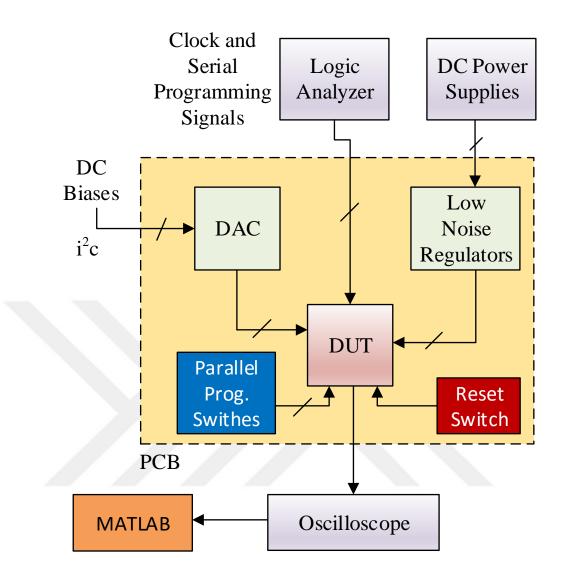

|    | 4.1   | Measurement Setup        | 54              |

|    | 4.2   | Pixel Response           | 57              |

|    | 4.3   | Noise Measurement        | 59              |

| 5  |       | nclusion<br>Future Works | <b>66</b><br>69 |

| Re | efere | nces                     | 74              |

# List of Figures

| 1  | Herschel and his famous experiment.                                   | . 2  |  |

|----|-----------------------------------------------------------------------|------|--|

| 2  | History of FPA.                                                       |      |  |

| 3  | Atmospheric transmittance of infrared region.                         |      |  |

| 4  | Block diagram of an IR imaging system.                                |      |  |

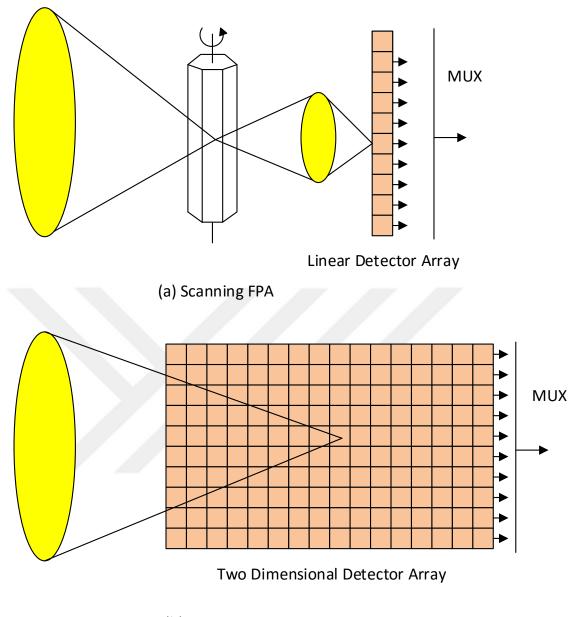

| 5  | There are two type of FPA's a) single dimensional scanning and b)     |      |  |

|    | two-dimensional starring.                                             | . 6  |  |

| 6  | Cooling IR detectors (a) Stirling cycle engine (b) four stage thermo- |      |  |

|    | electric cooler.                                                      | . 9  |  |

| 7  | Crayogenic Dewar with Stirling cooler.                                | . 10 |  |

| 8  | SWIR and LWIR Image fusion.                                           |      |  |

| 9  | Block diagram of an analog readout.                                   |      |  |

| 10 | Noise sources in the imaging system.                                  |      |  |

| 11 | High dynamic image vs regular image.                                  |      |  |

| 12 | Non-uniformity correction, a) raw image b) corrected image            | . 18 |  |

| 13 | Hybridizated FPA (a) an indium bump (b) loophole technique (c)        |      |  |

|    | SEM photo of indium bumps.                                            | . 22 |  |

| 14 | Comparison of (a) analog and (b) digital (c) ROIC signal block dia-   |      |  |

|    | grams                                                                 | . 23 |  |

| 15 | Architecture of analog readout integrated circuit.                    | . 25 |  |

| 16 | Schematic of unit cell operation.                                     | . 26 |  |

| 17 | The most popular types of amplifiers used in readout circuits         | . 28 |  |

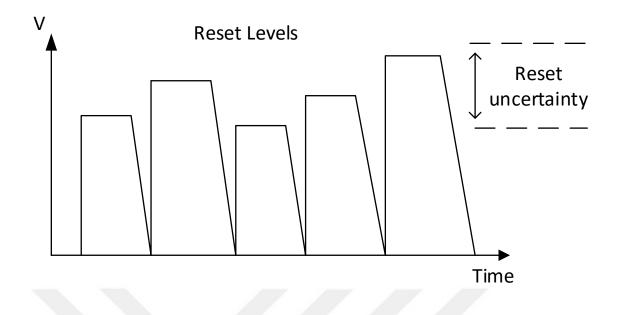

| 18 | Reset uncertainty due to thermodynamic fluctuations                   | . 29 |  |

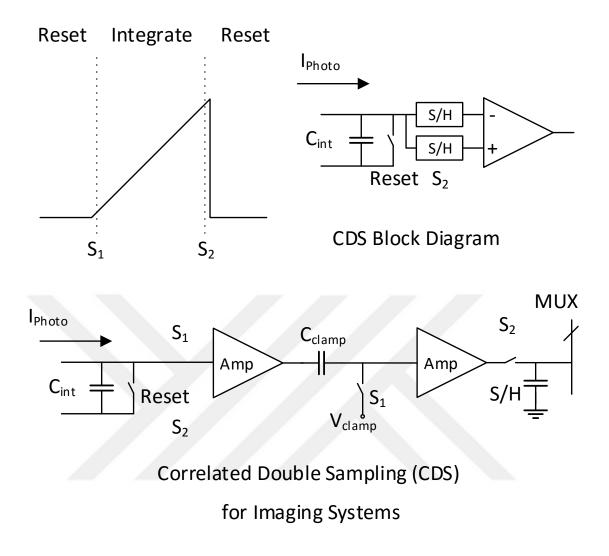

| 19 | Correlated double sampling timings, block diagram, and implemen-      |      |  |

|    | tation                                                                | . 30 |  |

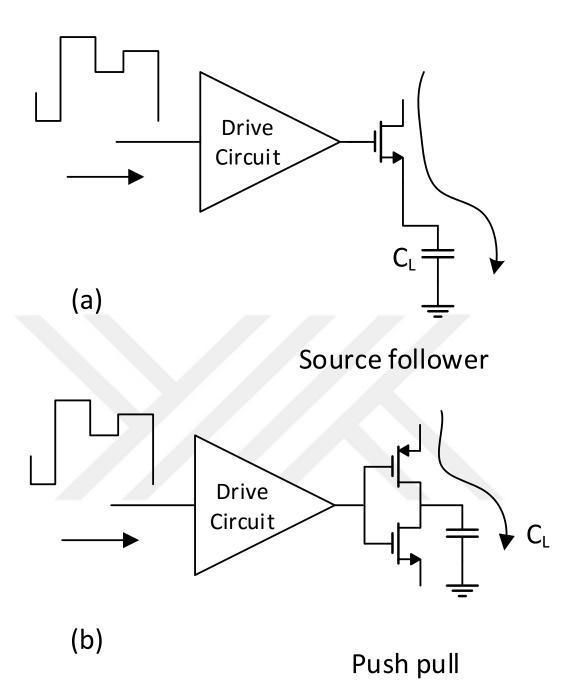

| 20 | Video output buffer with a) source follower and b) push pull output   |      |  |

|    | stage                                                                 | . 31 |  |

| 21 | a) Standard pixel structure b) smart pixel architecture               | . 33 |  |

| 22 | Two step integration. First integration is for detecting light level  |      |  |

|    | second one is actual integration of light.                            | . 34 |  |

| 23 | Detailed block diagram of the smart pixel                             | . 35 |  |

| 24 | NUC corrected and HDR image examples                                  | . 37 |  |

| 25 | HDR imaging with different gain settings and final image              |      |  |

| 26 | Block diagram of 32x32 Smart ROIC.                                    |      |  |

| 27 | Layout of 32x32 Smart ROIC.                                           |      |  |

| 28 | Schematic of the SWIR smart pixel                                     |      |  |

| 29 | Schematic of the CTIA.                                                |      |  |

| 30 | Layout of the pixel                                                   |      |  |

| 31 | Constant current source circuit.                                      |      |  |

| 32 | Process and mismatch compensated current source circuit               |      |  |

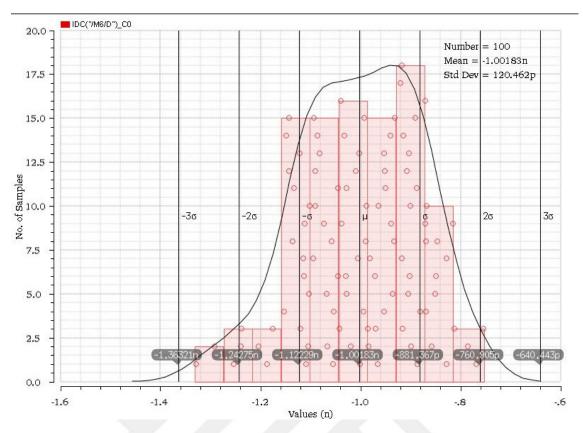

| 33 | Monte Carlo simulation result for 1 nA current.                       |      |  |

| 34 | Process and mismatch compensated current source circuit               |      |  |

| 35 | Layout of the opamp                                                   |      |  |

| 36 | Gain of the opamp (67.6 dB). $\ldots$                                 |      |  |

| 37 | Test PCB of the final prototype                                       |      |  |

| 38 | Block diagram of the DUT.                                             | . 55 |  |

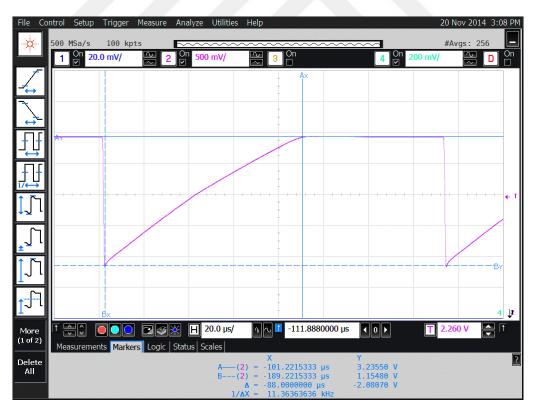

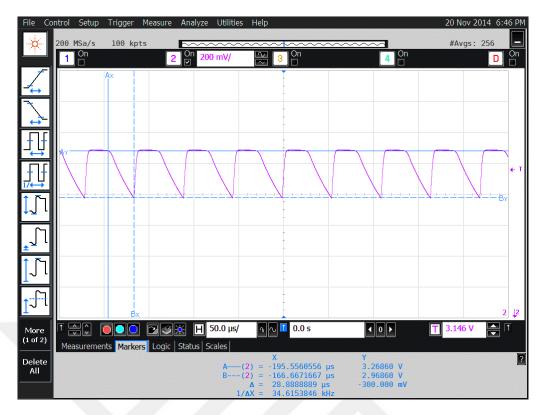

| 39 | 50 $\mu$ s integration time, 2.714V bias voltage, and 1.24V integrated        |    |

|----|-------------------------------------------------------------------------------|----|

|    | charge                                                                        | 57 |

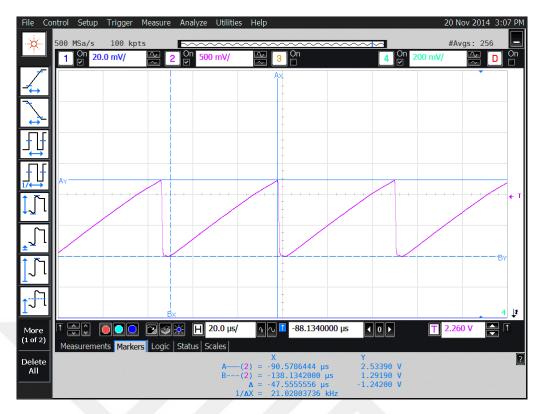

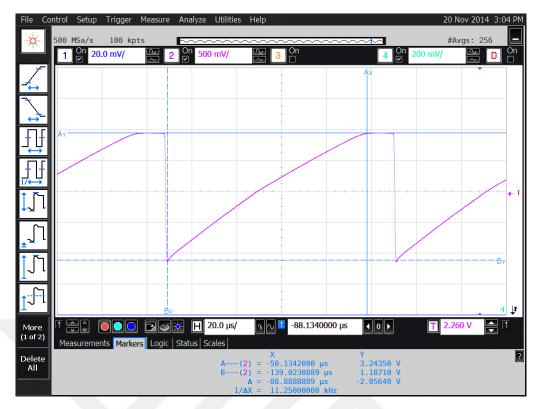

| 40 | 100 $\mu$ s integration time, 2.714V bias voltage, and 2.05V integrated       |    |

|    | charge                                                                        | 58 |

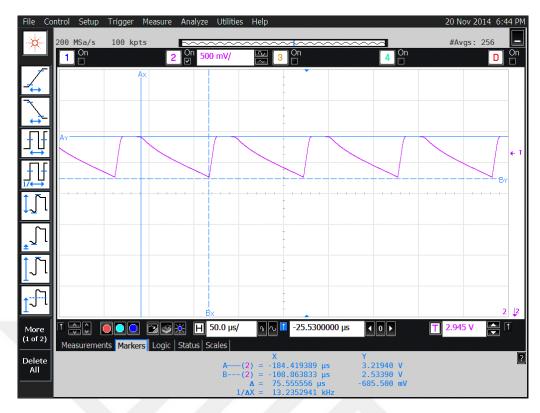

| 41 | 50 $\mu$ s integration time, 2.714 V bias voltage, and 2.05 V integrated      |    |

|    | charge                                                                        | 58 |

| 42 | 30 $\mu$ s integration time, 2.83 V bias voltage, and 300 mV integrated       |    |

|    | charge                                                                        | 59 |

| 43 | 75 $\mu \rm s$ integration time, 2.83 V bias voltage, and 685.5 mV integrated |    |

|    | charge                                                                        | 60 |

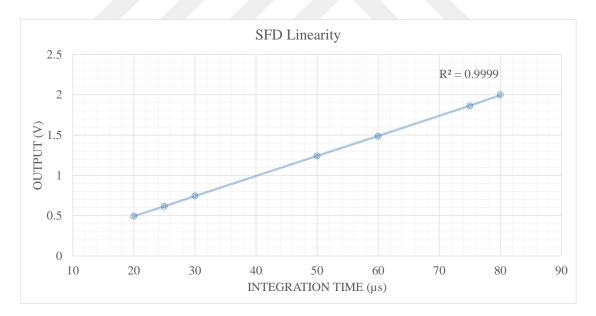

| 44 | Linearity of the SFD amplifier.                                               | 60 |

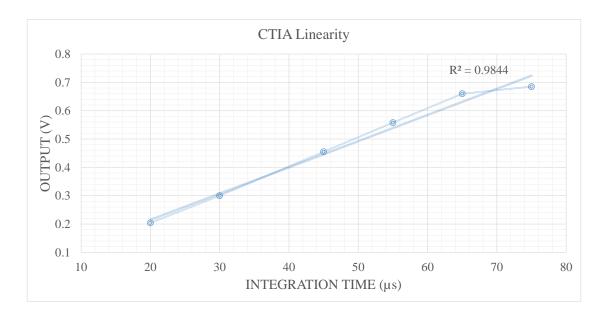

| 45 | Linearity of the CTIA amplifier                                               | 61 |

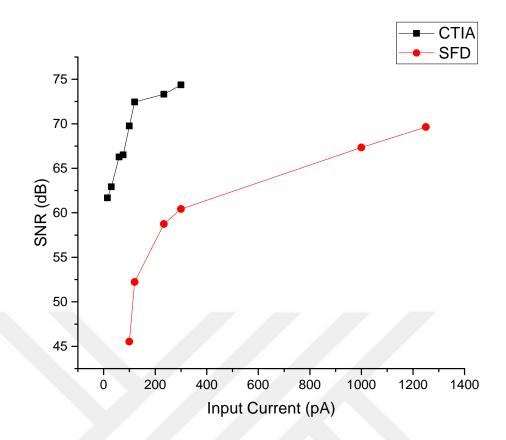

| 46 | SNR of CTIA and SFD amplifiers                                                | 62 |

# List of Tables

| 1 | ROIC performance requirements and their relation with system pa- |    |

|---|------------------------------------------------------------------|----|

|   | rameters                                                         | 14 |

| 2 | Advantages and drawback of Analog and Digital ROICs              | 25 |

| 3 | Comparison of popular preamplifier topologies                    | 27 |

| 4 | Truth table of the D-latch.                                      | 47 |

| 5 | Supply voltages of PCB board and ROIC.                           | 56 |

| 6 | Bias values of the ROIC.                                         | 56 |

| 7 | Digital signals of the ROIC.                                     | 56 |

| 8 | Comparison                                                       | 63 |

# List of Abbreviations

- ADC ..... Analog to Digital Converter

- ASIC ...... Application-Specific Integrated Circuit

- **BDI** ..... Buffered Direct Injection

- CCD ..... Charge Coupled Device

- CDS ..... Correlated Double Sampling

- CMRR ..... Common-Mode Rejection Ratio

- CTIA ..... Capacitive transimpedance Amplifier

- DAC ..... Digital to Analog Converter

- **DI** ..... Direct Injection

- **DROIC** ..... Digital Readout Integrated Circuit

- DSLR ..... Digital Single Lens Reflex

- DSNU ..... Dark Signal Nonuniformity

- ESD ..... Electrostatic Discharge

- **FoM** ..... Figure of Merit

- FPA ..... Focal Plane Array

- FPGA ..... Field Programmable Gate Array

- **FPN** ..... Fixed Pattern Noise

- FPS ..... Frame Per Second

- GBW ..... Gain Bandwidth

- GigE ..... Gigabit Ethernet

- HDR ..... High Dynamic Range

- LVDS ...... Low-Voltage Differential Signaling

- LWIR ..... Long-wave Infrared

- MCT ..... Mercury Cadmium Telluride

- MOS ..... Metal-Oxide Semiconductor

- MPW ..... Multi Project Wafer

- MWIR ..... Mid-wave Infrared

- ${\bf NEP} \ \ldots \ldots$  Noise Equivalent Power

- NIR ..... Near Infrared

- NUC ..... Non-uniformity Correction

- PCB ..... Printed Circuit Board

- PRNU ..... Pixel Response Nonuniformity

- ${\bf RGB}$   $\hfill \ldots \hfill {\bf RGB}$  Red Green Blue

- **RGBA** ..... Red Green Blue Alpha

- ROIC ..... Readout Integration Circuit

- $\mathbf{SFD} \quad \dots \dots \quad \text{Source Follower per Detector}$

- **SNR** ..... Signal to Noise Ratio

- SWaP ..... Size Weight and Power

- SWIR ..... Short-Wave Infrared

- **TEC** ..... Thermoelectric Cooling

- TEC ..... Termoelectric Cooler

- VHDL ..... VHSIC Hardware Description Language

- VLWIR ..... Very Long-wave Infrared

# 1 Introduction

### 1.1 A Brief History of Sensing the Invisible

The history of the infrared detector is backed in the year of 1800s with Hershel's the discovery of infrared radiation. In that experiment, Hershel was studying the spectrum of sunlight with a prism. He observed an increase of temperature when he was moving a thermometer from blue to red light. Just after red light when there was no visible light, he found a significant amount of rising in the thermometer. That was considered as the beginning of infrared detectors and systems.

After Hershel, there were not much effort to develop infrared detectors. Seeback's discovery of the thermoelectric effect in 1821 was the first development. Then, Nobili invented the first thermocouple in 1829. In 1880, the first bolometer was made by Langle utilizing a Wheatstone bridge. Before the end of 19th century, the first photoconductive effect was discovered by Smith. He was performing experiments using selenium.

There was a tremendous effort on photon detectors during World War I and II. Because of the ability to see the dark can bring an enormous advantage over enemies. The first infrared photoconductor, using thallium and sulfur  $(TI_2S)$ , was developed by Case in 1917. The concept of the electro-optical converter was designed by Holst in 1928. The first image converter based on photocathode was made in 1934 by Philips [1].

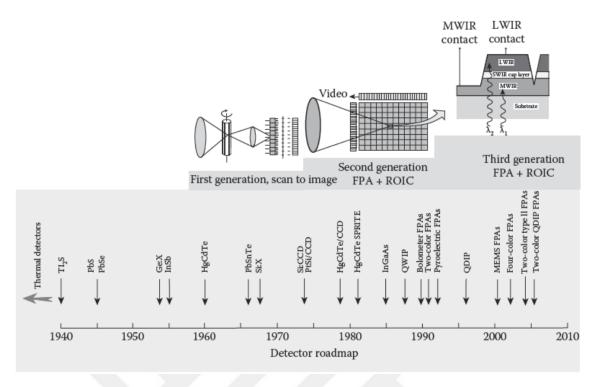

Today's modern focal plane arrays (FPA) are recent technologies. The first generation FPA's are only single-dimensional linear structures developed in the 1960s. Those FPA's are used with scanners to generate two-dimensional images. AIM-9 Sidewinder missile used these first generation systems in their guidance system. The second generation ROIC's are hybridized with two-dimensional staring detectors. First examples of the second generation FPA's can be seen at the end of the 1970s. Third generation term is a little bit blurry; there are no clear-cut definitions as the first and second generation. However, the third generation promises more functionality and intelligence for pixels such as analog to digital conversion inside a pixel instead of column level, a large number of pixels (2048x2048), dual-band or multicolor detectors inside the same pixel and some pre-processing functionalities

Figure 1: Herschel and his famous experiment [2].

within a pixel [3]. Fig. 2 shows the evolution of detector types along with ROICs.

Digital ROIC (DROIC)'s is also part of the third revolution. They provide high dynamic range solutions [4] and charge handling capacities such as 2.3 G $e^-$  [5]. High photocurrents, which are available in LWIR detectors, are required to benefit from high charge handling capability. For analog pixels, there are a lot of papers and patents exist that proposes solution for high dynamic range, dual band, and dual-color third generation detectors. Some of them use more than one input amplifier instead of gain stage inside a pixel [6–9]. Their pixel provides two outputs at the

Figure 2: History of FPA [3].

same time. In [10] user may have the option to select one of the input amplifiers. Also, one of them only uses a single amplifier which produces two different outputs from two different gain settings [7].

Another approach is developing smart ROICs that includes on-chip processing capabilities and functionalities to reduce processing overhead or improve performance [11–14]. Due to features added into pixel structure, pitch sizes of these ROICs are bigger than trending small pitch sizes. Thus, they are aiming for specific low-resolution applications. Finally, the most popular third generation trend is dual or multi-color imaging systems or detectors.

### **1.2 Infrared Imaging Systems**

Infrared imaging systems can be used in a variety of applications from civil to military; building or electrical/mechanical inspection, firefighting, machine vision, astronomy, security, surveillance, tactical systems are some of the application areas of infrared imaging systems [15]. All those systems utilize a different type of infrared sensors which work a particular part of the spectrum.

The infrared spectrum is sub-divided many sections according to its properties.

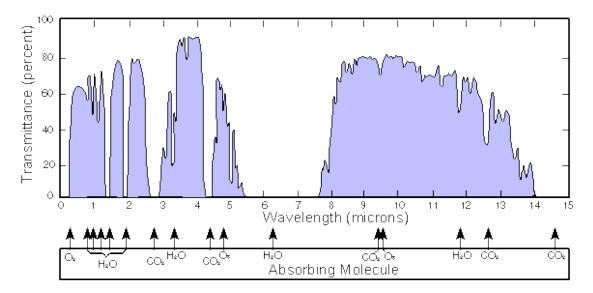

Figure 3: Atmospheric transmittance of infrared region [16].

Fig. 3 shows atmospheric absorption throughout infrared region. First sub-division starts right after at the end of visible spectrum 0.75  $\mu$ m which is near-infrared (NIR). Short wavelength (SWIR) (1.4-3  $\mu$ m), mid-wavelength (3-8  $\mu$ m), long wavelength infrared (8-15  $\mu$ m) and far-infrared (15-1000  $\mu$ m) are rest of the divisions in the spectrum. To explain briefly, NIR and SWIR can be used night vision devices such as security cameras and goggles and industrial inspections for product quality. Devices that uses MWIR sensor is used mostly for missile guidance or detection together with LWIR. LWIR region known as "thermal imaging" region which can passively detect heat waves. Thermal imaging systems are mostly used for surveillance purposes in the defense industry. Finally, far-infrared region finds itself useful for astronomy such as observations of faraway galaxies.

Advanced, military and scientific infrared solutions that mentioned above are very expensive. Besides high-end products, companies are extending the product range of low-cost infrared solutions to end users. For instance, FLIR Systems Inc. released infrared camera module named FLIR ONE<sup>TM</sup> for mobile phones which include a small bolometer based LWIR sensor in 2014 [17]. Moreover, SWIR sensors and systems gain popularity and can be seen for daily life more and more. For instance, SWIR camera is used in collision detection systems for cars to identify objects or human in the night or foggy weather. Another example is the detection of fake human hair, mustache, and beard due to SWIR reflection differences, in

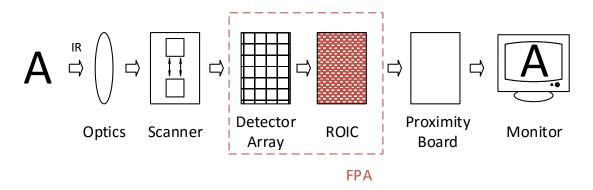

Figure 4: Block diagram of an IR imaging system.

airports and board control points.

NIR and SWIR bands are distinguished from thermal imaging bands (LWIR, MWIR). NIR and SWIR can be referred as reflected infrared and they do not sense thermal radiation. Since NIR and SWIR are reflective, they interact with objects such as bounces off of objects and create shadows and contrast like visible light. Unlike visible light, an output of reflective infrared is grayscale. For grayscale images, high dynamic range is desired for many applications such as machine vision, road traffic monitoring, security and military. Light sources or bright spots can saturate a large number of pixels and area of interest which is nearby the most lighted area can not be visible. HDR techniques are always desired to prevent saturations and improve SNR of an image, in SWIR.

Infrared imaging systems consist of many components such as detector, ROIC, signal processing and video processing modules. In Fig. 4 a typical block diagram of IR imaging system is shown. A scanner is an optional module that can be used with linear type detectors (single dimensional) to be able to create two-dimensional images. Fig. 5 shows both scanning and staring FPA's. Typically ROIC's and detectors are built on different substrates, then using flip chip bonding method, which is also called hybridization, they are connected to each other with indium bumps. This structure is called focal plane array (FPA) [18]. An output of FPA can be analog or digital.

Figure 5: There are two type of FPA's a) single dimensional scanning and b) two-dimensional starring.

#### 1.2.1 Optics

Optics is responsible for refracting infrared light to produce an image on the detector. All principles and design methodologies of visible optical elements apply to IR imaging systems. However, material choices are different. Germanium (Ge), Silicon (Si) and Gallium Arsenide (GaAs) are accessible infrared materials. Germanium is the most popular material among other options. It provides acceptable

transmittance between 2 to 15  $\mu$ m wavelength. It requires extra attention for handling and cutting because it is very brittle. Ordinary glass cannot be used beyond 2.5  $\mu$ m as an optical material [19].

Mirrors are frequently employed in IR systems. They were used in scanners and manifold systems. Optical crown glass, synthetic fused silica, low-expansion borosilicate glass, and Zerodur are most commonly used materials for mirror production. Also, Metallic coating is applied to these mirrors for maximizing reflectivity. Protected aluminum, gold and silver are popular material choices. Due to oxidization, bare aluminum is not among the first choices.

#### 1.2.2 Detectors

Infrared detectors are responsible for the conversion of IR photons to electrical signals in IR imaging systems. Responsivity, noise equivalent power (NEP) and detectivity are main three figures of merit parameters for detectors. Responsivity is defined as a ratio of electrical output (rms) to input radiation (rms). Depending on the type of a detector unit of responsivity is volts per watt or amperes per watt.

$$R_v(\lambda, f) = \frac{V_s}{\Phi_e(\lambda)\Delta\lambda} \tag{1}$$

NEP is the signal power that gives SNR ratio of 1 in 1 Hz output bandwidth. It is defined regarding responsivity.

$$NEP = \frac{V_n}{R_v} \tag{2}$$

Detectivity (D) is simply given by:

$$D = \frac{1}{NEP} \tag{3}$$

Detectivity-star is found by Jones [20] to define FoM for detectors. D-star includes NEP and detector area. It simply provides normalized detectivity value to compare detectors.

$$D^* = D(A_d \Delta f)^{1/2} = \frac{(A_d \Delta f)^{1/2}}{NEP}$$

(4)

in which  $A_d$  is detector active area,  $\Delta f$  is noise equivalent bandwidth. Unit of  $D^*$  is Jones.

$$\left[\frac{cm - Hz^{1/2}}{Watt}\right] \equiv Jones \tag{5}$$

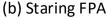

#### 1.2.3 Cooling of IR Detectors

Depending on detector material some detectors require cooling for optimum performance. Dark current levels are reduced at some absolute low temperatures. For instance, cryogenic (77 K) coolers are used for the MWIR and LWIR detectors. Specifically, mercury cadmium telluride (HgCdTe) which is the most popular 8-14  $\mu$ m detector operates the best at cryogenic temperatures. Cryogenic coolers are not efficient devices. The efficiency of cooling mechanism is around 4 %. Thus, system design of cooled IR detectors requires extra attention if the system is portable. The power consumption of the ROIC becomes significant due to low cooling efficiency. Even, system designers should consider number and shape wire bonds inside cooler from FPA to daughter board. Gold wire bonds radiate heat that is coming from FPA. Joule-Thomson and Stirling cycle refrigerator are the most popular closed cycle cooling systems. Fig. 7 shows dewar with Stirling cooler. The top part is plated with gold for shielding, and it contains FPA.

Depending on detector or performance thermoelectric cooling (TEC) is a choice for infrared imaging systems. Since cryogenic cooling requires dewar filled with  $LN_2$ , TEC becomes a cheap and compact solution. TEC's can achieve around 200 K with hermetic encapsulation. SWIR detectors do not require cryogenic cooling. Room temperature or TEC is sufficient for a typical SWIR detector.

Thermoelectric coolers work in the principle of Peltier effect. Choice of thermoelectric material is necessary and following formula can be used to determine figure of merit;

$$ZT = \frac{S^2\sigma}{k},\tag{6}$$

in which S is the Seebeck coefficient, T is average temperature, and sigma is electrical, and k is thermal conductivity.

(a) Stirling-cycle engine

(b) 4 stage thermoelectric cooler

Figure 6: Cooling IR detectors (a) Stirling cycle engine (b) four stage thermoelectric cooler.

#### 1.2.4 Proximity Board

Proximity board consists of different layers depending on the output of FPA. If FPA has an analog output, proximity board should have ADC's. All digital corrections and post-processing require being done in a digital domain. If FPA has a digital output, serial drivers such as LVDS are necessary for carrying signals to processor or FPGA. Inside the processing unit, further signal processing is applied to eliminate fixed pattern noise, non-uniformity correction, dead pixel correction. Non-uniformity correction and dead-pixel replacement are the most fundamental image processing algorithms for infrared imagers. Due to, all the detectors suffer from spatial non-uniformity and manufacturing defects.

Depending on application some sophisticated post-processing algorithms may be performed such as locking to moving objects, image fusion and, human detection on hardware or software level. Detecting human and moving objects are must have features for surveillance systems. On the other hand, image fusion element gains ground for advanced infrared imaging systems [22–26]. Image fusion is processing more than one image that comes from different sensors, into a single image. That image is a combination of essential features from various sensors. Image fusion is used in remote sensing, medical and infrared imaging systems. As mentioned

Figure 7: Crayogenic Dewar with Stirling cooler [21].

before LWIR and MWIR systems contains only heat information. Defining objects with only LWIR and MWIR information is hard. SWIR provides details such as shape and pattern of the object. Image fusion of SWIR and thermal imaging bands improves the quality of output for better detectivity. Fig. 8 shows SWIR, LWIR and hinted SWIR version of a scene. In SWIR, it is hard to identify a human being. In contrary, LWIR clearly highlights the human, but it lacks information from the

Figure 8: SWIR and LWIR Image fusion [27].

surroundings.

Furthermore, proximity board provides biases and supplies to ROIC and detector. Bias points can be adjustable via some digital interface on the board. Adjustable biases are essential to calibrate FPA. All supplies and biases coming from the board should have low noise levels to improve the performance of the system.

Digital programming of FPA also has been done on proximity board. Depending on communication protocol proximity board provides relevant digital signals. In general, FPA's comes with certain functionalities. To activate those functionalities, ROIC contains serial or parallel digital interface. Gain settings, integration time, windowing, frame speed adjustment, and dead pixel elimination are typical ROIC functions.

Finally, proximity board outputs processed image into industrial standard interfaces such as Camera Link and GigE.

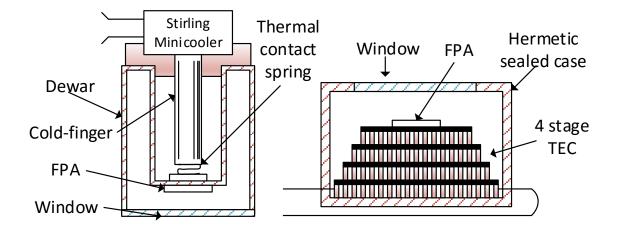

#### **1.3 Readout Integrated Circuits**

ROIC is one of the key components of imaging systems. It is responsible for acquiring detector signal by integration and transfer it to the signal processing components. In other words, ROIC provides charge to voltage conversion. Signal chain block diagram of FPA is shown in Fig. 9. In short, an analog ROIC consists of a

Figure 9: Block diagram of an analog readout [18].

unit cell, multiplexer, and output amplifier. In digital ROIC, the multiplexer is connected to column ADC. Instead of the output amplifier, the serial interface is used to output digital data. In ROIC designer wants to achieve the best performance for transferring photocurrent which can be defined as low noise, high SNR, and high injection efficiency.

Readout noise is undesirable, but it is unavoidable and fundamental part of the system. All ROICs suffer from readout noise which can be defined as a random variation of the output voltage level which is independent of the input current of the amplifier. Photons are emitted by light sources and emission process is defined by Poisson distribution which is a discrete probability of a given number of events occurring in a determined period. Commonly represented formula of Poisson distribution is equal to

$$P(\chi;\lambda) = \frac{\lambda^{\chi} \cdot e^{-\lambda}}{\chi!} \tag{7}$$

$\lambda$  represents an average number of electrons which also equal to the variance. This phenomenon is known as Poisson noise or shot noise.

Ideal SNR can be defined the only square root of the electrons collected ignoring

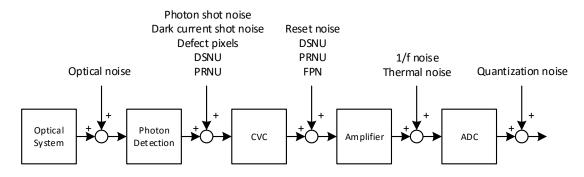

Figure 10: Noise sources in the imaging system [28].

readout noise contributions. Unfortunately, there are many noise contributions in the system, Fig. 10 shows all the noise sources that are coming from each stage. Optical noise occurs due to imperfections on the surface of a lens, coating, and material. DSNU and PRNU are dark signal non-uniformity and pixel response nonuniformity, respectively. These noise sources can be corrected with post-processing (using processor or FPGA) because they are spatial noises which do not depend on time. Fixed pattern noise (FPN) is also a spatial noise which comes from different responsivity of the pixels for the same illumination. Temporal noise sources are shot noise, reset noise (kTC noise), thermal noise (Johnson-Nyquist noise), 1/f noise and quantization noise [28].

Reset noise in order words kTC noise requires more attention to designers for low noise applications. Integration capacitance resets to fixed voltage value (reset voltage) at the beginning of a frame. Due to Maxwell-Boltzmann distribution of the number of the electrons on the capacitor, the voltage on the capacitor fluctuates and exact value is not defined. Reset voltage varies between reset cycles within some electron range depending on various effects such as design and temperature. This variation is called kTC noise or reset noise.

There is a fundamental method to remove reset noise which is called correlated double sampling (CDS). The CDS should take two samples for each frame; the first one is just after reset, and the second one is at the end of the integration. The difference between two sample will remove the reset noise because both samples introduced to the same level of reset voltage bias. This method is widely used not only FPAs but also CMOS and CCD sensors [29]. There are analog and digital implementations of this method. New generation readouts utilize a digital implementation of CDS because of it does not consume pixel space, and it provides calculation

| ROIC Performance<br>Parameters | Related System<br>Parameters            | Comments                             |

|--------------------------------|-----------------------------------------|--------------------------------------|

| Input referred noise           | Sensitivity                             | Reduce to enhance SNR                |

| Charge handling capacity       | Integration time and<br>photo-current   | Current handling range               |

| Power dissipation              | Cooldown time,<br>life time ,and weight | SWaP                                 |

| Crosstalk                      | Blooming of<br>saturated elements       | Element to element                   |

| Dynamic Range                  | Maximum saturation<br>signal            | Loss of signal                       |

| Linearity reliability          | Calibration                             | Proper identification                |

| Gain                           | Sensitivity                             | Signal amlifier<br>above noise floor |

| Uniformity                     | Fixed pattern noise                     | Eliminated with<br>post processing   |

Table 1: ROIC performance requirements and its relation with system parameters [18]

flexibility and less complexity.

### **1.4 ROIC Performance Parameters**

ROIC performance parameters strongly depend on detector and application. For instance, the detector type and its performance affect charge handling capacity. If a detector is a dark current level high small integration capacitance may saturate easily. Thus, high charge handling capacity can be the desired parameter for that kind of detector.

Designers do not have much choice regarding technology. Excluding DROIC's all other ROIC's uses 180 nm and bigger CMOS nodes mature technologies. Those technology nodes offer an excellent price-performance ratio. All these parameters should be considered regarding these technologies.

Table 1 summarizes critical ROIC performance parameters and their effects on system requirements. Some of the important concepts will be explained following subsections.

#### 1.4.1 Charge Handling Capacity

Most of the detectors that used in FPA's are photoconductors. Thus, an output of the detector is photo-current. ROIC integrates these currents into capacitance in each pixel. The capacitor is a dominant device inside the pixel. Photon emission process is defined by Poisson distribution, and it shows shot noise behavior. So, capacitances store not only signal charge but also store noise which is proportional to square root of the stored signal. Hence, charge handling capacity is essential for improving SNR. Depending on interested wavelength charge handling requirements change. Photocurrents in SWIR typically between 10pA-3nA. On the contrary, typical LWIR photocurrent level is 10nA. It may go up to hundreds of nanoamperes. At the same time, an application is also the important parameter to determine charge handling capacity. For instance, space observation systems do not require significant charge handling capacity because photocurrent levels coming from stars are very low.

There is a tradeoff between charge handling capacity and pixel size due to capacitance size. Since charge handling capacity is necessary for noise and applications, detector trend pushes designers to smaller pixel pitch sizes and bigger arrays. In recent systems, spatial resolution is needed for detection than charge handling capacity. In very near future, smaller than 10  $\mu$ m pitch sized detectors and systems will attract considerable attention.

Charge handling capacity  $(e^{-})$  of analog preamplifier can be calculated simply by capacitance formula:

$$Charge Handling Capacity(e^{-}) = \frac{C\Delta V}{q}$$

(8)

#### 1.4.2 Frame Rate

The frame rate is the frequency of sequenced frame data out of the ROIC. The frame rate is counted per second. The human eye and brain interpret more than 25 frames per second (fps) data as video. Most of the imaging systems work at 50 Hz. However, some scientific or military systems require higher frame rate such as 400 Hz. From IC designers perspective high frame rate requires high throughput. High throughput results into high power consumption and design challenges. Specifically, the magnitude of those challenges gets bigger for large array sizes.

#### 1.4.3 Input Referred Noise

Input referred noise electrons defines minimum detection floor of the ROIC. There are many contributions to input referred noise from unit cell. KTC noise of the integration capacitor, preamplifier, multiplexer, and buffer noises are square summed at the output and divided into transfer function of the ROIC. The final value is input referred noise. Depending on operating wavelength typical noise values vary. Due to high shot noise in LWIR and MWIR bands, 1000-100  $e^-$  noise range is typical. A SWIR can have lower than 10  $e^-$ .

#### 1.4.4 Dynamic Range

Definition of dynamic range is universal. In ROIC, dynamic range is the ratio of the maximum detectable signal level without saturation over minimum detectable input signal. Maximum range is limited with charge handling capacity, and minimum range is input referred noise floor. Dynamic range is a number, and it is defined in dB.

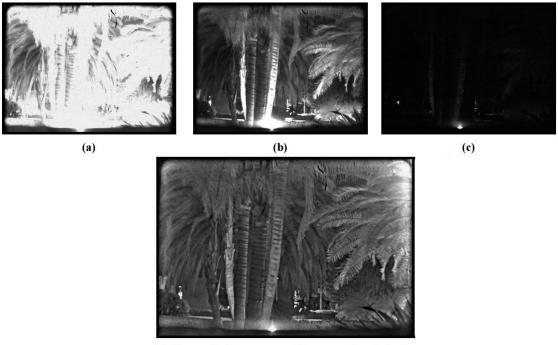

ROIC with ultra high dynamic range provides high contrast and accuracy for target scenes. Bright areas will not saturate easily, and dark zones will include more information. Fig. 11 compares regular and high dynamic range images. In a normal image, bright and dark zones lost all the information. Saturated traffic signs are readable, and branch of trees are visible, in HDR image. Also, the road is not bright anymore, and the pattern is apparent.

Dynamic range is defined by;

$$DR = \frac{DR_{Hi}}{DR_{Lo}} = \frac{ChargeHandlingCapacity}{InputReferredNoise}$$

(9)

or

$$DR[dB] = 20\log \frac{DR_{Hi}}{DR_{Lo}} \tag{10}$$

Figure 11: High dynamic image vs regular image [30].

#### 1.4.5 Linearity

The relationship between photocurrent and the integrated charge should be linear. 95 % linearity is acceptable for most of the ROIC's. If ROIC has high nonlinearity output data either maps to dark or bright pixels. Linearity is also performance parameter for detectors. In modern technologies using well-known detector materials, 99 % linearity is achievable.

#### 1.4.6 Uniformity

In FPA's, non-uniformity is inevitable. Due to mismatches and process variations, both pixels of ROIC suffers from non-uniformity. In other words, for a same photocurrent level pixel to pixel response is different.

Uniformity is also valid for detectors. In there, a cause of non-uniformity is fixed pattern noise. Dark signal non-uniformity (DSNU) and pixel response nonuniformity (PRNU) reasons of fixed pattern noise. DSNU is observed as a difference offset amount dark pixels. PRNU is pixel-wise variation under fixed illumination.

Non-uniformity is well known and studied subject; it is corrected in post-processing.

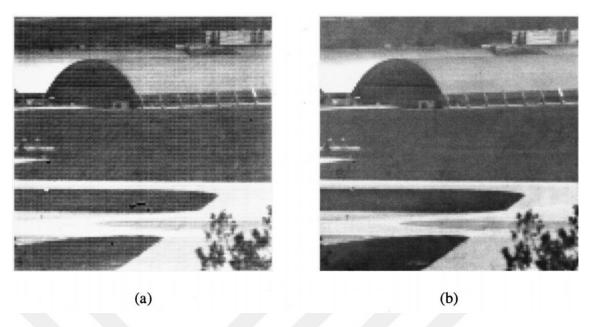

Figure 12: Non-uniformity correction, a) raw image b) corrected image [31].

Fig. 12 shows the comparison of the raw and corrected image. There is a visible pattern in Fig. 12 a) that pattern is corrected well in b). Non-uniformity correction (NUC) algorithm creates a map for both PRNU and DSNU which contains offset correction values for each pixel. That map is added on top of the output image. To generate correction map, FPA is calibrated with uniform dark and average hot (illuminated) scenes. Algorithm corrects for different illumination levels. In literature, there are many studies regarding efficiency and low power NUC algorithms.

#### 1.4.7 Power Dissipation

Power dissipation is crucial for portable and cooled systems. For system perspective, low heat translates into a compact cooler, long operation time and increased lifetime. Moreover, reducing power dissipation shortens cooling time. Thus, infrared imaging system will be operational in very short period. Size, weight, and power reduction (SWaP) trend forces to swap large systems. The ongoing developments are trying to reduce system sizes (cooler size) without sacrificing performance (resolution and speed). Tactical and high-performance systems do not have strict power consumption parameters.

#### 1.4.8 Gain

Integration capacitance inside the unit cell is not one-piece for almost all ROIC's. A user has the flexibility to increase or decrease total integration capacitance size at some point. This option gives a user to adapt low or high flux environments. Low capacitance provides better kTC noise performance, and high capacitance does not saturate easily. The user has 2 or 3 gain options. That option is manually selected for all array.

#### 1.5 Motivation

This thesis is in the design of readout integrated circuits (ROIC) for infrared focal plane arrays (FPAs) with high dynamic range (HDR), utilizing a smart input circuit selection mechanism. HDR for ROIC means very dark and bright signal levels is processed at the same time, which in return results in a low noise level and high SNR. In practical terms, HDR enables high contrast and accuracy which finds itself many applications from security to industry. The purpose of the proposed thesis will be to show a new approach to achieving high SNR levels and create novel and smart circuit approaches that are applicable for next generation analog ROICs.

The typical unit cell of an ROIC consists of the input amplifier, gain switches, multiplexer, output amplifier and some control switches. For a standard single band detector array, an ROIC uses only single input amplifier which optimized for average performance. Moreover, gain switches inside unit cell used to adjust capacitance value at the integration node which allows changing charge handling capacity. In order words, increasing integration capacitance allows handling larger signals while compromising noise performance.

This thesis focuses on achieving high dynamic range for an ROIC. A novel method is applied to a unit cell. Instead of using single input circuits, two input circuits which are optimized for different signal levels placed inside each pixel. A smart circuit mechanism, which decides best input circuit according to incoming light level, is also designed for each pixel. In short, an individual pixel can select best input amplifier circuit that is performing best SNR for the incoming signal level.

#### **1.6** Thesis Objectives

Up to now, ROIC's that have HDR capabilities designed and implemented on top the known architectures. Ideas and improvements are limited to minor changes inside unit cell. Meanwhile, HDR is a hot topic in image and signal processing world. People are trying to enhance capabilities of existing hardware with novel and efficient algorithms. They are always limited with boundaries of the hardware.

DROICs are recent technologies that achieve high dynamic ranges which exceed analog ROICs. Until today, there is no commercially available DROIC inside an IR system. Main reason is expensive for two-dimensional FPAs DROIC requires at least 90nm technology. As oppose to the recent trend, pixel sizes are big. Their advantage is with high charge handling capacities which enable them to achieve HDR. That limits their operation between MWIR and LWIR bands which have high photocurrents. Moreover, the noise floor is high compared to analog ROICs.

In the light of these points that mentioned above, the first objective of the thesis is to achieve HDR with low input referred noise (noise floor). Novel methods are employed to realize this architecture. That will be accomplished with analog ROIC concepts to avoid disadvantages of DROICs.

Another objective is compatibility with  $3^{rd}$  generation detectors.  $3^{rd}$  detectors promises more than detection of more than one band within the single pixel. Proposed ROIC architecture promises not only HDR but also a wide operating range (wide band operation).

#### 1.7 Organization

This thesis is organized as follows:

The first chapter starts with the brief history of IR detectors. Then, it gives the overview regarding infrared imaging systems. In the following section, ROIC and its performance parameters are discussed. Finally, motivation and objectives of the thesis presented.

Chapter two provides detailed information regarding ROIC architectures. Then, proposed smart pixel structure and alternative architectures will be discussed in detail.

The third chapter is devoted to the implementation of proposed architecture.

32x32 ROIC is implemented to prove proposed idea. Design and implementation of the sub-blocks of the prototype will be provided.

Measurement results of the prototype are presented and discussed in the fourth chapter. Measurement equipment and methods also explained in there.

Last chapter summarizes proposed points of novel architecture along with pluses and minuses. Future design perspective is given utilizing proposed architecture.

# 2 ROIC Architectures

ROIC made it possible two-dimensional FPAs in the 1970s. Early ROIC's was based on custom charge-coupled device (CCD) technology. Today, CMOS technology offers cheap, low power, and highly integrated solutions to ROIC requirements.

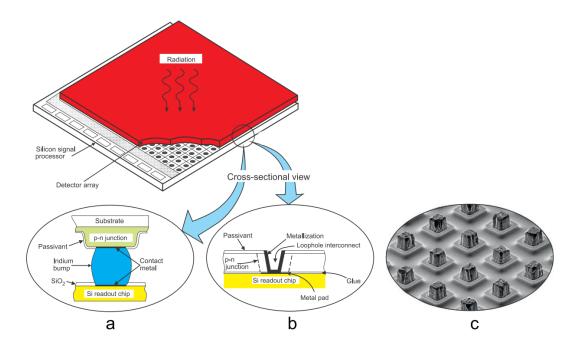

ROIC provides integration of photocurrent and multiplexing from a large number of pixels. In other words, it provides charge to voltage conversion and multiplexing. Integration is the keyword. Not only ROIC is integrated by itself but also ROIC + Detector integration key technology. That integration is called hybridization. Fig. 13 represents hybridization techniques. The most popular technique is indium bumps. Indium bumps provide low resistance and soft contact between detector and ROIC pixels. Due to properties of indium, this technique is compatible with cryogenic temperatures. Indium stays soft even at that temperature levels.

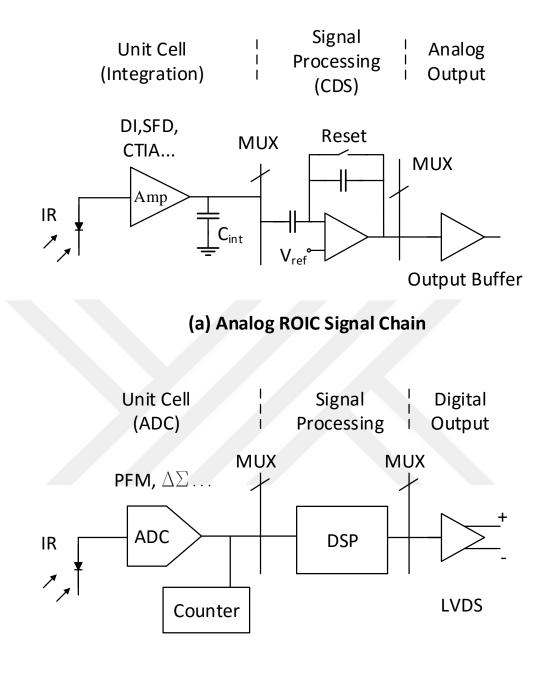

Modern ROIC's that are used in FPA's can be categorized into two; analog and digital. Analog ROIC or ROIC integrates photocurrent and stores it into a capacitance. Analog pixel output is multiplexed to an output buffer. Some ROICs employ column ADC's; pixel output is digitalized, and output of ROIC becomes digital. The signal flow of DROIC is a little bit different than analog ROIC. ADC

**Figure 13:** Hybridizated FPA (a) an indium bump (b) loophole technique (c) SEM photo of indium bumps [32].

(b) Digital ROIC Signal Chain

conversion is done inside a unit pixel. Data is stored in digital domain inside the pixel. Instead of video buffer, a serial digital interface will output signal information.

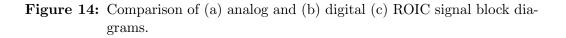

Fig. 14 shows analog and digital ROIC signal chains. Analog ROIC consists of a unit cell, multiplexer and optional signal processing module (in this case CDS) and output amplifier. Digital ROIC consists of in-pixel ADC, some signal processing module, and a digital serial output amplifier (LVDS). The main difference between two architectures lays inside a unit cell. One of them stores integrated charge into capacitance, other stores it inside a counter.

Analog ROIC may also have digital output amplifier (LVDS). Analog ROICs with column ADCs are quite popular. So these architectures also utilize benefits of digital output.

Each architecture has some advantages and drawbacks one to another. In the market, analog ROICs are dominated by a huge margin. 99 % of the market uses analog ROICs inside their FPAs. In literature, various DROIC architectures are available. There are many universities and companies available studying on DROIC. Table 2 compares both architectures with their advantages and drawbacks.

After charge-to-voltage conversion inside the pixel, there are two possible processing methods. The first method is multiplexing analog voltage to an outside of the FPA where it can be read by proximity card which consists off-chip electronics. The second method is using column ADC and converting analog data into digital and output digitally. Both approaches require different attention for designing proximity card. A user may need 14-16 bit ADC chip to sample an analog output. Depending on the speed of digital output some unique interfaces may need to acquire data such as LVDS. LVDS can typically provide around 650 Mbit/s speed, and it may go up to a rate of 3 Gbit/s. In both ways, analog to digital conversion is required at the same level to further process data. Final post-processing can be done with FPGA, ASIC or high-speed processor.

## 2.1 Analog ROIC Sub-blocks

#### 2.1.1 Preamplifiers

The most critical part of the analog readout is preamplifier. Choice of preamplifier depends on many parameters such as frame rate, injection efficiency, and noise. As mentioned previously preamplifier contains a significant part of noise contributions of the system. Thus, if a designer wants to improve SNR of the system, preamplifier selection is crucial.

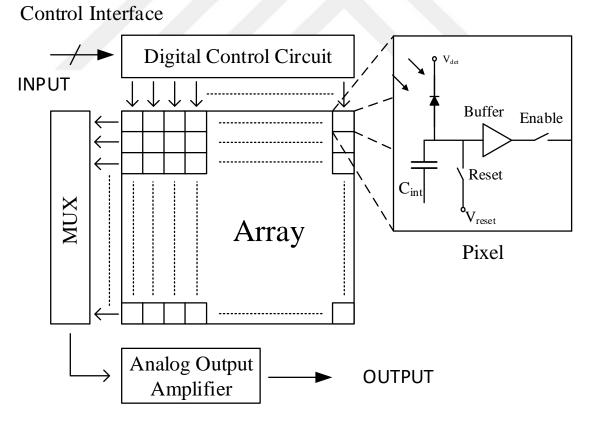

Basic unit cell operation is shown in Fig 16. Initially, reset switch is active

|            | Analog ROIC                                                                                                                                                            | Digital ROIC                                                                                                                                                          |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Advantages | <ul> <li>+ Reliable architecture</li> <li>+ Small pitch sizes</li> <li>+ Works all bands</li> <li>+ Cheap</li> <li>+ Low noise</li> <li>+ Big array size</li> </ul>    | <ul> <li>+ High charge handling<br/>capacity</li> <li>+ High dynamic range</li> <li>+ Low power architectures<br/>available</li> <li>+ Simple architecture</li> </ul> |

| Drawbacks  | <ul> <li>Limited charge handling capacity</li> <li>Charge handling limited with capacitance size</li> <li>Relavityle complex</li> <li>Analog signal routing</li> </ul> | <ul> <li>Commercially not available</li> <li>Expensive tech. cost</li> <li>High noise floor</li> <li>Susceptible to switching noise</li> </ul>                        |

Table 2: Advantages and drawback of Analog and Digital ROICs.

Serial/Parallel

Figure 15: Architecture of analog readout integrated circuit.

Figure 16: Schematic of unit cell operation.

and the detector is biased between  $V_{det}$  and  $V_{reset}$  voltages. Integration operation immediately starts after reset switch becomes open. During integration, according to light level and detector bias, DC current is integrated on  $C_{int}$  capacitor.  $C_{int}$ consists of all parasitic capacitances in that node, the input capacitance of buffer, integration capacitance, and interconnection capacitances.

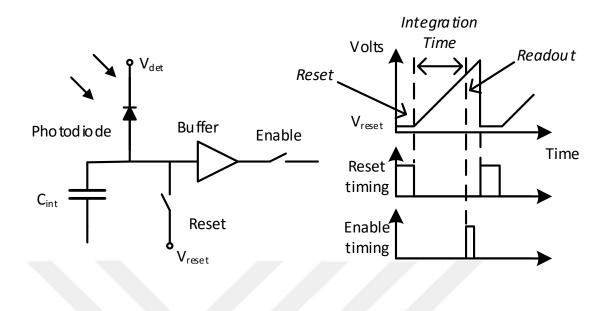

Preamplifier which is located inside a unit cell is the first electrical interface between ROIC and detector, which is also responsible for the integration of current and charge to voltage conversion. Detector characteristics such as input impedance, detector bias and input current determine preamplifier topology. There are various types of preamplifiers, but most common ones are a direct injection (DI), source follower per detector (SFD) and capacitive transimpedance amplifier (CTIA). Two critical parameters can be used to determine amplifier type for a pixel. These are illumination level and readout frame rate. These parameters will be used to determine well capacity and noise performance of the pixel.

DI consists of an only single transistor, and it has very small circuit area. It is commonly used for high flux applications due to high well capacity. It shows poor injection efficiency under low flux applications. Since it consists of single transistor

| Topology                                             | Advantages                                                                                              | Disadvantages                                                     | Comments                              |

|------------------------------------------------------|---------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|---------------------------------------|

| Direct Injection<br>(DI)                             | Low power<br>Large well capacity<br>Constant detector bias<br>LWIR, MWIR<br>Low noise                   | Poor performance<br>with low flux                                 | Popular for high<br>flux applications |

| Capacitance<br>Transimpedance<br>Amplifier<br>(CTIA) | Highly linear<br>Stable detector bias<br>Wide dynamic range<br>High Gain                                | High power<br>Complex<br>Large footprint                          | Best choice for<br>SWIR               |

| Source Follower<br>per<br>Detector (SFD)             | Simple<br>Small<br>Low Noise<br>Low Power                                                               | Gain <1                                                           | Commonly used in<br>IR astronomy      |

| Buffered Direct<br>Injection (BDI)                   | Detector bias is set<br>independently<br>High injection<br>efficiency<br>Improved frequency<br>response | More complex<br>Mid noise compared<br>to DI<br>Needs compensation | Rarely used                           |

Table 3: Comparison of popular preamplifier topologies.

power dissipation of pixel is very low. Because of these properties, DI is widely used for LWIR and MWIR imaging applications.

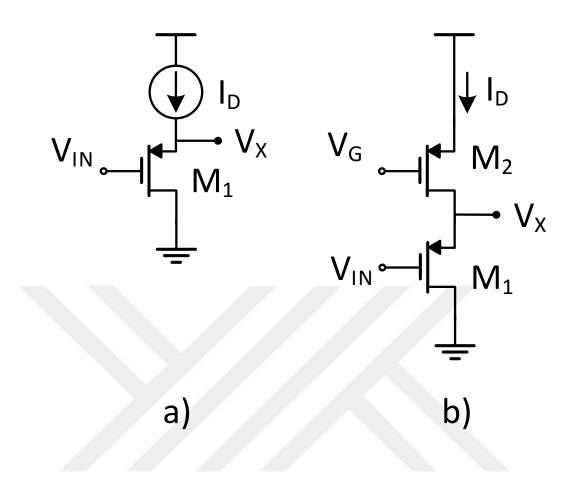

SFD architecture is also very compact and low power. It consists of only three transistors. Unlike DI, SFD is more suitable for low flux applications such as CMOS image sensors and SWIR due to small well capacity (100,000 electrons). It poorly performs under high flux applications.

CTIA is very flexible and can be used for all type of detectors. It has very high linearity for low flux application and high noise compared to SFD. It performs poorly under high flux applications compared to DI. Well capacity is around 1 million electrons. Due to the complexity of structure and number of transistors it requires high power. High linearity for low flux and medium size full well capacity make this favorable architecture choice for SWIR applications. Fig 17. shows all three the most basic amplifiers that are used in ROICs.

### 2.1.2 Signal Processing

One of the most popular and fundamental signal processing for ROIC is correlated double sampling (CDS). CDS eliminates correlated noise, kTC switching noise.

Figure 17: The most popular types of amplifiers used in readout circuits.

KTC noise also known as thermal noise is generated at the end of reset cycle. Noise  $(v_n = \sqrt{\frac{kT}{C}})$  is stored on capacitor  $(C_int)$  until beginning of next cycle [33,34]. Integration capacitance is measured twice to eliminate noise. First, voltage value after the reset cycle is stored. At the end of integration voltage value on the integration capacitance saved the second time. The difference value is free from offset and kTC noise.

KTC noise is caused by thermodynamic fluctuation of the charge on the capacitor. Once the capacitor is isolated from a source, the variation is frozen at same random value. Fig. 18 represents reset uncertainty for different integrations. Electrical charge of the reset noise on the integration capacitor can be represented as standard deviation [35],

Figure 18: Reset uncertainty due to thermodynamic fluctuations.

$$Q_n = \sqrt{k_B T C} \tag{11}$$

where  $k_B$  is the Boltzmann's constant, T is the temperature in Kelvin, and C is integration capacitance.

### 2.1.3 Output Buffer

The output buffer is responsible for transferring different pixel voltage values to outside world. If FPA is working in cryogenic temperatures, output buffer should be able to drive long cryogenic interface cables. Designer pays attention to following points for output buffer; power dissipation, frequency response, and slew rate.

Output load  $(C_L)$  is the limiting factor designing output buffer. The output of the buffer is series of pulses with different voltage levels. Since the output is a pulse, GBW product of the buffer should be large enough. Slew rate is another critical parameter. Since buffer deals with series of pulses with different amplitudes, the buffer should be able to charge and discharge load fast to generate non-distorted pulses. Otherwise, amplitudes of pulses may not be accurate.

There are two traditional topologies of video output buffer which shown in Fig. 20. The most common method is source follower. It is relatively low power, and the

Figure 19: Correlated double sampling timings, block diagram, and implementation.

circuit is less complex. Another method is push-pull topology. Push-pull design is complicated than source follower. Push-pull needs to appropriately biased; quiescent current should be provided to transistors active. Push pull has advantages over source follower regarding power consumption.

$$E(C_L) = \frac{1}{2} C_L \Delta V_{max}^2[J]$$

(12)

In the push-pull topology, the total power is calculated multiplying the energy and the repetition rate, and adding the energy required to provide the idle current [18].

$$P_{out}(min) > \frac{0.5C_L \Delta V_{max}^2}{T_{frame}} + (\Delta V_{max} + 1.5)I_{idle}[W]$$

$$\tag{13}$$

in which  $C_L$  is the total output load,  $\Delta V_{max}$  is the maximum output swing,  $T_{frame}$  is the time between two frames.

#### 2.1.4 Digital Control

Digital control blocks exist in all ROICs. It is responsible for generating all control signals. Integration time, controlling readout, adjusting gains, and this block provides all timing. Physically it is located on top of the unit cell array. Its height flexible but its weight is as wide as the array.

Digital control accepts inputs from outside. Clock and reset signals are essential for operation. Also, the integration time is provided to control circuit. Moreover, there are some basic functionalities such as gain adjustment, integrate while read, integrate then read, frame rate and the number of outputs. All these features can be adjusted via serial or parallel interfaces. Most of the ROICs prefer the serial interface over a parallel interface to reduce the number of pads. P

It is designed using one of the hardware description languages (Verilog or VHDL). It was very complicated to make fully custom. Then RTL code pass through digital synthesis procedure. The synthesized code was placed and routed by EDA software.

## 2.2 Proposed Architecture of the Smart Pixel

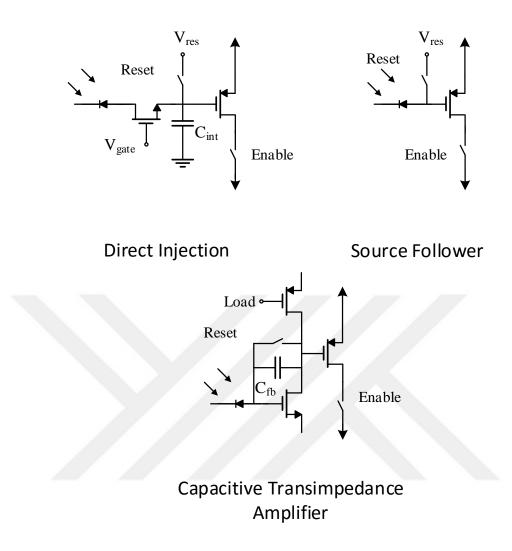

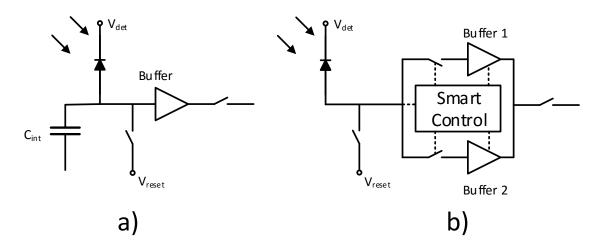

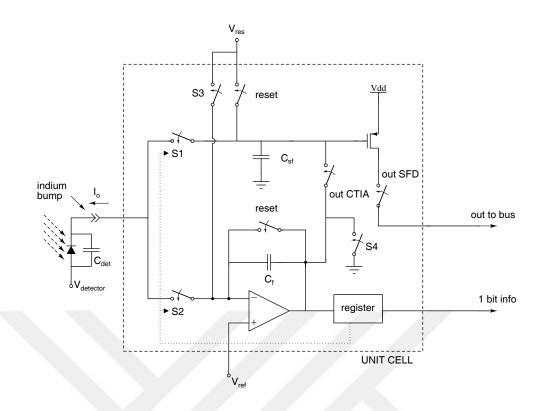

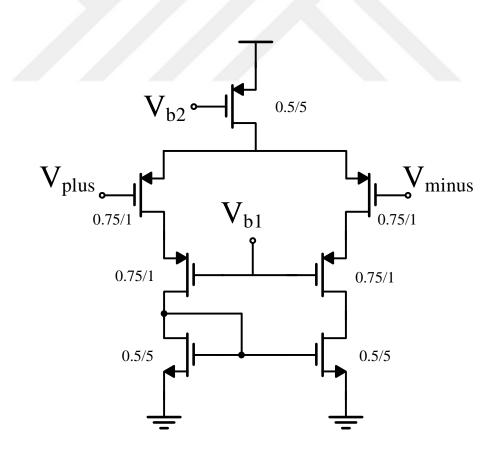

A generic pixel structure for hybrid readouts consists of the input amplifier, gain switches, control switches such as reset and enable, and a multiplexer. We have already examined this structure before along with commonly used input amplifiers. This proposed architecture uses two input amplifiers one is optimized for low illumination levels, and the other works well with relatively high illumination levels compared to first one. Fig 21 shows both regular and smart pixel architectures. Smart pixel not only distinguishes with some amplifiers but it also has an intelligent control unit.

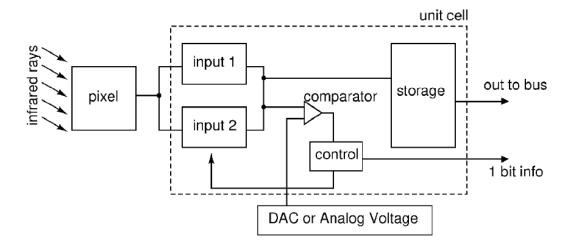

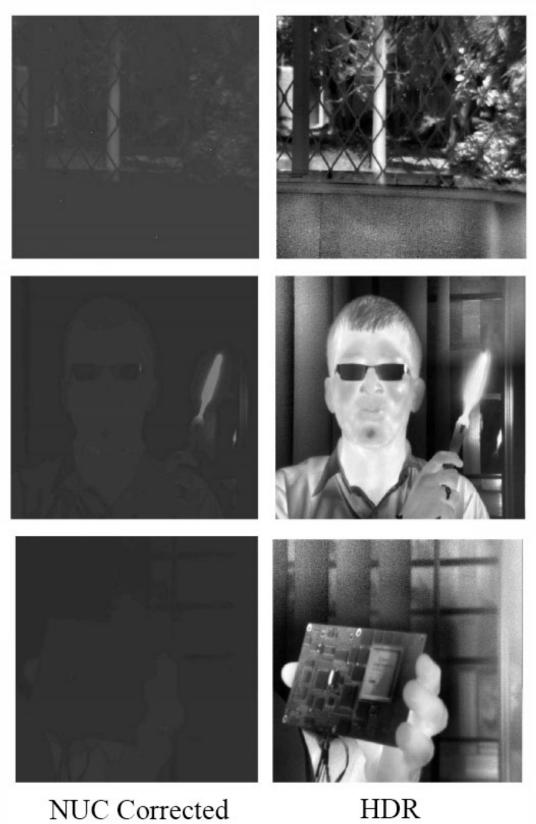

The smart control unit, which is unique and works independently for each pixel, decides which input amplifier should be active. For both low and high illuminations always best input amplifier will be selected. Hence, input dynamic range will be extended. Additionally, the smart control unit provides 1-bit information which shows selected input amplifier. This information is useful for post-processing such as nonuniformity correction.

There are two possible mechanisms for smart control pixel which is the heart of the smart pixel. The first method is depending on previously integrated illumination

Figure 21: a) Standard pixel structure b) smart pixel architecture.

level. In this approach, if flux information from previous integration was low, in the present integration low flux optimized input stage is selected. When low illumination optimized input stage is selected, but incoming flux level is high, in the following integration high illumination optimized input stage will be chosen. This method has some drawbacks using best input amplifier may not be possible for fast changing scenes.

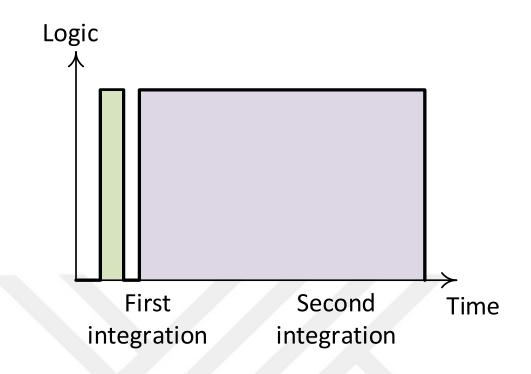

In the ideal world, each pixel should detect incoming light level and select best input amplifier. The second scheme tries to achieve an ideal scenario. In this scheme, there are two integrations. First integration is very short compared to the second (actual) integration. The charge which obtained from said first integration would be used to determine light level by the smart control unit. The intelligent control unit determines and activates best input amplifier for actual integration. Fig 21 shows the representation of timing diagram of the two-level integration.

For detecting light level, one of the amplifiers must be used. To obtain more gain and sensitivity low illumination level optimized amplifier is used as a default. Control mechanism compares acquired charge from first integration and certain threshold voltage. If the integrated charge is less than that certain threshold level, then the first input stage is chosen. Otherwise, the other input stage is activated by the smart control circuit. DAC can monitor this threshold voltage, and same value will be used for all pixels. Changing and modifying threshold voltage value gives

Figure 22: Two step integration. First integration is for detecting light level second one is actual integration of light.

flexibility to user favoring which amplifier to use mostly. For further improvement and flexibility hysteresis may be added to decision mechanism but this makes pixel structure complicated.

There are a couple of intuitive features and practicalities that come with smart pixel architecture. One of them is the flexibility of using dual-band detectors because two different input stages are already presented. Most of the dual-band detectors have single bonding area which makes it compatible with this architecture. Another extra feature is to be able to select one of the input amplifiers for whole FPA instead of automatic selection. That manual selection provides some power consumption if a user continuously observes very dark or bright objects. Block level architecture of smart pixel is presented in Fig 23.

Highlights from smart pixel architecture:

• There are two input amplifiers inside the pixel. One is optimized for low illumination levels; another one is optimized for high light levels.

Figure 23: Detailed block diagram of the smart pixel.

- Smart control unit selects best input amplifier according to light level. This mechanism is located inside each pixel.

- Decision mechanism of the smart control unit is based on two-level integration. First integration is very short, and voltage accumulated during this integration will be used to determine best input amplifier.

- Threshold level of decision mechanism is controlled outside with some voltage level.

- Since optimum input amplifier is selected for each frame; best SNR value is achieved for FPA.

- 1-bit digital information also provided by pixel for post processing such as non-uniformity correction.

- User has flexibility between the automatic or manual selection of input amplifiers for pixels. Manuel mode selects amplifier for whole ROIC.

- Since it has two input amplifiers pixel is compatible with dual-band detectors by design.

This whole smart pixel architecture applies to wide range NIR-SWIR detectors. It helps to extend the dynamic range of near visible (NIR) and shortwave infrared (SWIR) image sensors by improving SNR value. This band has a broad range of photocurrent output. This topology is also compatible with other combinations from all infrared spectrum from NIR to LWIR.

# 2.3 High Dynamic Range Imaging

Human eye discriminates around 10 million colors. Today's modern monitors are features 24 bit RGB color (True Color). 24-bit means that each color (Red, Green, and Blue) is represented with 2<sup>8</sup> different tones(shades). Total of 2<sup>24</sup> or 16,777,216 color variations are possible [36]. There is also 32-bit color standard which uses different color space RGBA. "A" in the RGBA stands for alpha which contains transparency information. Thus, each color of 32-bit color space has again represented with 8-bit shades.

The deep color format supports 30/36/48 bits, and per channel represented more than 8 bits, as 10/12/16 respectively. Video cards support deep color formats. Also, imaging software's can handle deep color images. Hardware support is very limited. Only some professional monitors support 30-bit color (1.07 billion). Thus, it is fair to ask why we need more bits or high dynamic range when the hardware is limited to display images and videos. Even human eye cannot distinguish that much wide color space.

For infrared imaging systems, color space is limited to a single color. In term of SWIR, all images and videos are grayscale. Human eye barely differentiates between 8-bit and 10-bit grayscale images. It may not matter for the human eye and vision; it matters from image processing perspective.

Professional DSLR cameras, mobile phone cameras and infrared imaging systems processes and works more than 8-bit information for each channel. Processing with only 8 bit of data causes loss of information and artifacts on an image. This is the reason why we need more than 8-bit color. For instance, mobile phone's camera outputs at least 10-12 bit image. Many color enhancement algorithms applied on a picture by processor chip. After all, processing is done, the image is converted into 8-bit. First of all, 8-bit image or video save a lot of disk space. All popular compressed image and video formats support 8-bit per channel [37]. Moreover, 8-bit hardware display support is cheap and everywhere. Finally, human eye OK with 8-bit images.

Figure 24: NUC corrected and HDR image examples [38].

Regarding HDR infrared imaging, the question is the same; why we need  $90\,$

(d) Composite image mapped to conventional display

Figure 25: HDR imaging with different gain settings and final image [30].

dB or more dynamic range when we are not able to see it. We can only see 8 bit. Also, the answer is same; we need it for post processing. A human cannot see, but bits and voltage levels are there. It is the matter of post processing. 24 compares non-uniformity corrected normalized image and HDR image. Only NUC corrected image looks so flat details are not visible. Without post processing raw output of image sensors are not usable.

HDR post-processing enables to create 8 bit or max 10-bit images/videos that contain more visible areas. For instance, let's assume that we have a 14-bit grayscale image. There are some dark and almost saturated areas in the picture. The image looks normal to human eye. When we look at the pixels, we have information regarding dark and bright zones. High dynamic range image processing collects these information and highlights them by combining into a single 8-bit image.

The following example explains high dynamic range image processing in simple manner. Fig. 25 presents same scene with different gain settings in a), b), and c). a) contains information regarding dark zones. b) is medium gain image and c) has details about bright zones. Finally d) is the combination of all three different gain mode. Fig. 25 d) includes details and information from all three modes. Branches are more visible and light does not saturate the palm tree. Finally, there are not much dark zones in the photo.

# 3 Smart Pixel Implementation

Up to now, history of infrared detectors and infrared imaging systems are touched on. Also readout integrated systems for infrared detectors are discussed with popular preamplifier structures. In this section, implementation of the prototype ROIC which includes smart pixel architecture will be discussed along with other peripheral circuits. Detailed analysis of smart pixel architecture will be provided.

# 3.1 32x32 Prototype

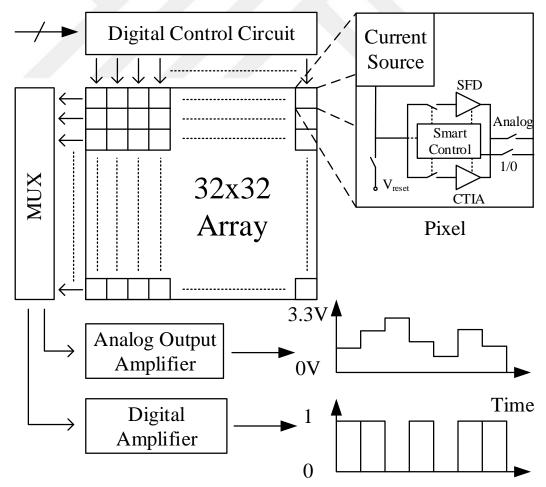

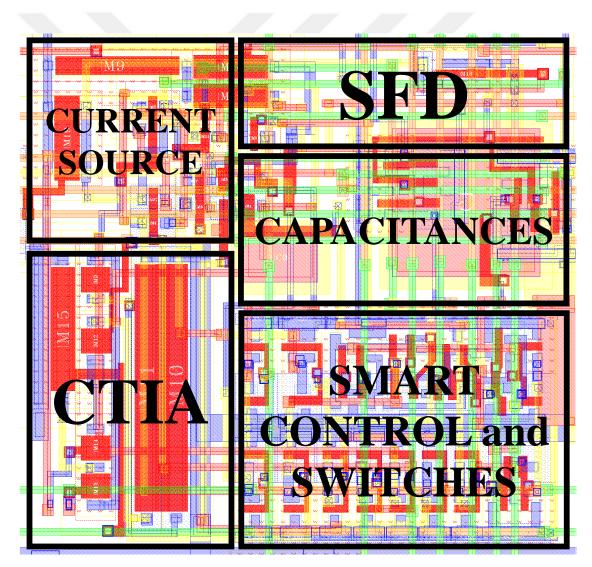

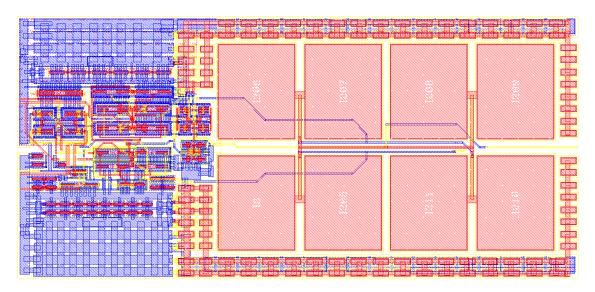

A 32x32 ROIC prototype with smart pixels is designed and fabricated using  $0.18\mu$ m XFAB technology. Architecture of ROIC is represented in Fig. 26. The ROIC includes array, current sources, digital control circuit, multiplexer and output

# Serial/Parallel Control Interface

Figure 26: Block diagram of 32x32 Smart ROIC.

amplifier. Except smart pixel overall architecture is similar to other analog ROICs.

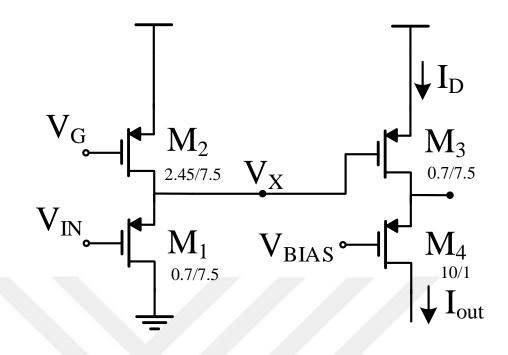

In this chip, current sources are used instead of infrared detector. Designed current source is compensated to process and mismatch variations and capable of providing current from 10pA to 3nA. Its architecture is based on [39], in order to reduce footprint of current source some optimizations are performed such as getting rid of temperature optimization part. Unlike a detector, the current sources are not hybridized to the ROIC chip, thus the detector bonding area inside the pixel is utilized for the current sources.

Along with regular analog output there is also a 1 bit digital output per pixel which comes from pixels. That 1 bit digital information indicates active amplifier. That is particularly useful.

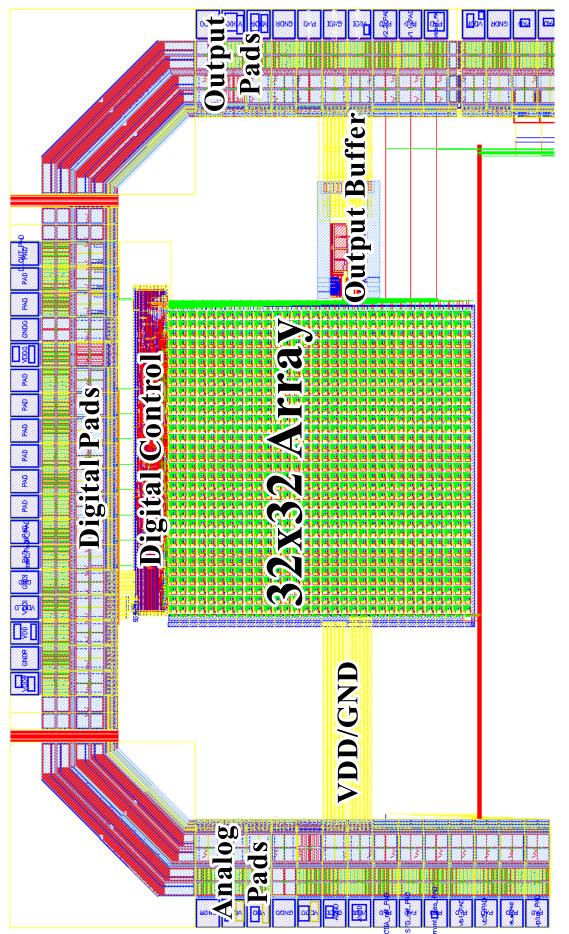

Digital control circuit provides reset, two level integration and output signals for pixels. It is serial and parallel programmable. Parallel programming allows to set pre-defined timings for integration times. Two level integration time is fully controllable via parallel and serial interface. Control circuit is designed at RTL level. Layout of the prototype is shown in Fig. 27. Array, control circuit and output buffer are tagged on Figure. Core area is 800 x 880  $\mu m^2$  which excludes output buffer. Area is pad dominated because final tapeout includes one more chip. Total multi project wafer (MPW) area is utilized.

### 3.1.1 Circuit Design Analysis

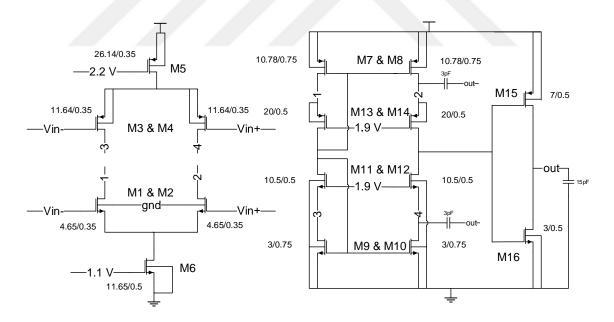

In proposed circuit design of the SWIR smart pixel, CTIA and SFD input amplifiers are selected. In general, ROIC with CTIA amplifier is used for SWIR detectors [18]. Considering very good handling of ultra low currents, high injection efficiency and linear conversion characteristics make the choice of CTIA inevitable [40]. As mentined in previous chapter CTIA consists of an inverting amplifier, integration capacitance and reset transistor which is in parallel with integration capacitance.

Integration capacitance of CTIA can be made very small unlike other topologies, because output of the unitcell is connected to amplifier output which is a low impedance node. This yields to perfect low noise performance [41].

Input referred noise of CTIA is given by:

Figure 27: Layout of 32x32 Smart ROIC.

$$N_{white}^{2} = \frac{kT}{q^{2}} \left[ \left( \frac{2T_{int}}{R_{o}} \right) + \left( \frac{C_{int} + C_{d}}{C_{L} + \frac{C_{int}C_{d}}{C_{int} + C_{d}}} \right) \left( C_{int} + \frac{C_{int} + C_{d}}{A_{vo}} \right) \right]$$

(14)

$$N_{1/f}^{2} = \frac{2T_{int}^{2}}{q^{2}} \left[ S_{fd} ln \left( \frac{1}{\pi f_{sat} T_{int}} \right) + \left( \frac{f_{s}}{f_{a}} \right)^{2} S_{fa} \left( \frac{C_{int} + \frac{C_{int} + C_{d}}{A_{vo}}}{C_{L} + \frac{C_{int} C_{d}}{C_{int} + C_{d}}} \right)^{2} ln \left( \frac{11.8f_{a}}{f_{s}} \right) \right]$$

(15)

kTC noise contributions in the formula can be eliminated with CDS. The inputreferred noise can be made small by choosing the integration capacitance small. Also, increasing the load capacitance reduces the noise bandwidth.

For a typical detector which has 2 pF detector capacitance and around 50 M $\Omega$  resistance, white noise is calculated as 85  $e^-$ . 6 fF  $C_{int}$  and 70 dB amplifier gain is used to achieve this calculation. CDS is required suppress kTC contribution. Depending on detector type effectiveness of CDS, less than 10  $e^-$  is a typical target value.

Source follower per detector consists of integration capacitance, reset transistor and source follower transistor. Integration capacitance can be calculated by adding integration capacitance and source follower input capacitance. While signal is integrated on to the capacitance, the detector bias changes since the signal is integrated directly on the same node as the detector unlike CTIA which keeps detector voltage constant [41].

The main source of white noise in the SFD is the source-follower transistor itself. Additionally, SFD is very susceptible to flicker noise [40].

Input-referred white noise electrons is given by:

$$N_{white}^2 = \frac{kT}{q^2} \left[ \frac{C_{int}}{C_L} C_{int} + \frac{2T_{int}}{R_O} \right]$$

(16)

in which for a detector with 2 pF capacitance and 50 M $\Omega$  impedance 250  $e^-$  noise is calculated for a 10  $\mu s$  integration time. less than 500  $e^-$  noise is reasonable value for a big integration capacitance in literature.

CTIA and SFD are used in the SWIR smart pixel design which they respectively cover low and high illumination levels. Choice of CTIA for low illumination level is based on its handling of very low currents and its noise performance with

Figure 28: Schematic of the SWIR smart pixel.