# UNIVERSITY OF TURKISH AERONAUTICAL ASSOCIATION INSTITUTE OF SCIENCES AND TECHNOLOGY

# DIGITAL POWER ESTIMATION USING SUBSAMPLING ANALOG-to-DIGITAL CONVERTERS FOR COMMUNICATION RECEIVERS

MASTER THESIS AYMEN MOHAMMED KHLEEL 1403630043

**Department of Electrical and Electronics Engineering**

**JUNE 2017**

# UNIVERSITY OF TURKISH AERONAUTICAL ASSOCIATION INSTITUTE OF SCIENCES AND TECHNOLOGY

# DIGITAL POWER ESTIMATION USING SUBSAMPLING ANALOG-to-DIGITAL CONVERTERS FOR COMMUNICATION RECEIVERS

**MASTER THESIS**

AYMEN MOHAMMED KHALEEL 1403630043

Department of Electrical and Electronics Engineering Thesis Supervisor: Assist.Prof. Dr. Ertan ZENCIR

**JUNE 2017**

Aymen Mohammed Khaleel, having student number 1403630043 and enrolled in the Master Program at the Institute of Science and Technology at the University of Turkish Aeronautical Association, after meeting all of the required conditions contained in the related regulations, has successfully accomplished, in front of the jury, the presentation of the thesis prepared with the title of: "DIGITAL POWER ESTIMATION USING SUBSAMPLING ANALOG-to-DIGITAL CONVERTERS FOR COMMUNICATION RECEIVERS"

Thesis Supervisor: Asst. Prof. Dr. Ertan ZENCIR

University of Turkish Aeronautical Association

Et p

Jury Members: Asst. Prof. Dr. Hassan SHARABATY University of Turkish Aeronautical Association

Asst. Prof. Dr. Enver ÇAVUŞ

Thesis Defense Date: 06.06.2017

# UNIVERSITY OF TURKISH AERONAUTICAL ASSOCIATION TO THE INSTITUTE OF SCIENCES AND TECHNOLOGY

I hereby declare that all information in this study I presented as my Master's Thesis, called: digital power estimation using subsampling analog-to -digital converters for communication receivers, has been presented in accordance with the academic rules and ethical conduct. I also declare and certify with my honor that I have fully cited and referenced all the sources I made use of in this present study.

06.06.2017 Aymen Mohammed KHALEEL

#### ACKNOWLEDGEMENTS

I would like to thank Dr. Ertan ZENCIR for everything I have learned from him over all the past period. I am also grateful to Dr. Hassan SHARABATY for his help and support; he was always standing on my side. My father and mother(s), I am indeed grateful for your trust and the big support you gave me, I would like also to thank my wife who encouraged me until I finished this work.

JUNE, 2017

Aymen Mohammed KHALEEL

### CONTENTS

| ACKNOWLEDGEMENTS                                | V    |

|-------------------------------------------------|------|

| CONTENTS                                        | VI   |

| LIST OF FIGURES                                 | VIII |

| LIST OF TABLES                                  | X    |

| ABBREVIATIONS                                   | XI   |

| ABSTRACT                                        | XII  |

| ÖZET                                            | XIV  |

| CHAPTER 1:                                      | 1    |

| 1. INTRODUCTION                                 |      |

| 1.1. BACKGROUND                                 |      |

| 1.2. LITERATURE REVIEW                          | 5    |

| 1.3. Scope of Research                          | 6    |

| 1.4. Thesis Overview                            | 6    |

| CHAPTER 2:                                      |      |

| 2. RF POWER DETECTION                           |      |

| 2.1. Envelop Detection                          | 8    |

| 2.1.1. Diode Envelop Detector                   | 9    |

| 2.1.2. Envelop Detector Using Transistors       |      |

| 2.2. ROOT MEAN SQUARE (RMS) POWER DETECTORS     |      |

| 2.2.1. Thermal Detection Method                 |      |

| 2.2.2. Diode Detection Method                   |      |

| 2.2.3. Translinear Detection Method             |      |

| 2.2.4. Features and Drawbacks                   |      |

| 2.3. LOG DETECTOR                               |      |

| 2.3.1. Log-amp Applications                     |      |

| 2.3.2. LOG Detector Principle of Work           |      |

| 2.3.3. Log Detector Specifications              |      |

| 2.3.4. LOG-amp Detectors Limitations and Issues | 35   |

| 2.3.5. LOG-amp Detector Circuit Diagram         |      |

| 2.                                      | 4. AUTOMATIC GAIN CONTROL (AGC)                                                                                                                                                                                                                                                                                                                      | 37                                            |

|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

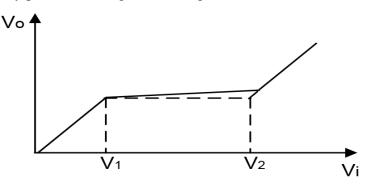

|                                         | 2.4.1. Complete System Circuit Scheme                                                                                                                                                                                                                                                                                                                | 39                                            |

| 2.                                      | 5. SUMMARY                                                                                                                                                                                                                                                                                                                                           | 41                                            |

| CHA                                     | PTER 3:                                                                                                                                                                                                                                                                                                                                              | 42                                            |

| 3.                                      | SAMPLING THEORY                                                                                                                                                                                                                                                                                                                                      | 42                                            |

| 3.                                      | I. SAMPLING AND RECONSTRUCTING OF RF ANALOG SIGNALS                                                                                                                                                                                                                                                                                                  | 42                                            |

| 3.                                      | 2. Aliasing                                                                                                                                                                                                                                                                                                                                          | 47                                            |

| 3.                                      | 3. BAND-PASS SAMPLING (SUBSAMPLING)                                                                                                                                                                                                                                                                                                                  | 51                                            |

|                                         | 3.3.1. First-order Sampling                                                                                                                                                                                                                                                                                                                          | 51                                            |

|                                         | 3.3.2. Integer Spectrum Position                                                                                                                                                                                                                                                                                                                     | 51                                            |

|                                         | 3.3.3. Random Band-pass Position                                                                                                                                                                                                                                                                                                                     | 52                                            |

|                                         | 3.3.4. Determining the Exact Sampling Frequency                                                                                                                                                                                                                                                                                                      | 54                                            |

| 3.                                      | 4. SUMMARY                                                                                                                                                                                                                                                                                                                                           | 55                                            |

|                                         |                                                                                                                                                                                                                                                                                                                                                      |                                               |

| CHA                                     | PTER 4:                                                                                                                                                                                                                                                                                                                                              | 56                                            |

| CHA<br>4.                               | PTER 4:<br>SUGGESTED MODULE FOR POWER ESTIMATION                                                                                                                                                                                                                                                                                                     |                                               |

|                                         | SUGGESTED MODULE FOR POWER ESTIMATION                                                                                                                                                                                                                                                                                                                | 56                                            |

| 4.                                      | SUGGESTED MODULE FOR POWER ESTIMATION                                                                                                                                                                                                                                                                                                                | <b> 56</b><br>56                              |

| <b>4.</b><br>4.                         | SUGGESTED MODULE FOR POWER ESTIMATION                                                                                                                                                                                                                                                                                                                | <b> 56</b><br>56<br>TED                       |

| <b>4.</b><br>4.                         | SUGGESTED MODULE FOR POWER ESTIMATION         1.       The Proposed Digital Power Estimation Algorithm         2.       Sampling Frequency Selection and Application to Modula         GNALS                                                                                                                                                         | <b> 56</b><br>56<br>TED<br>58                 |

| <b>4.</b><br>4.<br>4.<br>SI             | SUGGESTED MODULE FOR POWER ESTIMATION         I. THE PROPOSED DIGITAL POWER ESTIMATION ALGORITHM         2. SAMPLING FREQUENCY SELECTION AND APPLICATION TO MODULA         GNALS         3. TESTING MECHANISM AND CONDITIONS                                                                                                                         | 56<br>56<br>TED<br>58<br>65                   |

| 4.<br>4.<br>51<br>4.                    | <ul> <li>SUGGESTED MODULE FOR POWER ESTIMATION</li> <li>THE PROPOSED DIGITAL POWER ESTIMATION ALGORITHM</li> <li>SAMPLING FREQUENCY SELECTION AND APPLICATION TO MODULA</li> <li>GNALS</li> <li>TESTING MECHANISM AND CONDITIONS</li> <li>POWER ESTIMATION FOR AM MODULATED SIGNALS</li> </ul>                                                       | 56<br>TED<br>58<br>65<br>65                   |

| 4.<br>4.<br>51<br>4.<br>4.<br>4.        | <ul> <li>SUGGESTED MODULE FOR POWER ESTIMATION</li> <li>THE PROPOSED DIGITAL POWER ESTIMATION ALGORITHM</li> <li>SAMPLING FREQUENCY SELECTION AND APPLICATION TO MODULA</li> <li>GNALS</li> <li>TESTING MECHANISM AND CONDITIONS</li> <li>POWER ESTIMATION FOR AM MODULATED SIGNALS</li> </ul>                                                       | 56<br>TED<br>58<br>65<br>65                   |

| 4.<br>4.<br>51<br>4.<br>4.<br>4.        | <ul> <li>SUGGESTED MODULE FOR POWER ESTIMATION</li> <li>THE PROPOSED DIGITAL POWER ESTIMATION ALGORITHM</li> <li>SAMPLING FREQUENCY SELECTION AND APPLICATION TO MODULA</li> <li>GNALS</li> <li>TESTING MECHANISM AND CONDITIONS</li> <li>POWER ESTIMATION FOR AM MODULATED SIGNALS</li> <li>POWER ESTIMATION FOR M-QAM MODULATED SIGNALS</li> </ul> | 56<br>TED<br>58<br>65<br>65<br>67<br>72       |

| 4.<br>4.<br>51<br>4.<br>4.<br>4.<br>CH4 | <ul> <li>SUGGESTED MODULE FOR POWER ESTIMATION</li></ul>                                                                                                                                                                                                                                                                                             | 56<br>TED<br>58<br>65<br>65<br>67<br>72<br>72 |

| 4.<br>4.<br>51<br>4.<br>4.<br>4.<br>5.  | <ul> <li>SUGGESTED MODULE FOR POWER ESTIMATION</li> <li>The Proposed Digital Power Estimation Algorithm</li></ul>                                                                                                                                                                                                                                    | 56<br>TED<br>58<br>65<br>65<br>67<br>72<br>72 |

# LIST OF FIGURES

| FIGURE 1: ANALOG-ONLY AUTOMATIC GAIN CONTROL LOOP INCLUDING AN ANALO            | ЭG  |

|---------------------------------------------------------------------------------|-----|

| POWER DETECTOR IN A GENERIC RECEIVER CHAIN                                      | . 2 |

| FIGURE 2: DIGITAL AUTOMATIC GAIN CONTROL LOOP IN A GENERIC RECEIVER             |     |

| CHAIN                                                                           | . 3 |

| FIGURE 3: EQUIVALENT CIRCUIT OF SAMPLER                                         | . 4 |

| FIGURE 4: ENVELOP OF AN OSCILLATING SIGNAL.                                     | . 9 |

| FIGURE 5: BASIC DIODE DETECTOR CIRCUIT                                          | 10  |

| FIGURE 6: DUAL DIODE POWER DETECTOR.                                            | 10  |

| FIGURE 7: SQUARE-LAW, LINEAR AND COMPRESSION OPERATING REGIONS OF THE           |     |

| DIODE DETECTOR                                                                  | 11  |

| FIGURE 8: USING A WIDE BANDWIDTH DETECTOR TO TRACK THE SIGNAL ENVELOP           |     |

| CORRECTLY                                                                       |     |

| FIGURE 9: SCHOTTKY DIODE DETECTOR CIRCUIT                                       | 13  |

| FIGURE 10: SCHOTTKY DIODE, VOLTAGE DOUBLER DETECTOR CIRCUIT                     | 13  |

| FIGURE 11: SCHOTTKY DETECTOR DIODES                                             | 15  |

| FIGURE 12: DYNAMIC RANGE IMPROVEMENT WITH BIAS,                                 | 17  |

| FIGURE 13: CMOS ENVELOP DETECTOR SCHEME                                         | 18  |

| FIGURE 14: THERMISTOR SENSOR DIAGRAM.                                           | 22  |

| FIGURE 15: BOLOMETER DIAGRAM                                                    | 22  |

| Figure 16: Basic translinear loop that used in $RMS$ detector                   | 24  |

| FIGURE 17: CAPRIO QUAD INPUT INTERFACE CIRCUIT                                  | 26  |

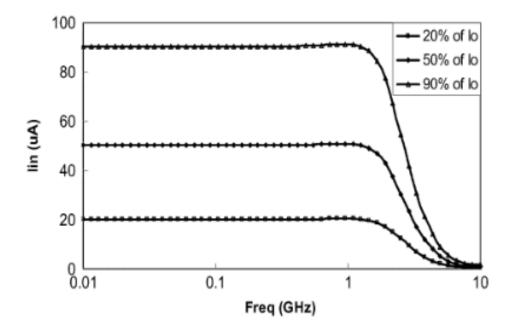

| Figure 18: Frequency response at the input of the translinear loop $\ldots$ .   | 26  |

| FIGURE 19: TRANSLINEAR LOOP WITH BASE-CURRENT COMPENSATION SHOWN IN             |     |

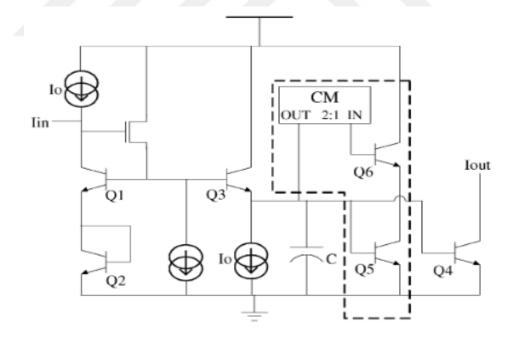

| THE DASHED REGION (CM: CURRENT MIRROR)                                          | 27  |

| FIGURE 20: OUTPUT INTERFACE CIRCUIT.                                            | 28  |

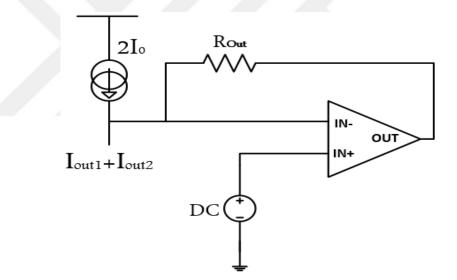

| FIGURE 21: COMPLETE CIRCUIT DIAGRAM OF RMS DETECTOR BY USING THE                |     |

| TRANSLINEAR PRINCIPLE                                                           | 29  |

| FIGURE 22: LOGARITHM FUNCTION OF THE LOG DETECTOR, ASSUMING $(X, Y)$ TO BE viii |     |

|            | THE INPUT AND OUTPUT SIGNALS RESPECTIVELY.                       | . 31 |

|------------|------------------------------------------------------------------|------|

| FIGURE 23  | : (A) CURRENT VS. VOLTAGE RELATIONSHIP OF A DIODE, (B) THE USE O | θF   |

|            | THIS RELATIONSHIP WITHIN THE OP-AMP FEEDBACK                     | . 33 |

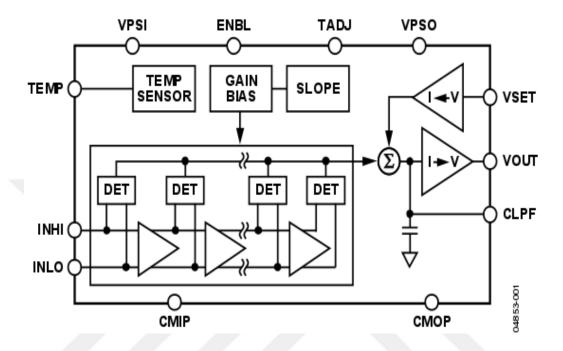

| FIGURE 24  | FUNCTIONAL BLOCK DIAGRAM OF AD8318 LOGARITHMIC                   |      |

|            | DETECTOR/CONTROLLER                                              | . 36 |

| FIGURE 25: | TYPICAL LOGARITHMIC RESPONSE AND ERROR VS. INPUT AMPLITUD        | Έ    |

|            | AT DIFFERENT TEMPERATURES                                        | . 37 |

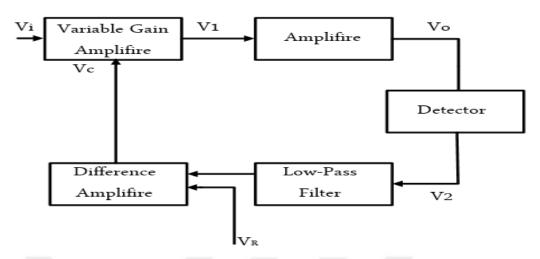

| FIGURE 26  | AGC BLOCK DIAGRAM.                                               | . 38 |

| FIGURE 27: | AGC (IDEAL) TRANSFER FUNCTION.                                   | . 38 |

| FIGURE 28: | THE COMPLETE CIRCUIT OF AN AGC SYSTEM                            | . 40 |

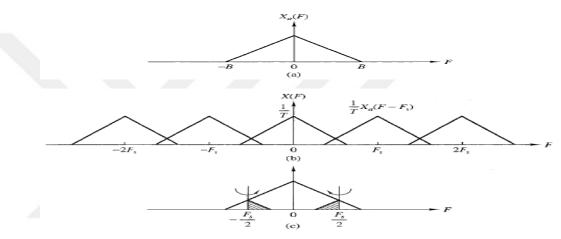

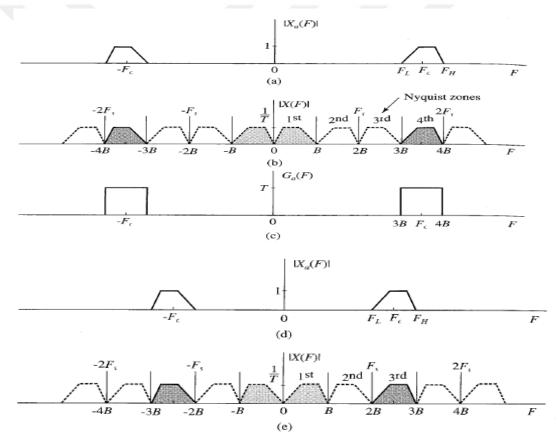

| FIGURE 29: | THE SAMPLING PROCESS FOR A BANDLIMITED SIGNAL AND ALIASING       | OF   |

|            | THE SPECTRUM REPLICAS.                                           | . 46 |

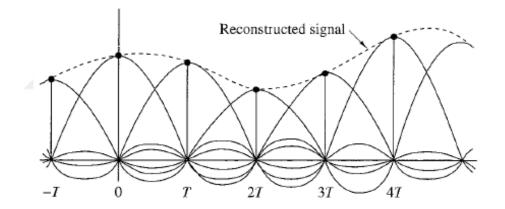

| FIGURE 30: | RECONSTRUCTION PROCESS TO RECOVER THE ORIGINAL ANALOG            |      |

|            | SIGNAL FROM ITS SAMPLES                                          | . 47 |

| FIGURE 31  | : Aliasing of Fs $< 2B$ .                                        | . 48 |

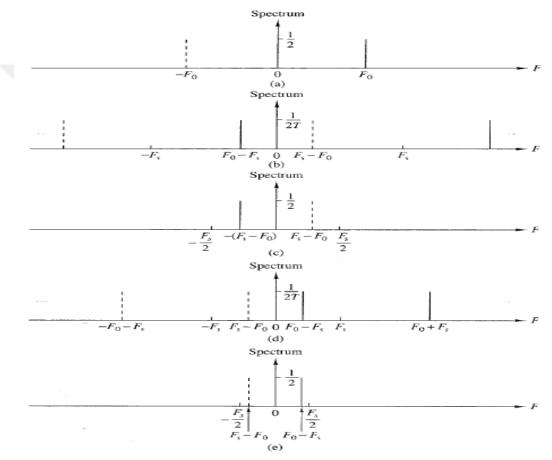

| FIGURE 32: | ALIASING IN A SINUSOIDAL SIGNAL                                  | . 49 |

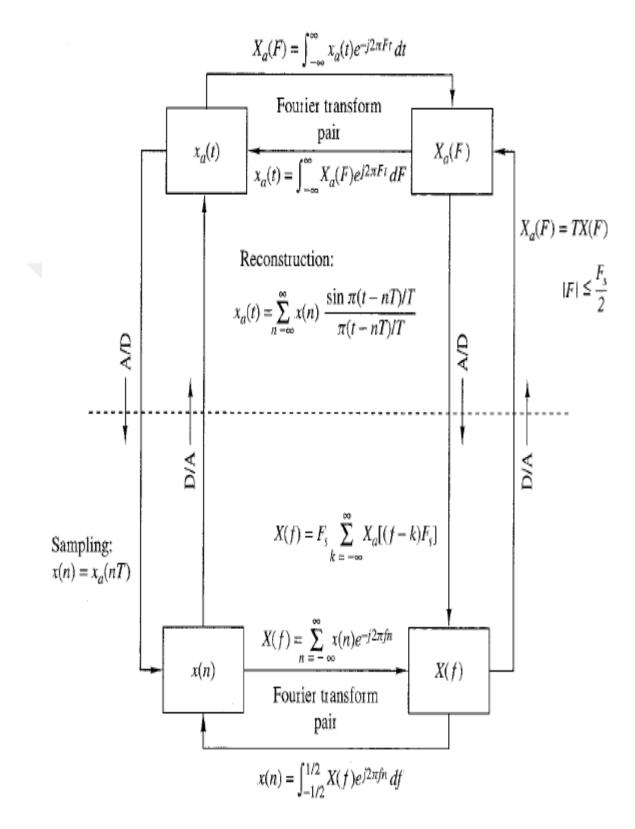

| FIGURE 33  | : SAMPLING AND RECONSTRUCTING FORMULAS FOR A BANDLIMITED         |      |

|            | SIGNALS                                                          | . 50 |

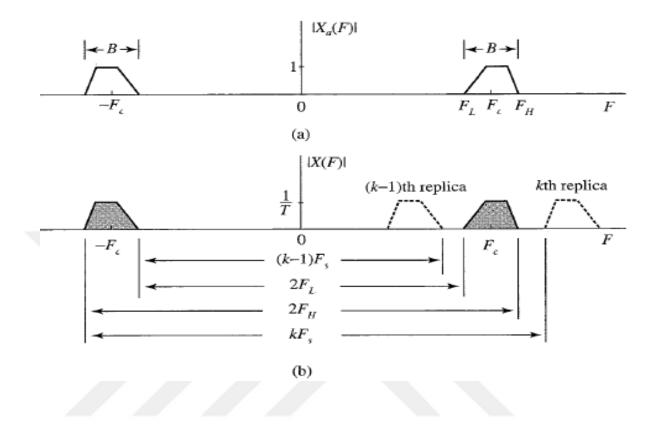

| FIGURE 34  | THE BAND-PASS POSITION CONFIGURATION: EVEN AND ODD CASES         | . 52 |

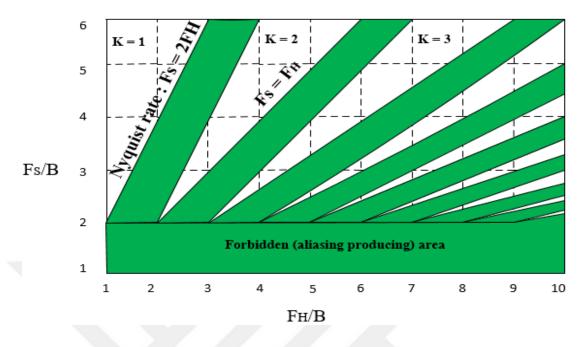

| FIGURE 35  | ARBITRARY POSITION BAND-PASS SIGNAL SAMPLING.                    | . 54 |

| FIGURE 36  | : ALLOWED (WHITE) AND FORBIDDEN (GREEN) REGIONS OF THE           |      |

|            | SAMPLING FREQUENCY                                               | . 55 |

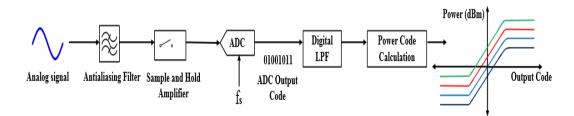

| FIGURE 37  | DIGITAL POWER ESTIMATION USING DIRECT SAMPLING                   | . 57 |

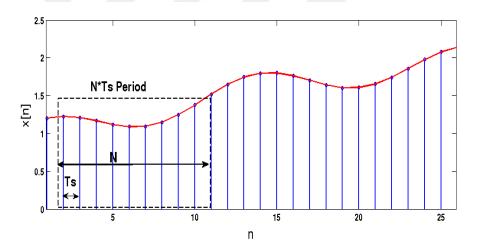

| FIGURE 38  | SAMPLING WINDOWS FOR THE INPUT SIGNAL                            | . 58 |

| FIGURE 39  | EXAMPLE AM MODULATED SIGNAL.                                     | . 59 |

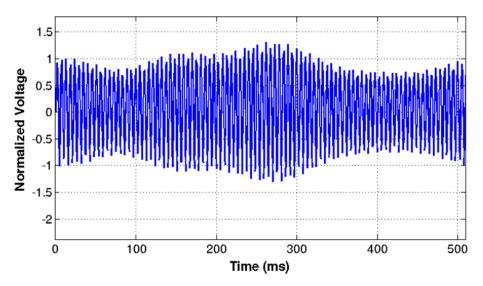

| FIGURE 40  | POWER ESTIMATION ERROR VS SUBSAMPLING FACTOR K ACCORDING         | ТО   |

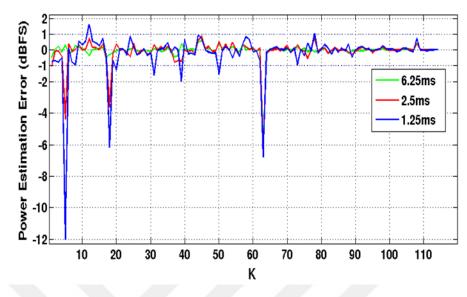

|            | Eq.3.3.3.11.                                                     | . 63 |

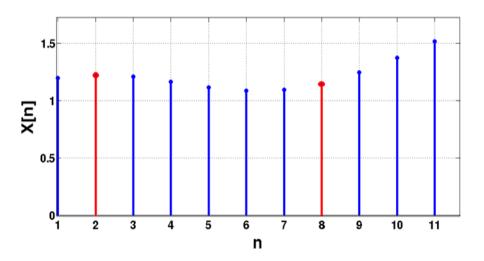

| FIGURE 41: | : EXAMPLE SAMPLE VALUES OF AN ANALOGUE SIGNAL                    | . 64 |

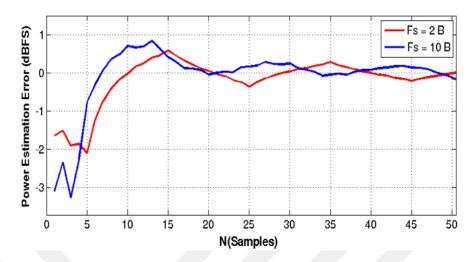

| FIGURE 42  | : ERROR CURVES OF TWO DIFFERENT SAMPLING FREQUENCIES FOR         |      |

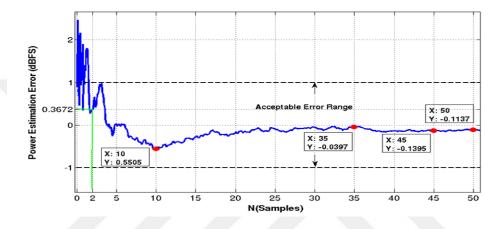

|            | POWER ESTIMATION OF THE AM MODULATED SIGNAL                      | . 65 |

| FIGURE 43  | THEORETICAL AND ESTIMATED POWER VALUES VS. NUMBER OF             |      |

| ix         |                                                                  |      |

|            |                                                                  |      |

| SAMPLES FOR THE $\operatorname{AM}$ modulated signal            | 66 |

|-----------------------------------------------------------------|----|

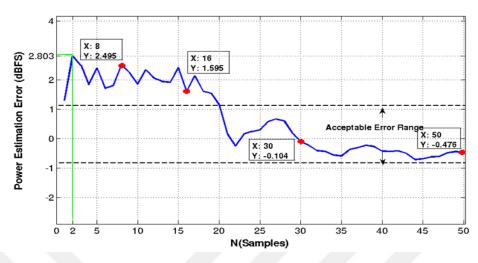

| FIGURE 44: POWER ESTIMATION ERROR FOR THE AM SIGNAL             | 66 |

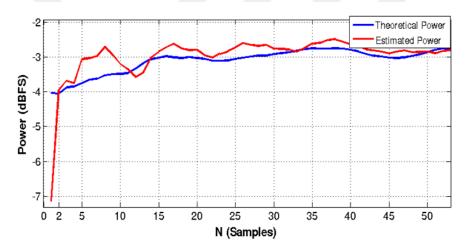

| FIGURE 45: M-QAM SIGNAL BANDWIDTH                               | 67 |

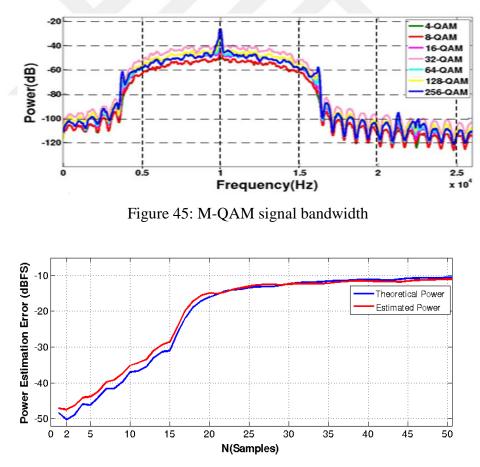

| FIGURE 46: THEORETICAL AND ESTIMATED POWER VALUES VS. NUMBER OF |    |

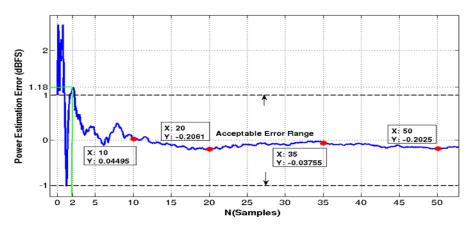

| SAMPLES FOR THE 4-QAM MODULATED SIGNAL                          | 67 |

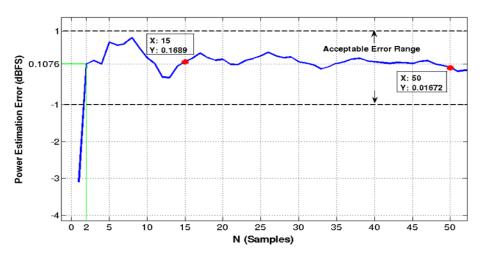

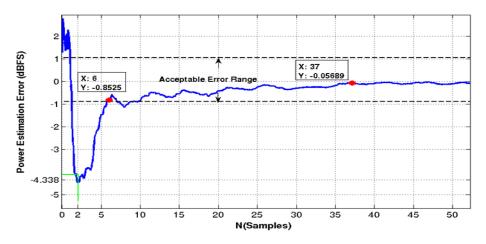

| FIGURE 47: POWER ESTIMATION ERROR FOR THE 4-QAM SIGNAL          | 68 |

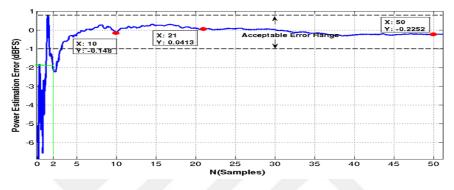

| FIGURE 48: POWER ESTIMATION ERROR FOR 8-QAM SIGNAL.             | 68 |

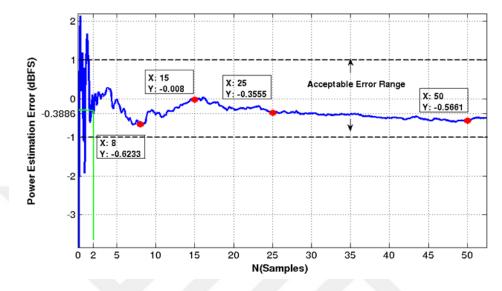

| FIGURE 49: POWER ESTIMATION ERROR FOR THE 16-QAM SIGNAL         | 69 |

| FIGURE 50: POWER ESTIMATION ERROR FOR THE 32-QAM SIGNAL         | 69 |

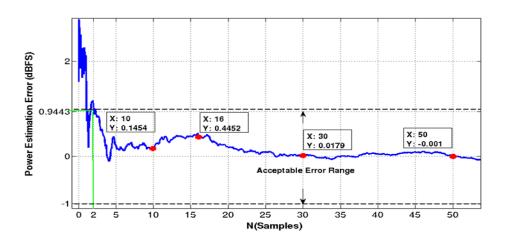

| FIGURE 51: POWER ESTIMATION ERROR FOR THE 64-QAM SIGNAL         | 70 |

| FIGURE 52: POWER ESTIMATION ERROR FOR THE 128-QAM SIGNAL        | 70 |

| FIGURE 53: POWER ESTIMATION ERROR FOR THE 256-QAM SIGNAL        | 71 |

# LIST OF TABLES

| Table .1. | Comparison between different RMS power detector | 30 |

|-----------|-------------------------------------------------|----|

|-----------|-------------------------------------------------|----|

# ABBREVIATIONS

| ADC  | : Analog-to-Digital Convertor [xii].               |

|------|----------------------------------------------------|

| LNA  | : Low Noise Amplifire [xii].                       |

| AGC  | : Automatic Gain Control [xii].                    |

| PVT  | : Process Voltage and Temperature variation [xii]. |

| SNDR | : Signal to Noise and Distortion Ratio [56].       |

| ENOB | : Effective Number of Bits [2].                    |

| RF   | : Bandpass signal (any modulated signal) [xii].    |

| VSWR | : Voltage Standing Wave Ratio [8].                 |

| QAM  | : Quadrature Amplitude Modulation [xii].           |

| QPSK | : Quadrature Phase Shift Keying [xii].             |

| LTE  | : Long Term Evolution [5].                         |

| GSM  | : Global System for Mobile communications [8].     |

| VGA  | : Variable Gain Amplifire [37].                    |

| DSP  | : Digital Signal Processing [73].                  |

|      |                                                    |

xi

#### ABSTRACT

# DIGITAL POWER ESTIMATION USING SUBSAMPLING ANALOG-to-DIGITALCONVERTERS FOR COMMUNICATION RECEIVERS

KHALEEL, Aymen Mohammed

Master Thesis, Department of Electrical and Electronics Engineering

Thesis Supervisor: Assist. Prof. Dr. Ertan ZENCIR June–2017, 79 pages

Abstract— The estimation of received signal power in wireline and wireless communication receiver chains is an important task since the total gain of the receiver chain is decided based on the power estimates. The setting of the receiver gain affects the noise figure of the receiver and the amount of distortion at the output of the receiver (Analog-to-Digital converter input). Adjusting the gain of several RF (Radio Frequency) and IF (Intermediate Frequency) blocks to set the overall receiver gain is carried out with Automatic Gain Control (AGC) loops, which are usually implemented as analog blocks employing analog power detection and estimation techniques. On-chip analog power estimation circuits used in RF frequencies are based on techniques such as envelope detection, and logarithmic amplification. These techniques suffer from accuracy issues such as process, voltage, temperature (PVT) spreads (primarily due to transconductance variation of core transistors), which prevents the realization of power-optimum designs. This work proposes an alternative method of measuring the power of an RF or IF signal with a subsampling analog-to-digital converter (ADC). This method presented in this thesis, which is called subsampling power estimation, being mainly digital, has a very tightly controlled power estimation characteristic unlike analog-only methods. The subsampling approach has a very low PVT spread due mainly to the sample and hold amplifier at the input stage of the ADC. Power estimation errors due to temperature variations may be compensated through self-calibration by generating a dynamically changing look-up table that would contain the power estimate vs. the digital code at the ADC output. In order to verify the validity of the xii

subsampling method, an MATLAB code was developed to find the power of a voice signal with amplitude modulation (AM) and quadrature amplitude modulation (QAM). The error between the Nyquist sampling and subsampling approaches is defined as the main parameter to verify the validity of the subsampling method. In simulations, it was found that the error was within approximately +0.1 dB for the power estimation of AM modulated signal, and - 0.148 dB for the QAM modulated signal. Results confirm that the estimation of power of RF signals could be achieved at much lower sampling rates rather than Nyquist rate. This would reduce the complexity of power estimation circuits which results in lower design cost.

**Key words:** Digital power estimation, subsampling ADC, communication receivers, RSSI.

### ÖZET

Kablolu ve kablosuz haberleşme alıcı zincirlerinde sinyal gücünün hesaplanması, alıcının toplam kazancının güç tahminlerine dayalı olarak karar verilmesinden dolayı önemli bir fonksiyondur. Alıcı kazancının ayarlanması, alıcının gürültü faktörünü ve alıcının çıkışındaki bozulma miktarını etkiler (Analog-Dijital çevirici girisi). Alıcının tamamının kazancını belirlemek için birçok RF (Radio Frequency) ve IF (Intermediate Frequency) blokların kazancının ayarlanması otomatik kazanç kontrol döngüleri sayesinde gerçekleştirilir. Kazanç control döngüleri analog güç bulma ve tahmin etme teknikleri kullanan analog bloklar kullanılarak icra edilir. RF frekanslarında kullanılan yonga-üstü analog güç hesaplama devreleri zarf bulma ve logaritmik yükseltme gibi teknikler temel alınarak tasarlanmaktadır. Bu teknikler voltaj, sıcaklık (PVT) serpilmelerine (özellikle ana transistor proses, transkondaktans değişimlerinden kaynaklı hassasiyet problemlerine) maruz kalmaktadır. Bu durum güç-optimize tasarımların gerçekleşmesine engel teşkil etmektedir. Bu tezde sunulan alt-örnekleme güç tahmini metodu sadece-analog usüllerin aksine çok sıkı control edilebilen güç tahmini karakteristiklerine sahiptir. Alt-örnekleme yaklaşımı çok düşük PVT serpilmesine sahiptir. Bu serpilmenin kaynağı da temelde analog bir blok olan ve Analog-Dijital Çeviricinin girişinde yer alan örnekle-ve-tut yükseltecidir. Sıcaklık değişimlerinden kaynaklı güç hesaplama hataları kendi-kendine kalibrasyon kullanılmasıyla telafi edilebilir. Bu kalibrasyon Analog-Dijital Çevirici çıkışındaki "güç tahminine" karşılık "dijital kod" tablosunu dinamik olarak değiştiren bir "look-up" tablosu sayesinde sağlanabilir. Altörnekleme metodunun geçerliliğini doğrulamak maksadıyla, genlik modulasyonlu (AM) ve kuadratik genlik modülasyonlu (QAM) bir ses sinyalinin gücünün hesaplanması için bir MATLAB kodu geliştirildi. Nyquist örnekleme ve altörnekleme güç tahmini değerleri arasındaki hata alt-örnekleme metodunun geçerliliğini ölçmek için temel parametre olarak tanımlandı. Simülasyonlarda genlik modülasyonlu sinyalin güç tahmini için yaklaşık +0.1 dB'lik ve kuadratik genlik modülasyonlu sinyal için ise -0.148 dB'lik hatalar elde edildi. Elde edilen

sonuçlar, RF taşıyıcı frekanslarda modulasyona tabi tutulmuş sinyallerin güç tahminlerinin Nyquist örnekleme hızlarından çok daha aşağı hızlarda başarılabileceğini doğrulamaktadır. Bu doğrulama sayesinde, güç tahmini devrelerinin karmaşıklıklarının azaltılabileceği ve bunun da daha düşük maliyetli tasarımlara kapı aralayacağı söylenebilir.

#### CHAPTER 1:

### **1. INTRODUCTION**

#### 1.1. Background

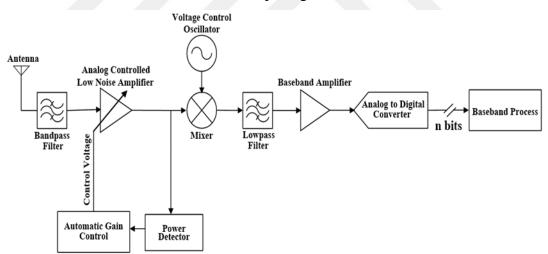

Maintaining a constant level of signal power at the output of an analog front end (the input of the ADC) regardless of the input signal level is an important design requirement which mandates strict control of each block's gain. Hence, several automatic gain control (AGC) loops are required to perform the task of adjusting the gain of their attached loop. AGCs are feedback amplifiers with closed-loop low-pass gain characteristics; they are responsible for providing a relatively constant output amplitude so that a circuit controlled by the loop can function with acceptably low distortion [1]. The power detector block is an important component of the AGC loop, which usually taps the output of the corresponding amplifier whose output power needs to be adjusted. Power detector circuits used in classical analog integrated designs are based on envelope detection where a differential amplifier is used such that the virtual ground is the full-wave rectified version of the input signal [2]. The spread in the gain of the differential amplifier and the following RC filter over process, voltage, and temperature significantly affects the accuracy of the voltage count, and thus the power estimates, which then affects the precise gain setting. Therefore, maintaining a good signal-to-noise ratio (SNR) with minimal distortion at the output of the related gain block is achieved with poor accuracy. This affects the performance of the receiver chain significantly. The negative gain errors for low input signal levels might lower the output SNR of the gain block, which in turn reduces the SNR of the entire receiver chain in terms of linearity. The positive gain errors for high input signal levels may drive the amplifier into a nonlinear region, thereby resulting in distortion. Moreover, setting the gain to levels higher than the required optimum level may significantly increase the power dissipation of the block(s). Another power estimation popularly used by analog designers is logarithmic amplification, which also suffers from the aforementioned problems of PVT spread. Logarithmic amplifiers need to employ multiple linear amplifiers to achieve the required dynamic range, which makes them a power hungry choice for power detection [3]. Another factor that makes logarithmic amplifiers less attractive is the high temperature variation. CMOS logarithmic amplifiers are so far unable to provide a stable performance of *RF* power detection over a wide dynamic range without using sophisticated temperature compensation techniques [4], [5]. The generic analog power detection technique is shown in Fig. 1. This article suggests an alternative digital method of measuring the power of an *RF* or *IF* signal. The method is mainly based on the idea that less analog processing would mean less spread over PVT. For this purpose, the signals are directly sampled by using a low power low energy over bit (*ENOB*) simple *ADC* whose clock frequency needs to be at least double the bandwidth of its input signal.

Figure 1: Analog-only automatic gain control loop including an analog power detector in a generic receiver chain.

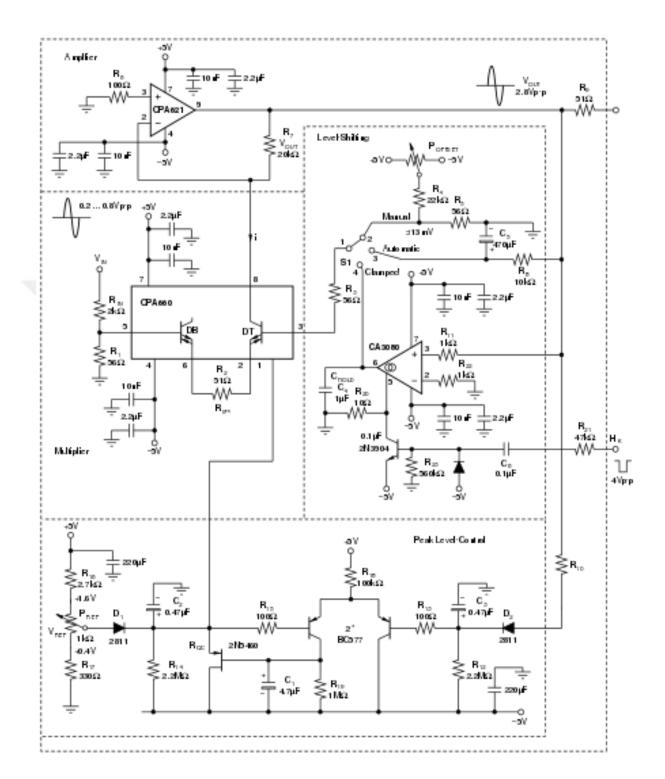

According to Nyquist sampling criteria, the sampling rate of an analog-to-digital convertor (ADC) should be at least twice the highest frequency of its input signal. This necessitates very high sampling rates, especially for RF frequencies, which makes the ADC design more challenging with high power consumption, since the power dissipation is directly proportional to the sampling frequency [6]. In addition, ADC

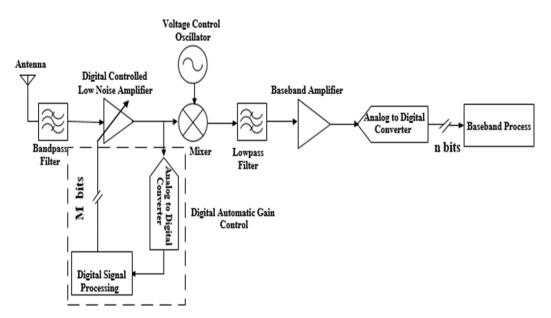

clock signal jitter requirements will also be more challenging when the sampling frequency increases [7]. The Nyquist-Shannon sampling Theorem, which is the modified version of the Nyquist Theorem, states that sampling the signal at a rate double its bandwidth will be sufficient to recover the original signal from the sampled version instead of considering the doubling of the highest frequency component [8]. For example, a signal with bandwidth B with a carrier frequency fc will require a minimum sampling frequency of 2B instead of 2( $f_c + B$ ) because the narrow-band signals do not change significantly during the time taken by a carrier to make one cycle. In this work, sampling of the analog signal is performed at the sub-Nyquist (or subsampling) rate directly at *RF* or *IF* frequencies. The sampled signal data is then squared and low-pass filtered (averaging) to estimate the power. The digital code representing the power estimate at the output of each block can then be used to adjust the gain of each block digitally through automatic gain control (*AGC*) loops, as shown in Fig. 2.

Figure 2: Digital automatic gain control loop in a generic receiver chain.

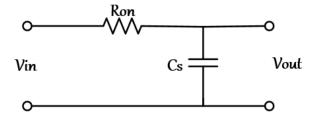

The subsampling process creates replicas of the spectrum. These replicas are spread on the frequency axis from the base band to the *RF* frequencies [9]. This process also generates extra thermal noise produced by the sampler circuit; this noise will affect the low power side of the large range for the power estimate. By looking at the sampler circuit depicted in Fig. 3, and in order to have negligible attenuation due to the thermal noise, , this circuit must have a bandwidth equal to the input frequency,  $f_{in}$  at least. Resistor  $R_{on}$  will have an integrated noise power of kT/C. The noise power added by the sampling circuit will be multiplied by a factor of 2m if subsampling is performed by a factor of *m*. Subsampling can also make the effect of noise in the sampling clock to deteriorate. It can be proven that the clock phase noise power is also amplified by  $m^2$  [10], [11], [12]. Increasing the sampling frequency to decrease the thermal noise is not practical due to the previous introduction; otherwise, the subsampling technique will be meaningless. Instead of increasing the sampling frequency, two consecutive subsampling stages can be used to reduce subsampling thermal noise, where a relatively high sampling frequency can be set at the first subsampling stage. This leads to a lower contribution of the first sampler circuit to the folded thermal noise [13], [14]. Furthermore, the MT/C thermal noise limit can be reduced with other techniques (which will not be discussed here) [15].

Figure 3: Equivalent circuit of sampler.

#### **1.2.** Literature Review

Diode detectors (used in envelop detection) have a better operation bandwidth and less plan area in implementation, which results in the cost advantage if it is compared to the FET counterparts. The Schottky diode is widely used for frequency mixing and RF power detection [16], [17], and the GaAs Schottky diode is used for terahertz (THz) spectroscopy in order to increase the operating bandwidth [18]. However, diode detectors have a significant uncertainty in determining accurately the dynamic diode turn-on characteristics when it deals with low-level signals in a precision operation. In high frequency cases, power dissipation increases in order achieve the required signal level by providing sufficient high-frequency gain. Moreover, dynamic range improvement will be a trade-off with sensitivity and power dissipation according to the method that is used for the improvement, which are either increasing the diode's video resistance or increasing the bias current [19]. Temperature is another effective parameter which needs compensation techniques such as enhancing the matching input network and using a supplemental DC bias current. Using each one of these solutions is related to the presence of low or high temperature conditions [20]. Unlike diodes detectors, FET transistors used for envelop detection increase the accuracy when used in precision applications at very high frequency due to the closed-form expressions that describe the transfer characteristics of the FET circuit [21]. These envelop detectors can function well with low dynamic range modulation schemes, while using it with high peak-toaverage modulation schemes will lead to inaccurate measurements. In modern communication systems such as 4G, 5G and LTE, signals may have a high peakto-RMS ratio (crest factor) that reaches 10 to 15 dB. For such operating conditions, RMS power detectors offer accurate measurements within  $\pm 0.2$  dB, with a high linearity of ±1 dB over a 40-decibel range and GHz operating area. RMS power detectors can be implemented based on different power detection methods, including thermal detection, diode detection, and translinear detection methods [22], [23], [24], [25]. The log detector provides a very high dynamic range compared with the other power detectors, typically (60 dB-120 dB) and this is the

main feature for this detector over the others. It is used widely in radar application systems for its high dynamic range and the constant false alarm rate properties that it has [26], [27]. Similar to the other power detectors, temperature is one of the main limitations that need to be compensated for in a log detector [28]. Moreover, these detectors are power-hungry detectors since they are implemented with a progressive compression technique over a cascaded amplifier chain [29]. However, all the previous power detectors are suffering from the PVT issue since they are based on analog topologies. This fact is the core reason to suggest the digital power estimation method in this study, where less analog processing would mean less spread over PVT.

#### **1.3.** Scope of Research

In this study, based on the subsampling approach, a digital power estimation method is introduced. This method is proposed to be the alternative for the analog power detection techniques. Therefore, we defined first the main concept for this method, which is the subsampling technique. This technique provides us with the discrete-time version (samples) of the given continuous-time signal, then, by using these samples, the signal power is being calculated and used to adjust the gain of a VGA. For the design purposes, a practical model for this method have been introduce, which is consist of multiple units that include filters, ADC with relatively low clock rate and code calculation block. In order to verify the validity of the proposed subsampling method, an MATLAB code was developed to find the power of different amplitude-modulated signals. The error between the Nyquist sampling and subsampling method. Finally, we have discussed the optimal sampling frequency selection method and illustrated the minimum sampling frequency that could be considered besides the effects of increasing it above the minimum value.

### 1.4. Thesis Overview

Chapter 2 contains the theory part that presents the different power detection techniques in detail, including the features and drawbacks for each technique. At

the end of the chapter, there will be a quick review of AGC circuit configuration and the principle of the work. Chapter 3 is a review of sampling theory. Additionally, the formulas and relationships for time and the frequency domain of sampling and reconstructing the signal are derived. The subsampling (bandpass sampling) concept is introduced in detail. Chapter 4 illustrates the proposed method for power estimation, including circuit configuration, work principles, mathematical formulas for computing the power value of a given signal, and finally the simulation results using the MATLAB software. In Chapter5, the conclusion and a brief discussion of future work are presented.

#### **CHAPTER 2:**

### 2. **RF POWER DETECTION**

A power detector is an electronic circuit that converts input RF power into a new form of DC voltage which is directly proportional to the input power via the RMS or logarithmic relationship. Moreover, a power detector can represent the oscillating signal in an envelope form by detecting the peak values of the input signal. These detectors are mainly used to measure and control the power in wireless systems for regularities, proof-of-design, safety, power amplifier linearization, and many other applications. This occurs when the detector is included within the AGC circuit. RSSI in mobile systems, for example, is used to control the incoming power and keep it at a desired level for the ADC and demodulator circuits. VSWR is another fundamental measurement that can be achieved with the use of a power detector circuit for high-power RF amplifiers to avoid the signal reflections from an antenna. These reflections are caused by the impedance mismatch, which causes severe damage to the amplifier. In the receiver chain, power detectors are used along with the LNA in order to guarantee that the signal level is not very high to be cut due to the op-amp saturation, and not very low to be within the noise level.

#### 2.1. Envelop Detection

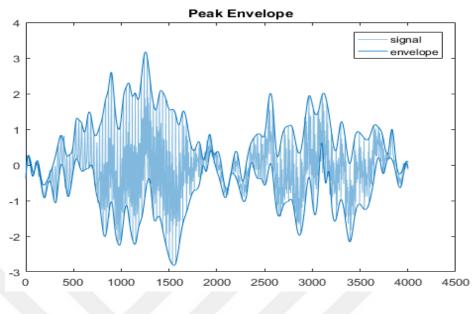

The envelop of a signal is the smooth curve that connects all the positive peaks of an oscillating signal. From the signal processing perspective, it is the low-frequency or DC-version of the oscillating signal (see Figure 4).

The envelop detector is an electronic circuit that rectifies an input oscillating signal and produces its envelop by detecting only the positive peaks of the oscillating signal. This can be done by using either a diode or a transistor. These types of detectors perform well when a constant envelop or low crest factor modulated signals are considered, such as GSM. However, it cannot produce the same good performance for a high peak-to- RMS ratio for modulated signals found in WCMDA and LTE.

Figure 4: Envelop of an oscillating signal.

#### 2.1.1. Diode Envelop Detector

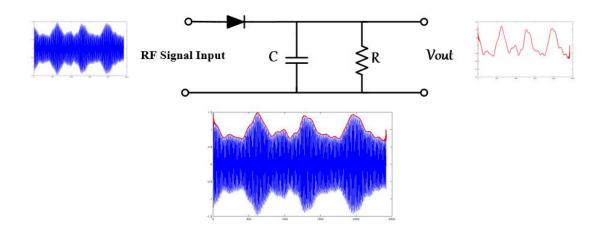

In Figure 5, the RF input signal is detected by the diode to be a DC voltage signal. This is done according to the diode operating concept, where the diode acts as a nonlinear element that passes the current in one direction and prohibits it in the reverse direction. Hence, the diode will connect all the positive peaks of the oscillating signal to form the envelop of the input signal, and prohibit the flow of negative peaks. This process called signal *rectifying*. A capacitor will smooth the rectified signal and filter it from the RF combined signals. The capacitance value will be according to the input signal bandwidth such that the signal will not filtered out due to the low cut off frequency. The direction of the diode will matter only when the rectified signal feeds back to the AGC circuit; otherwise, the positive or negative envelop signal could both be used, for example, for audio detection.

Figure 5: Basic diode detector circuit.

In order to detect the positive and negative carrier cycles, two diodes are often used. At the other hand, this makes the circuit relatively insensitive to even harmonic distortion (see Figure 6). The DC voltage signal at the output is proportional to the input signal power at low levels and it is proportional to the peak RF voltage when a high-level signal is present. Mega-ohm load resistor are used when high sensitivity is required.

Figure 6: Dual diode power detector.

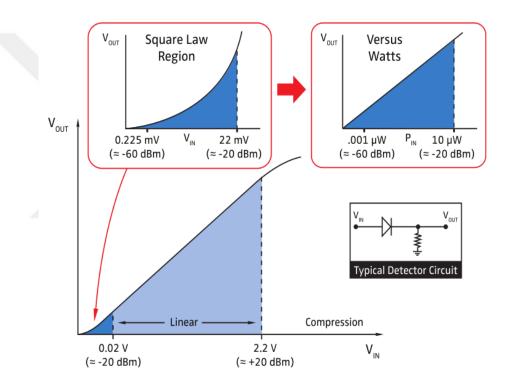

When the RF input is insufficient to make diodes the pass saturation current in the forward direction (less than -20 dBm, 30mV peak carrier voltage), diodes act as nonlinear resistors (see Figure 7) [30]. In this case the output signal is proportional to the squared RF input signal voltage and this is called the "squarelaw" region of the diode detector. If the input signal peak power is within this region, then the RF average power may be measured by considering the average of the output DC voltage, and this is also true for a modulated signal.

For a signal level greater than 0 dB (300-millivolt peak input voltage), the detector circuit acts as a peak detector, and the diodes will be able to pass the saturation current in the forward direction for the positive cycles of the input oscillating signal. The output DC voltage is equal to the peak RF input voltage minus the voltage drops at each diode (see Figure 7).

Figure 7: Square-law, linear and compression operating regions of the diode detector [30].

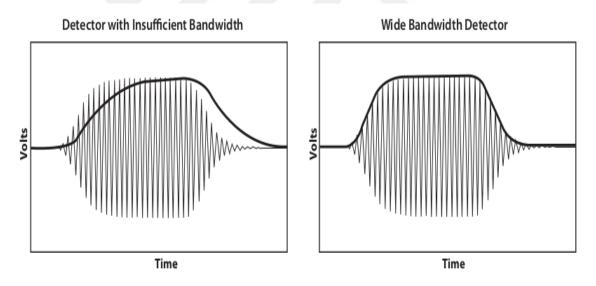

Diode detectors have a large dynamic range; however, since there are two regions of operation, the detector response will not be linear across the entire dynamic range. Moreover, diode detectors are very sensitive, and with the use of digital techniques, they can be linearized easily. However, when a modulated signal has a peak with an amplitude exceeding the limits of the square region, diode detectors will be challenged wherever these peaks enter the peak detection region. In this case, the detector output voltage tracks the peaks of the signal, and while the capacitor is discharging, the output voltage will not be able to track the peaks within this time. Therefore, the average power of the RF signal cannot be measured within the peak region of the diode detector.

To solve this problem, the resistor value may be chosen such that the output voltage signal decay time decreases and the output voltage signal will be sufficiently fast to follow the envelop fluctuations of the input modulated signal. This may be done through the decrease of the load resistance and capacitance ( $R_L$ ,  $C_L$ ) after the diodes in Figure 6. It is possible to linearize the output signal in real time and perform filtering when the detector is sufficiently fast to track the signal envelop without any lagging (see Figure 8). For such a fast diode detector, the instantaneous and average power of a given modulated signal may be measured so long as the power is within the dynamic range of the detector [30].

Figure 8: Using a wide bandwidth detector to track the signal envelop correctly [30].

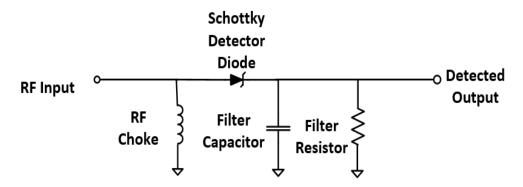

### 2.1.1.1. Schottky Diode Detector Circuit

In Figure 9, a half-wave rectifier represents the fundamental Schottky detector circuit. The incident RF oscillating signal alternatively causes the Schottky diode

to be forward and reverse biased. In the case of forward bias, the filter capacitor charges until the voltage across it equals the input voltage value.

Figure 9: Schottky Diode Detector Circuit.

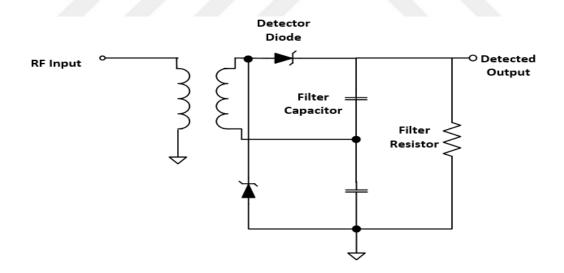

There are multiple detector circuit configurations, most of which contain more than one Schottky diode. This improves the detected output voltage. One of the basic Schottky detector circuit configurations is the voltage doubler detector circuit (see Figure 10).

Figure 10: Schottky Diode, Voltage Doubler Detector Circuit.

The Schottky diode junction operates with a majority of carriers without minority ones, unlike the p-n diode. This advantage slows the recovery time of the Schottky diode when the applied signal changes its polarities causing forward and reverse biasing of the Schottky diode. Moreover, due to the change of input signal polarity, the impedance changes virtually instantaneously enabling the Schottky diode to have a wide frequency operating area. The significantly low forward voltage of the Schottky diode with respect to the p-n junction diode adds another advantage to these diodes such that they are more sensitive than the p-n junction diodes. Figure 11 shows a comparison of sensitivity and operating bandwidth for different Skyworks' Schottky detector diodes [31].

| Minimum<br>Detectable<br>Signal (dBm) | Barrier Height | Input Signal<br>Frequency Range | Maximum<br>Capacitance<br>(pF) | Configuration                                                                                                        | Base Part<br>Number |

|---------------------------------------|----------------|---------------------------------|--------------------------------|----------------------------------------------------------------------------------------------------------------------|---------------------|

| -52                                   | ZBD            | Up to 30 GHz                    | 0.25                           | Chip, ceramic packaged                                                                                               | CDC7630             |

| -56                                   | ZBD            | Ku band                         | 0.15                           | Chip, ceramic packaged                                                                                               | CDC7631             |

| -60                                   | ZBD            | Up to 10 GHz                    | 0.3                            | Single junction, reverse series pair, series pair, and<br>unconnected pair, plastic packages                         | SMS7630             |

| -60                                   | ZBD            | Up to 100 GHz                   | 0.3                            | Single junction flip chip                                                                                            | SMS7630             |

| -50                                   | Low            | Ku band                         | 0.15                           | Chip, ceramic packaged                                                                                               | CDB7620             |

| -53                                   | Low            | Ku band                         | 0.1                            | Chip, ceramic packaged                                                                                               | CDF7621             |

| -53                                   | Low            | X band                          | 0.3                            | Chip, ceramic packaged                                                                                               | CDF7623             |

| -53                                   | Low            | Up to 10 GHz                    | 0.25                           | Single junction, common cathode pair, reverse<br>series pair, series pair, and unconnected pair,<br>plastic packages | SM57621             |

| -53                                   | Low            | Up to 100 GHz                   | 0.18                           | Single junction flip chip                                                                                            | SMS7621             |

| -52                                   | ZBD            | Ku band                         |                                | Beam lead, ceramic packaged                                                                                          | DD C2353            |

| -56                                   | ZBD            | Ku band                         |                                | Beam lead, ceramic packaged                                                                                          | DD C2354            |

| -50                                   | Medium         | X band                          | 0.15                           | Beam lead, ceramic packaged                                                                                          | DDB2503             |

| -50                                   | GaAs           | Up to 150 GHz                   | 0.04-0.07                      | GaAs single junction flip chip                                                                                       | DMK2790             |

| -48                                   | Medium         | Ku band                         | 0.1                            | Beam lead, ceramic packaged                                                                                          | DDB2504             |

| -47                                   | Medium         | S band                          | 0.30-0.50                      | Beam lead, ceramic packaged                                                                                          | DME2127             |

| -45                                   | Medium         | K band                          | 0.1                            | Chip, ceramic packaged                                                                                               | CDE7618             |

| -45                                   | Medium         | Ku band                         | 0.15                           | Chip, ceramic packaged                                                                                               | CME7660             |

| -45                                   | Medium         | K band                          | 0.1                            | Beam lead, ceramic packaged                                                                                          | DME2458             |

| -45                                   | Medium         | Ku band                         | 0.05-0.15                      | Beam lead, ceramic packaged                                                                                          | D ME2333            |

| -45                                   | Medium         | S band                          | 0.3-0.5                        | Series pair, beam lead, ceramic packaged                                                                             | D ME2050            |

| -40                                   | High           | X band                          | 0.15                           | Chip, ceramic packaged                                                                                               | CDP7624             |

| -40                                   | High           | K band                          | 0.1                            | Beam lead, ceramic packaged                                                                                          | DDB2265             |

Figure 11: Schottky Detector Diodes [31].

### 2.1.1.2. Features and Drawbacks

The Schottky diode is used as a detector and mixer as well as for power levelling for wireless LAN detectors, cellular phones, 24GHz radar systems, video detectors, etc. The RF performance (bandwidth) of diodes and the smaller plan area makes them often preferred and superior to that of FET circuits. The Zero Bias Schottky diode detector is widely used in RF and other applications. GaAs Schottky diodes are used to increase the operating bandwidth in terahertz (THz) spectroscopy [18]. The Schottky junction is widely used in frequency mixing and RF power detection circuits, due nearly to the ideal performance of Schottky diodes [17]. Furthermore, peak detectors utilizing nonlinear diode characteristics have long been used in electronic systems. They have the advantage of simplicity and high frequency capability. However, in order to use these detectors for precision operation, it generally requires high signal levels in order to overcome the uncertainties in determining accurately the dynamic diode turn-on characteristics. Moreover, when using diode detectors, the power dissipation will significantly increase at high frequencies in order to provide sufficient high-frequency gain to achieve the required signal level [21].

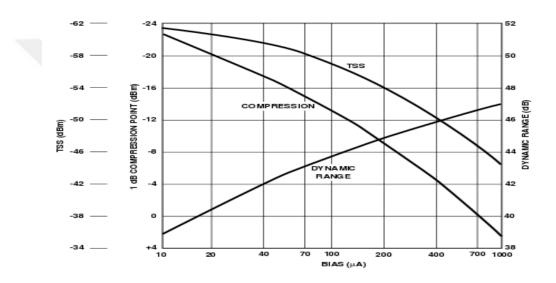

• Dynamic range: The square law dynamic range of Schottky diode detectors is defined as the difference between the power input for a 1-dB deviation from the ideal square law response (compression point) and the power input corresponding to the tangential signal sensitivity (TSS). In order to increase the dynamic range, the spacing between the TSS and the compression point should be increased (see Figure 12) [19].

The compression level can be raised by reducing  $R_L$ , the load resistance; however, this will degrade the sensitivity by

$$R_L/(R_L + R_V) Eq. 3$$

$R_L$  : Diode video resistance.

This degradation in the TSS exceeds the improvement in compression; therefore, there is no improvement in the square law dynamic range. Increasing the bias current raises

the compression level, but it also degrades the sensitivity. Nevertheless, the improvement in compression exceeds this degradation in sensitivity; hence, the square law dynamic range is increased. However, increasing the bias current will cause the power consumption to increase, too [19].

Figure 12: Dynamic range improvement with bias, [20].

- Sensitivity: This can be increased by decreasing the saturation current  $I_S$ . This happens when the video resistance  $R_L$  increases. However, there is a limit to improving the sensitivity such that when the resistance is so large such that it cannot be matched. An optimum diode is designed to have the proper saturation current. The choice of decreasing the saturation current involves a compromise between sensitivity due to high resistance and the losses due to matching. The disadvantages of using a resistor and DC biasing are the increase of power consumption and the 1/f generated noise.

- Temperature effect: At a relatively low temperature compensation, the use of a supplemental DC bias current is a possible solution to poor video bandwidth and low sensitivity. High temperature compensation can be performed by

providing a perfect matching at the input network as the impedance mismatch is the major cause of poor voltage sensitivity at  $85^{\circ}$  C [20].

#### 2.1.2. Envelop Detector Using Transistors

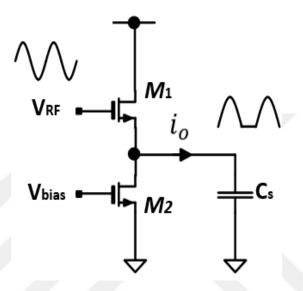

Figure 13: CMOS envelop detector scheme.

Figure 13 shows a basic schematic of an envelope detector, which is the CMOS version transferred from the bipolar one [21], [32]. M1 is biased in a subthreshold, where it provides a maximum nonlinear transfer function. M2 is a constant bias current source; this keeps the M1 gate bias voltage  $V_{gs0}$  constant. At capacitor  $C_s$ , the detector output is shown. The capacitor is charged by the output current  $i_0$  and it provides the grounding path to the RF signal. M1 performs the nonlinear transfer function from voltage to current to detect the RF signal, and depending on how abrupt the nonlinear transfer function is, the detector efficiency will be affected directly. MOS transistors show an exponential nonlinearity at room temperature in the subthreshold region of operation.

### 2.1.2.1. Detection Mechanism

If an NMOS transistor is used in subthreshold region for power detection, then the  $I_d - V_{gs}$  characteristic is:

$$I_d = I_{d0} e^{V_{gs}/V_0}$$

Eq.1

where  $V_0 = nkT/q$ , 1<n<2 and  $V_{gs}$  can be given by

$$V_{gs} = V_g + V_{gs0}$$

Eq.2

$V_{gs}$ : Gate-source voltage.

where  $V_g$  is the same  $V_{RF}$  represented in Figure 13, the low signal voltage. For small deviations from  $V_{gs0}$  (small amplitudes of  $V_g$ ), and by assuming any DC bias being included in  $I_{d0}$ , Eq.1 can be expanded to :

$$I_d = I_{d0} + \frac{d I_d}{d v_g} V_g + \frac{d^2 I_d}{d v_g^2} \frac{v_g^2}{2}$$

Eq. 3

then, the second derivative will be

$$\frac{dI_d}{dV_g} = \frac{I_{d0}}{V_0^2}$$

Eq.4

For an applied unmodulated RF signal,  $V_g = V_s \cos(wt)$ , and the quadratic term above can be expanded to be  $\cos^2(wt) = (1 + \cos 2wt)/2$ . Thus, to calculate the wanted incremental component in the output signal current  $i_0$ , which is dependent on the amplitude  $V_s$ , then:

$$i_s = I_{d0} \frac{V_s^2}{4V_s^2}$$

Eq.5

Different components of noise are added to the output current. These noise components originate from the transistor channel, a baseband noise which is transferred without frequency conversion, and the noise from the RF that is down converted to the baseband. The transistor channel noise is related to the bias current; therefore, it does not change with the change of the input signal level, and consequently, it will be kept constant in this circuit. By connecting the input to the ground at the baseband frequency, the baseband noise may be kept to low levels. The noise component originating from the RF frequency is down converted to the baseband when it is combined with the carrier or the in band blocker. Large blocking signals have a significant effect on the bias conditions of the transistor, and this will increase the detector sensitivity, while also risking the transistor to be pulled out of the subthreshold region. By keeping the bias current (DC current) generator constant in the circuit, the transistor channel noise and the sensitivity can be expected to be unaffected by the blocker power [32].

### 2.1.2.2. NMOS Envelop Detector: Features and Drawbacks

Closed-form expressions for the transistor-base envelop detector transfer function characteristic allow its use in precision applications at a very high frequency, unlike the diode-base envelop detectors, which require fairly large signal levels for precisions operation [21]. However, this envelop detector suffers from the PVT issue, where it is very sensitive to temperature and bias variations. In [33], a dummy envelop detector is used to feed the other input of the differential amplifier with an equal DC voltage while it is under the PVT variations, and the differential amplifier will amplify the difference signal.

#### 2.2. Root Mean Square (RMS) Power Detectors

Envelop power detectors are designed for constant envelop modulated signals, such as the Global System for Mobile communications (GSM) signals. Therefore, these detectors cannot be used for accurate measurements of a high peak-to-average ratio modulated signals. RMS power detectors, which are based on the average power measurement, are particularly suited to accurate power measurements of RF modulated signals that exhibit high peak-to-average ratio or noise-like property. RMS power detectors are usually realized by using methods of thermal detection, diode detection, and translinear detection [22], [23] [24] [25]. RMS power detectors produce a DC voltage signal proportional to the log of the input signal RMS value 20 in a linear relationship. Within a 40 dB range, it may provide a linearity of better than  $\mp 1$  dB. In addition, it can function well within the GHz range. Accurate measurements of  $\mp 0.2$  dB may be achieved for even high crest factor RF signals that are found in CDMA/WCDMA, WimAX, OFDM and higher level QAM modulation systems. These systems can produce a 10 to 15 dB crest factor in 3G, 4G, 5G and LTE wireless devices implemented in smartphones and cellular base stations.

#### **2.2.1.** Thermal Detection Method

The most basic design of thermal sensors was in the "light bulb" power detector by Ernst Lecher toward the end of the 1800s. These thermal-sensors absorb the input RF energy and generate an increase of heat in a terminating load. The increase in temperature in the terminating load is measured and calculated using a direct or indirect method, followed by computation of the conforming input power.

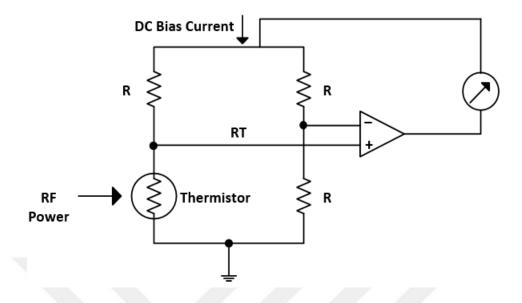

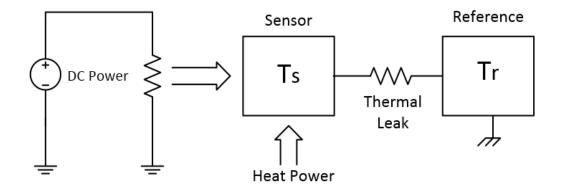

For RF power measurement equipment, the thermal detection method is widely used. It compares the heat value generated by an unknowing AC signal with a known heat value generated by a calibrated reference DC voltage (Figure 14). The advantages of this method are the wide bandwidth and the low measurement errors produced [22], [23]. However, the realization of thermal detection is complex and expensive, and it is not suitable for integration with the low-cost CMOS process.

A thermistor (Bolometer, see Figure 15) acts as an RF load from one side, and as the temperature measurement device from the other side, as illustrated in Figure 14. The thermistor's resistance varies according to the temperature; thus, by detecting the in-circuit resistance, it is easy to measure its temperature.

Figure 14: Thermistor Sensor Diagram.

Putting the thermistor element in one corner of a wheat-stone bridge is one of the common and basic practices. Thermistor resistance should be at the same value as the other resistors in the bridge to ensure balance. A (DC) substitution circuit is used for the purpose of balance, where a DC bias current is used to heat the thermistor and increase the temperature; thus, the thermal resistance will be sufficiently increased to be equal to the other resistors in the bridge. The thermistor resistance should be at the correct value in order to properly terminate the input RF signal, typically 50  $\Omega$  or 100  $\Omega$ .

Figure 15: Bolometer diagram.

The input RF signal power plus the power from the DC bias current is equal to the total power dissipated by the thermistor. The power consumption in relation to the RF signal heat can be calculated easily (since the bridge is in balance) by subtracting the DC reference power that is equal to  $1/4(V_{bridge}*I_{bridge})$  from the total dissipated power. The remaining three resistors are designed to have a negligible temperature coefficient due to resistance.

Practically, another thermistor bridge is used (the first thermal bridge is exposed to the RF signal) to cancel the temperature changes of the environment. The RF signal power will be dissipated in the terminated load of a thermocouple sensor; accordingly, the increase in the temperature is calculated. The temperature increases because of the thermocouple concept.

The output-generated voltage from the thermocouple-sensor is linear with the input power, and due to heat flow delays, it has a relatively long time constant. This means that the obtained readings are proportional to the average power of the input RF signal. Therefore, these sensors are widely used for modulated signal average-power measurements. However, the sensitivity is a major disadvantage for the thermal detection method in the RF measurement usage (for signals lower than microwatts level).

#### 2.2.2. Diode Detection Method

Diode detector circuits need to function with constant envelop signals. However, calibration ensures that the detector will perform well at a fixed peak-to-average ratio. In this case, for instance, QPSK is the only modulation scheme used by a communication system; then accurate power measurements can be made through the use of diode circuits. However, in systems with varying crest factors, such as CDMA or WCDMA, true RMS measurements become difficult to realise. Theoretically, different look-up tables may be used to solve this problem. This is based on the call loading at the base station (to notify with the crest factor for a specific channel). However, the calibration of a base station for every call loading is unpractical. In multi-carrier systems, it becomes impossible with this virtual 23

solution, where the crest factor of multiple carriers is changing for each carrier independently [34].

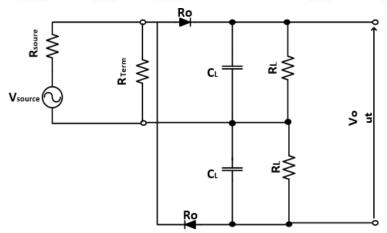

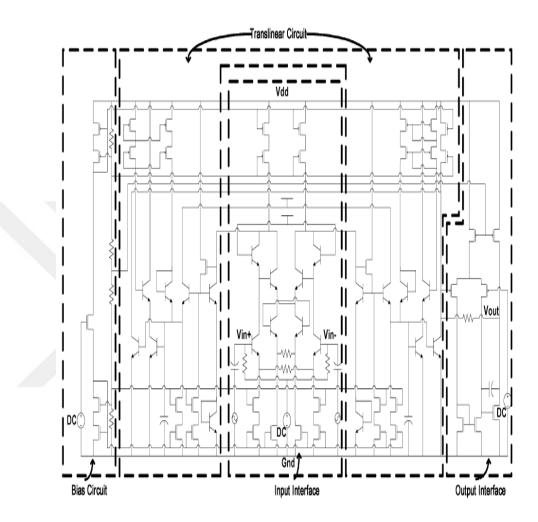

## 2.2.3. Translinear Detection Method

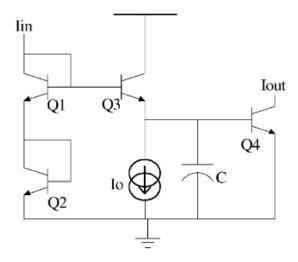

The translinear concept is a simple and smart method to realize complex mathematical functions by implementing a small number of transistors. All the input and output signals are current signals and the voltage changes need to be ignored while analysing translinear circuit behaviour. Static and dynamic translinear principles for nonlinear analog circuits are discussed in [35], [36], with systematic analyses and practical applications.

Depending on the translinear principle, an RMS detector has two essential units: a squarer-driver and low-pass filter circuits. These two parts can be performed within a single translinear loop. In Figure 16 [37], the relationship between  $I_{in}$  and  $I_{out}$  for ideal transistors (infinite  $\beta$ ), is represented by

$$I_{in}^{2} = I_{o}I_{out} + CV_{T}I_{out}$$

Eq. 1

Figure 16: Basic translinear loop that used in RMS detector

$I_o$ : the bias current, solving for  $I_{out}$  yields

$$I_{out} = \frac{I_{in}^2 / I_o}{1 + s C V_T / I_o} = \langle \frac{I_{in}^2}{I_o} \rangle$$

Eq.2

The operator <> stands for the time-average function.

Thus,  $I_{out}$  becomes the mean square of  $I_{in}$  and by performing the square root of  $I_{out}$ , gives the baseband signal RMS value. To save the implementation area, the square-root operation is performed off-chip. The input current  $I_{in}$  to the translinear loop has to be positive. For the purpose of improving the high-frequency performance, all transistors should be biased at all times, which is done by adding a DC bias current  $I_o$  to  $I_{in}$  to eliminate the need for a rectifier ( $|I_{in}| < I_o$ ). ( $V_{in}/I$ ) and ( $I_{out}/V$ ) converters are provided to interface with external voltage-mode signals

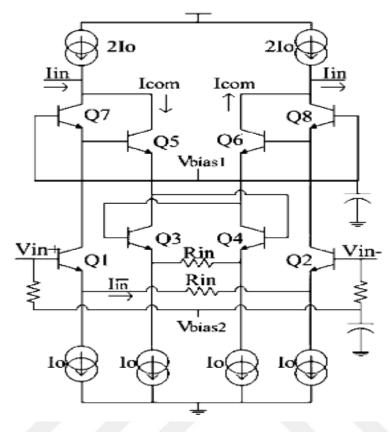

## **2.2.3.1.** Input Interface Circuit

Figure 17, shows the RMS detector wide-bandwidth voltage-to-current converter circuit, [38] [39].  $I_{in}$  is given by:

$$I_{in} = \frac{V_{in}}{R_{in}} - \frac{V_{BE1} - V_{BE2}}{R_{in}}$$

Eq.3

$V_{BE1}$  and  $V_{BE2}$  directly affect the current; therefore, the current generated from the voltage dropping across the resistor (in the second term of the right side in Eq.3) is a nonlinear current. The additional output current from Q3–Q6 in Caprio quad minimizes this nonlinearity effect for a certain level. A 50-ohm Shunt-resistance is connected to each of the differential V/I converter inputs (see Figure 20). On-chip capacitors are used to bypass  $V_{bias1}$  and  $V_{bias2}$  inputs. In this case, the circuit can be driven as single-ended with one input left open-circuited. Figure 18 shows the simulated frequency response of the V/I converter.

Figure 17: Caprio quad input interface circuit [37].

Figure 18: Frequency response at the input of the translinear loop [37].

## 2.2.3.2. Squarer-Divider and Low-Pass Filter

A rectifier is unnecessary for signal balancing processing purposes, where the output currents,  $+I_{in}$  and  $-I_{in}$  of the differential V/I convertor are added to the bias current and feed to two copies of the translinear loops, as shown in Figure 19. These output currents are given by

$$I_{out \ 1,2} = \langle \frac{(I_o \pm I_{in})^2}{I_o} \rangle$$

Eq. 4

For two loops, the output current is given by

$$I_{out 1} + I_{out 2} = \langle \frac{(I_o + I_{in})^2}{I_o} \rangle + \langle \frac{(I_o - I_{in})^2}{I_o} \rangle = \frac{1}{I_o} \langle (I_o + I_{in})^2 + (I_o - I_{in})^2 \rangle$$

$$= \frac{2\langle I_{in}^2 \rangle}{I_o} + 2I_o$$

Eq. 5

Obviously, omitting the second right part of Eq.5 (offset current) will result in the mean-square value of the input current being multiplied by  $2/I_o$ .

Figure 19: Translinear loop with base-current compensation shown in the dashed region (CM: current mirror) [37].

It is worth mentioning that temperature is not an effective parameter for these formulas. Instead of connecting a diode at the input of the loop, an NMOS source follower is used for the purpose of base-current error minimization (see Figure 21).

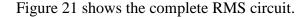

## 2.2.3.3. Output Interface Circuit

After the squarer-driver and low-pass filter, the current-signal should be converted back to a voltage-signal and the offset current removed, which is performed by I/V converter circuit. This circuit is realized by a transimpedance amp consisting of a CMOS op-amp with feedback resistor  $R_{out}$  (see Figure 20).

Figure 20: Output interface circuit.

The circuit design of this converter is basic and straightforward due to the signal's low frequency level at this point. The non-inverting terminal is connected to a DC value equalling the collector voltages of the output transistors in the translinear circuits in order to compensate for early effects. The current remaining after subtracting the offset current is converted into an output voltage.  $V_{out}$  is the product of the mean-square value of  $V_{in}$  and the gain k.

$$V_{out} = \frac{2R_{out}\langle I_{in}^2 \rangle}{I_o} = k \langle V_{in}^2 \rangle$$

Eq. 6

Figure 21: Complete circuit diagram of RMS detector by using the translinear principle [37],.

# 2.2.3.4. Error Analysis

The collector current of Q3 (see Figure 21) is not exactly equal to  $I_o - I_c$  because of the finite current gain of the transistors Q4 and Q5. This causes an error in the translinear loop, which worsens when  $I_{cQ4}$  is increases. The dashed part of Figure 19 shows how base-current compensation can be used to significantly reduce the base-current error. The compensation circuit causes the base-current errors to be decreased by  $2/(1+\beta)$ . For free-temperature variations, it can be experimentally proved that the total relative errors of the output are decreased to  $\pm 1\%$ . For temperature variations from -40 °C to 100°C, the output will change by  $\pm 1.2$  dB, [37].

#### 2.2.4. Features and Drawbacks

The key advantage of using RMS detectors over other types of power detectors is the ability to deal with high peak-to-average ratio signals existing within different modulation schemes in modern communication systems, such as 4G, 5G and LTE. For instance, long calculation procedures and large calibration tables in the baseband are no longer necessary when dealing with modulated CDMA signals and unmodulated carriers because the RMS detector will produce the same value (0 dBm) for both. However, dynamic range, sensitivity, bandwidth, power dissipation, and chip-area are trade-offs between all these parameters, and it is very difficult (if not impossible) to achieve optimal RMS detector performance with respect to each of the previous parameters (see Table 1).

| Parameters      | [41]       | [42]        | [43]    | [40]     |

|-----------------|------------|-------------|---------|----------|

| Voltage         | 1.2 V      | 2.8 V       | 3V      | 3.3 V    |

| Power           | 0.18 mW    | 70 mW       | 50 dB   | 63.36 mW |

| Dynamic Range   | 20 dB      | 40dB@       | 50dB    | 58dB     |

|                 |            | 8GHz        |         |          |

|                 |            | 60dB@       |         |          |

|                 |            | 3.6Ghz      |         |          |

| Min.Input Power | -35dBm @   | -60dBm@ 3.6 | -45 dBm | -50dBm   |

|                 | 1Ghz       | GHz         |         |          |

|                 |            |             |         |          |

| Frequency 125M  | 1Hz-5.5GHz | DC – 8GHz   | 450MHz  | 0.5-3GHz |

|                 |            |             |         |          |

|                                                                 | Process | 130 nm | 180 nm | 350 nm | 130nm |  |  |  |

|-----------------------------------------------------------------|---------|--------|--------|--------|-------|--|--|--|

| Table 1: Comparison between different RMS power detectors [40]. |         |        |        |        |       |  |  |  |

### 2.3. LOG Detector

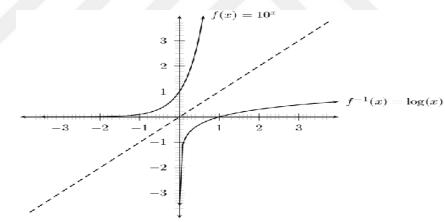

A logarithmic amplifier (a log-amp or log detector) is used as a power detector depending on its transfer function (see Figure 22). The concept is simple such that the output voltage or current is proportional to the logarithic value of the input voltage or current. This power representation is compatible with the modern communication standards that use the dBm power scale. Keeping this input/output relationship valid over a high dynamic range is a key advantage of using log detectors among the other power detectors. The word "amplifier" in the name "log amplifier" does not have the common meaning of amplification; it is in fact a linear-to-logarithmic converter.

Figure 22: Logarithm function of the log detector, assuming (x,y) to be the input and output signals respectively.

## 2.3.1. Log-amp Applications

• Log-amps can be used for optical-circuits, power control, as well as for medical, chemical, and biological instrumentation. The DC log-amp ("DC" is

somewhat of a misnomer) is used where signals in such applications are common to be relatively slowly-changing signals, i.e., up to about 1 MHz.

• Baseband log-amp: It used in audio and video circuits, when some type of signal compression is needed, as well as within IF stages of a signal receiver chain and the signal-processing path of ultrasound circuits. It has a symmetrical output for positive and negative input signals, with an output, which is positive for positive inputs and negative for negative inputs.

• Demodulating log-amp: This both compresses and demodulates RF signals and generates at the output a logarithmic version of the rectified input signal's envelope. This detector is used in RF-transceiver applications, where the received RF-signal strength is used to control the transmitter output power. The output is based on the absolute value of the input, and it is positive regardless whether the input is positive or negative.

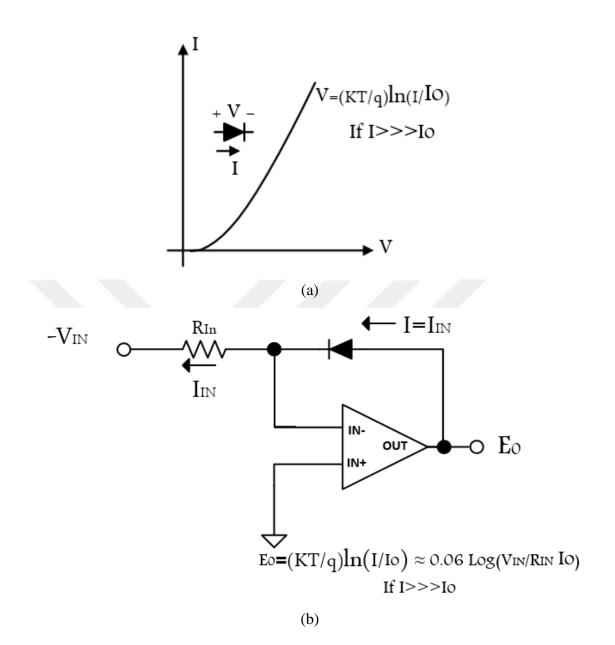

## **2.3.2. LOG Detector Principle of Work**