# $\underline{\textbf{ISTANBUL TECHNICAL UNIVERSITY}} \bigstar \underline{\textbf{INSTITUTE OF ENERGY}}$

# DESIGN OF FAULT-TOLERANT CASCADED H-BRIDGE MULTILEVEL INVERTER WITH OUTPUT-SIDE TRANSFORMERS USING BIDIRECTIONAL SWITCHES

## M.Sc. THESIS

## Muhammet BİBEROĞLU

**Energy Science and Technology Department**

**Energy Science and Technology Programme**

## <u>ISTANBUL TECHNICAL UNIVERSITY</u> ★ <u>INSTITUTE OF ENERGY</u>

# DESIGN OF FAULT-TOLERANT CASCADED H-BRIDGE MULTILEVEL INVERTER WITH OUTPUT-SIDE TRANSFORMERS USING BIDIRECTIONAL SWITCHES

## M.Sc. THESIS

Muhammet BİBEROĞLU (301101062)

**Energy Science and Technology Department**

**Energy Science and Technology Programme**

Thesis Advisor: Prof. Dr. Filiz KARAOSMANOĞLU

**JANUARY 2013**

# <u>İSTANBUL TEKNİK ÜNİVERSİTESİ</u> ★ ENERJİ ENSTİTÜSÜ

# ÇİFT YÖNLÜ ANAHTARLAR KULLANARAK HATA TOLERANSLI ÇIKIŞ TRAFOLU KASKAT H-KÖPRÜ ÇOK-SEVİYELİ EVİRİCİ TASARIMI

## YÜKSEK LİSANS TEZİ

Muhammet BİBEROĞLU (301101062)

Enerji Bilim ve Teknoloji Anabilim Dalı Enerji Bilim ve Teknoloji Programı

Tez Danışmanı: Prof. Filiz KARAOSMANOĞLU

Muhammet Biberoğlu, a M.Sc. student of ITU Institute of Energy student ID 301101062, successfully defended the thesis entitled "DESIGN OF FAULT-TOLERANT CASCADED H-BRIDGE MULTILEVEL INVERTER WITH OUTPUT-SIDE TRANSFORMERS USING BIDIRECTIONAL SWITCHES", which he prepared after fulfilling the requirements specified in the associated legislations, before the jury whose signatures are below.

| Thesis Advisor: | Prof. Dr. Filiz KARAOSMANOĞLU İstanbul Technical University            |  |

|-----------------|------------------------------------------------------------------------|--|

| Jury Members :  | Prof. Dr. Filiz KARAOSMANOĞLU İstanbul Technical University            |  |

|                 | Assoc.Prof. Dr. Önder GÜLER<br>İstanbul Technical University           |  |

|                 | <b>Assoc.Prof. Dr. M. Turan SÖYLEMEZ</b> İstanbul Technical University |  |

Date of Submission: 14 December 20012 Date of Defense: 23 January 2013

To my parents,

### **FOREWORD**

First, I would like to express my deepest appreciation to my advisor, Prof. Dr. Filiz KARAOSMANOĞLU, for her support, all of her help and instructions during my study and research; also, I would like to thank Assist. Prof.Dr. Kayhan INCE, for his help, guidance and suggestions throughout the research.

I would also like to thank all my colleagues from Department of Energy Systems Engineering of Yalova University for their support and trust. Moreover, I would like to extend a special thanks to my colleagues Mr.Taha Nurettin GÜCİN and Mr.Abdussamet SUBAŞI for their support and motivating words.

Finally, I would like to express my great gratitude to my parents. There are no words that can show my appreciation to them for all the sacrifices.

December 2012

Muhammet BİBEROĞLU (Electrical&Electronics Engineer)

## TABLE OF CONTENTS

|                                                                              | <b>Page</b> |

|------------------------------------------------------------------------------|-------------|

| FOREWORD                                                                     | ix          |

| TABLE OF CONTENTS                                                            |             |

| ABBREVIATIONS                                                                |             |

| LIST OF TABLES                                                               |             |

| LIST OF FIGURES                                                              |             |

| SUMMARY                                                                      |             |

| ÖZET                                                                         |             |

| 1. INTRODUCTION                                                              |             |

| 1.1 Thesis Structure                                                         |             |

| 2. THEORETICAL BACKGROUND OF MULTILEVEL INVERTERS                            | 7           |

| 2.1 Multilevel Inverter Topologies                                           |             |

| 2.1.1 Neutral point clamped MLI                                              |             |

| 2.1.2 Capacitor-clamped MLI                                                  |             |

| 2.1.3 Cascaded H-Bridge MLI                                                  |             |

| 2.1.4 Multiple source topology                                               |             |

| 2.1.5 Multi-winding transformer topology                                     | 16          |

| 2.1.6 Modular topology                                                       |             |

| 2.1.7 Multiple-transformer topology                                          | 18          |

| 2.2 Modulation Techniques for MLIs                                           |             |

| 2.2.1 MLI PWM strategies                                                     |             |

| 2.2.3 Other MLI modulation algorithms                                        |             |

| 2.3 Bi-directional Switch Technology                                         | 23          |

| 2.4 Fault-Tolerant MLI Strategies                                            | 25          |

| 2.5 Literature Review                                                        |             |

| 3. PROPOSED MULTILEVEL INVERTER SYSTEM DESIGN                                | 33          |

| 3.1 System Components                                                        | 36          |

| 3.1.1 H-Bridge inverter modules                                              |             |

| 3.1.2 Transformers and bi-directional switches                               | 38          |

| 3.2 Fault -Tolerant Inverter System and Application of Reconfiguration Techn | ique        |

|                                                                              | 45          |

| 3.2.1 Normal operation (no-fault) mode                                       | 45          |

| 3.2.2 Fault conditions                                                       |             |

| 3.2.2.1 First inverter fault                                                 | 53          |

| 3.2.2.2 Second inverter fault                                                | 54          |

| 3.2.2.3 Third inverter fault                                                 | 55          |

| 4. RESULTS and DISCUSSIONS                                                   | 57          |

| 4.1 No Fault Condition                                                       | 57          |

| 4.2 Fault Conditions                                                         |             |

| 4.2.1 First inverter fault condition                                         |             |

| 4.2.2 Second inverter fault condition                                        |             |

| 4.2.3 Third inverter fault condition                                         |             |

| 5. CONCLUSION                                                                |             |

| REFERENCES                                                                   | 83          |

| CURRICULUM VITAE                                                             | 91          |

#### **ABBREVIATIONS**

**MOSFET** : Metal Oxide Semiconductor Field Effect Transistor

**IGBT** : Insulated Gate Bipolar Transistor

DC : Direct Current

AC : Alternating Current

MLI : Multilevel Inverter

BDS : Bidirectional Switch

DB : Diode-Bridge CS : Common Source

**RES** : Renewable Energy Sources

**SARES** : Stand Alone Renewable Energy Systems

**PWM**: Pulse Width Modulation

PS-PWM : Phase Shifted Pulse Width Modulation

LEVEL Shifted Pulse Width Modulation

PD-PWM : Phase Disposition Pulse Width Modulation

**POD-PWM**: Phase Opposition Disposition Pulse Width Modulation

APOD-PWM: Alternate Phase Opposition Disposition Pulse Width Modulation

NPC : Neutral Point ClampedFC : Flying CapacitorCHB : Cascaded H-Bridge

MTT : Multi-winding Transformer Topology

**SVM** : Space Vector Modulation

**SHE** : Selective Harmonic Elimination

NLC : Nearest Level Control

IEA : International Energy AgencyTHD : Total Harmonic Distortion

**MTHD**: Minimisation of Total Harmonic Distortion

# LIST OF TABLES

|                                                                                       | <u>Page</u> |

|---------------------------------------------------------------------------------------|-------------|

| <b>Table 2.1 :</b> Switches states and the output voltage for three-level NPC         | 10          |

| <b>Table 2.2:</b> Switches states and the output voltage for three-level FC           |             |

| <b>Table 2.3 :</b> Switch-Sates for the first H-Bridge cell                           |             |

| <b>Table 2.4:</b> Applicability of modulation methods to multilevel topologies        |             |

| <b>Table 2.5 :</b> Comparison of multilevel inverter topologies depending on          |             |

| implementation factors                                                                | 23          |

| Table 3.1 : Output voltage according to the switch states                             | 38          |

| <b>Table 3.2 :</b> Simulation parameters for the IGBT-Diode devices.                  |             |

| <b>Table 3.3:</b> Simulation parameters of the first inverter's transformer           | 40          |

| <b>Table 3.4 :</b> Simulation parameters of the second transformer.                   | 40          |

| Table 3.5 : Parameters of the third inverter.                                         |             |

| <b>Table 3.6 :</b> Simulation parameters of MOSFETs                                   |             |

| <b>Table 3.7:</b> PWM switching functions up to comparing conditions.                 |             |

| <b>Table 3.8:</b> Bi-directional switches' states up to the fault conditions.         |             |

| Table 4.1: Output voltage and current parameters with DB-MOSFET and with              |             |

| resistive load                                                                        |             |

| Table 4.2: Output voltage and current parameters with DB-MOSFET and with              |             |

| load                                                                                  |             |

| Table 4.3: Output voltage and current parameters with CS-MOSFETs-BDS ar               |             |

| with resistive load.                                                                  |             |

| Table 4.4: Output voltage and current parameters with CS-MOSFETs-BDS are              |             |

| with R-L load                                                                         |             |

| Table 4.6 : Output voltage and current parameters for a R-L load when a fault         |             |

| occurred in first inverter.                                                           |             |

| <b>Table 4.7:</b> Output voltage and current parameters for a resistive load when a f |             |

| occurred in the second inverter.                                                      |             |

| <b>Table 4.8:</b> Output voltage and current parameters for a R-L load when a fault   |             |

| occurred in the second inverter.                                                      |             |

| <b>Table 4.9:</b> Output voltage and current parameters for a resistive load when a f |             |

| occurred in the third inverter.                                                       |             |

| <b>Table 4.10:</b> Output voltage and current parameters for a RL load when a fault   |             |

| occurred in the third inverter                                                        | /8          |

# LIST OF FIGURES

|                                                                                           | Page       |

|-------------------------------------------------------------------------------------------|------------|

| Figure 1.1 : Share of resources of the in electricity production                          | 2          |

| <b>Figure 1.2 :</b> Waveforms for different inverter types                                |            |

| Figure 2.1: Power range of available power semiconductors.                                |            |

| Figure 2.2: Generalized staircase waveform.                                               |            |

| Figure 2.3: Diode-clamped mulilevel inverter circuit topologies: (a)Three-l               |            |

| (b)Five-level.                                                                            |            |

| Figure 2.4: FC multilevel inverter circuit topologies (a) Three-level (b) Five-           | -level .12 |

| Figure 2.5: Cascaded H-Bridge multilevel inverter with seperate DC source                 |            |

| Figure 2.6 : CHB asymmetric exponent 2                                                    | 15         |

| Figure 2.7: CHB asymmetric exponent 3                                                     | 15         |

| Figure 2.8: Multiple source topology                                                      | 16         |

| Figure 2.9: Multi-winding transformer topology.                                           | 17         |

| Figure 2.10 : Modular topology.                                                           | 17         |

| Figure 2.11: Cascaded H-Bridges with isolation transformers.                              | 18         |

| Figure 2.12: Multilevel inverter modulation classification.                               |            |

| Figure 2.13: Device working quadrants.                                                    |            |

| Figure 2.14: Different bi-directional switch implementations by using MOS                 |            |

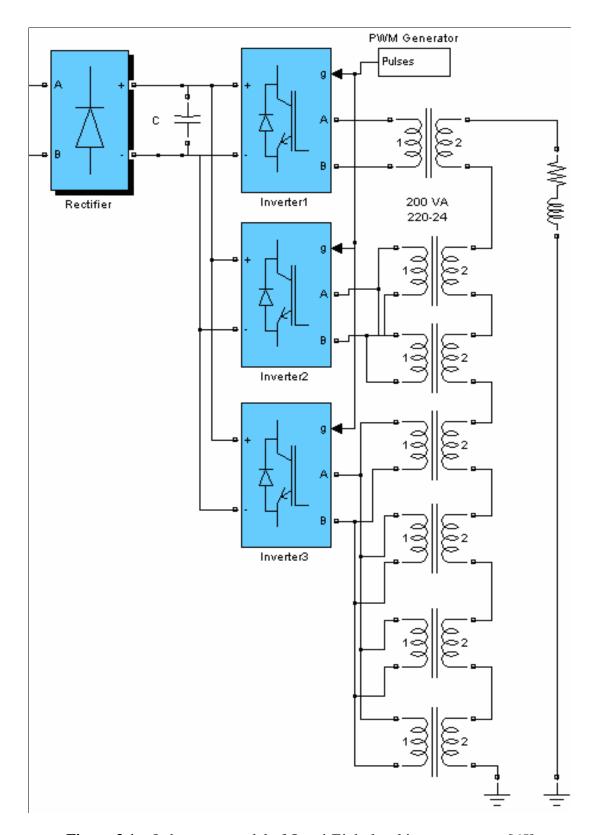

| <b>Figure 3.1 :</b> Laboratory model of Quasi-Eight level inverter system                 |            |

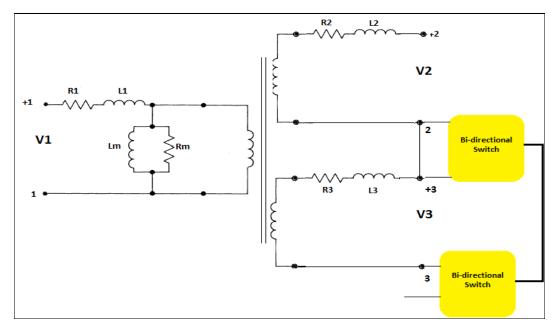

| Figure 3.2: Proposed multilevel inverter topology.                                        |            |

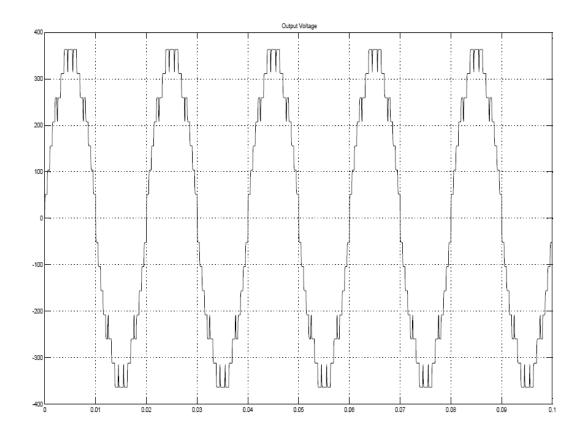

| Figure 3.3 : Quasi-8-level inverter's output voltage                                      |            |

| Figure 3.4: Typical H-Bridge inverter module.                                             |            |

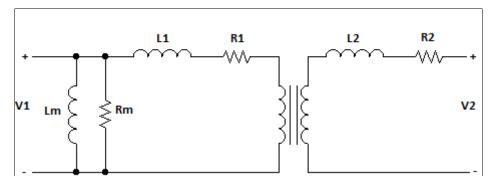

| Figure 3.5: Equivalent circuit of transformer connected to the output of firs             |            |

| inverter                                                                                  |            |

| <b>Figure 3.6 :</b> Equivalent circuit of third H-Bridge inverter's transformer           |            |

| <b>Figure 3.7 :</b> Diode-Bridge MOSFET BDS current flow paths at                         |            |

| a)Positive alternation b)Negative alternation                                             |            |

| Figure 3.8: Common Source MOSFETs BDS current flow paths at                               |            |

| a)Positive alternation b)Negative alternation                                             |            |

| Figure 3.9: The proposed inverter when no fault exists                                    |            |

| Figure 3.10 : Compared signals for PWM.                                                   |            |

| <b>Figure 3.11 :</b> The compared signal for production of PWM signal (fc=1000lf fm=50Hz) |            |

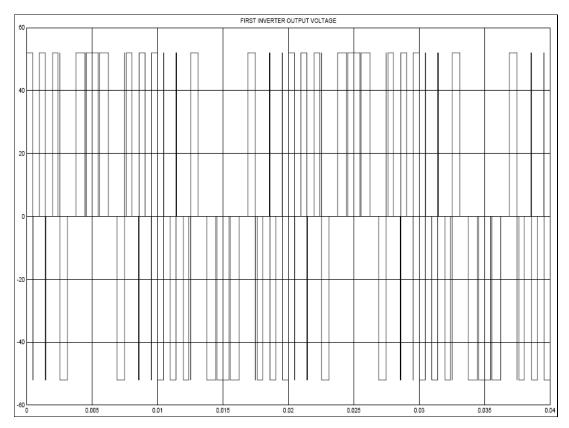

| <b>Figure 3.12 :</b> The output voltage of the first inverter (fc=1000Hz)                 | 47<br>18   |

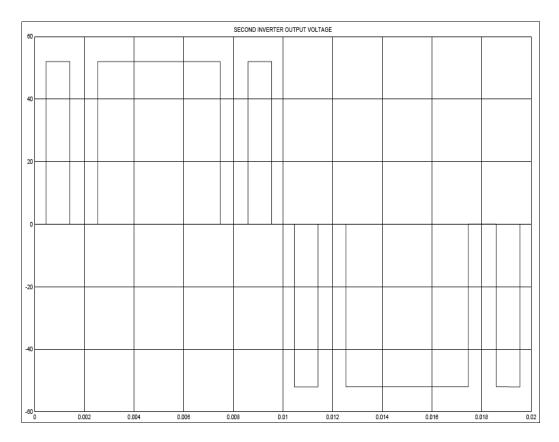

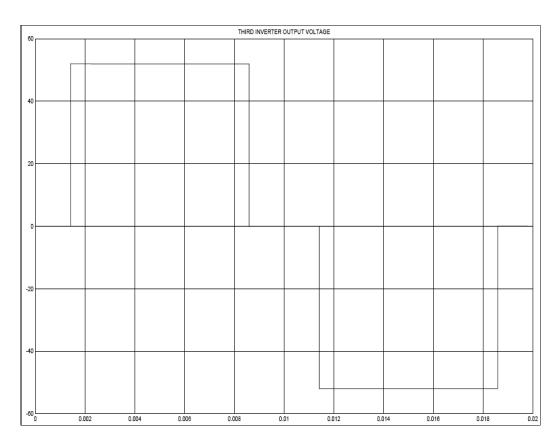

| <b>Figure 3.13 :</b> The output voltage of the second inverter (f=150Hz)                  |            |

| <b>Figure 3.14 :</b> The output voltage of the second inverter (1=150Hz)                  |            |

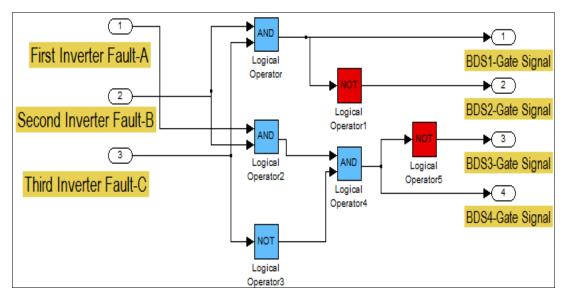

| Figure 3.15: The simulation circuits of gating signals of the BDSs                        |            |

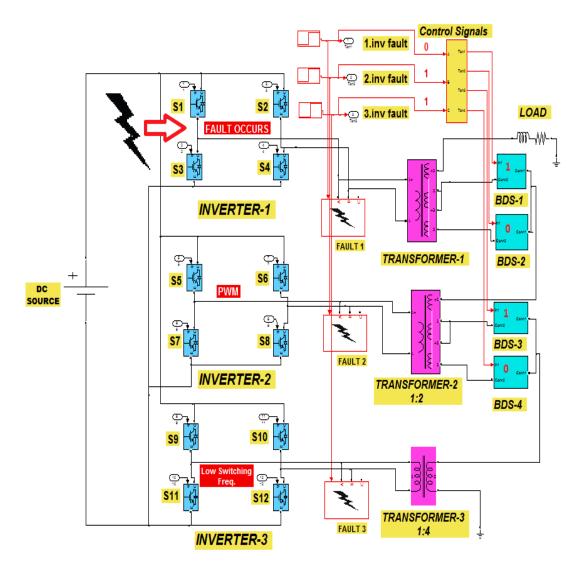

| <b>Figure 3.16:</b> Proposed multilevel inverter when a fault exists in the first inv     |            |

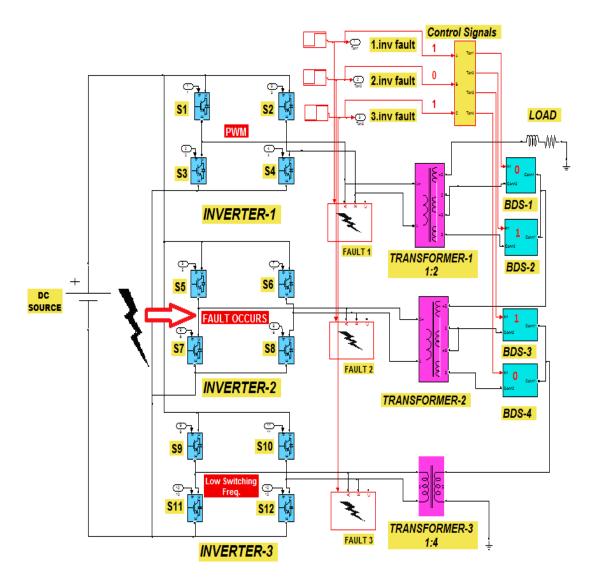

| Figure 3.17: Proposed multilevel inverter when a fault exists in second inv               |            |

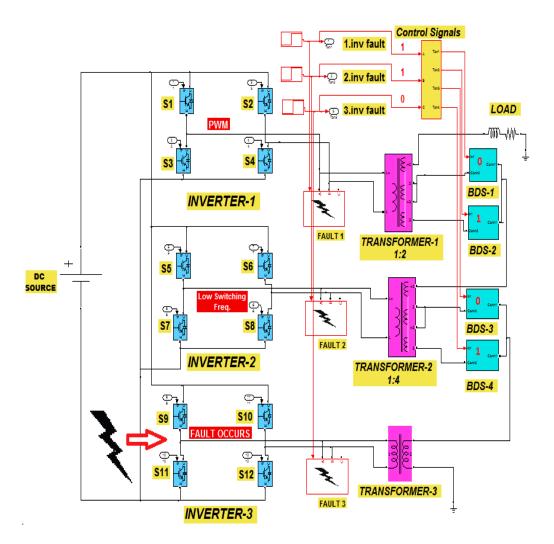

| Figure 3.18: Proposed multilevel inverter when a fault exists in second inv               |            |

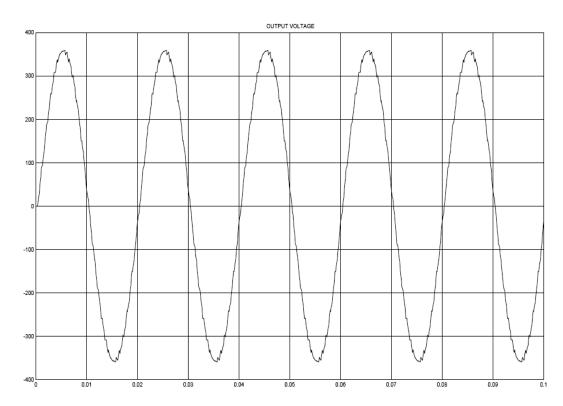

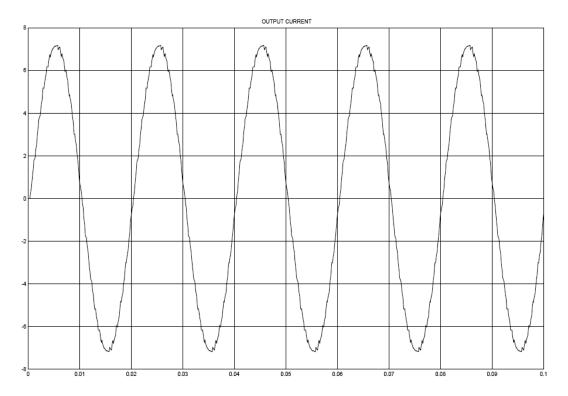

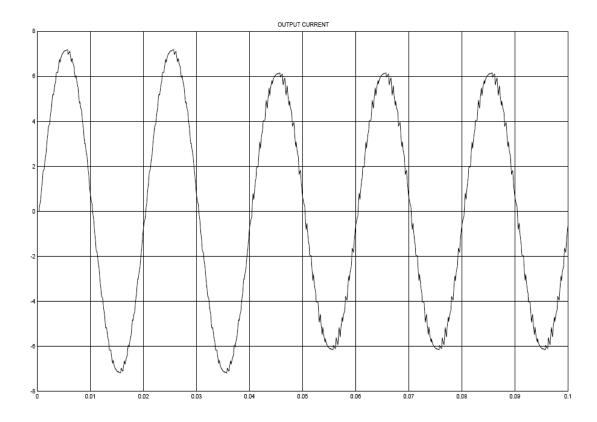

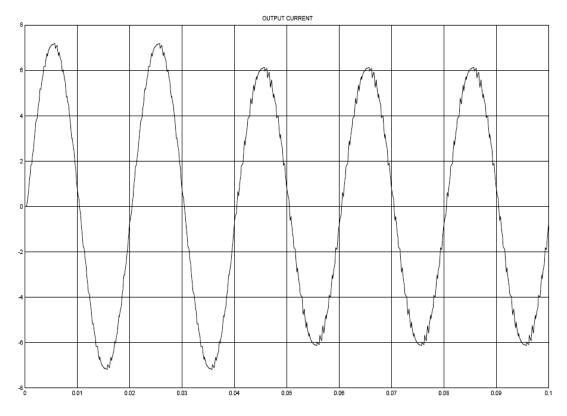

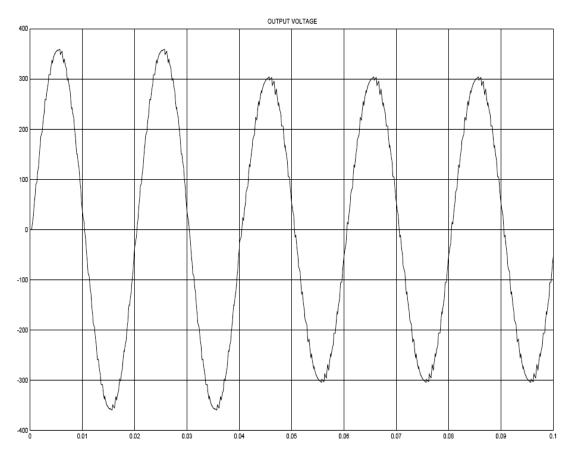

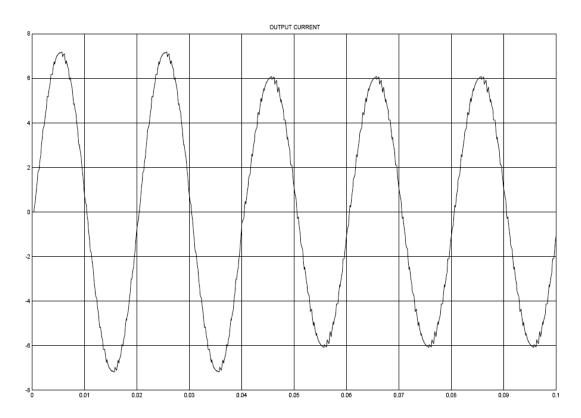

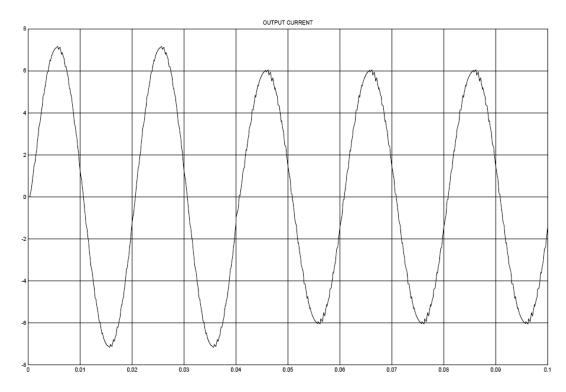

| <b>Figure 4.1 :</b> Output voltage with DB-MOSFET-BDS with purely resistive load5       |   |

|-----------------------------------------------------------------------------------------|---|

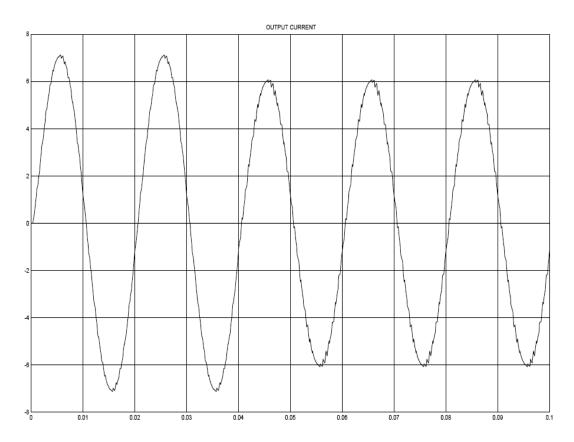

| Figure 4.2: Output current with DB-MOSFET-BDS with purely resistive load 5              | 9 |

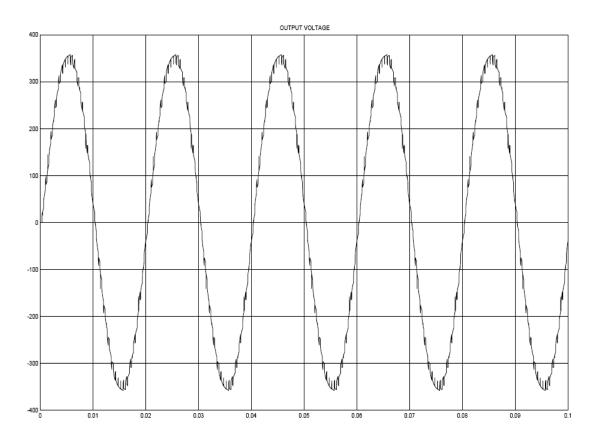

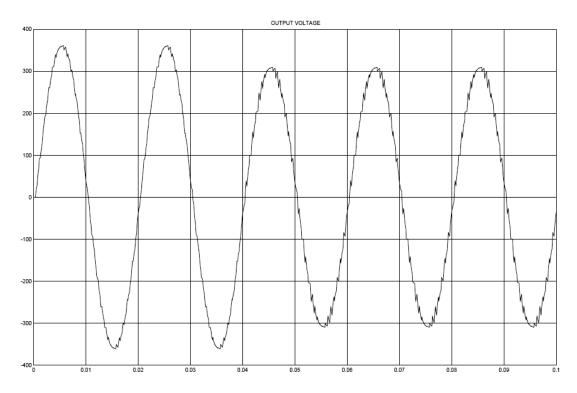

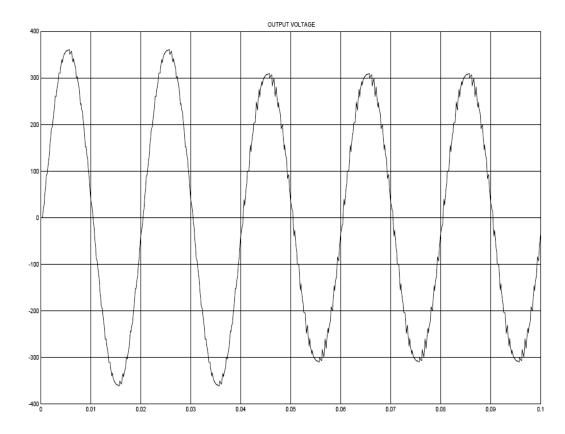

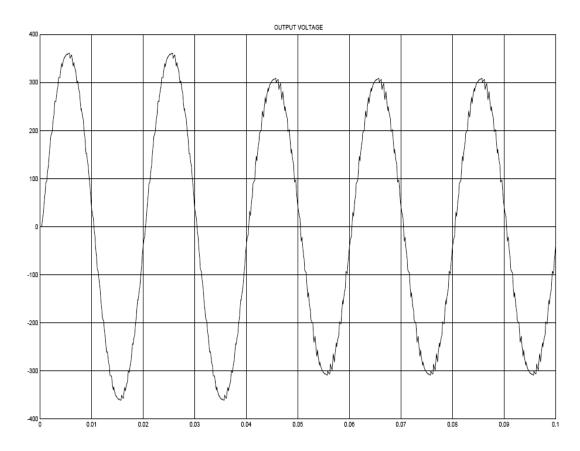

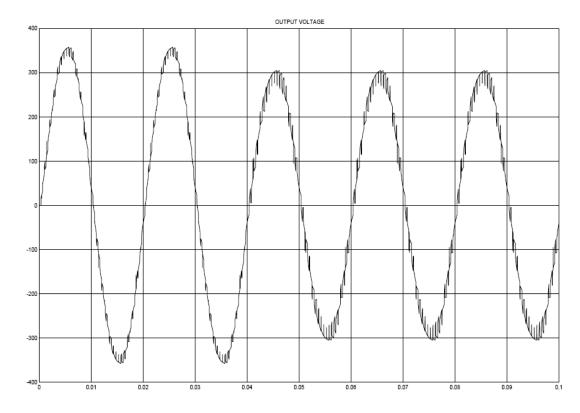

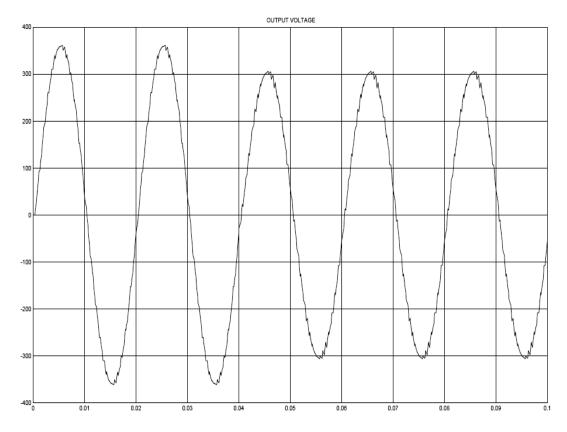

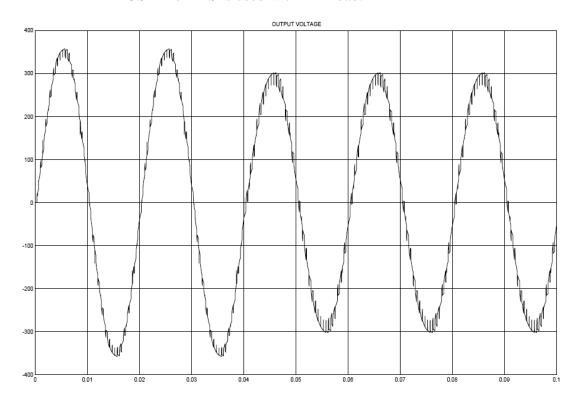

| <b>Figure 4.3 :</b> Output Voltage with DB-MOSFET-BDS with R-L load                     | 0 |

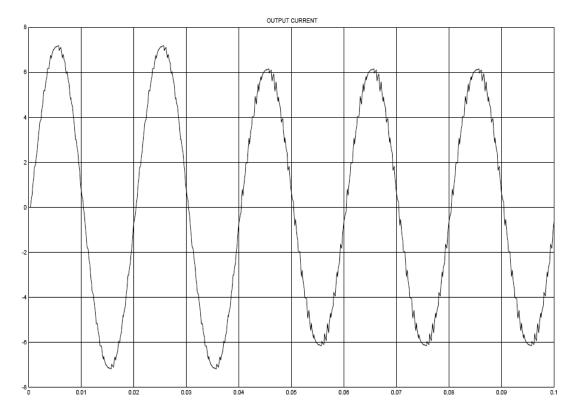

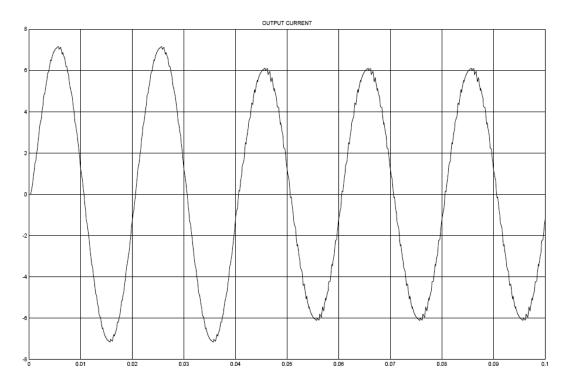

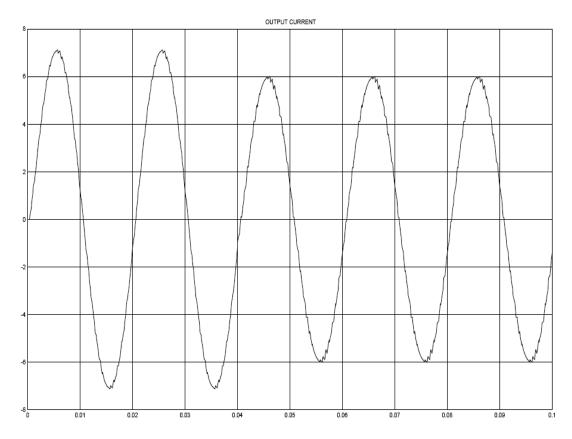

| <b>Figure 4.4 :</b> Output current with DB-MOSFET-BDS with R-L load6                    | 1 |

| Figure 4.5: Output voltage when a fault occurred in first inverter if DB-MOSFET         | - |

| BDS used with resistive load6                                                           | 3 |

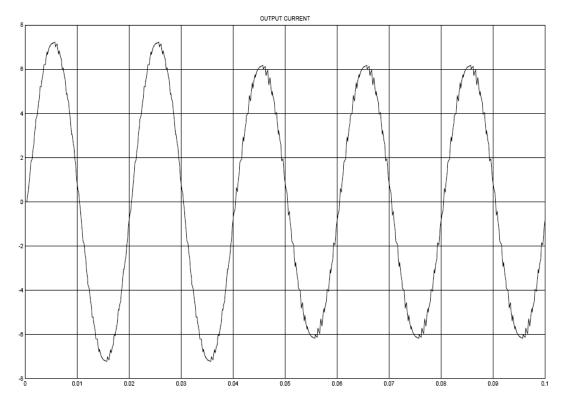

| Figure 4.6: Output current when a fault occurred in first inverter if DB-MOSFET         | - |

| BDS used with resistive load6                                                           | 4 |

| <b>Figure 4.7 :</b> Output voltage when a fault occurred in the first inverter if CS-   |   |

| MOSFET-BDS used with resistive load6                                                    | 4 |

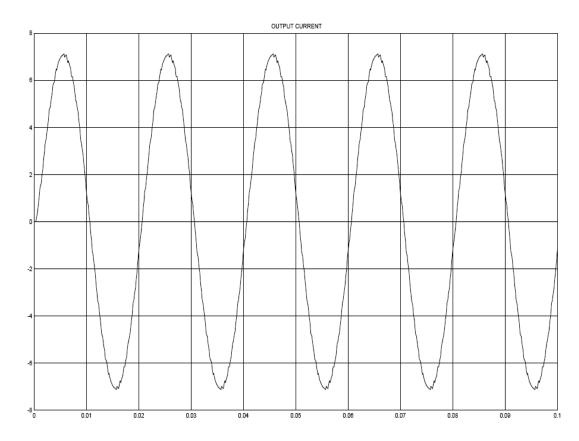

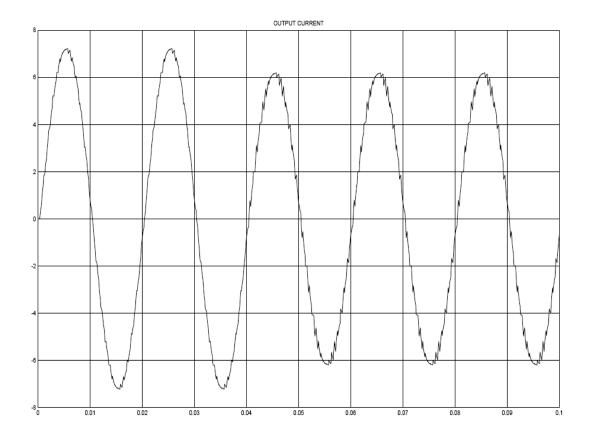

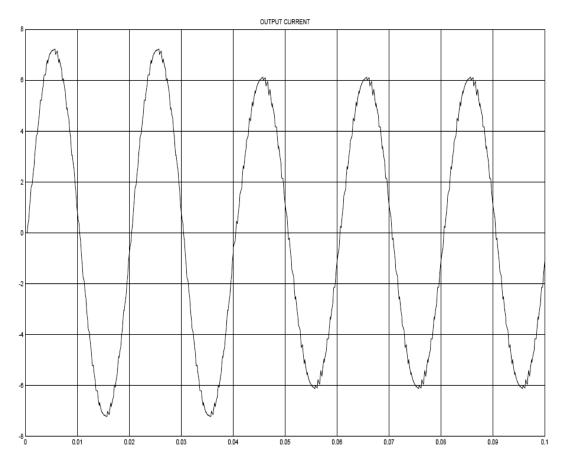

| <b>Figure 4.8 :</b> Output current when a fault occurred in the first inverter if CS-   |   |

| MOSFET-BDS is used with resistive load6                                                 | 5 |

| Figure 4.9: Output voltage when a fault occurred in the first inverter if DB-           |   |

| MOSFET-BDS used with R-L load6                                                          | 7 |

| Figure 4.10: Output current when a fault occurred in the first inverter if DB-          |   |

| MOSFET-BDS used with R-L load6                                                          | 7 |

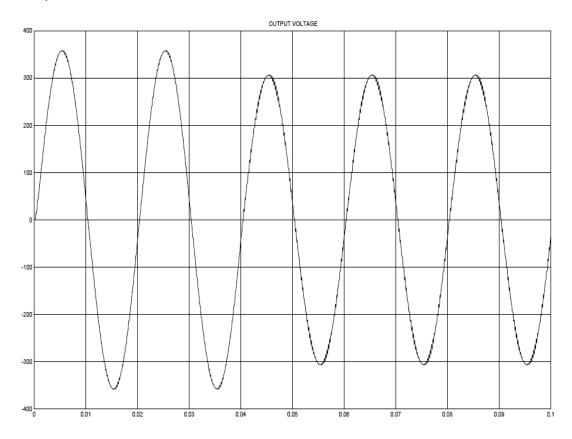

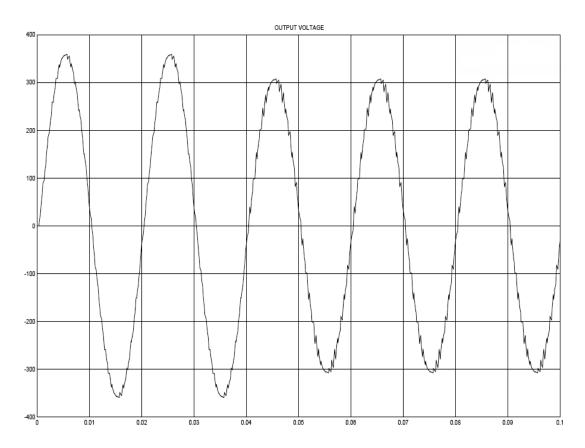

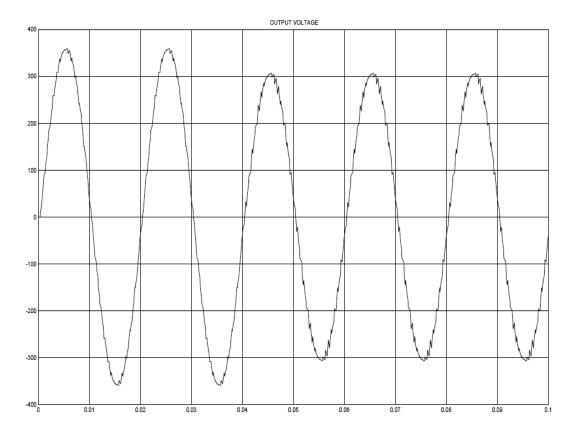

| <b>Figure 4.11 :</b> Output voltage when a fault occurred in the first inverter if CS-  |   |

| MOSFET-BDS used with R-L load6                                                          | 8 |

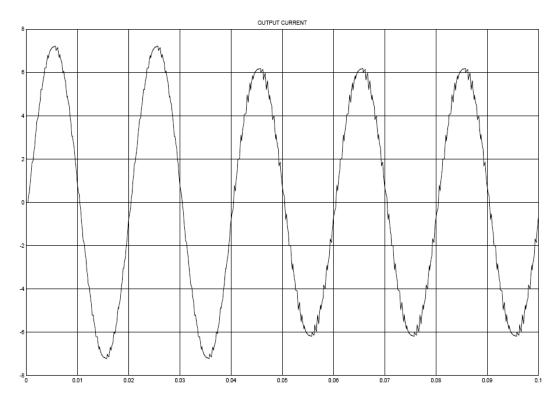

| Figure 4.12: Output current when a fault occurred in the first inverter if CS-          |   |

| MOSFET-BDS used with R-L load6                                                          | 8 |

| Figure 4.13: Output current when a fault occurred in first inverter if DB-              |   |

| MOSFET-BDS is used with resistive load                                                  | 0 |

| <b>Figure 4.14 :</b> Output current when a fault occurred in the second inverter if CS- |   |

| MOSFETs-BDS is used with resistive load                                                 | 0 |

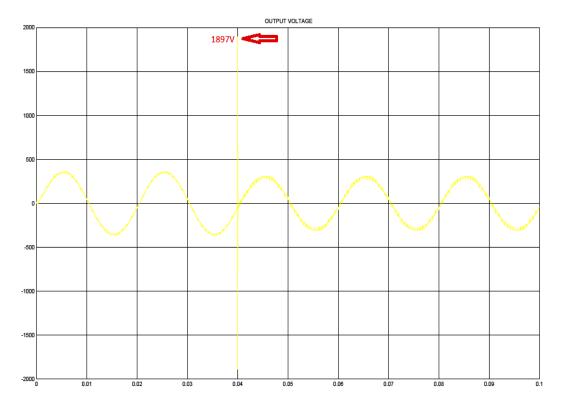

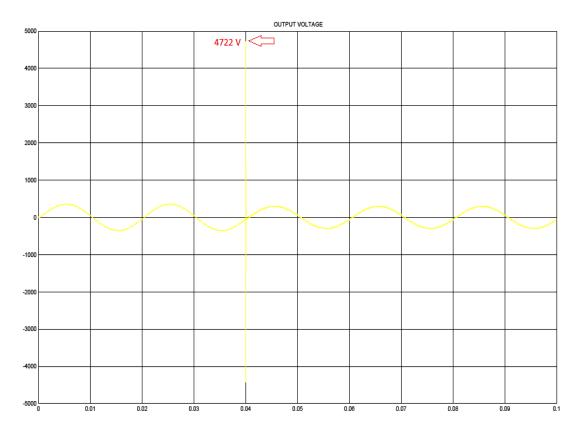

| Figure 4.15: Output voltage when a fault occurred in the second inverter if DB-         |   |

| MOSFET-BDS is used with resistive load                                                  | 1 |

| <b>Figure 4.16 :</b> Output current when a fault occurred in the second inverter if CS- |   |

| MOSFETs-BDS is used with resistive load                                                 | 1 |

| <b>Figure 4.17 :</b> Output voltage when a fault occurred in the second inverter if CS- |   |

| MOSFETs-BDS is used with R-L load7                                                      | 2 |

| <b>Figure 4.18 :</b> Output current when a fault occurred in the second inverter if CS- |   |

| MOSFETs-BDS is used with R-L load                                                       | 3 |

| Figure 4.19: Output voltage when a fault occurred in the second inverter if DB-         |   |

| MOSFET-BDS is used with R-L load7                                                       | 3 |

| Figure 4.20: Output current when a fault occurred in the second inverter if DB-         |   |

| MOSFET-BDS is used with R-L load7                                                       | 4 |

| Figure 4.21: Output voltage when a fault occurred in the third inverter if DB-          |   |

| MOSFET-BDS is used with resistive load                                                  | 5 |

| Figure 4.22: Output current when a fault occurred in the third inverter if DB-          |   |

| MOSFET-BDS is used with resistive load                                                  | 6 |

| Figure 4.23: Output voltage when a fault occurred in the third inverter if CS-          |   |

| MOSFETs-BDS is used with resistive load7                                                | 6 |

| <b>Figure 4.24 :</b> Output current when a fault occurred in the third inverter if CS-  |   |

| MOSFETs-BDS is used with resistive load7                                                | 7 |

| Figure 4.25: Output voltage when a fault occurred in the third inverter if CS-          |   |

| MOSFETs-BDS is used with R-L load7                                                      | 8 |

| Figure 4.26: Output current when a fault occurred in the third inverter if CS-          |   |

| MOSFETs-BDS is used with R-L load7                                                      | 9 |

| Figure 4.27: Output voltage when a fault occurred in the third inverter if DB-          |   |

|                                                                                         | 9 |

| Figure 4.28: Output current when a fault occurred in the third inverter if DB- |    |

|--------------------------------------------------------------------------------|----|

| MOSFET-BDS is used with R-L load                                               | 80 |

# DESIGN OF FAULT-TOLERANT CASCADED H-BRIDGE MULTILEVEL INVERTER WITH OUTPUT-SIDE TRANSFORMERS USING BIDIRECTIONAL SWITCHES

#### **SUMMARY**

Local electricity production, especially from renewable energy sources, seems to be one of the ideal solutions for the areas away from electrical grid of the cities. The globally increasing energy demand, running short of fossil fuels and researches for finding environment friendly choices strengthen this solution. However, the produced energy must be conditioned for the requirements of the electrical devices so that it can be used. One of the most needed devices for this purpose is the inverter.

Inverters can convert DC voltage/current signal to the AC voltage/current with desired magnitude and frequency. After invention of multilevel inverter, which syntheses the voltage as a staircase waveform, in the early of 80's, a though competition has been started between the multilevel inverters and classic two-level inverters. Multilevel inverters can achieve very low total harmonic distortion (THD) values at low switching frequencies without using any filtering units when compared with classic two-level inverters.

Among the multilevel inverters cascaded H-Bridge inverters comes to the fore by modularity and letting to increase the level of the system easily. However, multilevel inverters use high number of semiconductor elements, which increases the probability of any fault in the circuit, which may cause the whole system stopping for a long time. This is very critical issue for the buildings that have vital importance like hospitals or the industries where faults cost large amounts of money.

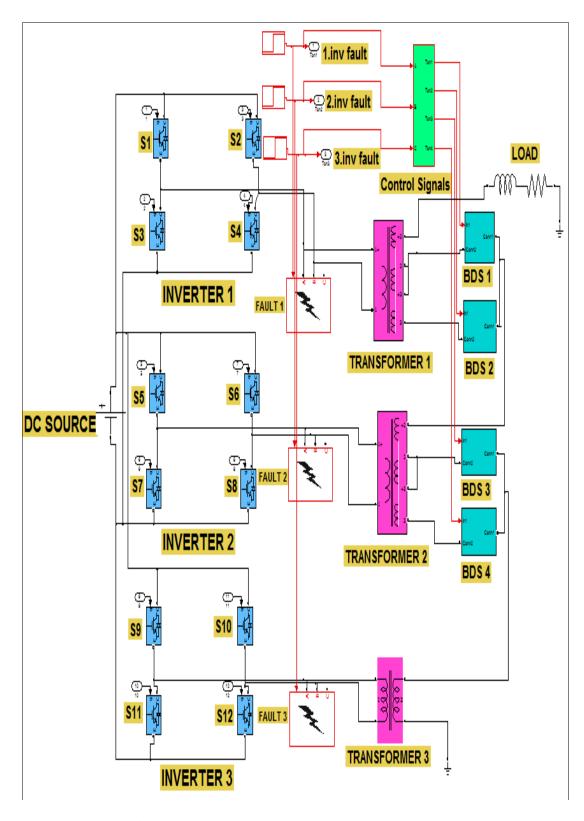

In this thesis, as a candidate solution for the problem mentioned above, a fault-tolerant cascaded H-Bridge quasi-eight-level multilevel inverter with a single DC source and with output side transformers is designed and application of reconfiguration technique is shown. The proposed inverter system can continue working if a fault occurs in one of H-Bridges with a one level decrement in the output voltage in quarter period. The proposed inverter system is designed and tested in MATLAB-SIMULINK simulation environment and comparisons are made by using two types of bi-directional switches, Diode-Bridge (DB) MOSFET and Common-Source (CS) MOSFETs, up to the quality parameters, THD and efficiency, under no-fault and fault conditions with resistive and series connected resistive-inductive loads.

## ÇİFT YÖNLÜ ANAHTARLAR KULLANARAK HATA TOLERANSLI ÇIKIŞ TRAFOLU KASKAT H-KÖPRÜ ÇOK-SEVİYELİ EVİRİCİ TASARIMI

#### ÖZET

Şehir elektrik şebekesinden uzak bölgeler için, özellikle yenilenebilir enerji kaynaklarını kullanarak yerel-yerinde elektrik üretimi ideal çözümlerden biridir. Artan enerji talebi, fosil kaynakların tükenmesi ve çevre dostu seçeneklerin aranması bu çözümü güçlü kılmaktadır. Ayrıca bu çözümün maliyeti ile bu bölgelere yeni iletim hattı kurulmasının maliyeti kıyaslandığında nu çözümün daha avantajlı olduğu söylenebilir. Ancak üretilen bu elektriksel enerjinin evlerde, işyerlerinde kullanılabilmesi için, elektrikli cihazların çalışma koşullarıyla uyumlu olması gerekmektedir. Bu gerekliliği sağlamak için en yaygın kullanılan cihazlardan biri de eviricilerdir.

Eviriciler DC gerilim/akım sinyalini istenilen büyüklük ve frekansta AC gerilim/akım sinyaline çevirebilen güç elektroniği cihazlarıdır. Eviriciler; kare dalga eviriciler, modifiye edilmiş sinüs dalga eviriciler, saf sinüs dalga eviriciler ve çok seviyeli eviriciler olarak 4 temel grup altında toplanabilir.

1980'li yılların başında gerilimi merdiven basamağı şeklinde sentezleyebilen çok seviyeli eviricilerin hayatımıza girmesi ile çok seviyeli eviriciler ve klasik eviriciler arasında amansız bir yarış başlamıştır. Çok seviyeli eviriciler diğer klasik eviriciler ile kıyaslandığında, herhangi bir filtre ünitesi kullanmadan düşük anahtarlama frekanslarında çok düşük toplam harmonik bozunma değerlerine sahip AC sinyaller üretebilirler.

Çok seviyeli eviriciler: diyot-kenetlemeli, kapasite-kenetlemeli ve kaskad H-Köprü eviriciler olarak 3 ana gruba ayrılabilirler Çok-seviyeli eviriciler içinde kaskad H-Köprü eviriciler modüler yapıları ve kolaylıkla çıkış sinyalinin seviyesini artırmaya izin vermeleri ile ön plana çıkmaktadırlar. Ayrıca kaskad H-köprü eviricilerin yenilenebilir enerji kaynakları ile kolaylıkla adapte edilebilmesi bu tip eviricilerin evirici piyasasındaki yerini her geçen gün daha da sağlamlaştırmaktadır. Buna karşın çok-seviyeli eviricilerde fazla sayıda yarı-iletken eleman bulunması bu tip eviricilerin ortak bir dezavantaj olarak karşımıza çıkmakta ve sistemde hata oluşma olasılığını artırmaktadır. Bu durumda tüm sistemin uzun sureli olarak durması sorunu gerçekleşmektedir. Böylesi durma sorunları, özellikle hastane gibi hayati öneme sahip yapılar ve sistemin uzun sureli durması ile kayda değer boyutlarda maddi zarara uğrayabilecek büyük ölçekli işletmeler için kritik ve ciddi bir probleme neden olmaktadır.

Bu tez çalışmasında, belirtilen probleme çözüm seçeneği adayı olarak, hata toleranslı, tek fazlı ve tek DC kaynaklı, çıkış tarafında ikncil sarımları çok-sarımlı trafo tipli, 15 seviyeli kaskad H-Köprü evirici tasarımı ve yeniden yapılandırma tekniğinin uygulaması sunulmaktadır. Tasarlanan çok-seviyeli evirici sistemi, H-Köprü modüllerinden herhangi birinde hata meydana gelmesi durumunda, kontrol

sisteminde uygulanan modifikasyonlar ve trafoların ikincil sarımlarında trafonun dönüşüm oranını ayarlayabilme amacıyla bulunan çift-yönlü anahtarlar sayesinde gerilim seviyesi çeyrek periyotta bir azalarak çalışmasını sürdürebilmektedir. Çift-yönlü anahtar çeşitleri olan Diyot-Köprü MOSFET ve Ortak Kaynaklı MOSFET'ler ayrı ayrı tasarlanan sistemde test edilerek çıkış gerilimi ve çıkış akımı üzerinden kalite parametrelerine göre (toplam harmonik bozunma ve verimlilik) direnç ve seri bağlı direnç-bobin yükleri altında kendi aralarında kıyaslamaları yapılmıştır. Sistem MATLAB-SIMULINK simülasyon ortamında dizayn ve test edilmiştir.

#### 1. INTRODUCTION

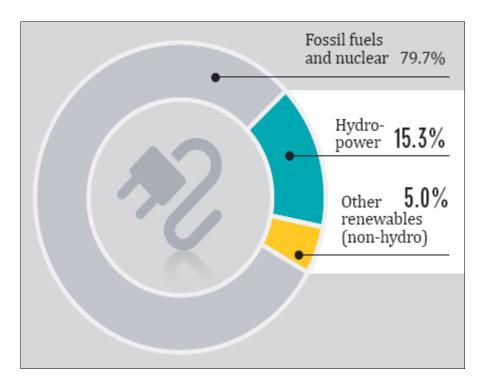

According to last report of International Energy Agency (IEA), the world total electricity generation was 20055 TWh, and the world total electricity consumption was 16759 TWh in 2009. Furthermore, three scenarios are mentioned in IEA's report for the forecasting of the energy vision of the world for the period runs to 2035; The New Policies Scenario, The Current Policies Scenario, and The 450 Scenario. According to projections done in these scenarios, the world electricity demand is varies from 28321 TWh to 31722 TWh [1]. If we consider the statistics for Turkey, total net electricity consumption was 169.4 billion kWh and total net electricity generation was 211.2 billion kWh in 2010 [2]. Moreover, if Turkey's growing economy and industry is considered, the electricity demand will rise continually year after year. In order to meet that demand, new energy resources should be found or existing resources should be used in more intelligent ways. Renewable energy sources (RES) stand as a wise solution for this problem. Renewable energy continued to grow strongly in all end-use sectors, power, heating and cooling, as well as transport, and supplied an estimated 17% of global final energy consumption and has a share of 20.3%, including hydro-power, in world total electricity generation in 2011, as shown in Figure 1.1. As in previous years, about half of the new electricity capacity installed worldwide was renewable based [3].

It is estimated that 2 billion of people are living without connection to electricity grid and this amount is increasing [4]. The electricity produced from RES can be integrated to distribution grid system or as an alternative way, RES can be used as stand-alone in remote areas from integrated-grid system due to environmental and economical reasons. This is especially valid for rarely populated areas where the cost for central supply is too high due to long power transfer distances and relatively low power demand. For example, electricity supply for the houses in European Alps or for hotels in Uludağ (Turkey) can be provided by the stand alone renewable energy sources (SARES).

**Figure 1.1:** Share of resources of the in electricity production [3].

The electricity generated from RES must be compatible with grid system or satisfy the necessities of stand-alone systems. For the particular case of SARES, it is of common sense that it should be capable of supplying alternating current (AC) electricity, thus providing compatibility with standard appliances that are cheap and widely available [5]. In Turkey, AC electricity grid needs  $\pm 10\%$  of  $230V_{rms}$  AC voltage and 50 Hz frequency. In order to satisfy these needs some power conversion systems are required.

The adoption of AC power has created a trend where most devices adapt AC power from an outlet into DC power for use by the device. However, AC power is not always available and the need for mobility and simplicity has given batteries an advantage in portable power. Thus, for portable AC power, inverters are needed. Inverters take a DC voltage from a battery or a solar panel as input, and convert it into an AC voltage output [6].

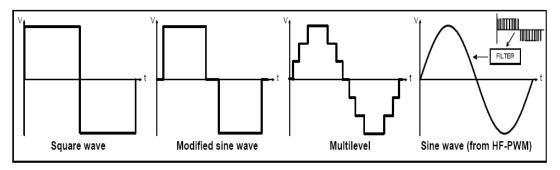

Inverters can be classified in four groups according to their output waveform; square-wave, modified square-wave (also called square wave or modified sine wave), pure sine-wave (synthesized by high frequency pulse width modulation-PWM) and multilevel (or multi-step). In Figure 1.2 waveforms for each category are shown [7].

**Figure 1.2 :** Waveforms for different inverter types [7].

Square wave and modified sine wave inverters do not take much attention in because of their very poor quality waveforms but they are still available in market for practical applications. Multilevel and pure sine wave inverters are focused by the researches and all works are being done about them. In recent years there is a though competition between classical two level inverters and multilevel inverters. Multilevel converters show several advantages over conventional two-level converters. Some of the most attractive features of multilevel converters are briefly summarized as follows in [8] and [9]:

- Staircase waveform quality: Multilevel converters generate output voltages with much lower harmonic content and reduce the dv/dt stresses. Therefore, electromagnetic compatibility (EMC) problems can be reduced.

- Common-mode (CM) Voltage: Multilevel converters produce smaller CM voltage. The stress in the bearings of a motor connected to a multilevel motor drive, for example, can be therefore reduced. Furthermore, using advanced modulation strategies, CM voltage can be eliminated.

- **Input current**: Multilevel converters can draw input current with low distortion.

- **Switching frequency**: Multilevel converters can operate at both fundamental switching frequency and high switching frequency PWM. Therefore, through lower switching frequency, lower switching losses and higher efficiency can be achieved.

However, multilevel converters have some disadvantages. For these converters, great number of power semiconductors needed. This makes the overall system more complex, increases the conduction losses and probability of fault.

Reliability is a big challenge for the inverters using multilevel technology, due to used high number of semiconductor elements. The increasing number of switching elements causes the probability switching errors to rise. These switching errors may cause the whole system to shut down for a long time. Besides these errors, also short-circuit fault conditions may occur within the network system. It is wanted that the inverters simultaneously detect this error and keep the desired level of output voltage so that the energy flow continues. These issues become even more important in the buildings of vital importance (hospitals etc.) or in the institutions where these collapses cost large amounts of money. As a result, the industry leans to fault analysis and reconfiguration strategies so that the collapse time of such systems is shortened.

Conventional protection systems generally use passive devices such as fuse, over current relay and breakers, which just disconnect the system from the energy source. Fault analysis studies focus on analyzing the fault modes and providing operation methods for these modes.

The main objective of this thesis is to design and simulate a multilevel inverter which is based on the single-phase, single DC source cascaded H-Bridge multiple transformer inverter topology with bi-directional switches, and to improve the reliability of this multilevel inverter. The fault tolerant ability is resulted from the inherent redundant nature of the multi-switching-states topology and control signals modification and the performance of a reconfiguration technique that allows a cascaded H-bridge inverter to keep working even with a faulty bridge. The theory of fault-tolerant algorithm and reconfiguration is thoroughly investigated and its performance is verified by simulations in MATLAB-SIMULINK environment.

#### 1.1 Thesis Structure

In Chapter 2, the state of the art of the multilevel inverters are presented and advantages and disadvantages of all multilevel inverter topologies are discussed briefly. Moreover, different types of bi-directional switches are shown and a short review of fault-tolerant and reconfiguration systems are done.

In Chapter 3, the proposed inverter scheme will be introduced in detail. The main working principle and control system explained briefly. Also, design parameters of

used semiconductor devices, transformers and bi-directional switches are shown. Fault management and reconfiguration techniques are explained in depth.

In Chapter 4, the simulation results are presented according to the different types of bi-directional switches and fault conditions. The designed systems performance parameters Total Harmonic Distortion (THD), efficiency, etc. Results are shown, and comments and comparisons are made. In the last chapter, a summary of works which have been done in this thesis are presented; finally, future works that can be followed as a progression of this thesis are mentioned.

#### 2. THEORETICAL BACKGROUND OF MULTILEVEL INVERTERS

In this chapter, existing multilevel inverter (MLI) topologies in the market are explained and their differences, advantages and disadvantages are exhibited. Besides, modulation techniques of the MLIs, bidirectional swtiches' working principles and their types are presented. Finally, the fault tolerant MLI strategies are introduced.

### 2.1 Multilevel Inverter Topologies

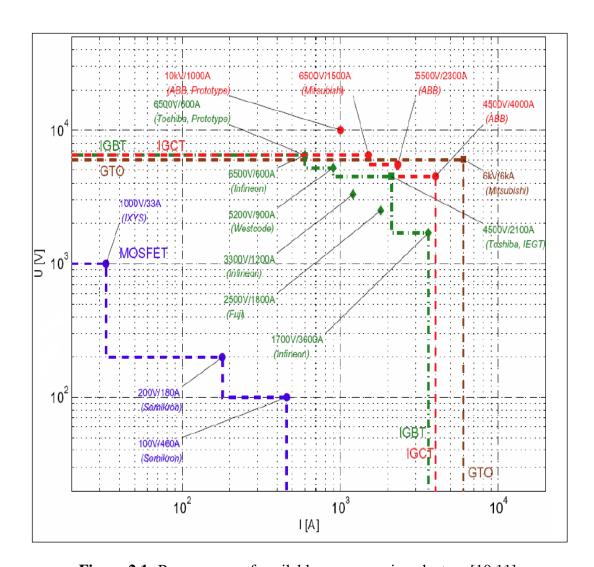

Fundamentally, a multilevel converter is able to achieve higher power by using a series of power switches with several lower voltage DC sources or with single DC source to perform the power conversion by synthesizing a staircase voltage waveform. According to the inverter topology requirements, for example; power ratings and switching frequencies, appropriate power switches must be chosen. Power ranges for the power semiconductors in the market are given in Figure 2.1 [10,11].

Multilevel inverters use medium-power semiconductors as switches. While designing inverter circuitry, a choice had to be made between the two main types of switches used in power electronics. One is the power MOSFET, which is much like a standard MOSFET, but designed to handle relatively large voltages and currents. The other is the insulated gate bipolar transistor, or IGBT. Each has its advantages, and there is a high degree of overlap in the specifications of the two [12].

IGBTs tend to be used in very high voltage applications, nearly always above 200V, and generally above 600V. They do not have the high frequency switching capability of MOSFETs, and used at frequencies lower than 20 kHz. They can handle high currents, are able to output greater than 5 kW, and have very good thermal operating ability, being able to operate properly above 100 Celsius. One of the major disadvantages of IGBTs is their unavoidable current tail when they turn off. Essentially, when the IGBT turns off, the current of the gate transistor cannot dissipate immediately, which causes a loss of power each time this occurs [12].

**Figure 2.1:** Power range of available power semiconductors [10,11].

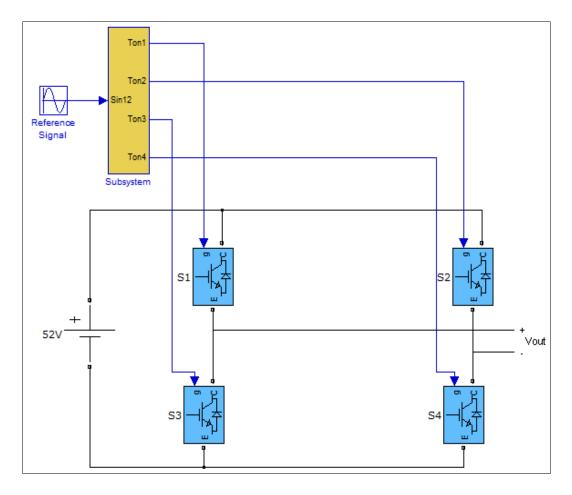

Power MOSFETS have a much higher switching frequency capability than do IGBTs, and can be switched at frequencies higher than 200 kHz. They do not have as much capability for high voltage and high current applications, and tend to be used at voltages lower than 250V and less than 500W. MOSFETs do not have current tail power losses, which makes them more efficient than IGBTs. Both MOSFETs and IGBTs have power losses due to the ramp up and ramp down of the voltage when turning on and off (dV/dt losses). Unlike IGBTs, MOSFETs have body diode [12]. In the proposed inverter topology, MOSFETs were used as switches.

Multilevel converters are a viable solution to increase the power with a relatively low stress on the components and with simple control systems. Moreover, multilevel converters present several other advantages. First of all, multilevel converters generate better output waveforms than the standard converters. Then, multilevel converter can increase the power quality due to the great number of levels of the

output voltage, by this way; the AC side filter can be reduced. Furthermore, multilevel converters can operate with a lower switching frequency sharing the whole voltage in small steps, so the electromagnetic emissions generated by them are weaker, to comply with the standards [13].

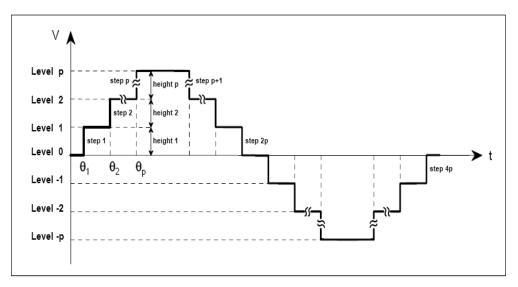

As mentioned before, multilevel inverters produces staircase voltage form. The generalized staircase waveform is shown in Figure 2.2. [7].

**Figure 2.2:** Generalized staircase waveform [7].

In this thesis following notations will be used to specify the properties of inverters;

P : The number of steps in quarter-cycle

$2 \times p+1$  :Number of levels of an inverter

$4 \times p$  :Number of steps of an inverter

There are lots of multilevel inverter topology in the literature tested and installed. Multilevel inverters have been taking place in market about 40 years. Basicly, there are three fundamental multilevel topologies; diode clamped (NPC), flying capacitor (FC), and cascaded H-Bridge (CHB). Other topologies are the variations of these topologies. They can be classified as:

- Neutral point clamped multilevel inverter (NPC)

- Capacitor-clamped multilevel inverter (FC)

- Cascaded H-Bridge multilevel inverter (CHB)

- Multiple source topology

- Multi-winding transformer topology (MTT)

- Modular topology

- Multiple-transformer topology

### 2.1.1 Neutral point clamped MLI

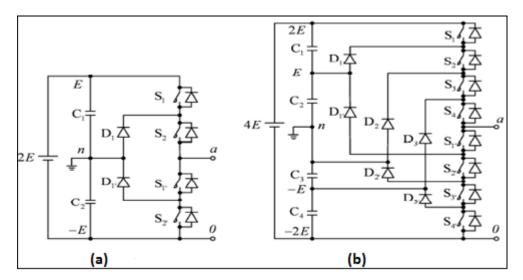

This type of multilevel inverter topology was proposed by Nabae et al. in 1981 which is shown in Figure 2.3-a [14]. In this circuit, the DC-bus voltage is split into three levels by two series-connected bulk capacitors, C1 and C2. The middle point of the two capacitors, n, can be defined as the neutral point. The output voltage  $V_{an}$  has three states: E, 0 and E. For voltage level E, switches S1 and S2 need to be turned on; for E, switches S1' and S2' need to be turned on; and for the 0 level, S2 and S2' need to be turned on like shown in Table 2.1. [15]. It was the first widely used multilevel inverter in the market and still popular in industry applications. Number of levels can be increased by using the same concept of diode-clamped voltage levels as shown in Figure 2.3.b

**Figure 2.3 :** Diode-clamped mulilevel inverter circuit topologies: (a)Three-level (b)Five-level [14].

**Table 2.1:** Switches states and the output voltage for three-level NPC [15].

| Output Voltage               | Switches' States |         |       |       |

|------------------------------|------------------|---------|-------|-------|

| $(\mathbf{V}_{\mathbf{an}})$ | $S_1$            | $S_1$ , | $S_2$ | $S_2$ |

| <b>E</b> ( <b>V</b> )        | 1                | 0       | 1     | 0     |

| -E (V)                       | 0                | 1       | 0     | 1     |

| 0 (V)                        | 0                | 0       | 1     | 1     |

Advantages of NPC multilevel inverters are:

- A large number of levels yield a small harmonic distortion.

- All phases share the same DC bus.

- Reactive power flow can be controlled.

- Control is simple [16].

The disadvantages are the followings:

- Different voltage ratings for clamping diodes are required.

- Real power flow is difficult because of the capacitors' imbalance.

- Different current ratings for switches are required due to their conduction duty cycle [16].

### 2.1.2 Capacitor-clamped MLI

The capacitor-clamped multilevel converter or flying-capacitor (FC) converter, is similar to the diode-clamped topology, which is shown in Figure 2.4. However, the capacitor-clamped multilevel topology allows more flexibility in waveform synthesis and balancing voltage across the clamped capacitors [16]. The inverter in Figure 2.4.(a) provides a three level output across a and n, i.e.  $V_{an} = E$ , 0, or -E. For the voltage level E, switches S1 and S2 need to be turned on; for -E, switches S1' and S2' need to be turned on; and for the 0 level, either pair (S1, S1') or (S2, S2') needs to be turned on like shown in Table 2.2. Clamping capacitor C1 is charged when S1 and S1' are turned on, and is discharged when S2 and S2' are turned on. The charge of C1 can be balanced by a proper selection of the 0-level switch combinations [15]. Number of levels can be increased with the same idea as in NPC shown in Figure 2.4(b).

The advantages of the capacitor-clamped multilevel converter are:

- When the number of levels is increased that allows the capacitors extra energy during long discharge transient.

- Flexible switch redundancy for balancing different voltage levels

- A large number of levels yields a small harmonic distortion.

- Active and reactive power flow can be controlled [16].

**Figure 2.4 :** FC multilevel inverter circuit topologies (a)Three-level (b)Five-level [16].

**Table 2.2**: Switches states and the output voltage for three-level FC [15].

| Output Voltage (V.)               | Switches' States |         |       |         |

|-----------------------------------|------------------|---------|-------|---------|

| Output Voltage (V <sub>an</sub> ) | $S_1$            | $S_1$ , | $S_2$ | $S_2$ , |

| <b>E</b> ( <b>V</b> )             | 1                | 0       | 1     | 0       |

| -E (V)                            | 0                | 1       | 0     | 1       |

| 0 (V)                             | 1                | 1       | 0     | 0       |

| 0 (V)                             | 0                | 0       | 1     | 1       |

The disadvantages are:

- Large number of capacitors is bulky and more expensive than the clamping diodes used in the diode-clamped multilevel converter.

- Control for maintaining the capacitors' voltage balance is complicated.

- Poor switching utilization and efficiency for real power transmission [16].

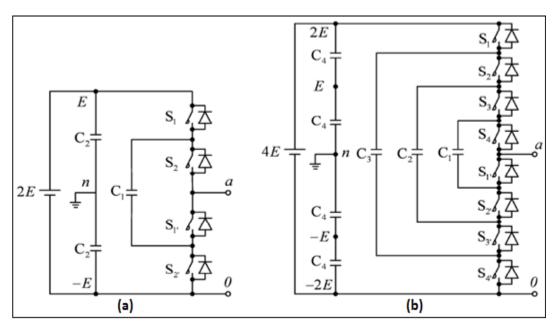

# 2.1.3 Cascaded H-Bridge MLI

Cascaded H-Bridge(CHB) multilevel inverter was first proposed in 1975 by Baker and Bannister [17]. The CHB inverter produces a sinusoidal voltage from different sources of direct current. The inverter is based on the fullbridge(H-Bridge) inverter (cell), that allows increase the number of levels 2m +1 where m is the number of cells that build the inverter [18]. This type of inverter avoids the use of interlocking diodes, capacitors voltage balancing float also a low THD can be obtained by controlling the gate trigger of the different voltage levels, this topology is divided into two types:

- Symmetric CHB inverter

- Asymmetric CHB inverter [19].

Figure 2.5: Cascaded H-Bridge multilevel inverter with seperate DC sources [19].

In the CHB symmetric the power sources in each cell are of same value: If we consider topology in Figure 2.5, when

$$V_{DC1} = V_{DC2} = V_{DC3} = E (2.1)$$

Each H-bridge cell can generate three output voltage: E,-E or 0 according to the switch states given in Table 2.3. In this table, switch states and output voltage values are given only for the first H-Bridge cell. Moreover, for other H-Bridge cells this idea is identical. The output voltage  $V_{an}$  is equal to the sum of the all of H-Bridges' output voltages. By the way, the output  $V_{an}$  can take values as 3E, 2E, E, 0, -E, -2E, -3E, then we have 7-level CHB symetric. The output voltage level can be increased by adding more H-bridge cells in cascade.

$$V_{an} = V_{H1} + V_{H2} + V_{H3} (2.2)$$

**Table 2.3:** Switch-Sates for the first H-Bridge cell [19].

| Output                | Switches' States |          |                 |                 |

|-----------------------|------------------|----------|-----------------|-----------------|

| Voltage (Van)         | $S_{11}$         | $S_{12}$ | S <sub>13</sub> | S <sub>14</sub> |

| <b>E</b> ( <b>V</b> ) | 1                | 0        | 1               | 0               |

| -E (V)                | 0                | 1        | 0               | 1               |

| 0 (V)                 | 1                | 1        | 0               | 0               |

| 0 (V)                 | 0                | 0        | 1               | 1               |

## Advantages of this topology are:

- No need for clamping diodes and clamping capacitors.

- Required a small number of components compared to diode-clamped and capacitor-clamped multilevel inverters.

- By increasing the number of levels, lower harmonic distortion can be achieved [20].

### A disadvantage is that:

• The number of independent DC sources required increases with the number of desired levels [20].

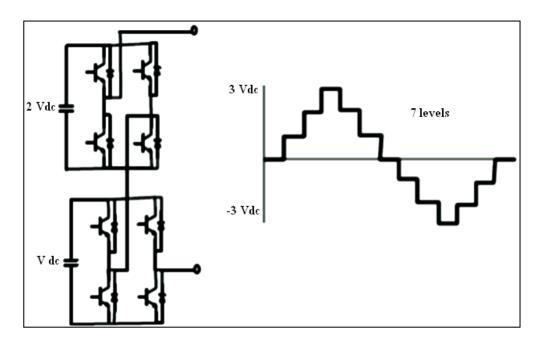

The CHB asymmetric get more levels in the output voltage with the same number of cells that integrates a CHB symmetric. The difference in levels of output voltage is mainly due to use of different supply voltages in the cells of the inverter and the use of appropriate modulation technique. The advantage of using the CHB asymmetric is that it has less conduction losses favor the results of tension the inverter the output. The main disadvantage is that some levels the voltage the output is achieved by the sum of voltages of opposite signs, leading, higher switching losses [21]. Furthermore, the CHB asymmetric is divided in two classes:

- CHB asymmetric exponent 2

- CHB asymmetric exponent 3

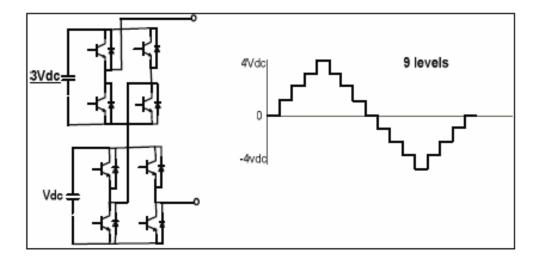

The CHB asymmetric exponent 2 is shown in Figure 2.6, the levels of input voltage of each cell are  $V_{dc}$  and  $2V_{dc}$  (exponent 2). In this configuration  $2^{m+1}$ -1 voltage levels can be achived at the load voltage where m is the number of H-Bridge cells [22].

The CMLI asymmetric exponent 3 is shown in Figure 2.7, the levels of input voltage of each cell are Vdc and 3Vdc (exponent 3) [22]. In this topology, the voltage delivered to the output has 3<sup>m</sup> voltage levels where m is the number of H-Bridge cells.

Figure 2.6: CHB asymmetric exponent 2 [22].

Figure 2.7: CHB asymmetric exponent 3 [22].

In general the advantages of the CHB asymmetric are:

- It requires fewer components because the same amount of cells and more symmetric levels are achieved.

- A greater number of levels, lower harmonic distortion.

- The active and reactive power flow can be controlled [22].

# A disadvantage is that:

• As the number of levels increases, the converter control becomes more complex as more levels must be achieved with less number of cells [22].

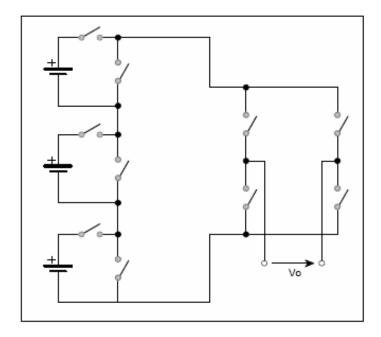

# 2.1.4 Multiple source topology

This topology uses isolated DC sources produce a stepped waveform by the aid of just one H-bridge inverter, shown in Figure 2.8. [23]. This topology is one of the most efficient multilevel inverter in the market. It has been tested in RES applications more than 15 years and proved that it is efficient, robust and reliable [24]. However, this configuration requires seperate DC sources and does not provide input-output isolation.

**Figure 2.8:** Multiple source topology [23].

# 2.1.5 Multi-winding transformer topology

It is a variation of multiple source topology. An example of three-winding topology is shown in Figure 2.9.

Advantages of this topology:

- Just a single source is required

- Input-output isolation achived by the use of transformer.

- It uses just one transformer so it is efficient.

# Disadvantage is:

• Lots of switches in the output side [7].

**Figure 2.9 :** Multi-winding transformer topology [7].

# 2.1.6 Modular topology

Figure 2.10 shows the eight-module modular topology. This topology is generally proposed for high power applications [25,26]. Each module, which is a two terminal device, is modelled by two switches and one local DC capacitor. The disadvantage of this topology every module's capacitor needs a voltage measurement circuit and it does not support loads with DC current component [7].

Figure 2.10: Modular topology [25,26].

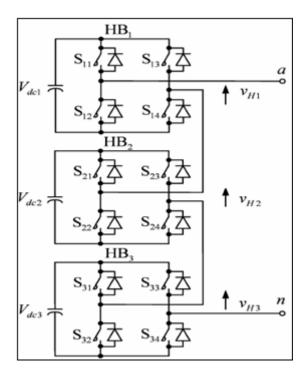

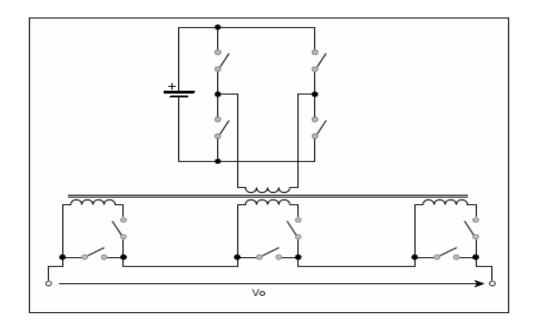

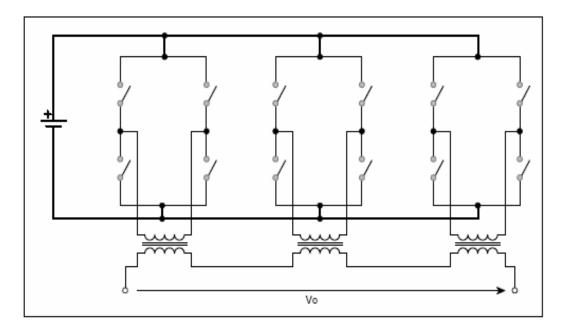

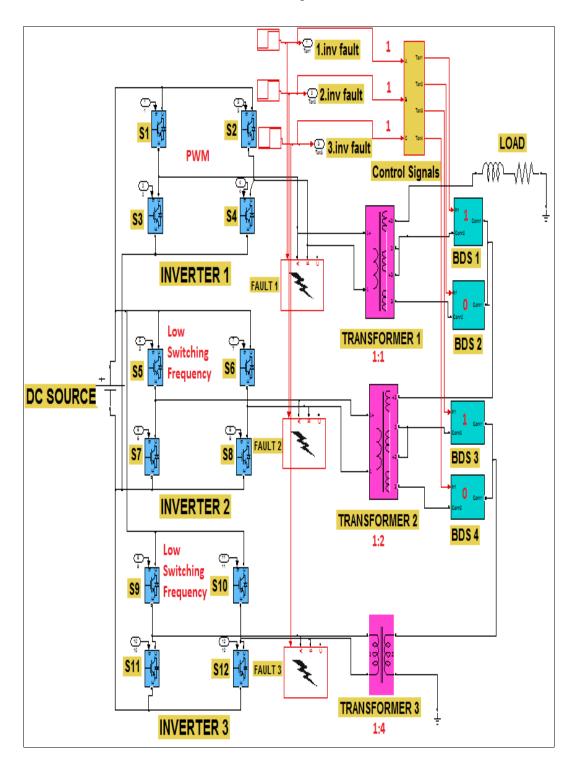

## 2.1.7 Multiple-transformer topology

This topology is a variation of cascaded multilevel inverter. In this configuration each H-Bridge module has a isolation transformer at the output side. Every secondary of transformer is connected in series to pile of output level up. There is some inverters in the market based on this topology [27,28].

The turn ratios of the transformers can be exponent 2 or exponent 3. According to these turn ratios of the transformers the level of the inverter is determined. When we consider the topology shown in Figure 2.11;

If we select the turns-ratios of the transformers are as exponent 2, we will have turns-ratios as followings; the first transformer's  $1:2^0$ , the second transformer's  $1:2^1$ , and for the third transformer's  $2^2$ . As a result at the output stage will have 15-level (7 level positive,7 level negative and level'0'). The formula for determining the voltage levels in this system is  $2^{n+1}$ -1 where n is the number of H-Bridge cells.

If we select the turn-ratios of the transformers are as exponent 3, we will have turnsratios at first transformer is  $1:3^0$ , at second transformer  $1:3^1$ , and at third transformer  $3^2$ . As a result, at the output stage will have 27-level (13 level positive,13 level negative and level'0'). The number of the levels in this transformer can be easily found by the formula  $3^n$ .

Figure 2.11: Cascaded H-Bridges with isolation transformers [7].

Advantages of this topology:

- This topology requires only one DC source.

- It is robust and reliable.

- The leakage reactance of transformers act like series active filter, so

THD is reduced.

- The transformers provide a galvanic isolation between input and output.

- It maintains the advantages of the cascade multilevel inverter:

- o Low dV/dt in the devices.

- High definition of the output voltage and low harmonic content.

- It uses a smaller quantity of semiconductors that the other two topologies of multilevel inverters [7].

The only disadvantage of this topology is it requires some low frequency transformers.

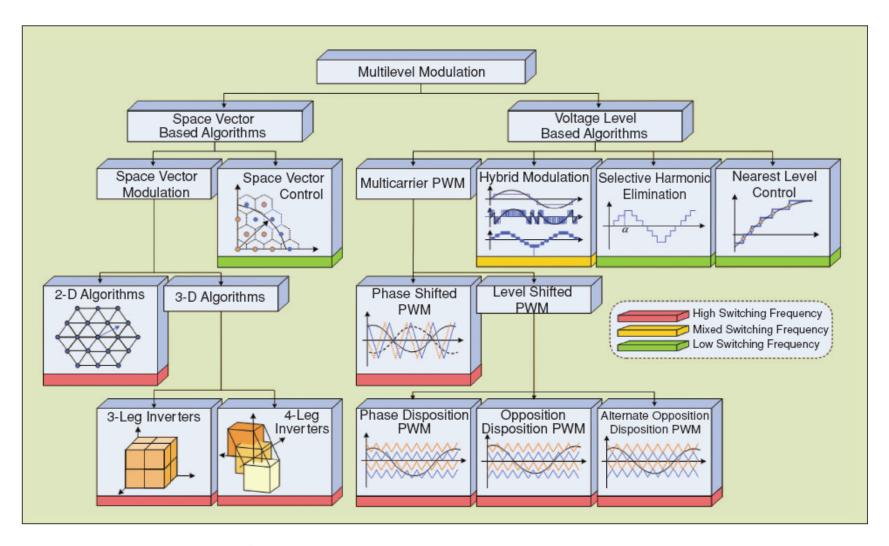

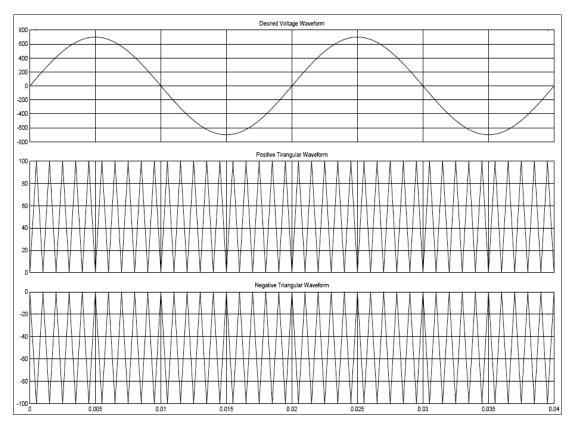

### 2.2 Modulation Techniques for MLIs

The modulation algorithm used to drive the multi-level converter give the voltage level required for each leg; the translation in the proper configuration of switches is done by other algorithms which can be hardware or software implemented. It is generally accepted that the performance of an inverter, with any switching strategies, can be related to the harmonic contents of its output voltage [29]. Power electronics researchers have always studied many novel control techniques to reduce harmonics in such waveforms. Up-to-date, there are many techniques, which are applied to inverter topologies. A classification of the modulation methods for multilevel inverters is presented in Figure 2.12. The modulation algorithms are divided into two main groups depending on the domain in which they operate: the state-space vector domain, in which the operating principle is based on the voltage vector generation, and the time domain, in which the method is based on the voltage level generation over a time frame [30]. The aim of redundant configurations which is, to improve the switching pattern, to balance the current flowing through the switches, must be defined for the application. In general, low switching frequency methods are preferred for high-power applications due to the necessary reduction of switching losses, while the better output power quality and higher bandwidth of high switching frequency algorithms are more suitable for high dynamics applications [31,32,33].

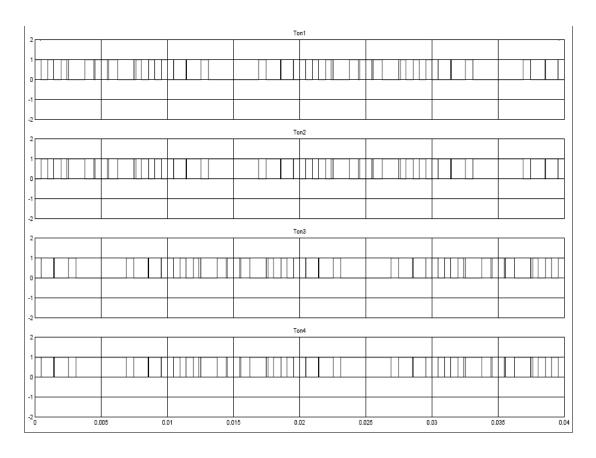

#### 2.2.1 MLI PWM strategies

Classic PWM techniques have been successfully adopted to multilevel inverter topologies by using multiple carries to control each power switch of the inverter so they are known as multicarrier PWM methods.

For multicell topologies, FC and CHB, each carrier can be associated to a particular power cell to be modulated independently using sinusoidal bipolar PWM and unipolar PWM, respectively, providing an even power distribution among the cells. Therefore, this method is known as phase shifted PWM (PS-PWM). This method naturally balances the capacitor voltages for the FC and also mitigates input current harmonics for the CHB.

The carriers can also be arranged with shifts in amplitude relating each carrier with each possible output voltage level generated by the inverter. This strategy is known as level shifted PWM (LS-PWM), and depending on the disposition of the carriers, they can be in phase disposition (PD-PWM), phase opposition disposition (POD-PWM), and alternate phase opposition disposition (APOD-PWM) [34]. LS-PWM methods can be implemented for any multilevel topology; however, they are more suited for the NPC, since each carrier signal can be easily related to each power semiconductor. Particularly, LS-PWM methods are not very attractive for CHB inverters, since the vertical shifts relate each carrier and output level to a particular cell, producing an uneven power distribution among the cells. This power unbalance disables the input current harmonic mitigation that can be achieved with the multipulse input isolation transformer, reducing the power quality.

Finally, the hybrid modulation is in part a PWM-based method that is specially conceived for the CHB with unequal dc sources and for the CHB topologies with transformers [30]. Moreover, this idea gives significant results for multiple-transformer topology. The basic idea is to take advantage of the different power rates among the cells of the converters to reduce switching losses and improve the inverter efficiency. This is achieved by controlling the high-power cells at a fundamental switching frequency by turning on and off each switch of each cell only one time per

cycle, while the low-power cell is controlled using unipolar PWM. In this thesis, hybrid modulation are used and will be discussed detailly in next chapter.

#### 2.2.2 Space vector modulation techniques

Space vector modulation (SVM) is a technique where the reference voltage is represented as a reference vector to be generated by the power converter. The SVM technique generates the voltage reference vector as a linear combination of the state vectors obtaining an averaged output voltage equal to the reference over one switching period [35].

### 2.2.3 Other MLI modulation algorithms

Although SVM and multicarrier PWM are widely accepted and have reached a certain maturity for multilevel applications, other algorithms have been developed to satisfy particular needs of different applications.

Selective harmonic elimination (SHE), for example, has been extended to the multilevel case for high-power applications due to the strong reduction in the switching losses [36,37,38]. However, SHE algorithms are very limited to openloop or low-bandwidth applications, since the switching angles are computed offline and stored in tables, which are then interpolated according to the operating conditions. In addition, SHE based methods become very complex to design and implement for converters with a high number of levels (above five), due to the increase of switching angles, hence equations, that need to be solved. In this case, other low switching frequency methods are more suitable. The time-domain version of SVC is the nearest level control (NLC), which in essence is the same principle but considering the closest voltage level that can be generated by the inverter instead of the closest vector [39]. As mentioned above, not all of the modulation schemes are suitable for each topology; moreover, some algorithms are not applicable to some converters. Table 2.4 summarizes the compatibility between the modulation methods and the multilevel topologies.

Selecting the best inverter topology for the application can differ according to system requirements. As a particular case for SARES, the most important performance parameters are reliability, surge power capacity and efficiency. Multilevel inverters are presented in recent works that they can successfully satisfy these parameters [7].

**Figure 2.12 :** Multilevel inverter modulation classification [30].

Depending on the application, the multilevel converter topology can be chosen according to some factors as shown in Table 2.5.

**Table 2.4 :** Applicability of modulation methods to multilevel topologies [30]. ✓ Applicable X Not Applicable – Applicable/Not Recommended

| <b>Modulation Methods</b> | Topologies |          |     |

|---------------------------|------------|----------|-----|

| Wiodulation Wethous       | NPC        | FC       | СНВ |

| SVM                       | ✓          | ✓        | ✓   |

| LS-PWM                    | ✓          | ✓        | -   |

| PS-PWM                    | X          | ✓        | ✓   |

| Hybrid Modulation         | X          | X        | ✓   |

| SHE                       | ✓          | ✓        | ✓   |

| SVC                       | -          | ✓        | ✓   |

| NLC                       | -          | <b>√</b> | ✓   |

**Table 2.5 :** Comparison of multilevel inverter topologies depending on implementation factors [30].

| Implementation                       | Topologies           |                       |                     |                                      |

|--------------------------------------|----------------------|-----------------------|---------------------|--------------------------------------|

| Factors                              | NPC                  | FC                    | СНВ                 | MTT                                  |

| Specific<br>Requirements             | Clamping diodes      | Additional capacitors | Isolated DC sources | Low<br>frequency<br>transform<br>ers |

| Modularity                           | Low                  | Low                   | High                | High                                 |

| Design and implementation complexity | Low                  | Medium                | High                | High                                 |

| Control concerns                     | Voltage<br>balancing | Voltage<br>setup      | Power<br>sharing    | Power<br>sharing                     |

| Fault tolerance                      | Difficult            | Easy                  | Easy                | Easy                                 |

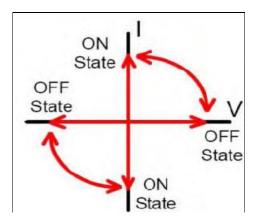

# 2.3 Bi-directional Switch Technology

By definition a Bi-Directional Switch (BDS), in literature also named bilateral switch or AC-switch or 4Q-switch (Q stands for quadrant), has to be capable of conducting

currents and blocking voltages of both polarities, depending on control actual signal as shown in Figure 2.13 [40].

Since no single device is available as a bidirectional self commutated switch, a bidirectional switch is synthesized from the combination of commonly used solid state devices. In order to build a composite BDS with the capability of conduction in both directions, it is necessary to connect two discrete devices in anti-serial association of two unidirectional voltage devices or in anti-parallel association of two unidirectional current devices [41].

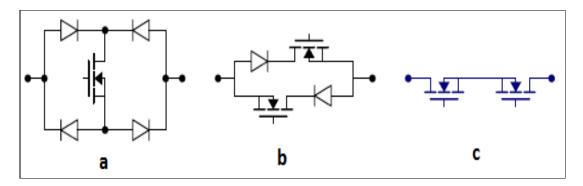

**Figure 2.13 :** Device working quadrants [40].

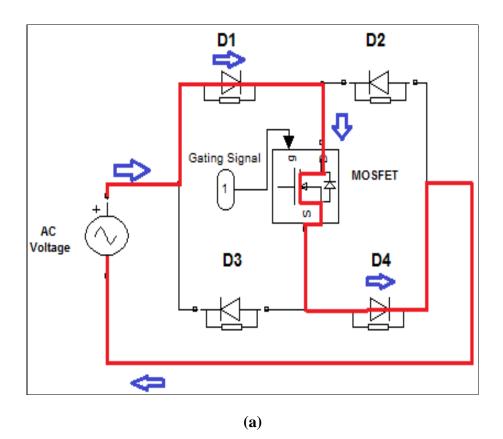

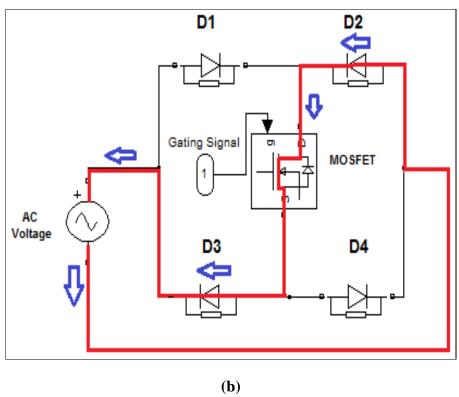

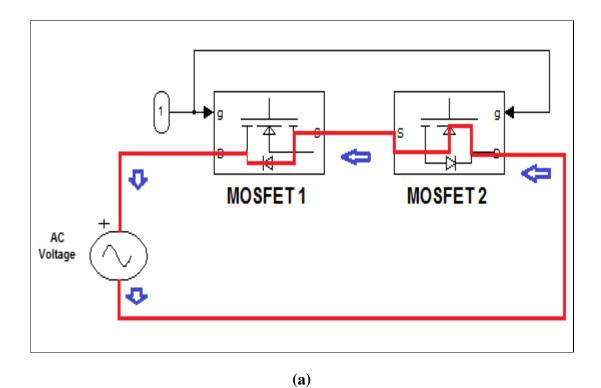

There are lots of BDS configurations in the literature using different semiconductors like IGBTs, IGTCs, BJTs and MOSFETs. However, the configurations with MOSFETs are mentioned in this work. There are different bi-directional switch configurations by MOSFETs in the market shown in Figure 2.14.

**Figure 2.14 :** Different bi-directional switch implementations by using MOSFETs [7].

The switch shown in Figure 2.13.a is easy to control. Only one unidirectional controllable switch (MOSFET) is used in a four-diode bridge. However, its voltage drop is high. It is equal to the sum of the voltage drops of two diodes and the

transistor. This arrangement is expensive if high voltage fast recovery diodes are to be used. The unique control makes this switch a real bidirectional switch [7].

The second proposed configuration of bi-directional switch was the anti-parallel arrangement of two active devices, MOSFETs in Fig.2.13.b, with series diode. The two diodes are used to provide the reverse voltage blocking capability. This configuration reduces the voltage drop but needs two MOSFETs. It is the most expensive configuration. Furthermore, compared to the diode bridge switch, this solution has also the advantage of lower conduction losses, since only two devices are conducting at any given time [7].

With MOS-transistors, the switch of Figure 2.13.c is the simplest one. It needs only two components because the diodes are part of the transistors. This configuration provides lower losses when compared to previously mentioned configurations because of the low on resistance of modern MOSFETs and its bi-directional channel conduction capability. When both MOSFETs are on, it can be modelled as a two times Ron resistance of a single MOSFET [7].

## **2.4 Fault-Tolerant MLI Strategies**

Reliability is an important issue in cascaded H-bridge converters and multitransformer topologies because they use a high number of power semiconductors. A faulty power semiconductor in any of H-bridges can potentially lead to expensive downtime and great losses on the consumer side. Also any failure of the semiconductors in H-Bridges break the balance between the positive and negative parts of the output voltage that quickly increases the harmonic distortion. It is important to maintain normal operation under fault conditions because failed operation of a inverter could cause tremendous losses for consumers, especially when the inverter is feeding critical loads. Cascaded multilevel inverters have a character that each unit can work independently. After a unit stops working because of fault, if we can make the other units continue working with the output of the system unchanged or changed in acceptable limits, the reliability of the system will be improved greatly. [42]. With the fault-tolerant control strategies and reconfiguration techniques, operation can continue with the undamaged cells; thus increasing the reliability of the system. The key issue when designing a fault-tolerant system is to improve system reliability [43].

For a fault-tolerant system, the basic goal is to continue operation in the event of a power failure. There are two types of fault-tolerant method, one is hardware redundant, and another is to cut the fault unit away [44].

The hardware redundant is to design surplus unit in the systematic design. In [43], the proposed strategy for the fault-tolerant system is redundancy. In CHB inverters, all H-Bridge cells are identical so the redundacy strategy is easily applied by adding an H-Bridge cell as a back-up to maintain operation when one of H-Bridge cells fails. When the trouble appears, replace the trouble unit with the surplus unit, in order to make the system continue working. Dependability of this method is relatively high, but it needs at least one unit unused as redundant, which causes the ratio of the systematic utilization low. When the trouble appears, replace the trouble unit with the surplus unit, in order to make the system continue working. Dependability of this method is relatively high, but it needs at least one unit unused as redundant, which causes the ratio of the systematic utilization low.

Cutting the failure unit away takes the advantage of the cascaded inverter's property that is each unit of the inverter can work independently, so after cutting the fault unit away, the rest can continue to work. If taking this method, to make the output of the three phases balance, each healthy phase should cut one unit, too. As the result, the value of output voltage is reduced and the machine system must run at a lower speed at this moment [45]. However for the single-phase systems this problem does not exist.

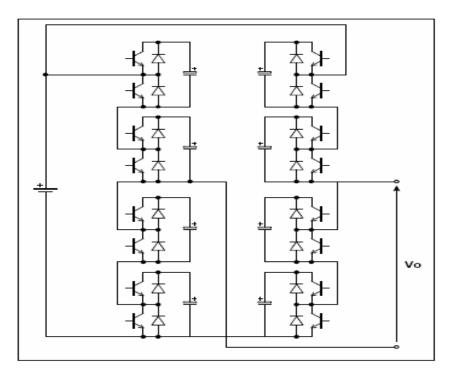

As an alternative method to these methodes mentioned above, B.Wang and et al. proposed a reconfiguration method with bi-directional swtiches for 3-phase systems. Once a fault is detected in any of the IGBTs of any H-bridge, the control is capable to reconfigure the hardware keeping the higher power bridges in operation. In this way, the faulty phase can continue working at the same voltage level by adjusting its gating signals. This method is based on the multiple-transformers topology. The design consists of three H-Bridge cells and with output transformers for each cell. The turn ratios of the transformers scaled in power of three. One of the transformers in the topology is multi-winding transformer with bi-directional switches which are used between different windings of the transformer. When a fault occurs, by the aid of bi-directional switches, the turn-ratio of the transformer changes and the desirable voltage level is achived [42].

#### 2.5 Literature Review

In this subdivision, literature review of the multilevel inverter types, multilevel inverter modulation techniques, bi-directional switch types and fault tolerant designs of multilevel inverters are done.

Generally, multilevel inverter applications can be classified in three groups within the semi-conductor technologies framework; these are diode-clamped inverters, capacitor clamped inverters and multi-cascade H-bridge inverters [46,47,48,49].

There are some review studies about multilevel inverters and modulation techniques in the literature. J.Rodriguez presented the most important topologies like diodeclamped inverter (neutral-point clamped), capacitor-clamped (flying capacitor), and cascaded multicell with separate dc sources. Emerging topologies like asymmetric hybrid cells and soft-switched multilevel inverters are also discussed. Their work presents relevant control and modulation methods developed for this family of converters: multilevel sinusoidal pulsewidth modulation, multilevel selective harmonic elimination, and space-vector modulation [50].

J.Rodriguez et al. presented a technology review of voltage-source-converter topologies for industrial medium-voltage drives. This paper presents the operating principle of each topology and a review of the most relevant modulation methods, focused mainly on those used by industry. They asserted that the topology and modulation-method selection are closely related to each particular application, leaving a space on the market for all the different solutions, depending on their unique features and limitations like power or voltage level, dynamic performance, reliability, costs, and other technical specifications [51]. Leopoldo G. Franquelo et al. made a review study and claimed that multilevel inverter technology has potential in current and future power applications by expailing MLI topologies, modulation techniques, fault-tolerant system designing and usage areas detailly [30]. And current survey studies about MLIs are presented in [49,52].

As a special case, S.Daher et al. presented a compilation of the most common topologies of multilevel converters is and showed which ones are best suitable to implement inverters for stand-alone applications in the range of a few kilowatts. He asserted that the most suitable topologies are the multiple transformer and the multi-winding transformer for stand-alone applications [54].

P.Palanivel analysed three carrier pulse width modulation techniques, the constant switching frequency (CSF), variable switching frequency (VSF), and phase shifted pulse width modulation (PSPWM), which can minimise the total harmonic distortion and enhances the output voltages from five level inverter [53].

Steffen Bernet et al. was designed and compared neutral-point clamped, flying capacitor and series connected cascaded H-Bridge multilevel inverters at the same voltage level and showed that series connected cascaded H-Bridge inverts are very attractive for high frequencies [47].

In this thesis, cascaded H-Bridge inverters are used as a base for proposed inverter. Hence, literature review of cascaded H-Bridge inverter is made in detail. The CHBs generally divided into two main categories; CHB with separate DC sources and with single DC source.

A.R.Being et al. proposed a fifteen-level cascaded H-bridge configuration with equal seperate DC sources with low harmonic content using low voltage MOSFETs as switching devices [55]. H.Patangia is presented a 8-level 1kW CHB inverter prototype with seperate DC sources using sectionalized PWM technique. They achived 99% efficiency but their system has high total harmonic distortion which is about 15% [56]. O.L.Jimenez et al. focused on the comparative study of cascaded multilevel inverter with two inverter cells, symmetric (5 levels) and asymmetrical (7 and 9 levels). These inverters are implemented without changes in the power semiconductor devices, only modify the control stage and input supply voltages in the cells. Their work presented the analysis of the output voltage total harmonic distortion (THD) of CHB and ACHB [20]. N.Farokhnia et al. applied minimisation of total harmonic distortion (MTHD) switching strategy is applied to the cascaded multilevel inverter to reduce the THD. In this paper, they proposed to consider the alterable DC sources instead of constant DC sources, if it is possible. They showed that the value of THD in both cases of phase and line voltages is effectively reduced [57]. J.Pereda et al. offered a solution to the problem of Cascaded H-Bridge(CHB) Asymetric cascaded H-bridge(ACHB) inverters that is large number of and bidirectional and isolated dc supplies. This problem reduces the power quality with the voltage amplitude. They presented a solution to this problem by using highfrequency link using only one DC power source which reduces the number of active semiconductors, transformers, and reduces harmonic content [58]. Also, Cheol-soon Kwon et al. proposed a cascaded H-bridge multilevel inverter employing trinary dc sources in order to obtain a large number of output voltage levels with minimum devices which permits to easy increase of the output voltage levels and output power owing to modularity characteristic [59].

The CHB inverters using single DC source are examined in literature in two main groups; with virtual DC sources and with transformers in literature. CHB inverters with virtual DC sources are presented as a new hybrid CHB inverter which modifies the traditional CHB inverter by using one DC source. The traditional cascade multilevel inverter requires n DC sources for 2n + 1 levels. The proposed system allows the use of a single DC source as the first DC source which would be available from PV cells, batteries or fuel cells, with the remaining DC sources being capacitors. K.M Tsang et al. designed a PWM-less 27-level inverter has been based on three cascaded H-bridges with a single energy source and two capacitors. These capacitors are used as virtual DC sources in this work [60]. There are some studies based on this topology with different modulation techniques [46,48,61,62,63].

CHB inverter systems with transfromers are presented as a solution to one of the major limitations of the cascade multilevel converters which is requirement of isolated dc voltage sources for each H-bridge, which increases the converter cost and reduces the reliability of the system. E.Barcenas et al , proposed a CHB topology that does not require different DC sources, using a single DC source for all the system. On the other hand, it maintains the isolation between the inverter and the system, which output transformers can be coupled for the application of series compensators. Some of the researchers are focused on adjusting the turn-ratios of transformers to achive desired voltage level with less component using different modulation techniques to reduce the THD, conduction losses and switching losses [64]. H.Weiss and K.Ince described design and layout of single phase system quasieight level PWM inverter system with the transformers' turn ratios of exponent 2 [65]. As an alternative way some of the authors offered a CHB multilevel PWM inverter system with cascaded transformers with turn ratios of exponent 3 to achive more output voltage level [66,67,68].

Also F.S. Kang proposed a system that reduces two-fold the secondary turn ratio of the transformer that is connected to the PWM inverter to reduce witching losses and THD with an efficient switching function [69]. As an alternative way, some studies are done that substitutes one of the full-bridge inverter by a half-bridge inverter by this difference they managed to reduce the number of switches and have a high quality output voltage [70,71]. In order to reduce the number of transformers, components size and to trim down the weight, some of the authors used three-phase transformers instead of single-phase transformers in CHB inverter systems [72,73,74,75].

If we look at the studies that employ bi-directinal switches; Yaosuo Xue and Madhav Manjrekar have used the full bridge approach with bidirectional switching method for a single phase with separated DC source, five-level-cascaded inverter [76].

Another work about bidirectional switching method is done by Won-kyun Choi and his coworkers for cascaded H-bridge inverter circuit [77]. Chawki Benboujema et al. compared various types of bidirectional switching methods. In their work they also used MOSFETs as semi-conductor elements within the bidirectional switch circuit for AC applications. The results of their work showed that MOSFETs are advantageous for applications with low voltage and high frequency requirements, whereas IGBTs are the only choice for applications with high voltage requirements [78]. In parallel with the study mentioned above, Benboujema et al. aimed to develop a bidirectional switch system for electricity networks. They compared voltage, current and gain parameters between the Bipolar Junction Transistor (BJT) and Trench Base-Shielded Bipolar Transistor (TBSBT) and determined the advantages and disadvantages of them [79].

With a fault-tolerant control strategy and reconfiguration technique, operation can continue with the undamaged cells; thus increasing the reliability of the system.

Pablo Lezana explained the fault identification methods and hardware modifications that allow for operation in faulty conditions. He asserted that that multilevel inverters can significantly increase their availability and are able to operate even with some faulty components [80].

Christophe Turpin et al. studied the probable faults of hard and soft switching techniques and emphasized that the more the switching elements are the higher the probability of a fault is [81].

Another study on this topic is done by Surin Khomfoi and Leon M. Tolbert, which investigates the feasibility of the fault correction techniques using neural networks.

They claimed that the mathematical modeling of systems having too many switching elements is difficult [82].

Another study on the topic of fault tolerance, the publication of Sergio Daher, is about the shutdowns of the excitation systems due to fault conditions and the cost of these shutdowns [7].